Способ и устройство преобразования сигнала произвольной формы с использованием ступенчатых пилообразных функций - RU2017107277A

Код документа: RU2017107277A

Формула

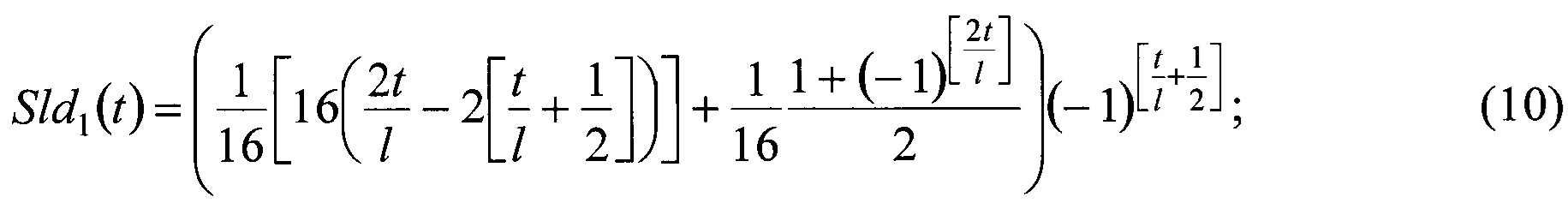

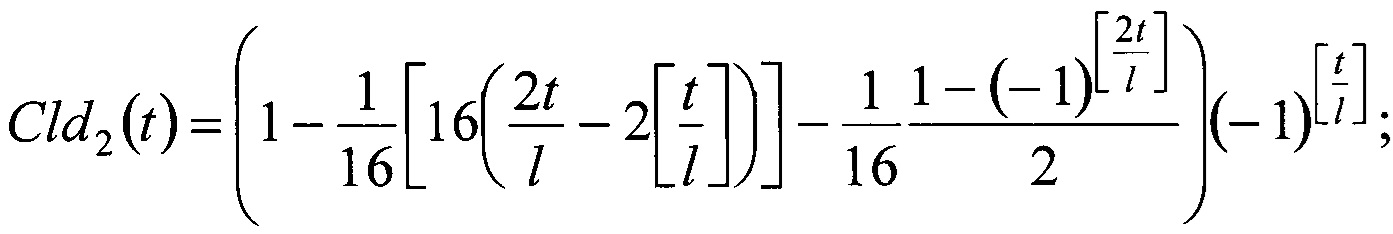

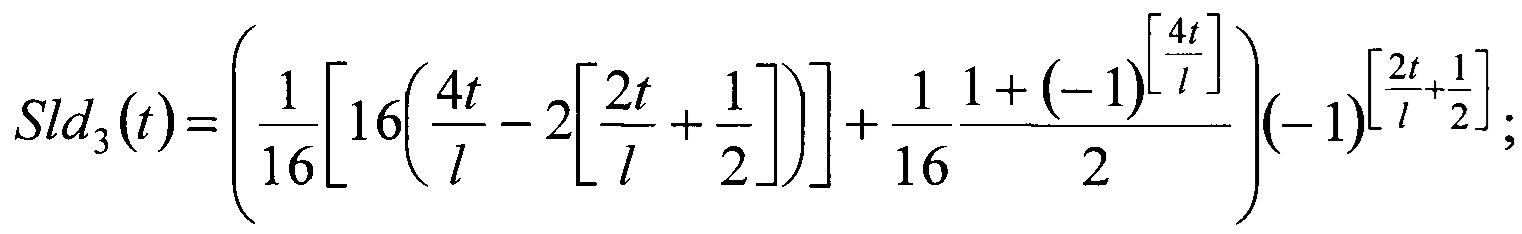

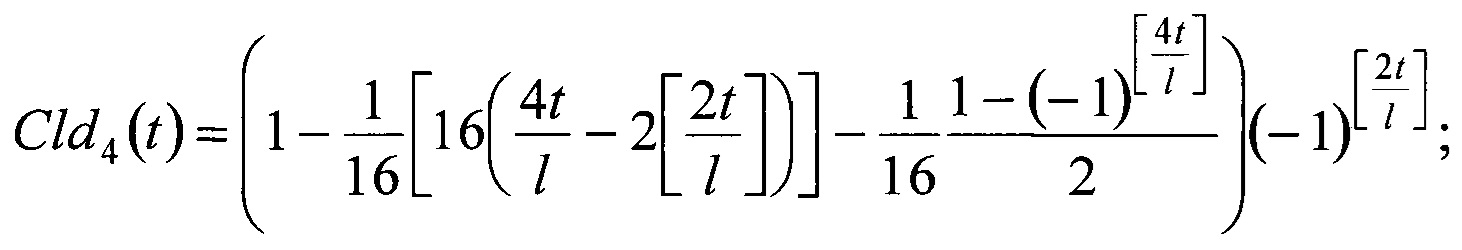

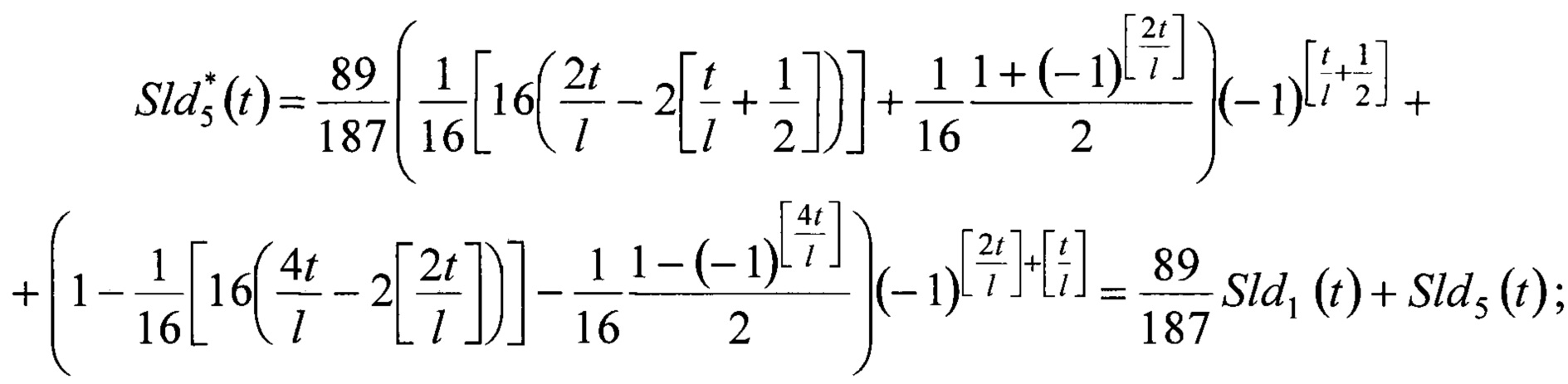

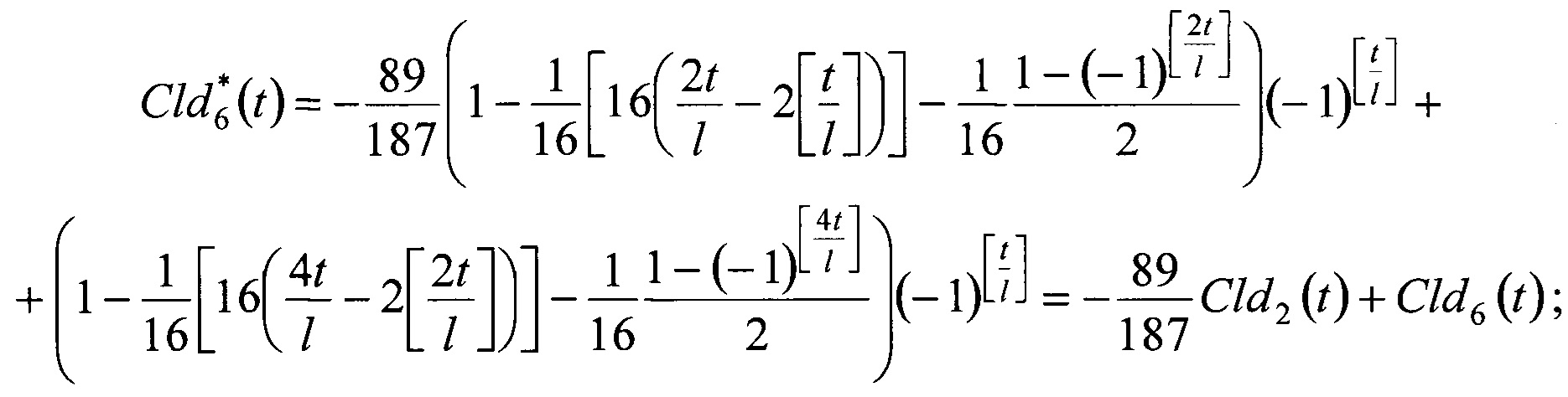

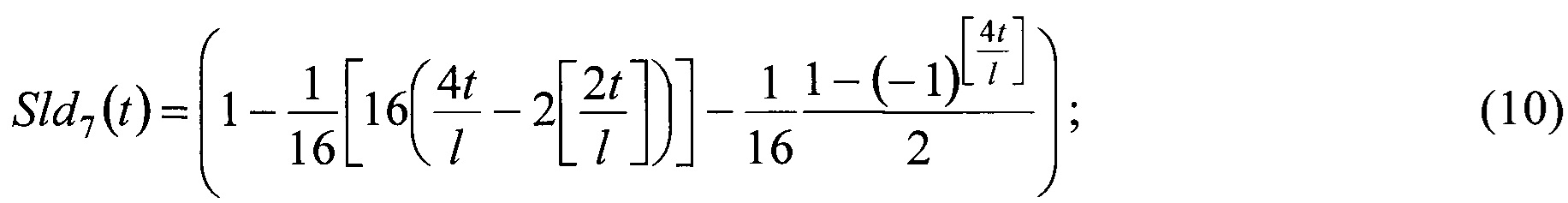

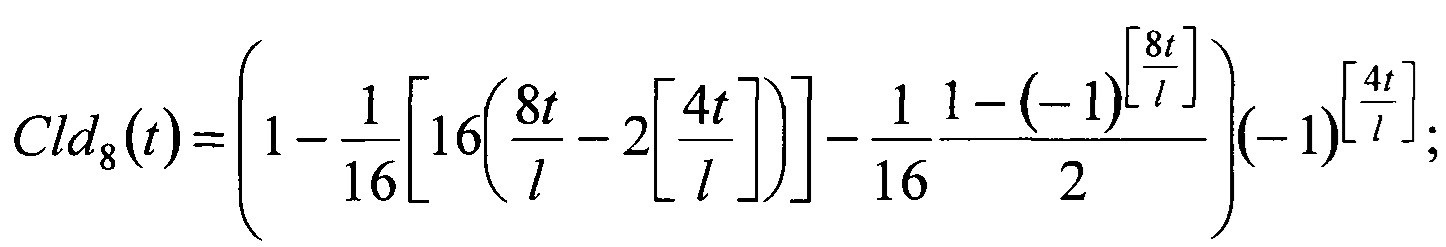

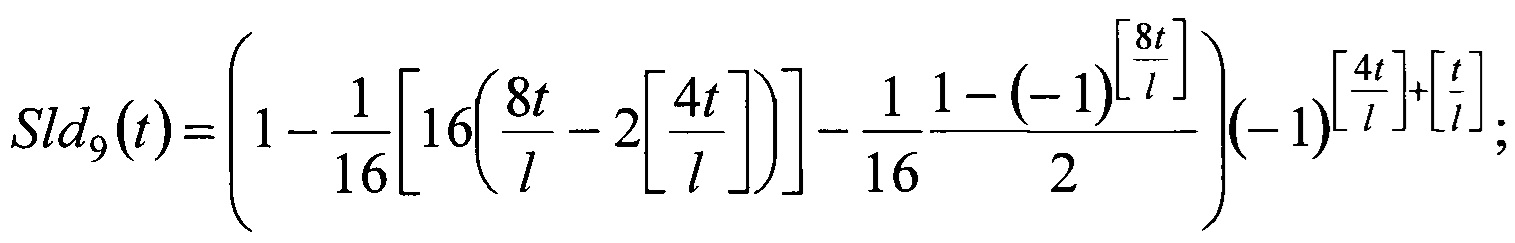

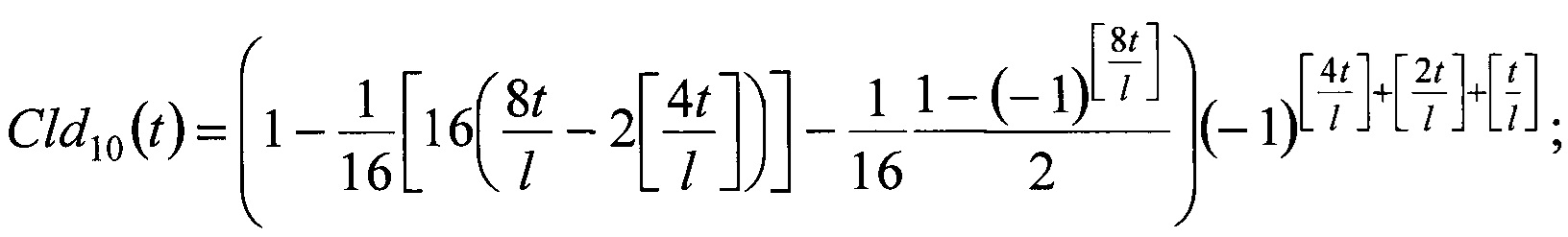

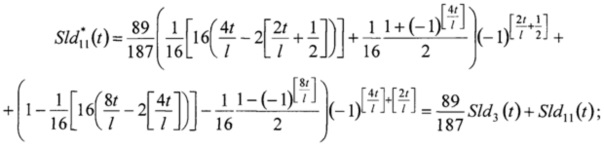

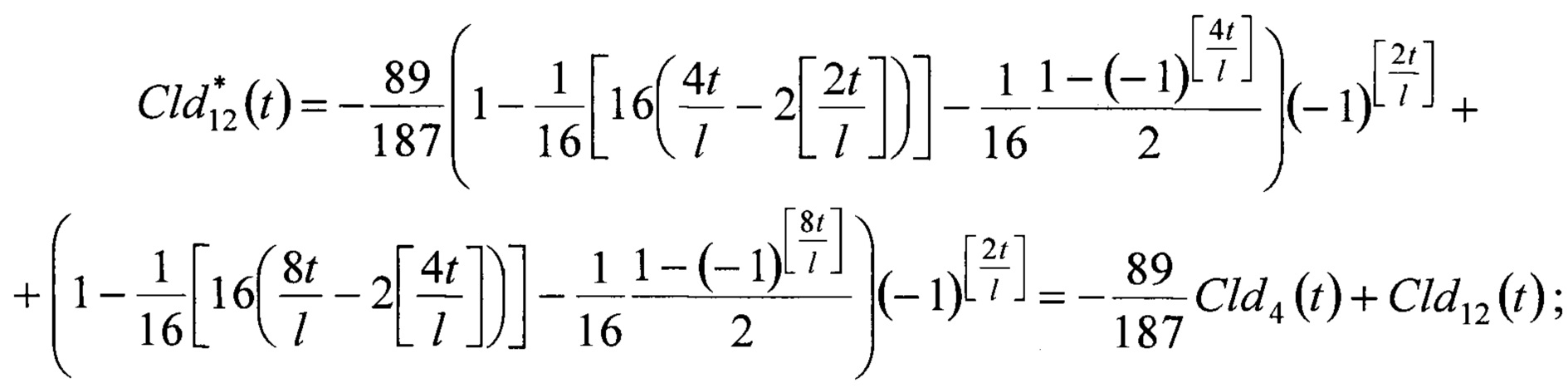

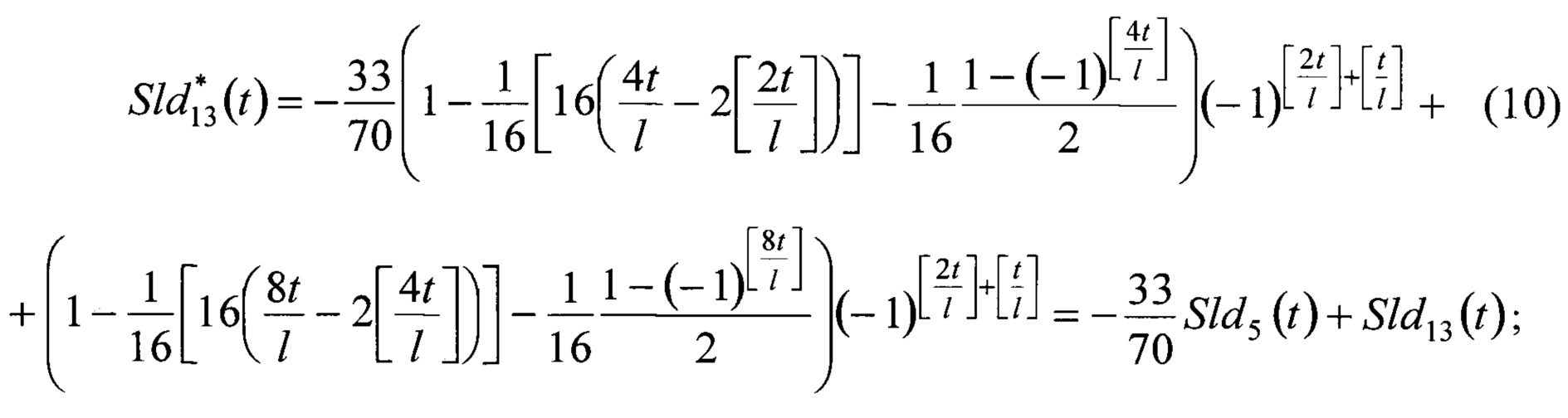

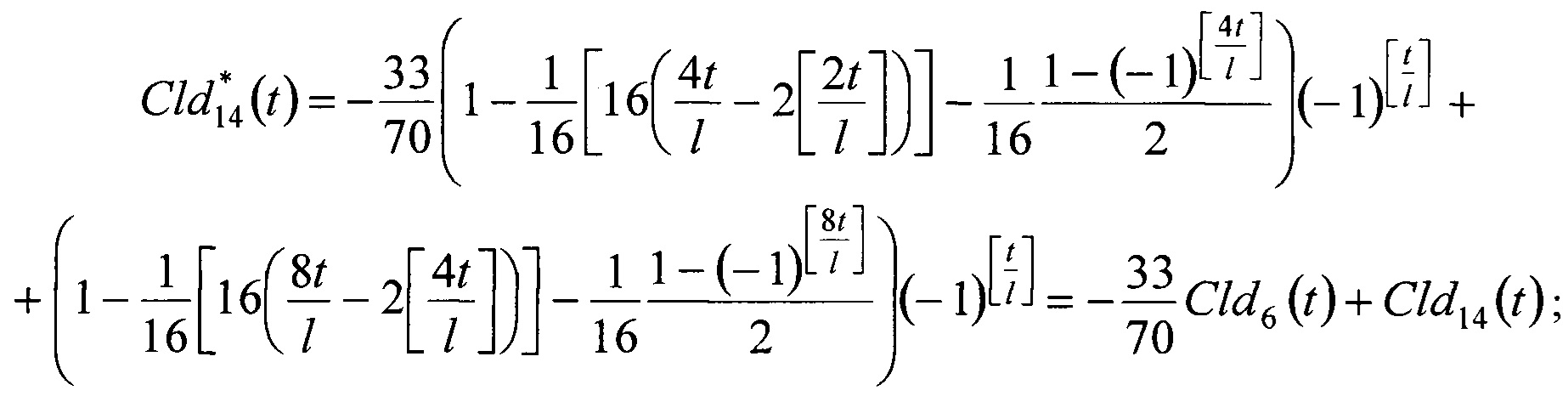

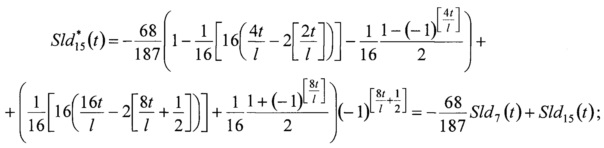

1. Способ преобразования сигнала произвольной формы, содержащий при прямом преобразовании параллельное формирование напряжений Уолша, принимающих значения ±1, интегрирование этих напряжений, формирование базиса ортогональных пилообразных напряжений, умножение этих напряжений на напряжение сигнала, интегрирование напряжений от произведений пилообразных напряжений на напряжение сигнала, вычисление, отсчитывание и запоминание коэффициентов преобразования, при обратном преобразовании сигнала: умножение коэффициентов преобразования, в виде напряжений, на соответствующие пилообразные напряжения и суммирование полученных напряжений, восстанавливающее сигнал, отличающийся тем, что с помощью генератора однополяоных прямоугольных импульсов и синхронных двоичных счетчиков формируют частоты однополярных прямоугольных импульсов с коэффициентами деления 2, 4, 8, 16, 32, 64, 128, 256, 512 и 1024, из которых с помощью четырех дешифраторов преобразуют параллельные четырехразрядные коды в напряжения логического уровня, появляющиеся на одном из шестнадцати выходов каждого дешифратора, с помощью этих напряжений и делителей, составленных из одинаковых резисторов, электронных ключей, коммутирующих выходы делителей напряжений, формируют ступенчатые пилообразно изменяющиеся во времени коэффициенты деления делителей напряжений в соответствии со следующим равенствами:

Cld0(t)=1;

где t - время;

l - полупериод преобразования напряжения Sld1 (t);

[…] - операция выделения целой части.

- одновременно, в процессе формирования базисных функций, параллельно умножают напряжение сигнала F(t) на ортогональные ступенчатые пилообразно изменяющиеся коэффициенты деления делителей напряжения;

- параллельно вычисляют значения интегралов от произведений сигнала и ортогональных ступенчатых пилообразно изменяющиеся коэффициенты деления делителей напряжений на промежутках длиной 2l:

- из значений интегралов, вычисляют значения коэффициентов преобразования по ступенчатым пилообразно изменяющимся коэффициентам деления делителей напряжений an в виде напряжений в соответствии с равенствами:

при обратном преобразовании (восстановлении, фильтрации) сигнала по ступенчатым пилообразно изменяющимся коэффициентам деления делителей напряжений, составленных из одинаковых резисторов:

параллельно умножают ортогональные ступенчатые пилообразно изменяющиеся коэффициенты деления делителей напряжений на напряжения, соответствующие значениям коэффициентов преобразования по ортогональным ступенчатым пилообразно изменяющимся коэффициентам деления делителей напряжений, затем параллельно суммируют полученные напряжения, восстанавливают сигнал, либо, положив отдельные коэффициенты an=0, фильтруют сигнал.

2. Устройство, реализующее способ преобразования сигнала произвольной формы, содержащее источник сигнала произвольной формы,

формирователь ортогональных пилообразных напряжений,

схемы умножения от 1-ой по 30-ю типа AD539,

0-й, 1-й, 2-й, …, 15-й блоки интеграторов,

0-й, 1-й, 2-й, …, 15-й блоки отсчитывающих и запоминающих элементов,

0-й, 1-й, 2-й, …, 15-й резисторы,

резистор обратной связи, операционный усилитель, генератор напряжений Уолша с числами секвент от 0 до 16,

выходы генератора напряжений Уолша подключены к одноименным входам формирователя ортогональных пилообразных напряжений,

выходы формирователя ортогональных пилообразных напряжений подключены к вторым входам схем умножения, а первые входы схем умножения соединены параллельно и подключены в выходу источника сигнала,

выходы схем умножения с 1-ой по 15-ю подключены к одноименным входам интеграторов с 1-го по 15-й,

выход источника сигнала произвольной формы через 0-й вход блока интеграторов подключен к входу 0-го блока отсчитывающих и запоминающих элементов;

выход 1-го блока интеграторов подключен к входу 1-го блока отсчитывающих и запоминающих элементов, выход 2-го блока интеграторов - к входу 2-го блока отсчитывающих и запоминающих элементов, … выход 15-го блока интеграторов - к входу 15-го блока отсчитывающих и запоминающих элементов;

выходы отсчитывающих и запоминающих элементов подключены к первым входам схем умножения с 16-ой по 30-ю, вторые входы схем умножения с 16-ой по 30-ю подключены к выходам формирователя ортогональных пилообразных напряжений,

выходы схем умножения с 16-ой по 30-ю подключены к входам сумматора,

к входу операционного усилителя подключен выход 0-го резистора, 1-го резистора, 2-го резистора, … 15-го резистора;

выход операционного усилителя, являющийся одновременно выходом устройства, подключен к входу резистора обратной связи;

отличающееся тем, что в него введены

- генератор однополярных прямоугольных импульсов, в котором частоту тактовых импульсов с помощью четырех синхронных счетчиков делят с коэффициентами 2, 4, 8, 16, 32, 64, 128, 256, 512, 1024;

- четырехзарядные выходы счетчиков, начиная с выхода коэффициента деления 2 и по 16, соединяют с выходами первого дешифратора, который преобразует четырехразрядный код, поступающий на входы в напряжение низкого логического уровня, появляющегося на одном из 16 выходов дешифратора, выходы первого дешифратора через инвертирующие схемы соединяют с входами управления ключей двух делителей напряжений модулей формирования ступенчатых пилообразно изменяющихся делителей напряжений;

- выходы делителей частоты с коэффициентами деления 4-32 соединяют с входами второго дешифратора;

- выходы делителей частоты с коэффициентами деления 8-64 соединяют с входами третьего дешифратора;

- выходы делителя соединяют с коэффициентами деления 16-128 соединяют с входами четвертого дешифратора;

- выходы второго, третьего и четвертого дешифраторов через инвертирующие схемы соответственно соединяют с входами ключей делителей напряжений еще трех формирователей ступенчатых пилообразно изменяющихся коэффициентов деления делителей напряжений;

- выходы четырех инверторов 1.0-1.15; 2.0-2.15; 3.0-3.15; 4.0-4.15 дешифраторов соединяют с одноименными входами управления ключами коммутации делителей напряжений 15 модулей формирователей ортогональных ступенчатых пилообразно изменяющихся коэффициентов деления делителей напряжений, объединенных в блок умножения сигнала на коэффициенты деления делителей напряжения при прямом преобразовании;

- входы всех делителей напряжения модулей формирования и умножения соединяют параллельно и подключают к выходу источника сигнала, на 15 входах формируют произведения напряжения сигнала на ступенчатые пилообразно изменяющиеся коэффициенты деления делителей напряжений и подключают к входам 15 интеграторов, кроме этого выход источника сигнала подключают к входу нулевых интеграторов;

- выходы интегратора соответственно с нумерацией подключают к входам схем отсчитывания и запоминания, выходы схем отсчитывания и запоминания подключают к входам схем вычисления коэффициентов разложения а0-а15;

для обратного преобразования:

выходы схем вычисления коэффициентов разложения а1-а15 соединяют с соответствующими входами 1-15 второго блока умножения сигнала ступенчатых пилообразно изменяющихся коэффициентов деления делителей напряжений,

выходы второго блока умножения соединяют с входами сумматора на операционном усилителе, кроме этого выход схемы вычисления коэффициента а0 соединяют с входом нулевого резистора сумматора, на выходе сумматора получают восстановленный сигнал.

Комментарии