Способ и устройство преобразования сигнала произвольной формы с использованием ступенчатых пилообразных функций - RU2682862C2

Код документа: RU2682862C2

Чертежи

Описание

Изобретение относится к области измерений, вычислительной и импульсной технике и предназначено для прямого, обратного преобразований и фильтрации сигналов произвольной формы и различной природы (речь, музыка, видео, связь и т.д.).

В настоящее время применяется большое количество различных базисов (Фурье, Уолша, Адамара, Хаара, Добеши и т.д.) [1, 2, 5, 6, 7, 8]. Выбор типа анализирующего базиса для обработки сигналов, как правило, определяется тем, какую информацию необходимо извлечь из сигнала. Каждый базис имеет свои характерные особенности во временном и частотном пространствах. С помощью различных базисов можно полнее выявить и подчеркнуть те или иные свойства преобразованного сигнала. При этом другим аспектом выбора является скорость и объем вычислений.

Наиболее часто наряду с классическим преобразованием Фурье используются преобразования Уолша или Адамара, являющегося аналогом преобразования Уолша, и пилообразные функции [1, 2, 4]. Эти преобразования имеют алгоритмы быстрого вычисления.

Преобразования сигналов, основанные на использовании напряжений Уолша и ортогональных пилообразных напряжений, относятся к классу линейных функций [1, 2].

Согласно преобразованию с использованием пилообразных напряжений в [1] (Приложение 1. Стр. 25-28), при прямом преобразовании сигнала (вычислении коэффициентов разложения) выполняют следующие операции:

- параллельно (одновременно) генерируют пилообразные напряжения;

- параллельно умножают сигнал в виде непрерывно изменяющегося напряжения F(t) (без оцифровывания) на пилообразные напряжения

- параллельно вычисляют значения интегралов от произведений напряжения сигнала на пилообразные напряжения на промежутках времени, равных 2l

где j∈N;

l - полупериод преобразования;

t - время;

- отсчитывают значения интегралов Jj, равные значениям коэффициентов разложения bj по пилообразным напряжениям

где при l=1 bj=Jj.

При обратном преобразовании сигнала (восстановлении и фильтрации):

- параллельно умножают коэффициенты разложения bj - в виде напряжений, полученных при прямом преобразовании, на пилообразные напряжения

- параллельно суммируют произведения коэффициентов разложения в виде напряжений на пилообразные напряжения, формируют восстановленный сигнал G(t), представляющий собой среднеквадратичное приближение входного сигнала F(t)

или фильтрованный сигнал, положив отдельные значения K(j)=0.

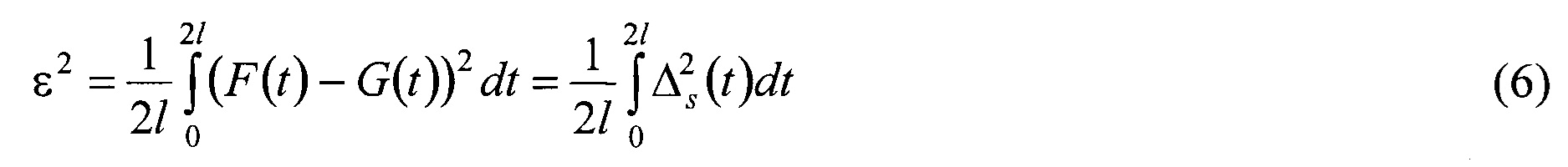

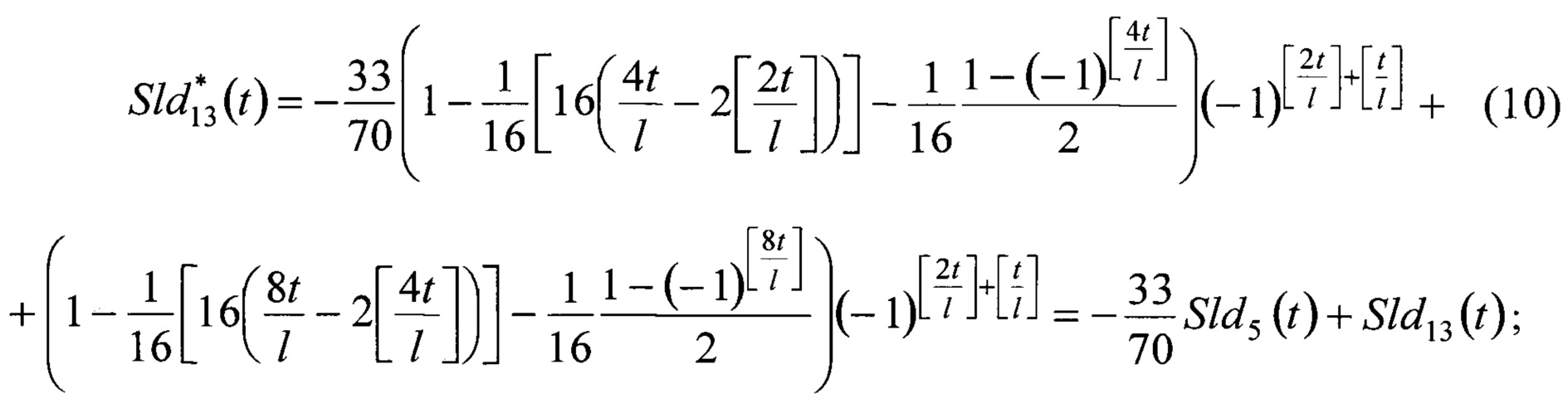

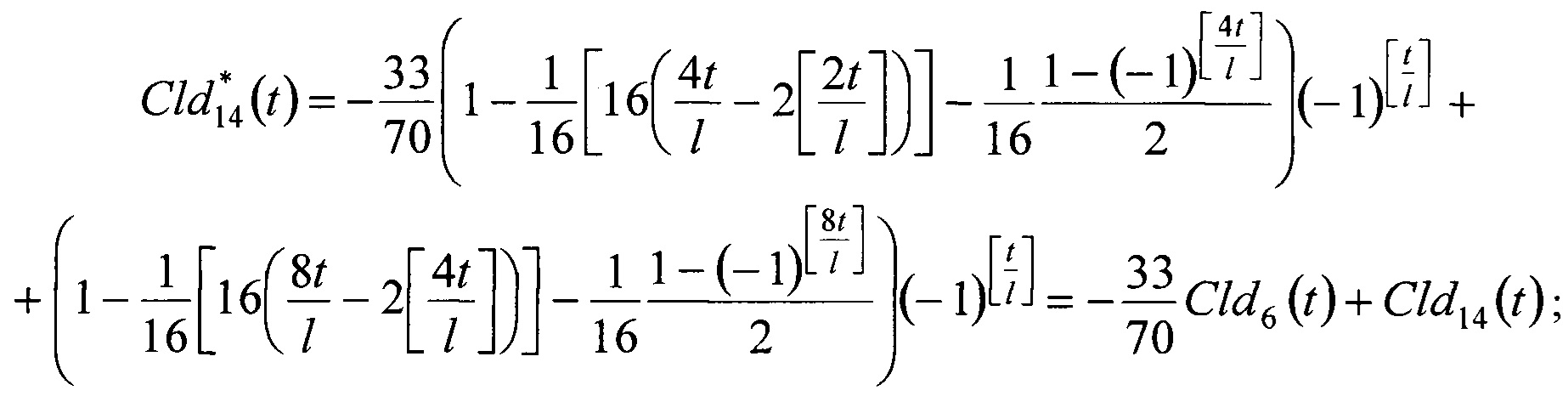

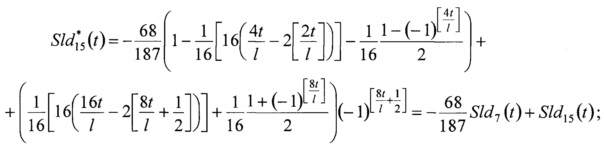

Для оценки возможности преобразования сигнала по предлагаемым ортогональным ступенчатым пилообразным функциям (10), отображающим изменение во времени коэффициентов деления делителей напряжений, составленных из одинаковых резисторов, и сравнения способа, основанного на применении пилообразных функций из [1], используем вычисление средней квадратичной погрешности из [8] (Приложение 2. Стр. 414, 415)

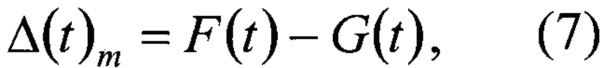

и наибольшее уклонение восстановленного сигнала G(t) относительно исходного F(t),

где: F(t) - исходный сигнал;

G(t) - восстановленный сигнал.

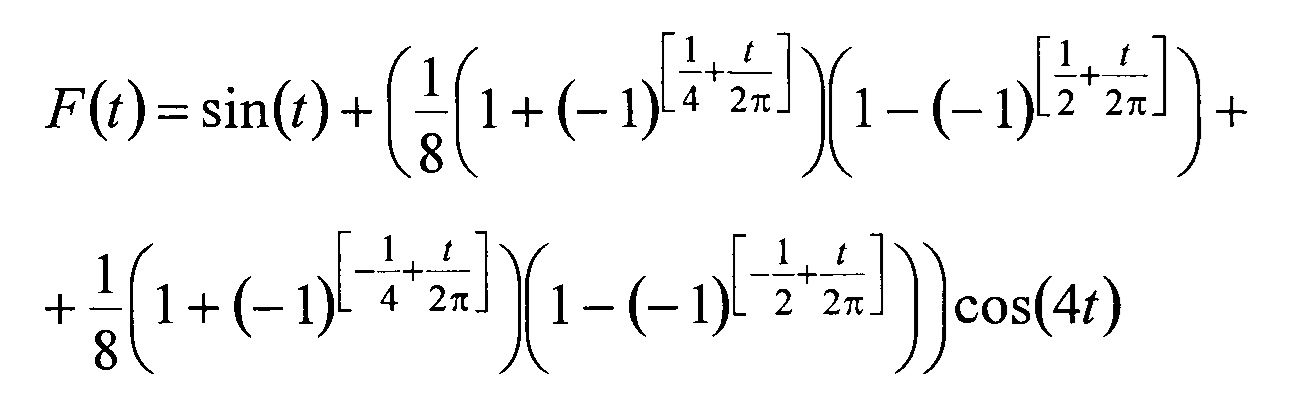

Исходный сигнал

подвергнем прямому и обратному преобразованию по пилообразным функциям из [1] и предлагаемым пилообразным ступенчатым функциям (9) и используем (6) и (7).

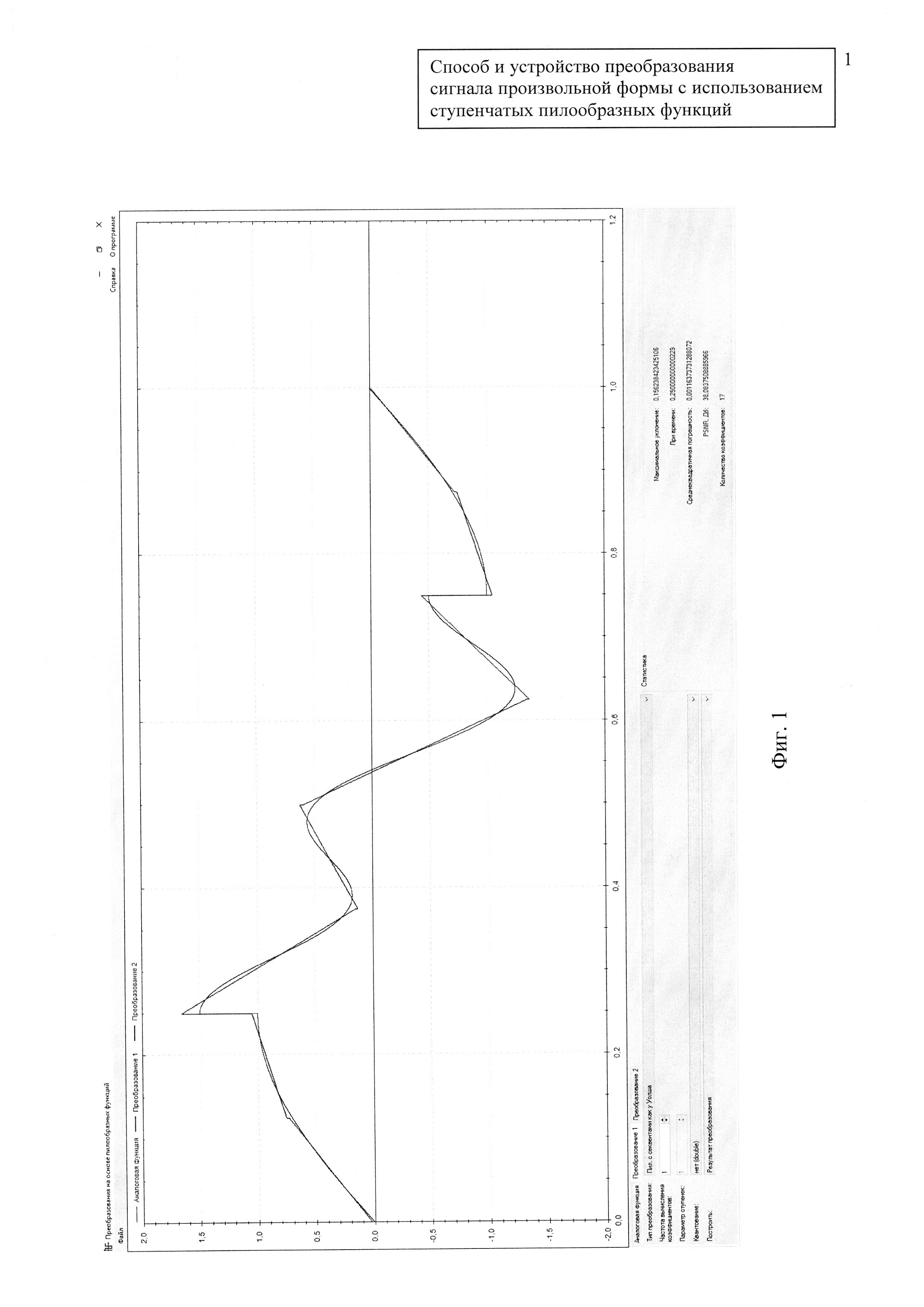

Результаты преобразования по пилообразным напряжениям приведены на фиг. 1.

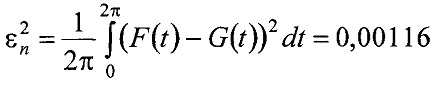

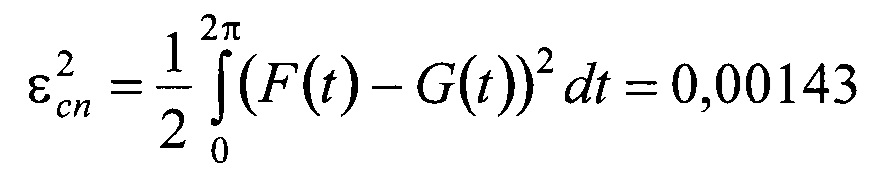

Средняя квадратичная погрешность по пилообразным напряжениям (методическая погрешность

а максимальное уклонение в отдельных точках более Δn(t)=0,15624.

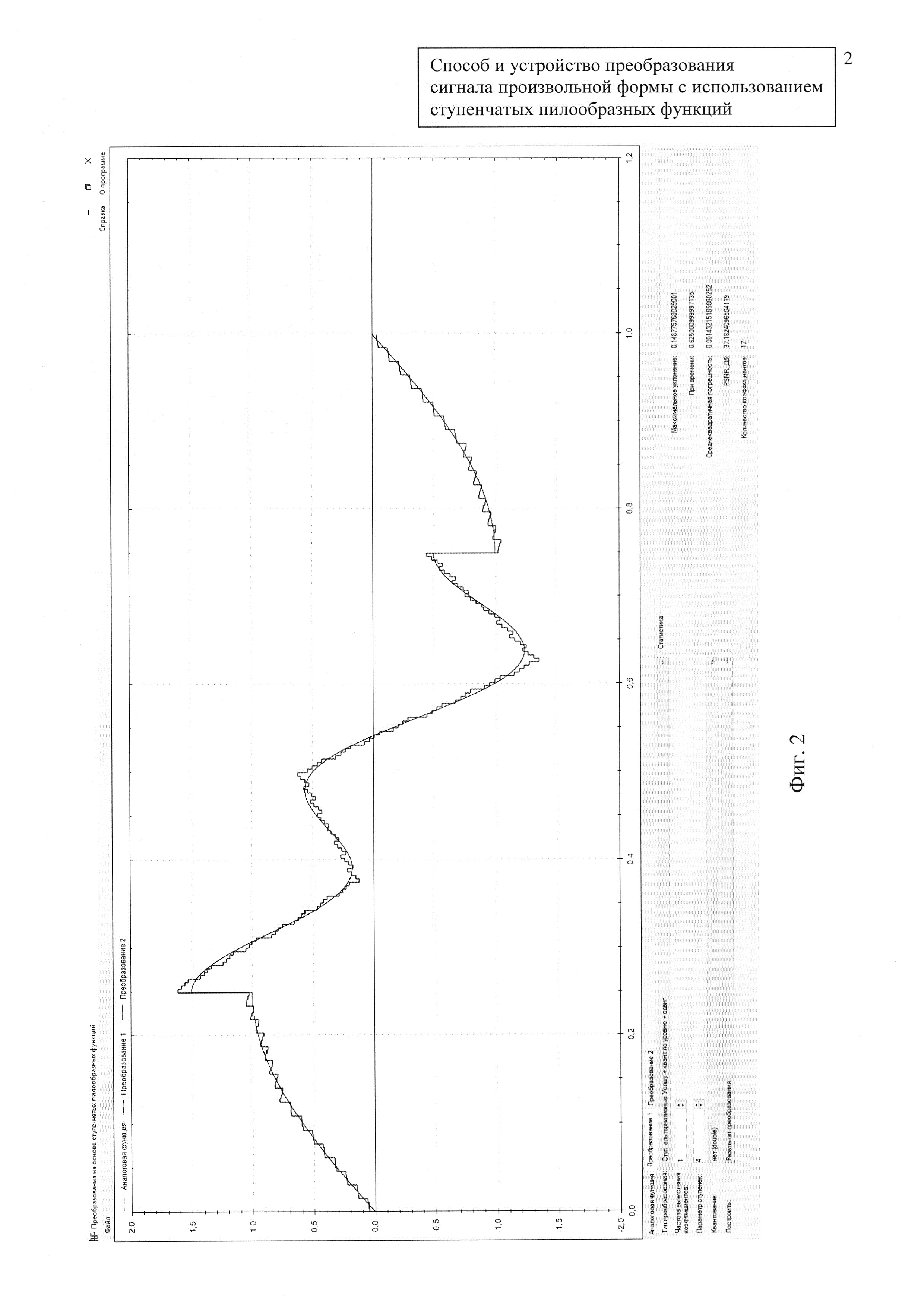

Результаты преобразования по пилообразным ступенчатым функциям в виде графиков приведены на фиг. 2.

Средняя квадратичная погрешность преобразования по пилообразным ступенчатым функциям (методическая погрешность

а максимальное уклонение

Δсn(t)=0,14878.

Для наглядности оценки этих двух преобразований результаты приведений и сигнал приведены на фиг. 1 и фиг. 2.

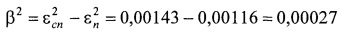

Из сравнения результатов следует, что методическая погрешность преобразования по пилообразным ступенчатым функциям уступает по сравнению с пилообразным преобразованием всего лишь на

а уклонение

δ=Δn-Δcn=0,15624-0,14878=0,0846.

Из сравнения способов следует, что практически эти способы имеют почти одинаковые методические погрешности, поэтому достоинства и недостатки этих методов следует сравнить при конкретной реализации.

При реализации способа [1], основанного на использовании пилообразных напряжений, используют двуполярные прямоугольные напряжения Уолша [2. Приложение 3. Стр. 47], которые интегрируют с помощью интеграторов на операционных усилителях, а также используют аналоговые умножители сигналов типа AD539 (Приложение 5), построенных также на операционных усилителях.

Из [4, 5] известно, что использование аналоговой техники связано с недостатками, обусловленными наличием сдвигов токов и напряжений, а также и температурой (Приложение 4. Стр. 54-56).

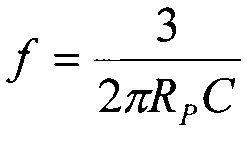

Из [4] следует, что у интеграторов с использованием операционных усилителей, в цепи отрицательной обратной связи которых устанавливаются конденсаторы, погрешность достигает 5% и выше (Приложение 4. Стр. 131, 132), что считается большими величинами даже при использовании различных способов компенсации токов смещения. Эти способы уменьшают погрешность интеграторов, однако при этом ограничивают область частот, в которой происходит интегрирование

где ƒ - частота интегрируемых импульсов, RP - сопротивление, шунтирующее конденсатор обратной связи, С - емкость конденсатора обратной связи.

При этом погрешность интегрирования составляет около 5%.

К тому же к конденсаторам обратной связи предъявляются повышенные требования.

На этапе умножения исходного сигнала F(t) на пилообразные напряжения [1] используются умножающие схемы, которые построены на базе операционных усилителей, также имеют погрешности. Лучшие умножители AD539 в соответствии с техническими характеристиками также обладают погрешностями (Приложение 5).

Целью изобретения является уменьшение аппаратной погрешности при использовании пилообразных напряжений, формируемых с помощью интеграторов на операционных усилителях и умножителях аналоговых сигналов на этапе вычисления произведений сигнала F(t) на пилообразные напряжения.

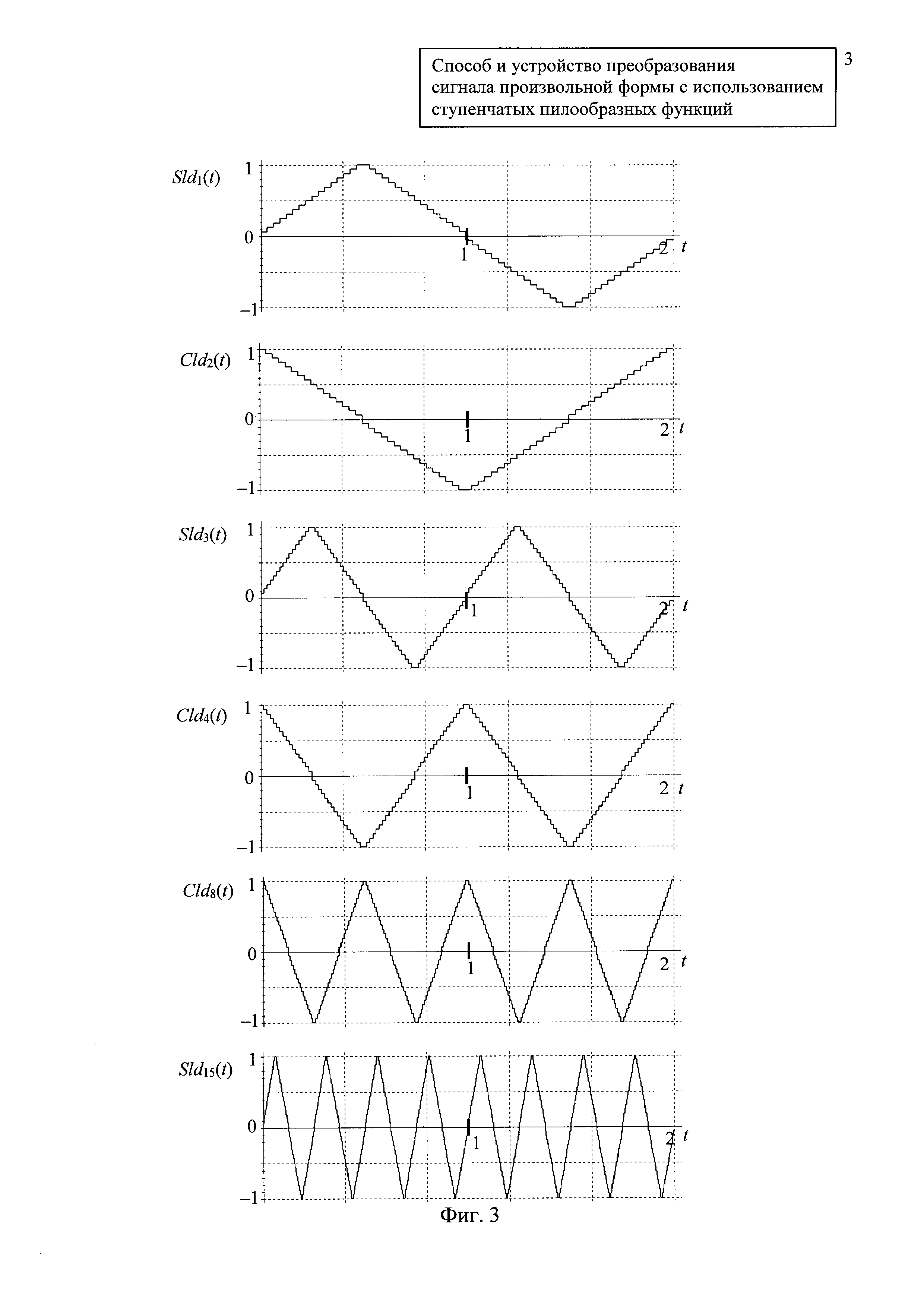

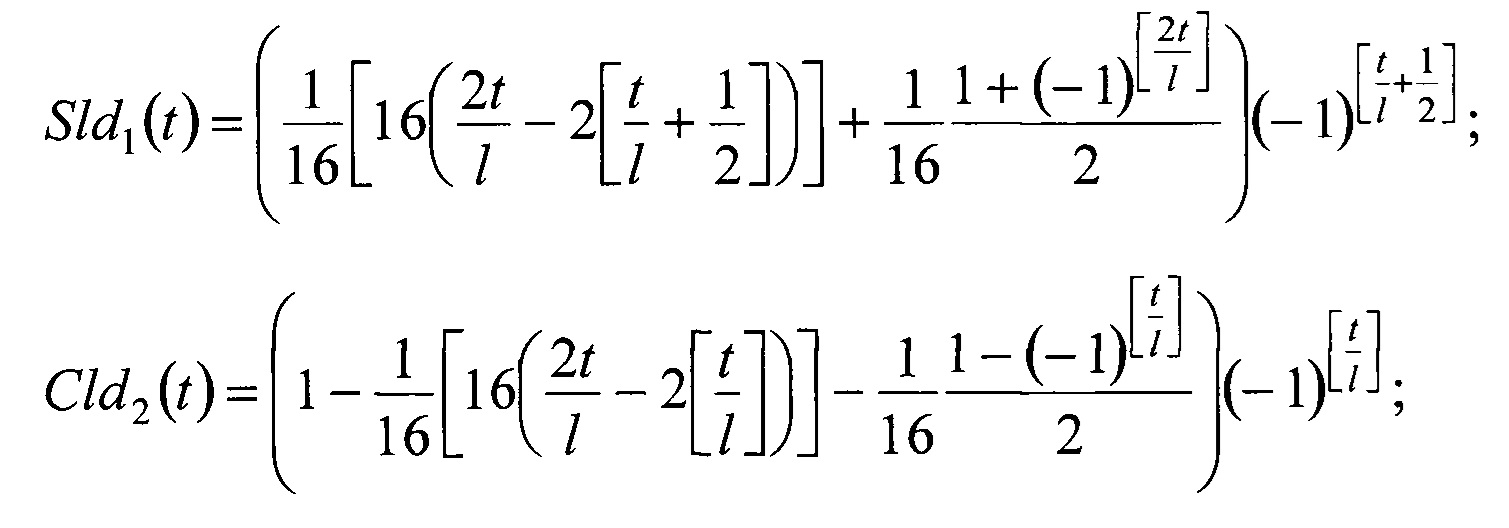

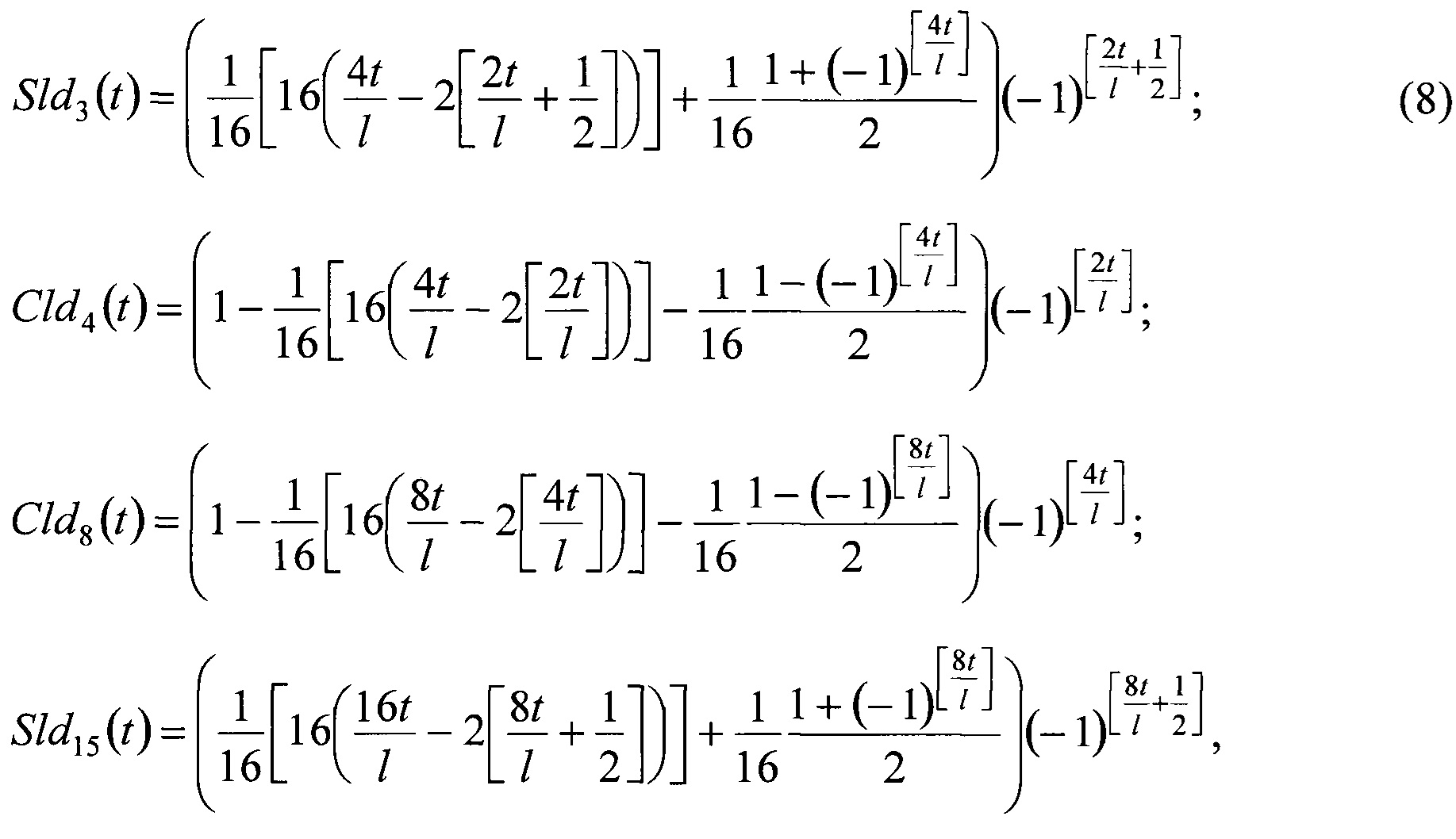

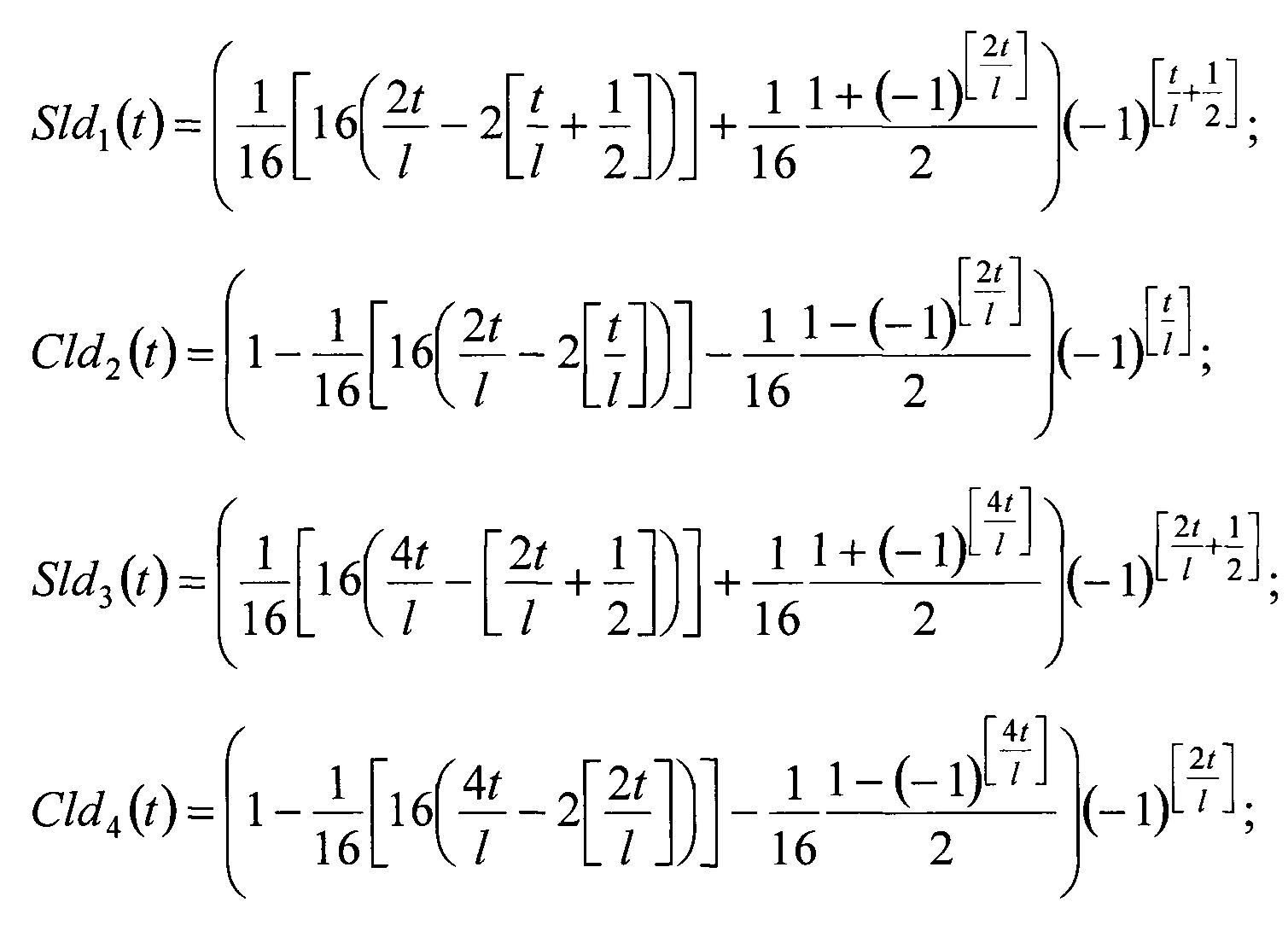

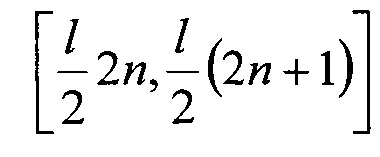

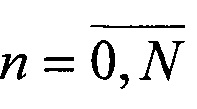

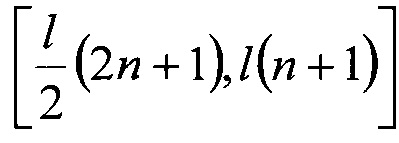

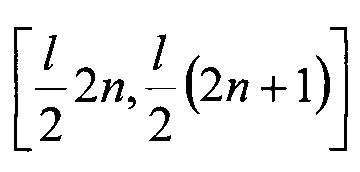

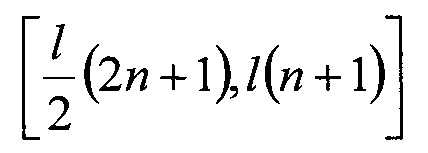

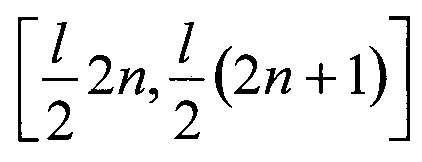

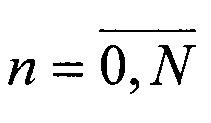

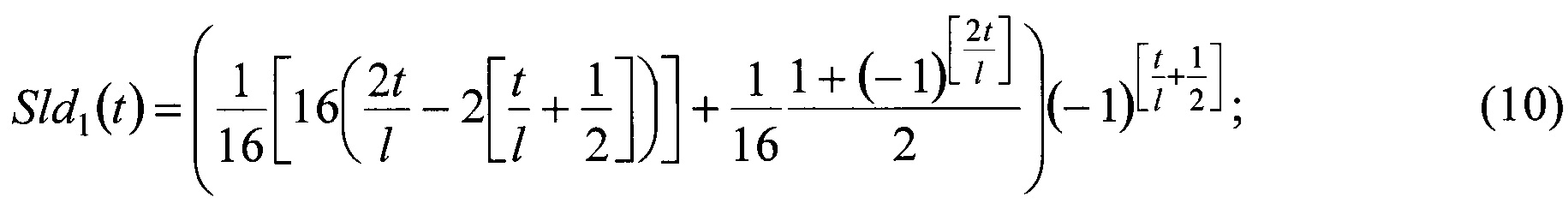

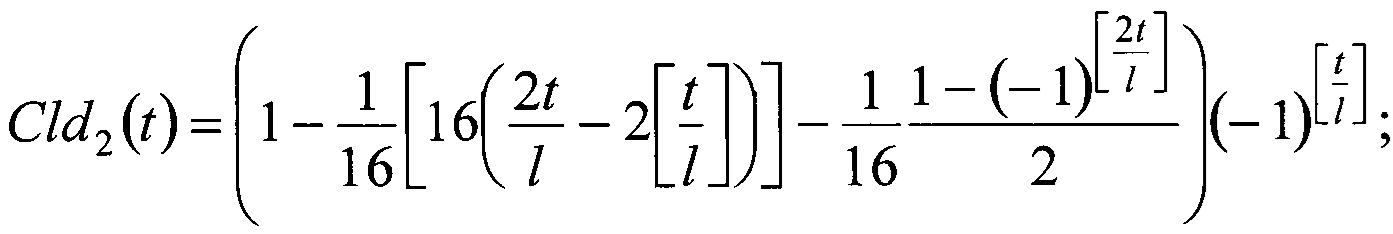

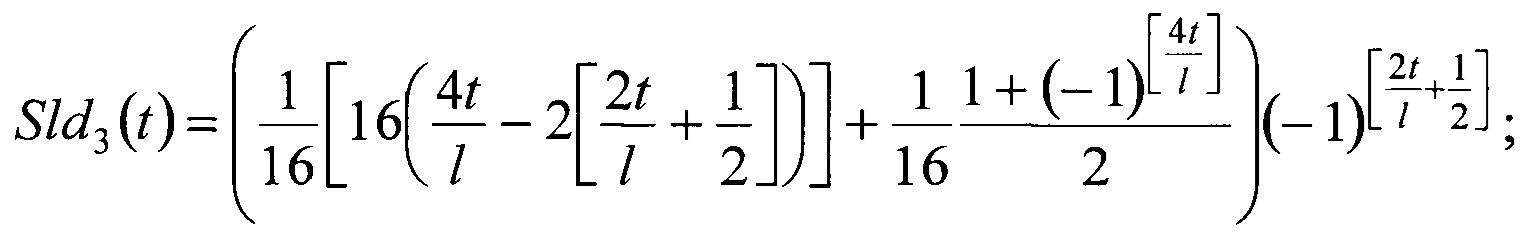

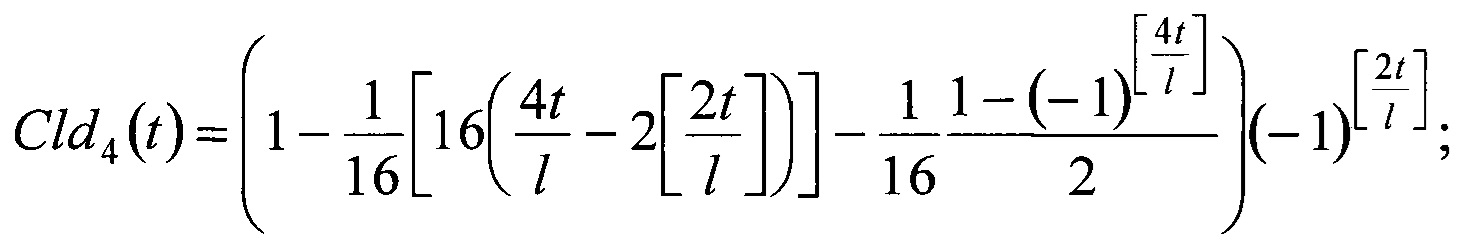

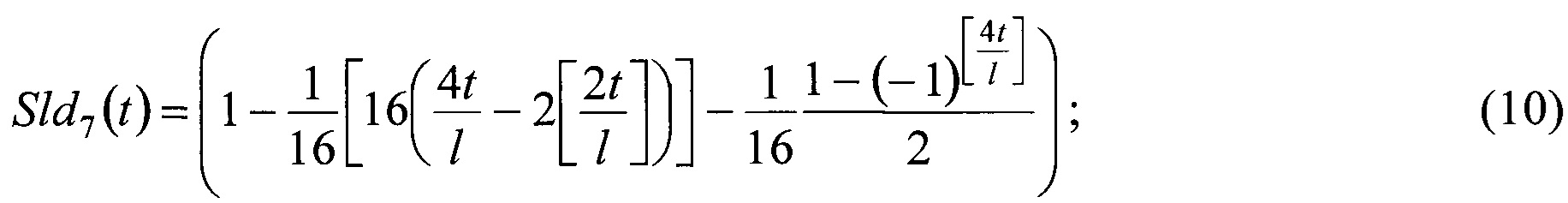

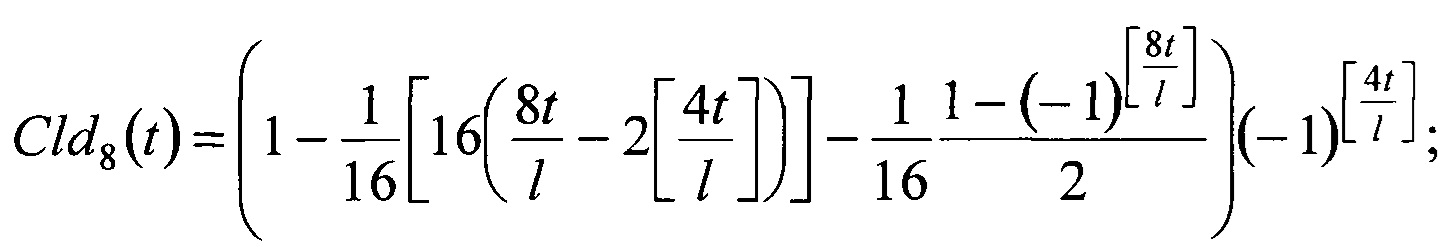

Поставленная цель достигается тем, что в предлагаемом способе и устройстве преобразования сигнала формируют порождающие ступенчатые пилообразные функции в виде изменяющихся во времени коэффициентов деления делителей напряжения, составленных из одинаковых резисторов, с числами секвент 1, 2, 3, 4, 8 и 15

где: t - время;

l - период преобразования Sld1;

[…] - операция выделения целой части.

Графики этих функций приведены на фиг. 3.

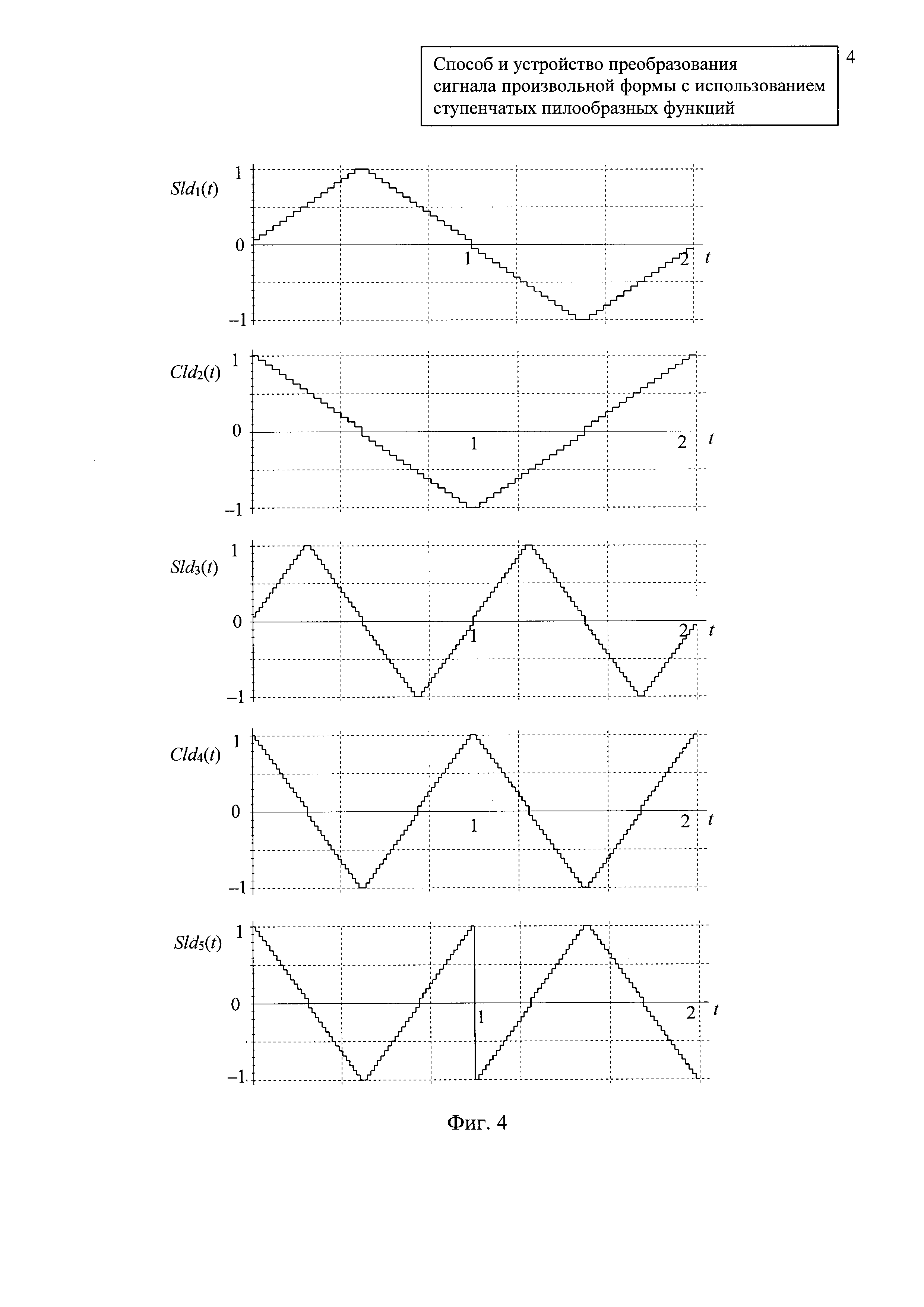

Затем, используя функцию ступенчатых пилообразно изменяющихся коэффициентов деления делителей напряжения с числами секвент 4 и 8 с помощью электронных ключей и усилителей, изменяющих знак на -1 (Фиг. 9, фиг. 10, фиг. 20)

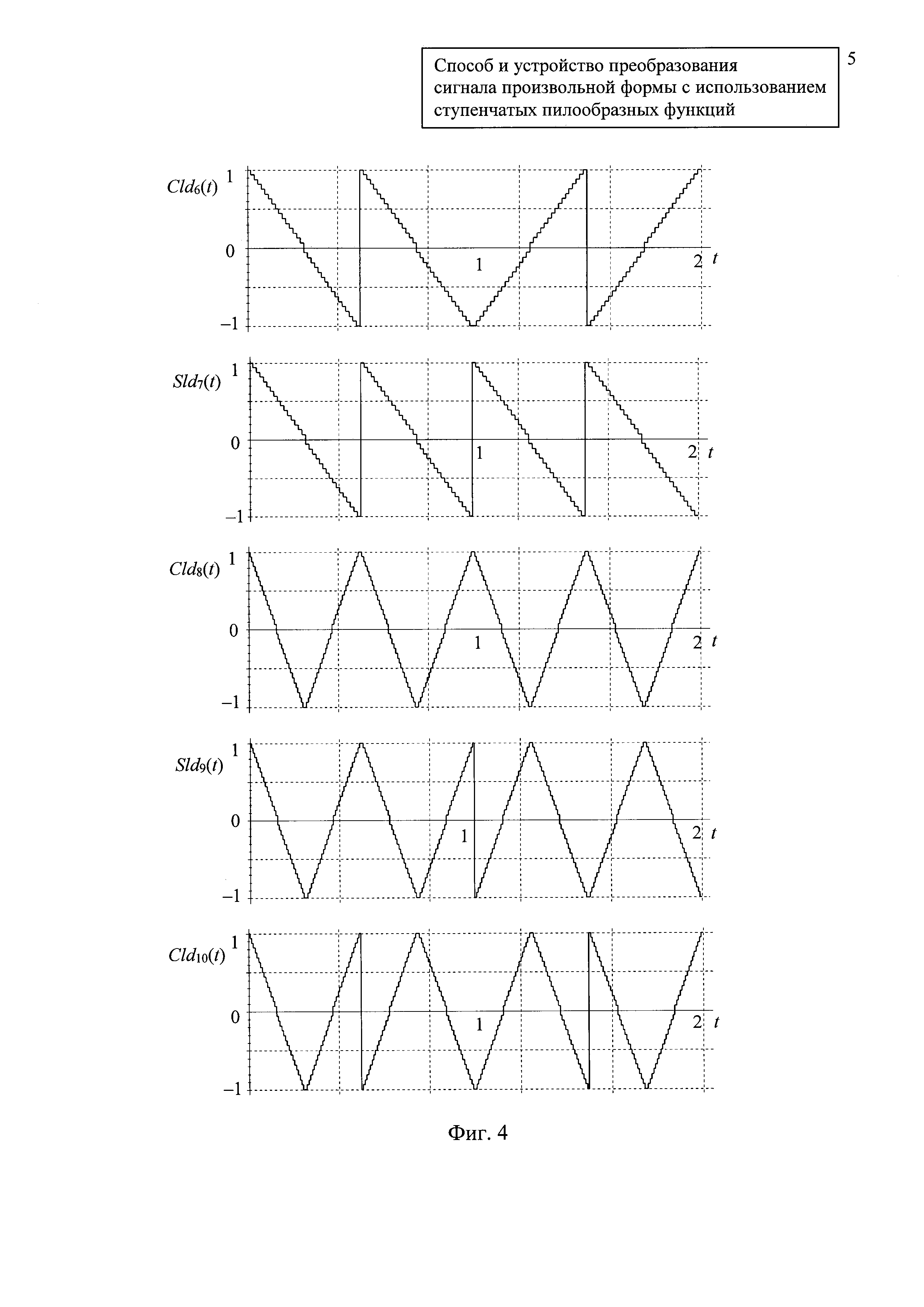

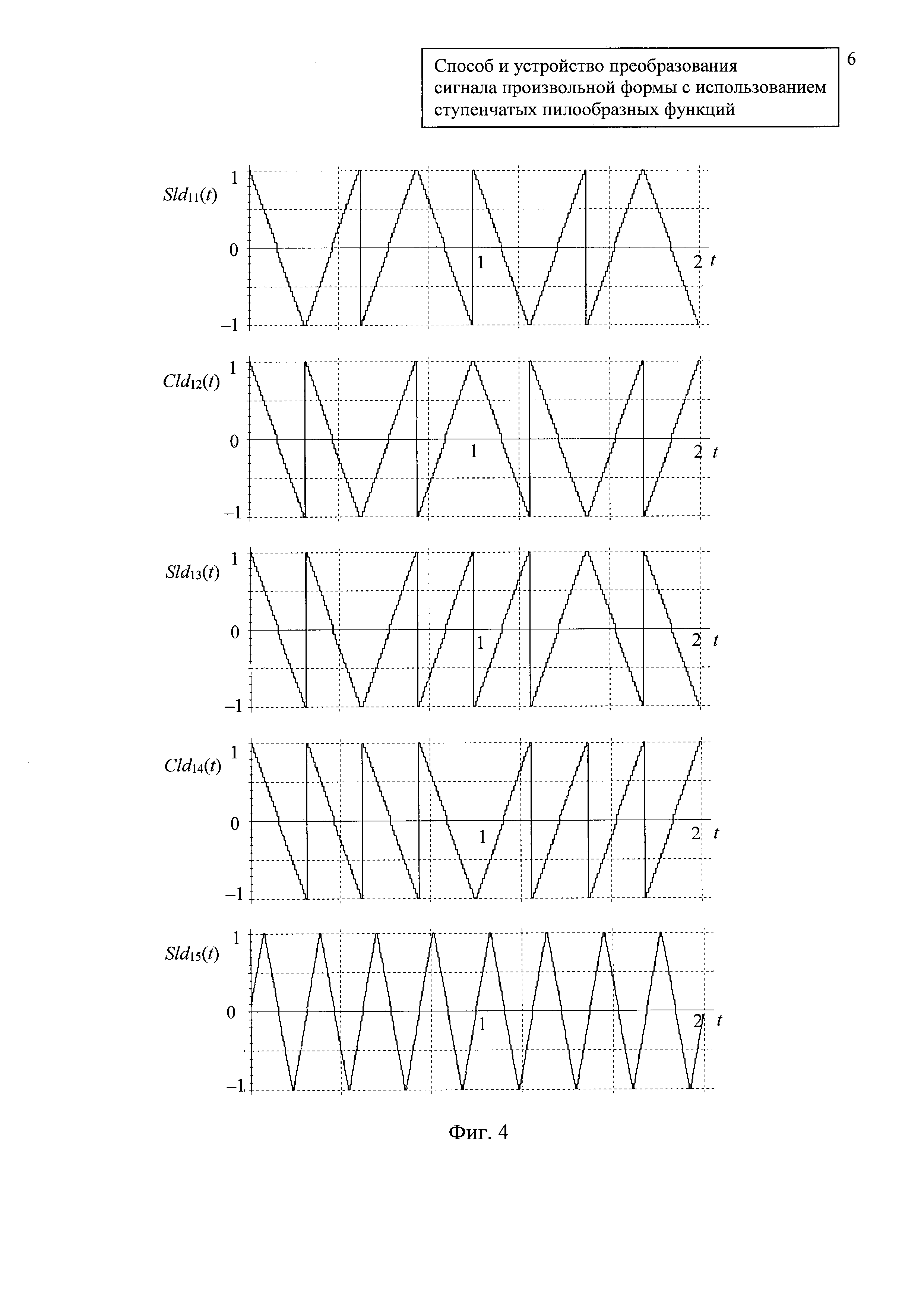

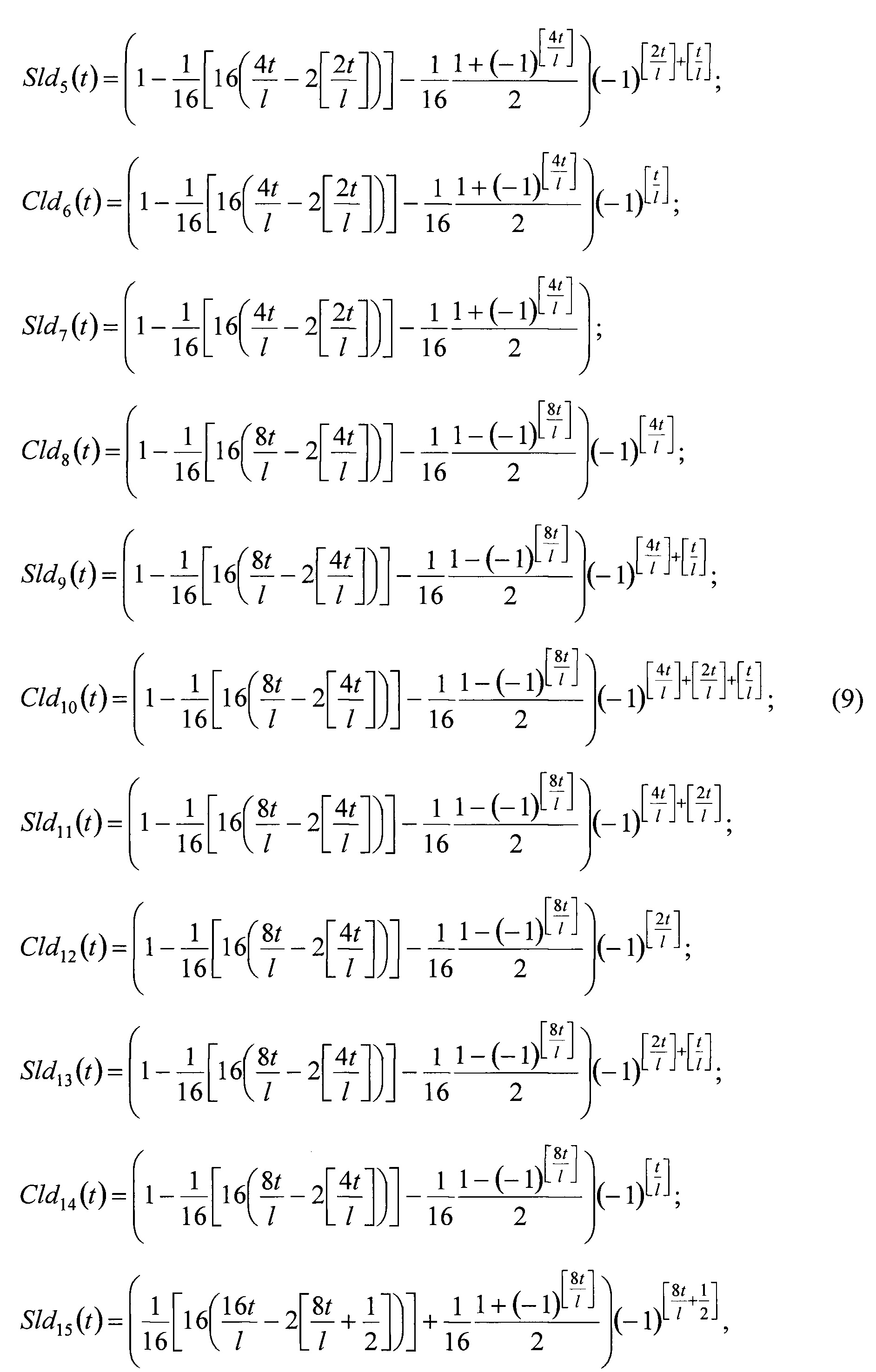

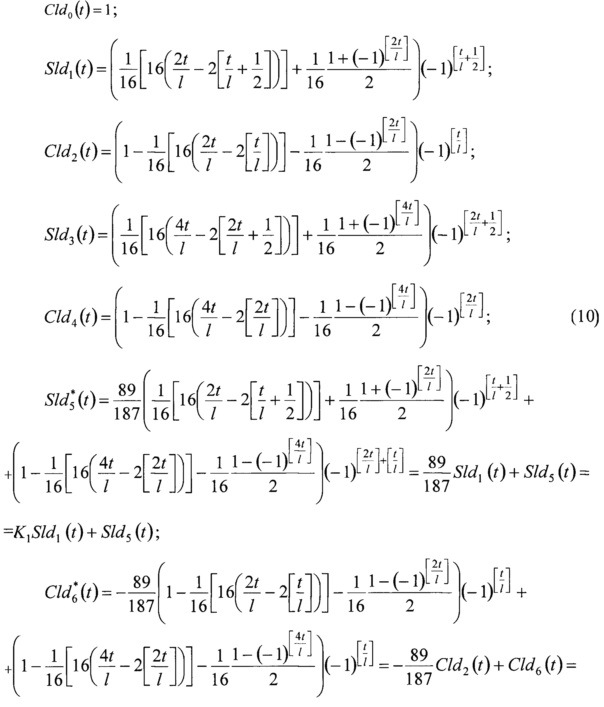

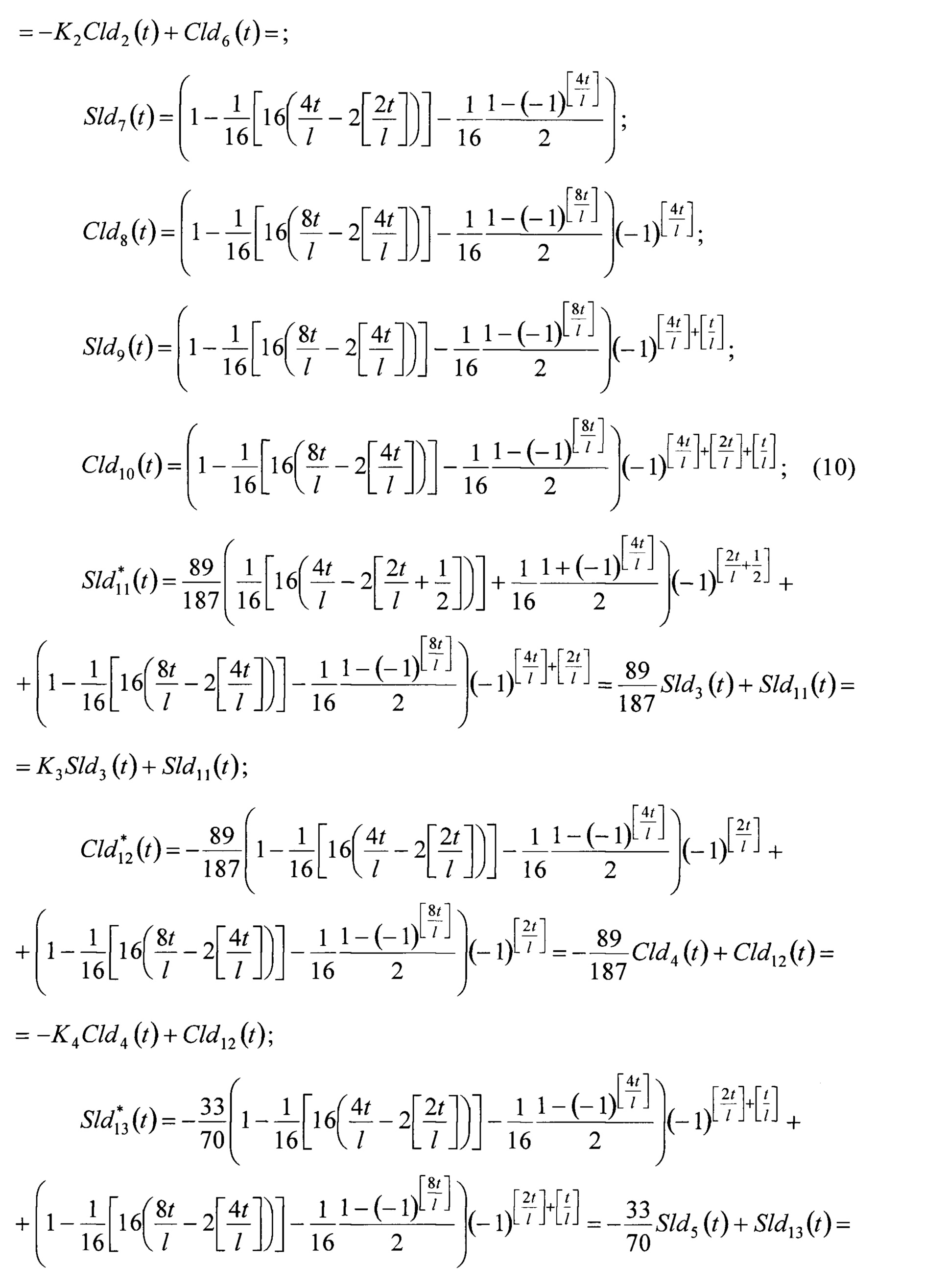

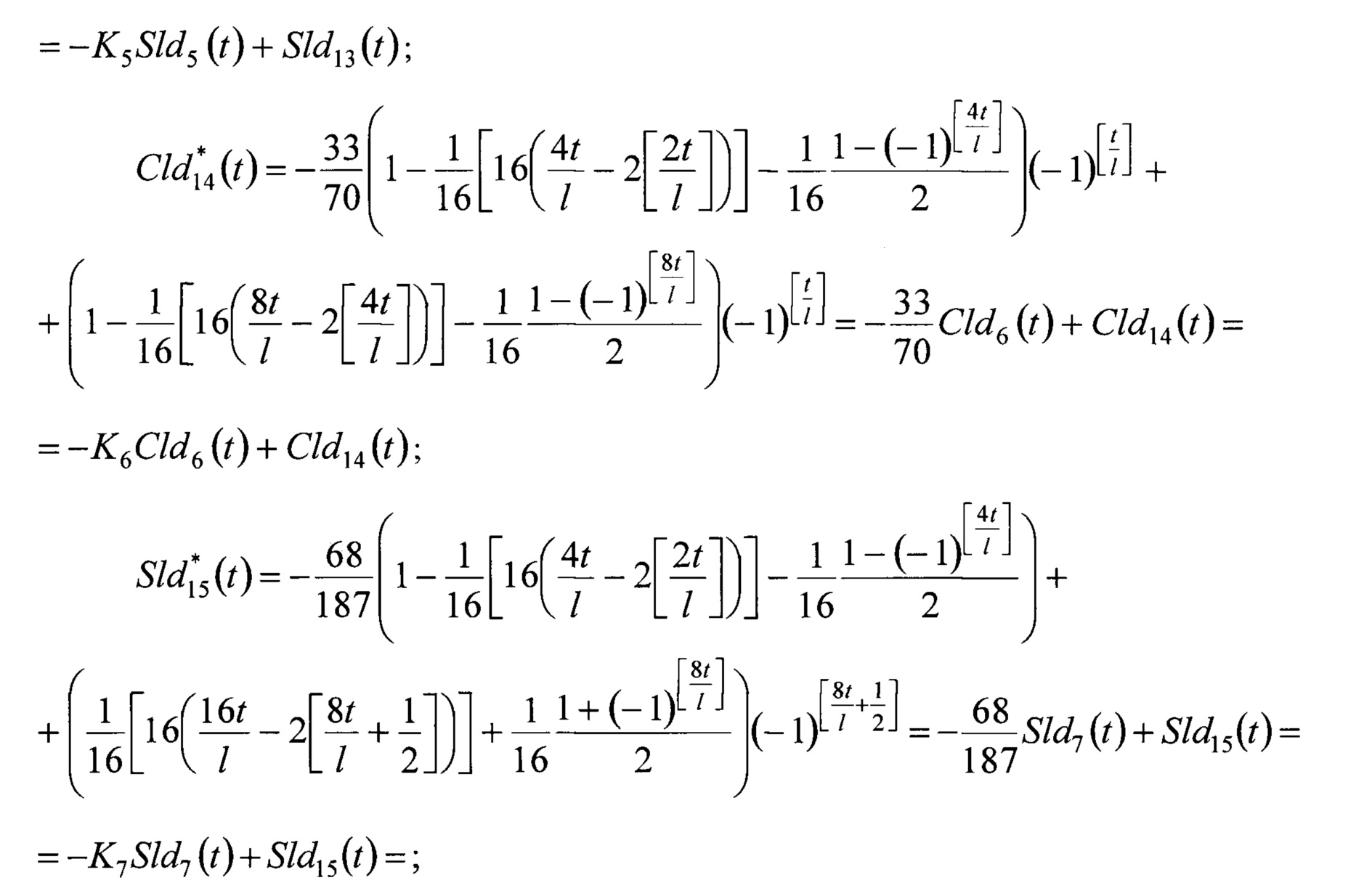

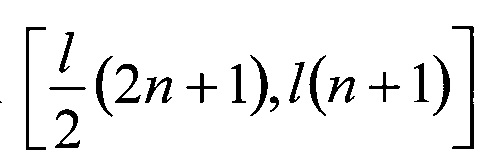

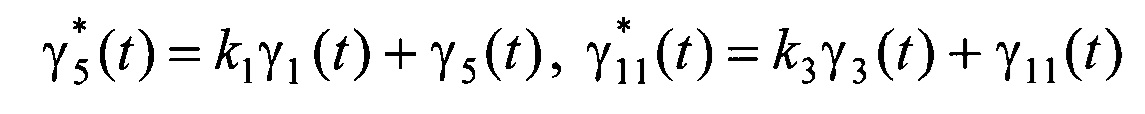

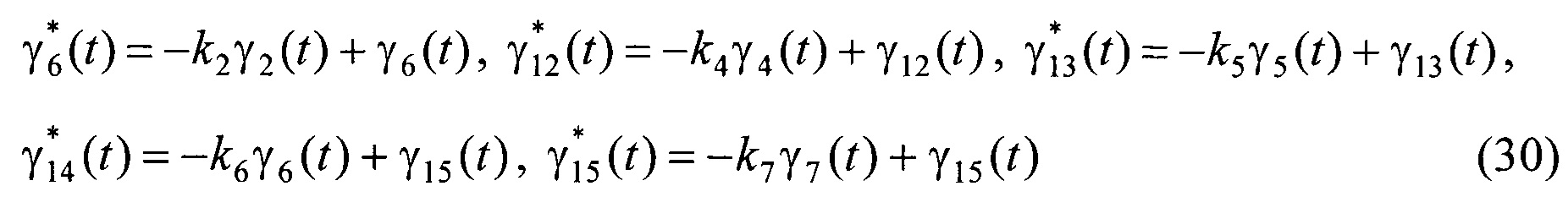

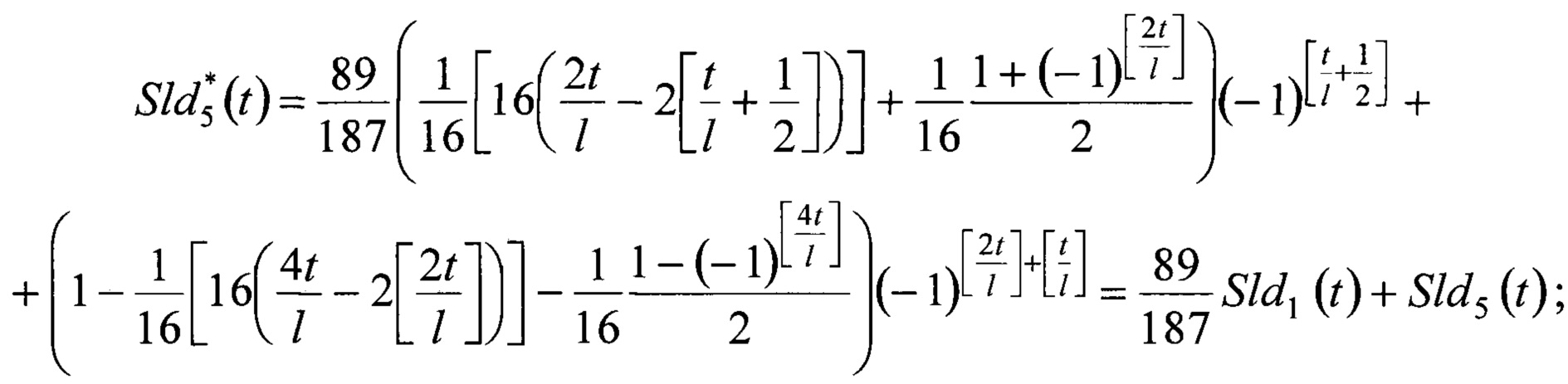

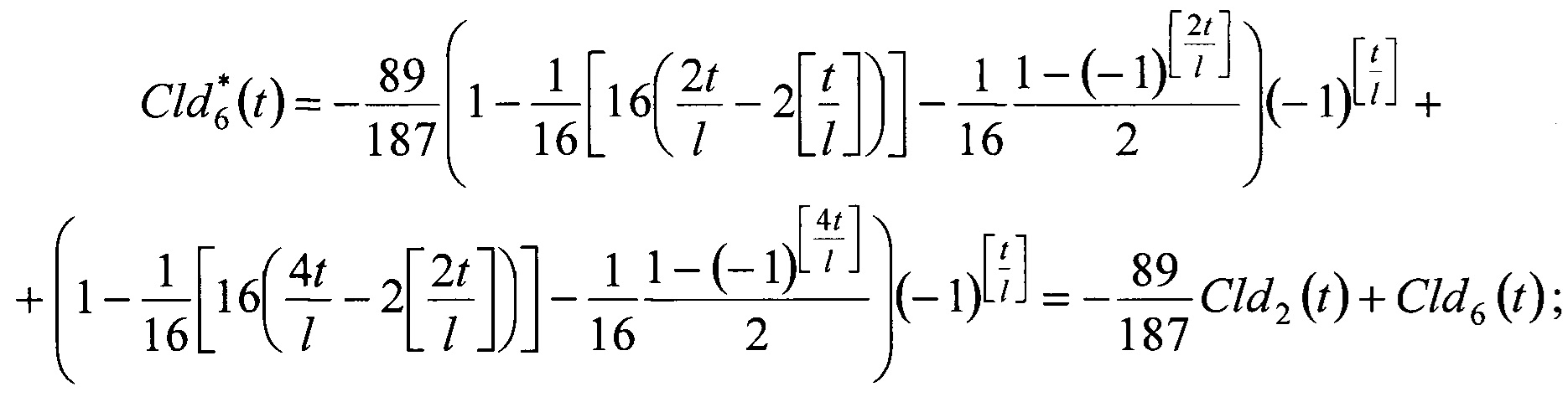

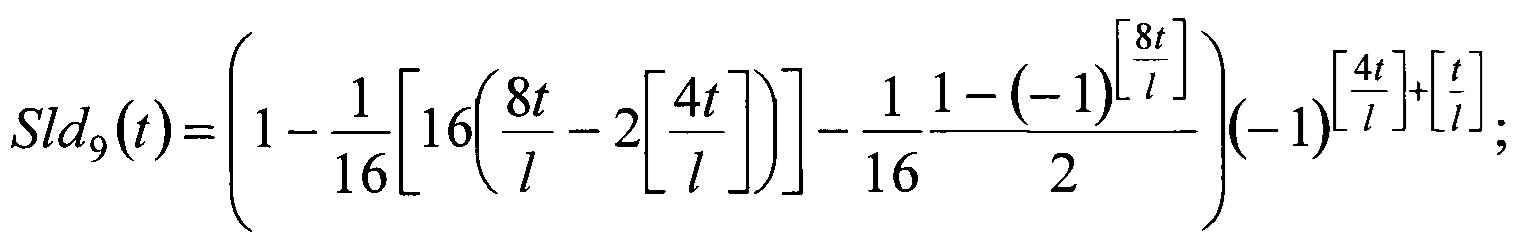

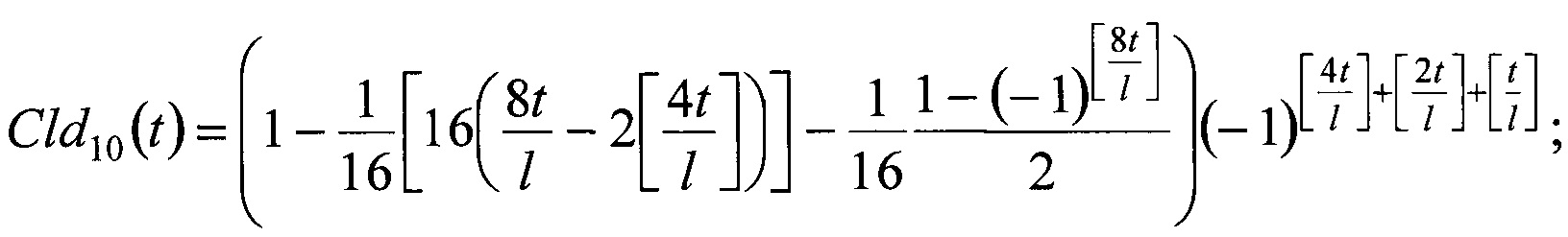

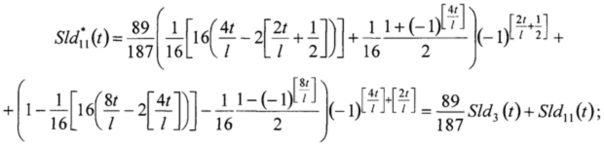

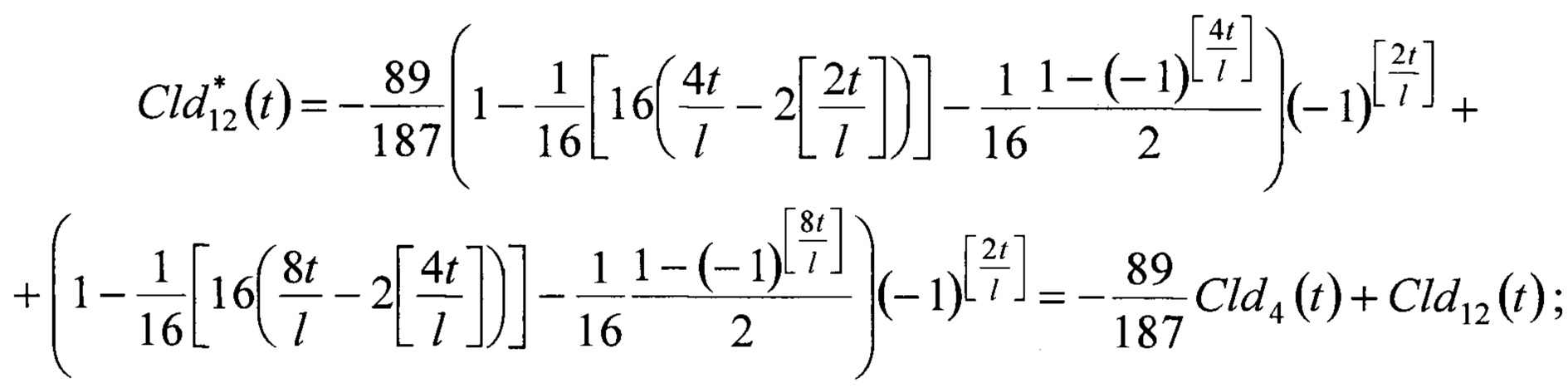

формируют функцию ступенчатых пилообразно изменяющихся коэффициентов деления с числами секвент 5, 6, 7, 9, 10, 11, 12, 13, 14. Полученные функции изменения коэффициентов деления делителей напряжений упорядочивают по возрастанию чисел секвент (9) фиг. 4, приводят к ортогональному виду и тем самым формируют ортогональные ступенчатые пилообразные функции коэффициентов деления резистивных делителей напряжений, изменяющихся во времени в соответствии со следующими равенствами:

где t - время;

l - полупериод преобразования функций Sld1(t);

[…] - операция выделения целой части.

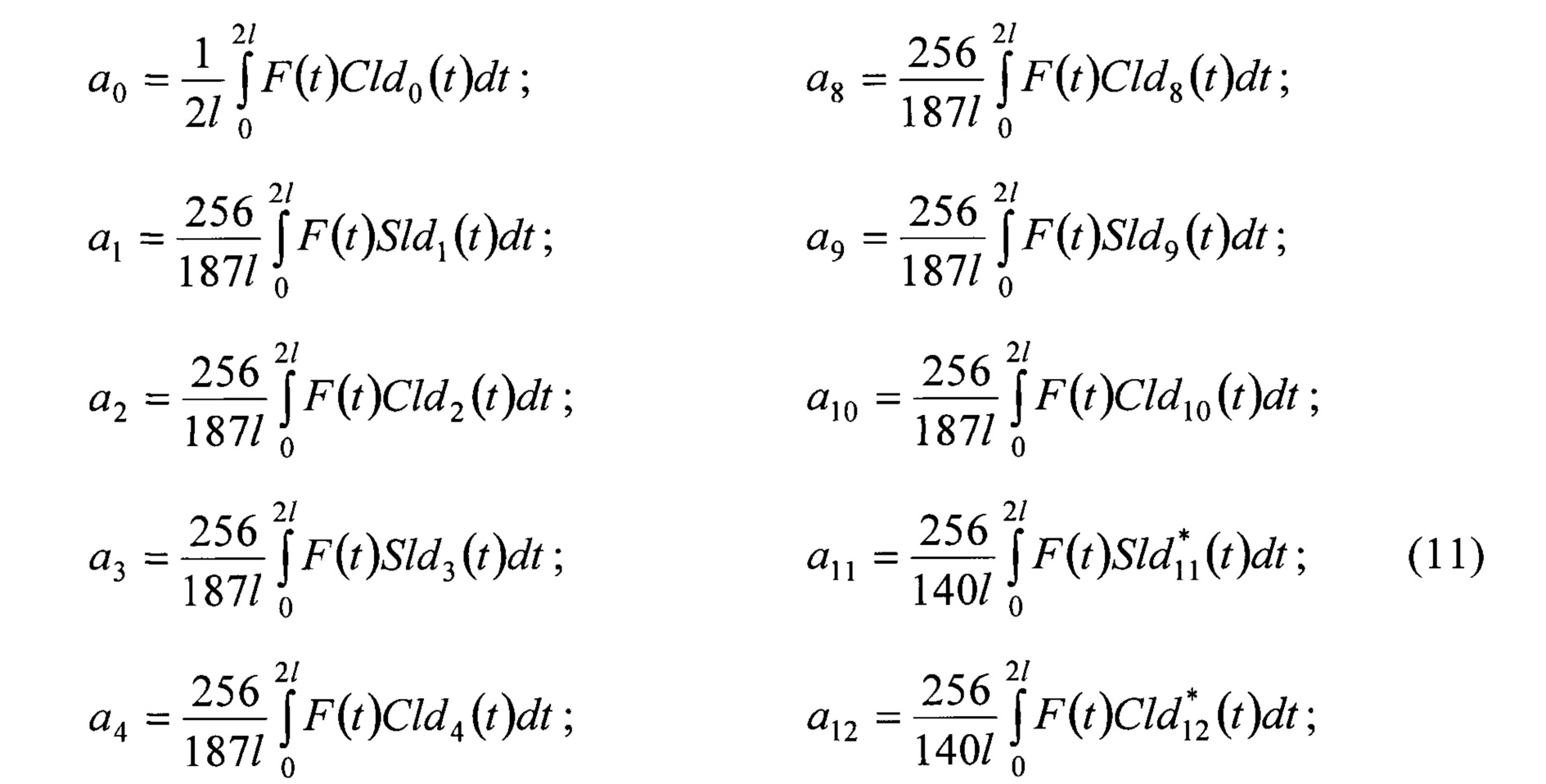

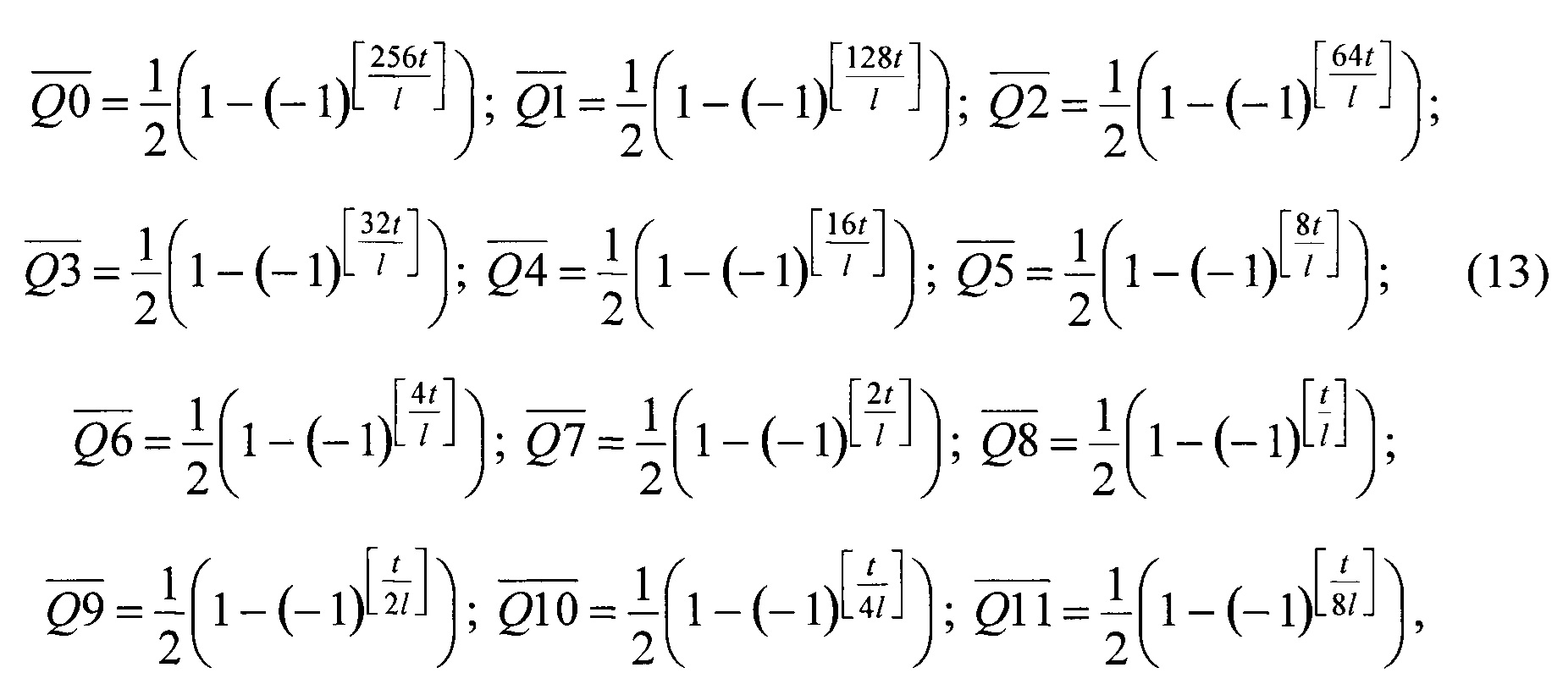

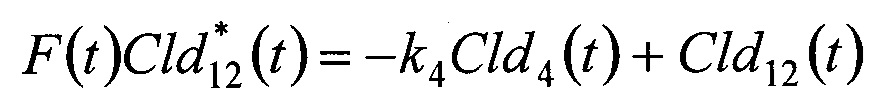

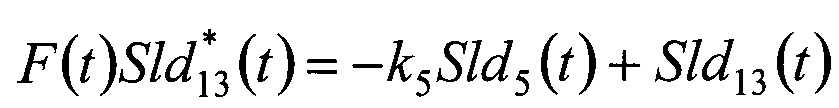

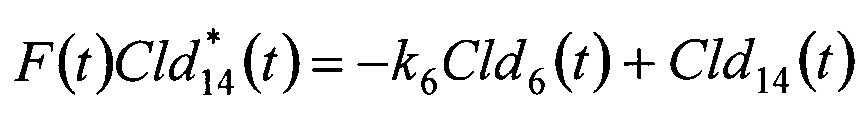

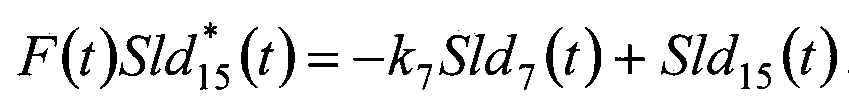

Коэффициенты преобразования при использовании ортогональных ступенчатых пилообразно изменяющихся коэффициентов деления делителей напряжений определяются из следующих равенств:

Сравнивая характер изменений пилообразных функций, используемых в [1] (Приложение 1, фиг. 1), с характером изменения предлагаемых ступенчатых пилообразно изменяющихся коэффициентами деления делителей напряжения фиг. 3, составленных из одинаковых по величине сопротивлений и изготовленных по одной и той же технологии, свидетельствует о том, что по характеру изменения и расположению секвент предлагаемого преобразования полностью совпадают, поэтому способ и устройство преобразования сигналов по пилообразным напряжениям [1] выбраны в качестве прототипа, как наиболее близкие к предлагаемым способу и устройству.

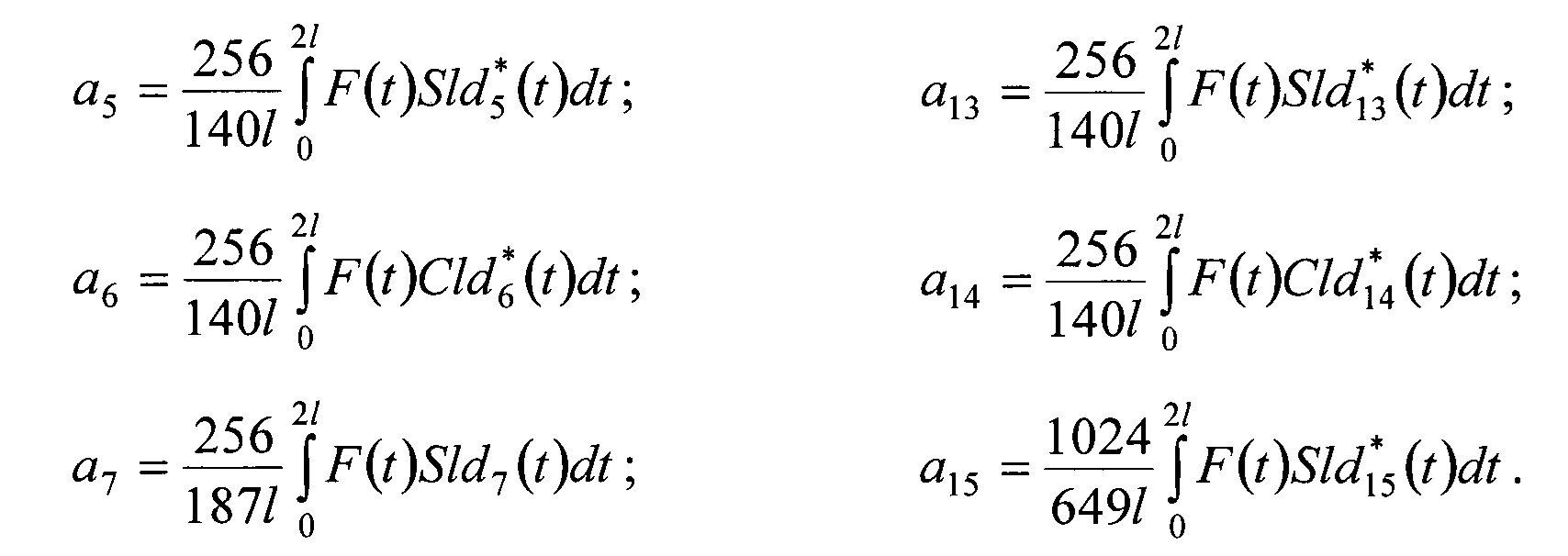

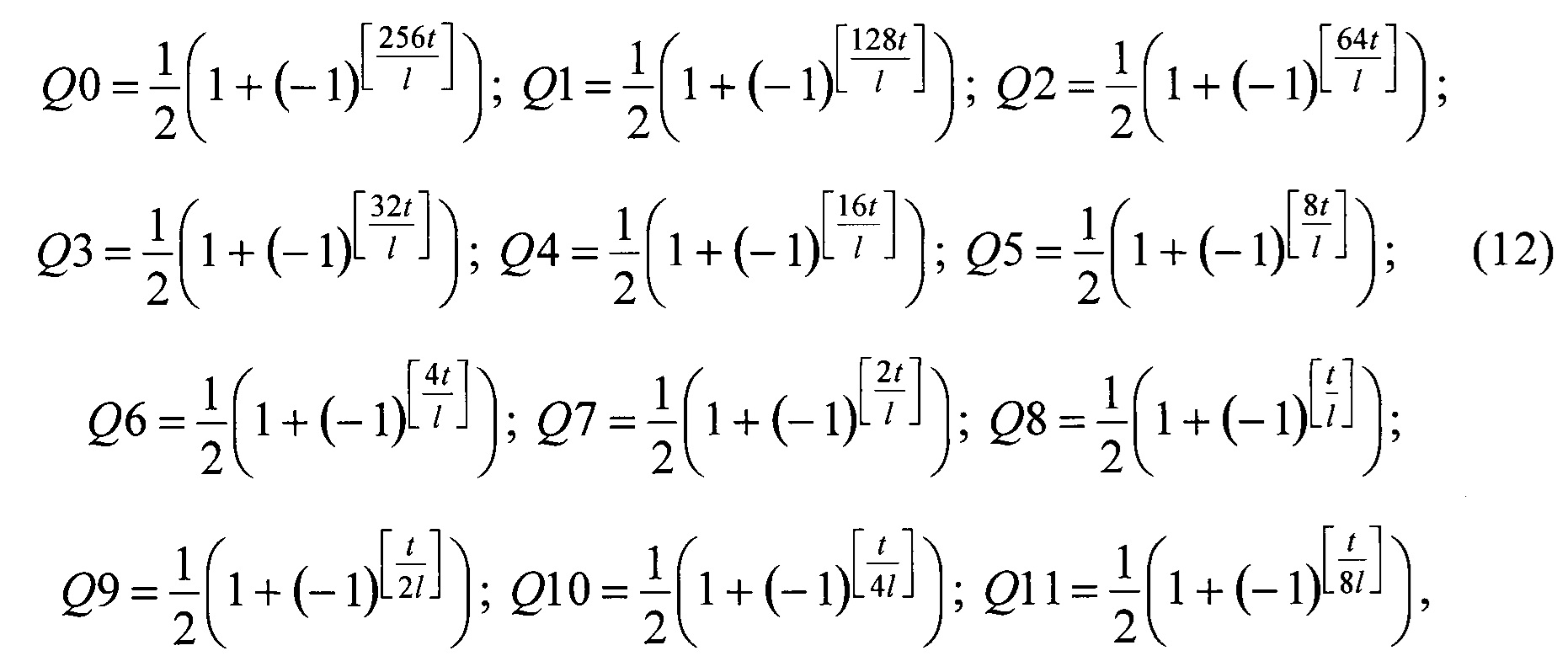

Предлагаемый способ реализуется следующим образом:

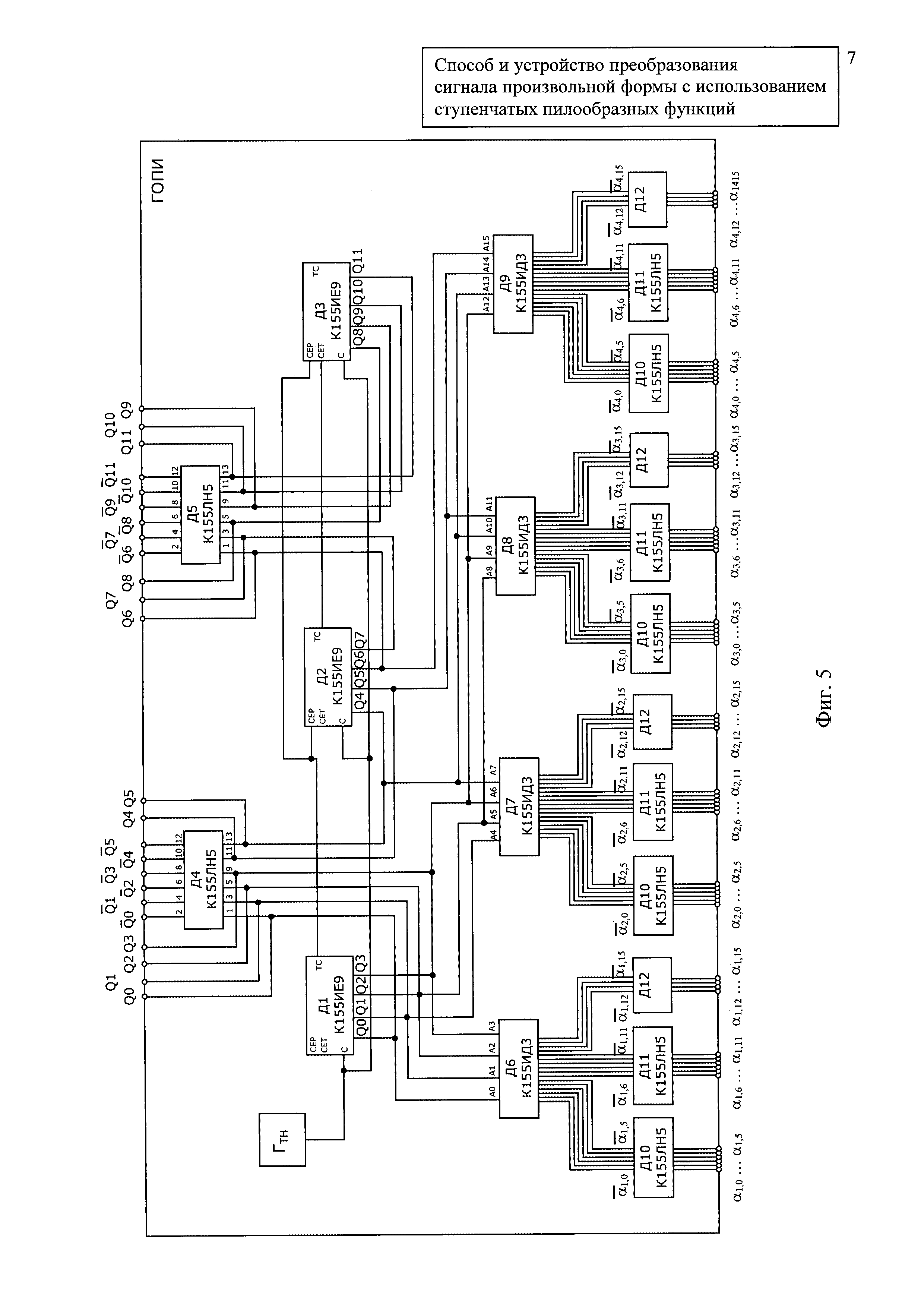

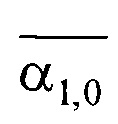

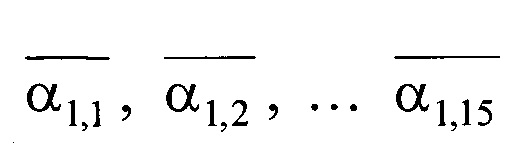

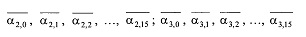

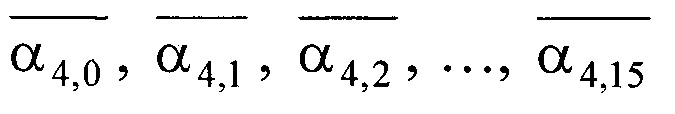

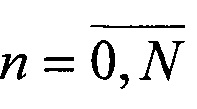

- импульсы генератора однополярных импульсов тактовой частоты FT делят с помощью синхронных счетчиков D1, D2, D3 фиг. 5 типа К155ИЕ9 [9, Приложение 6. Стр. 97, 98];

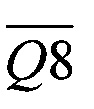

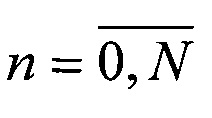

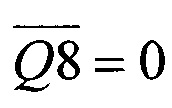

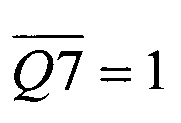

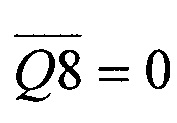

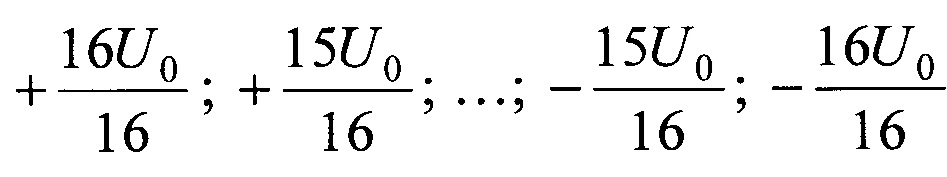

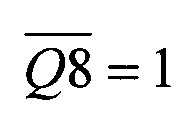

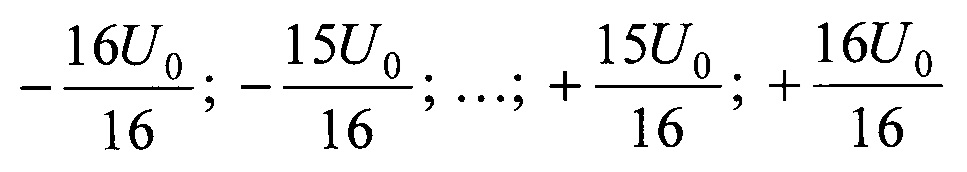

- в результате деления на выходах Q0, Q1,…Q11 формируют однополярные импульсы с частотами кратными двум:

где l - полупериод импульсов Q8;

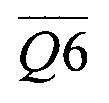

- выходы Q0, Q1, …, Q5 счетчиков D1, D2 соединяют с входами 1, 3, 5, 9, 11, 13 инверторов D4 типа К155ЛН5 фиг. 5, [9] (Приложение 6, Стр. 27), а выходы Q6, Q7, …, Q11 - с входами 1, 3, 5, 9, 11, 13 инверторов D5. На выходах 2, 4, 6, 8, 10, 12 инверторов D4 и D5 получают инверсные прямоугольные импульсы:

где l - полупериод импульсов

- выходы Q0, Q1, Q2, Q3 счетчика D1 соответственно соединяют с входами А0, A1, А2, A3 дешифратора D6 типа К155ИД3 [9] (Приложение 6. Стр. 132, 133, фиг. 5), преобразующие четырехразрядный код, поступающий на входы А0, A1, А2 и A3 в напряжения низкого уровня, появляющегося на одном из шестнадцати выходов (Приложение 6. Стр. 133), а 16 выходов

- выходы счетчиков Q1, Q2, Q3, Q4 соответственно соединяют с входами А4, А5, А6, А7 дешифратора D7; выходы счетчиков Q2, Q3, Q4, Q5 соединяют с входами А8, А9, А10, А11; выходы счетчиков Q3, Q4, Q5, Q6 - с входами А12, А13, А14, А15;

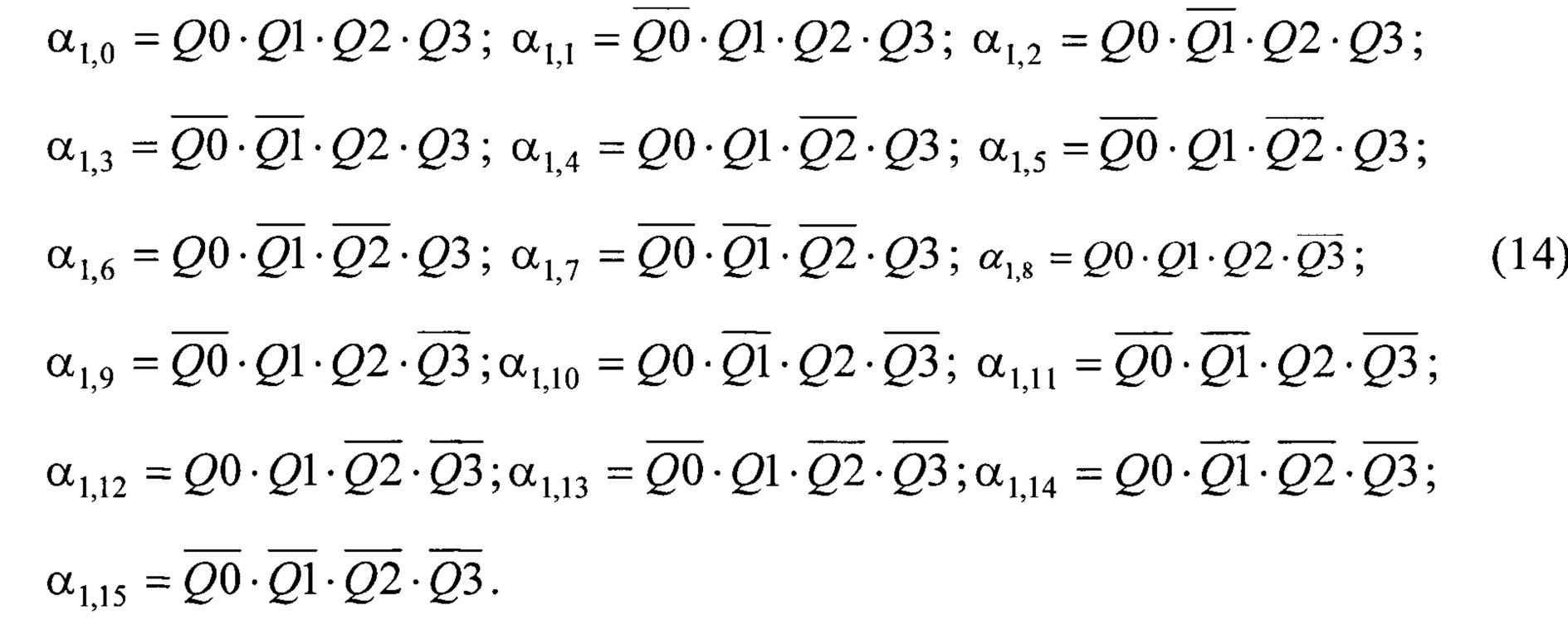

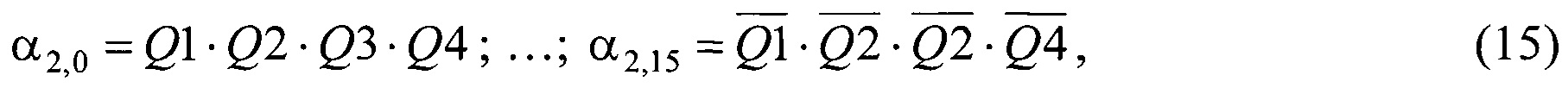

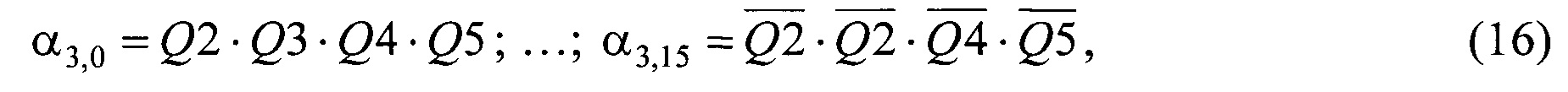

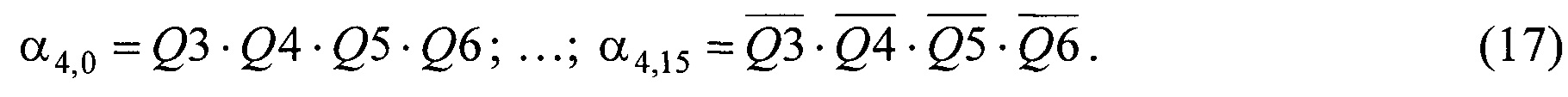

- выходы дешифраторов D7, D8, D9, а именно

Аналогично формируются последовательности α2,0…α2,15, α3,0…α3,15, α4,0…α4,15:

Импульсные последовательности (14), (15), (16), (17) используют для управления ключами резистивных делителей S0-S15 и S0*-S15*, а импульсы Q4-Q9 и

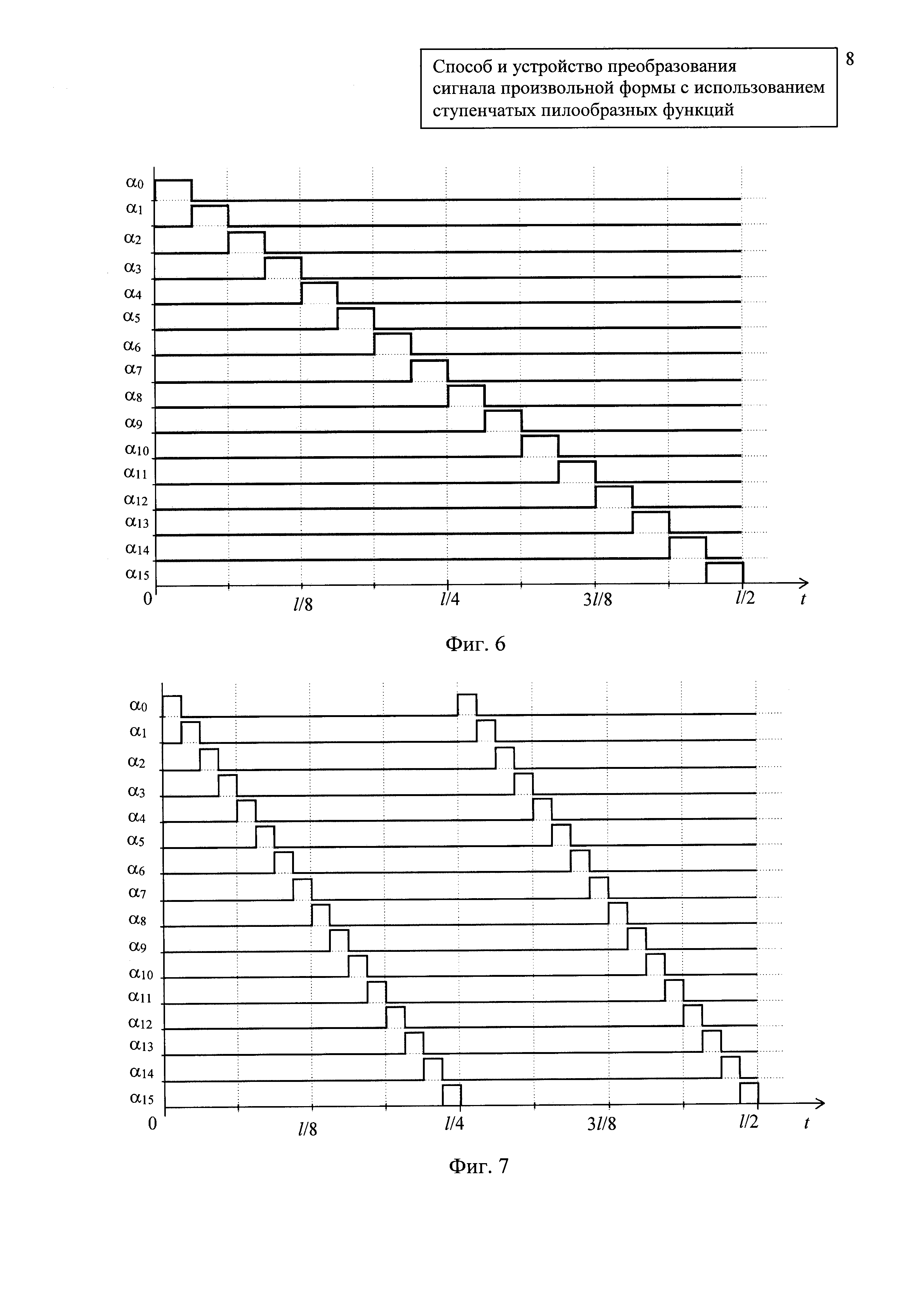

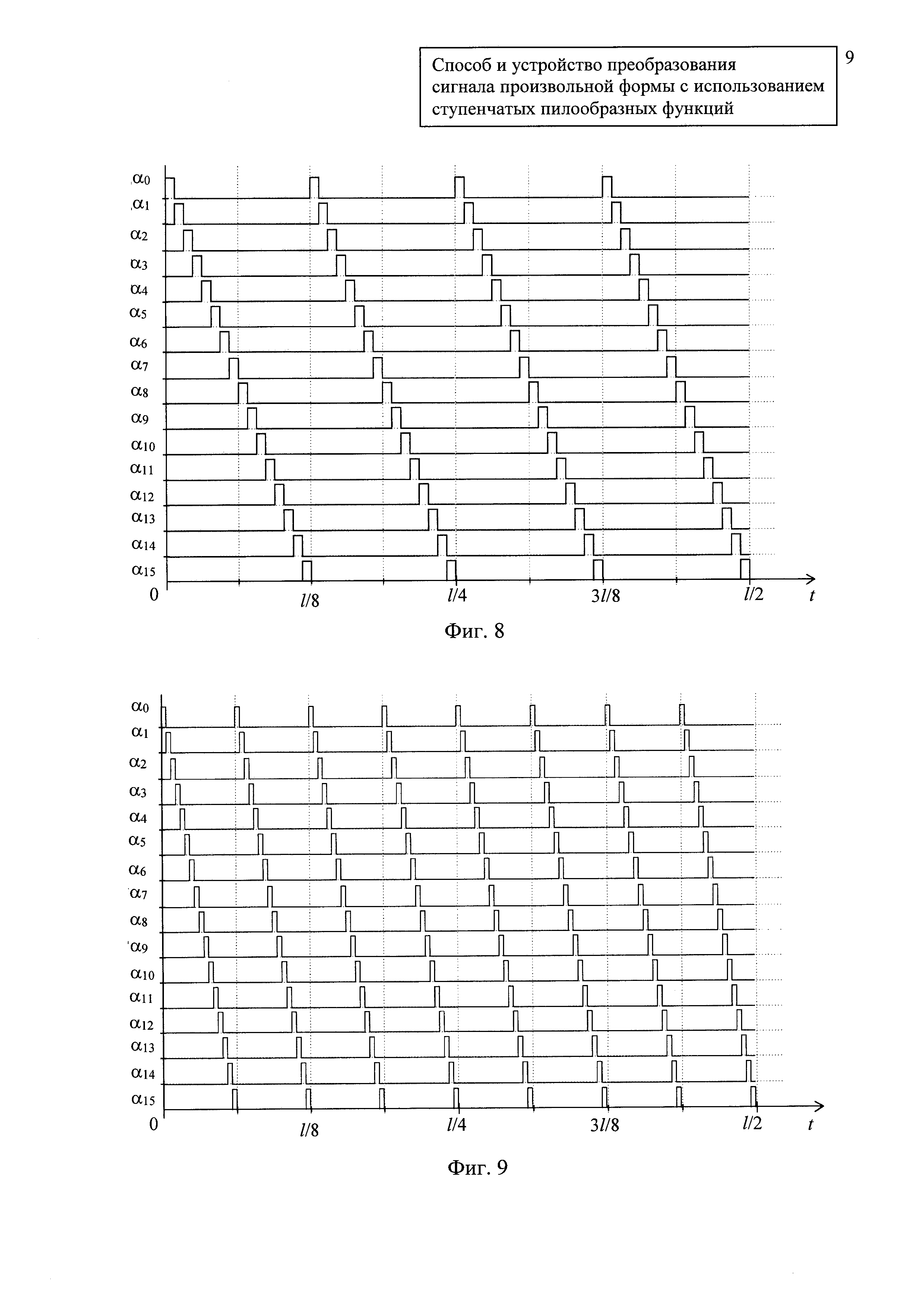

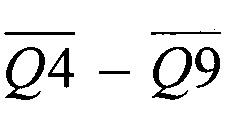

Графики импульсных последовательностей (14)-(17) приведены на фиг. 6, фиг. 7, фиг. 8, фиг. 9.

Схема, приведенная на фиг. 5, представляет собой генератор однополярных импульсов (ГОПИ) (фиг. 6-фиг. 9) в отличие от генератора двуполярных напряжений Уолша, используемого в патенте [1] и [2] (Приложение 3. Стр. 47).

На следующем этапе, используя импульсы ГОПИ и делители напряжения, составленные из одинаковых резисторов, формируют порождающие функции изменений коэффициентов деления делителей напряжений.

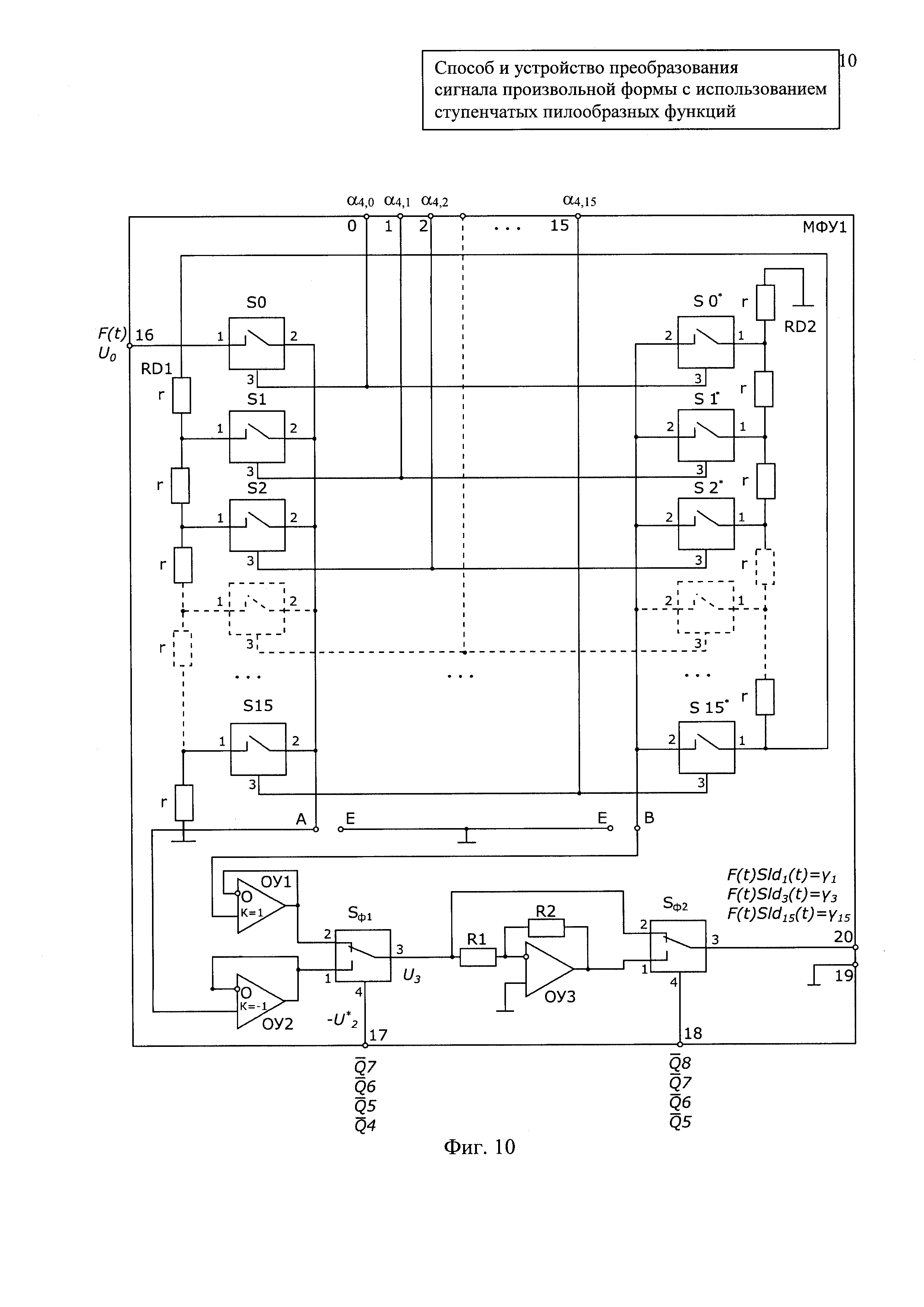

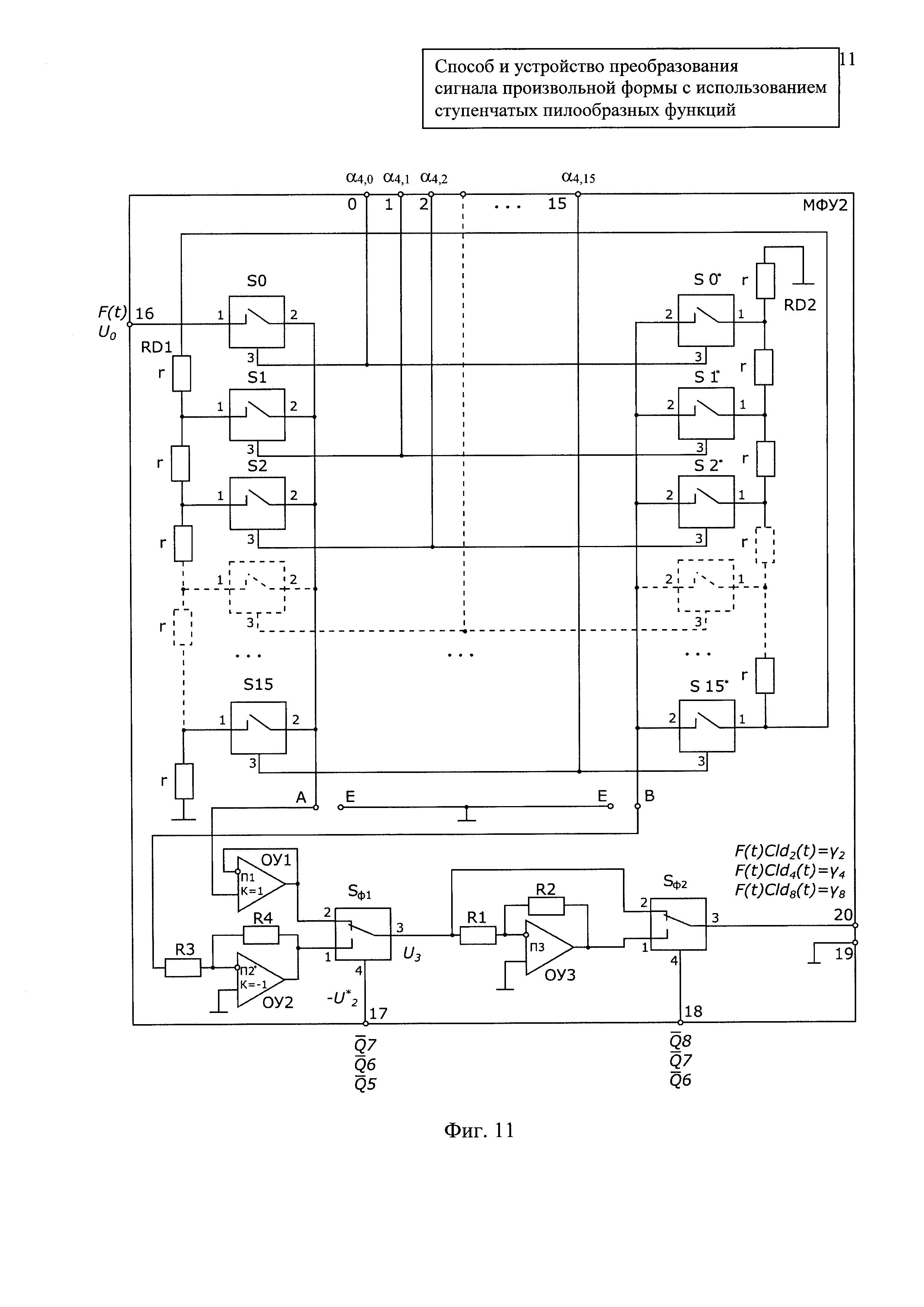

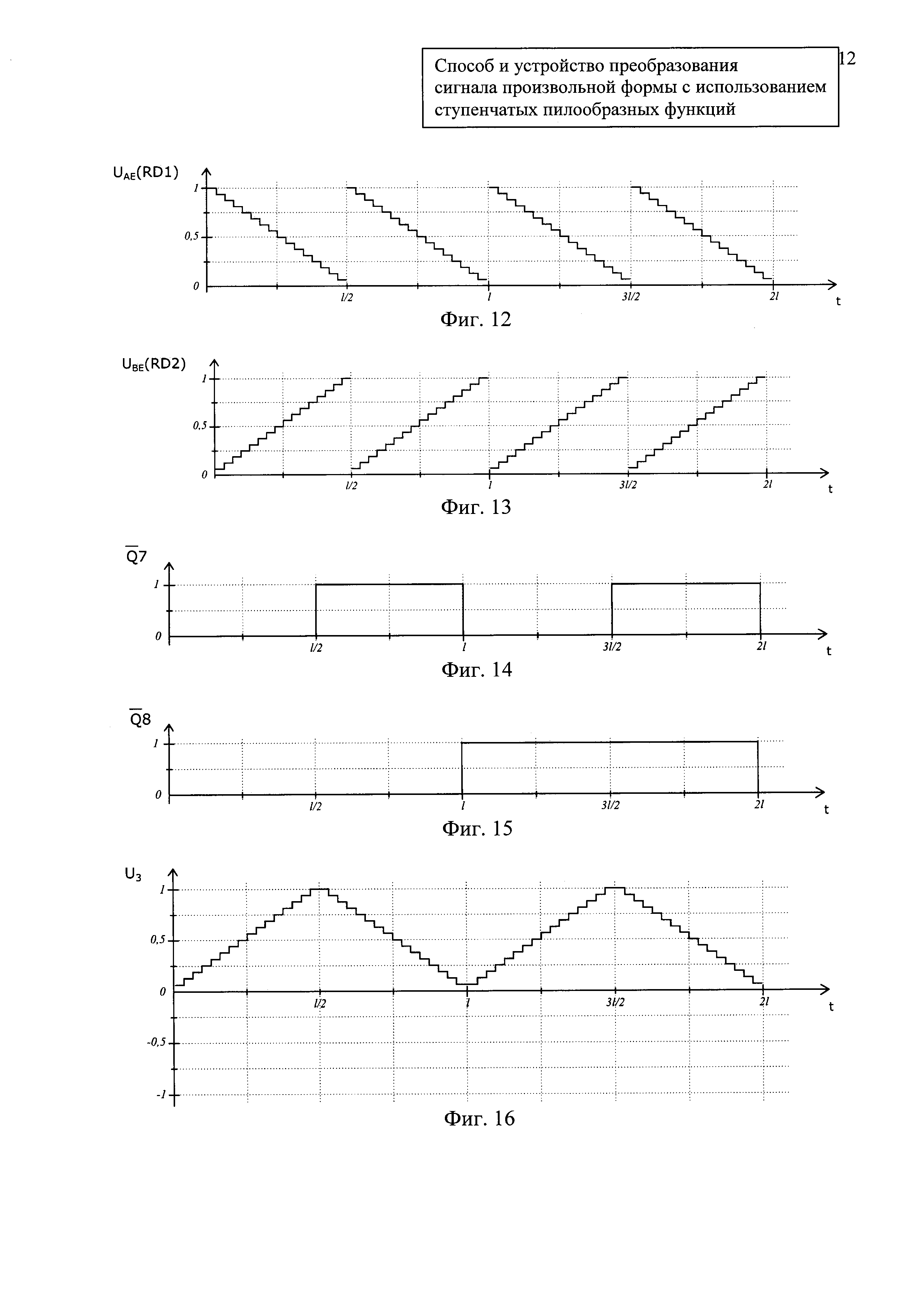

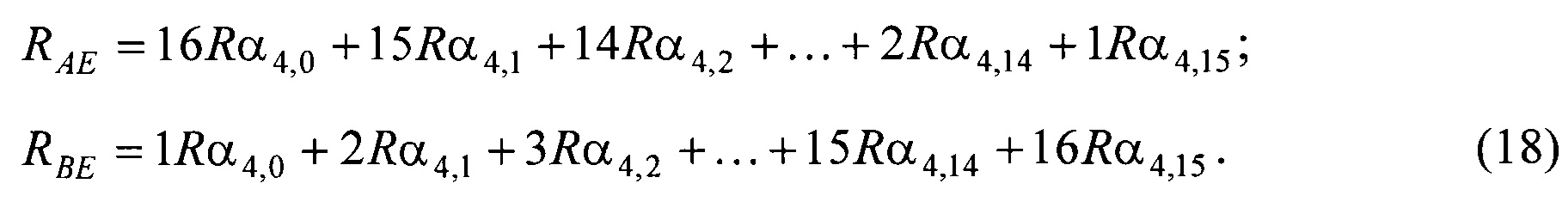

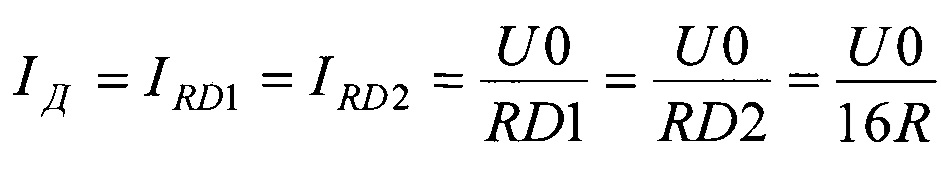

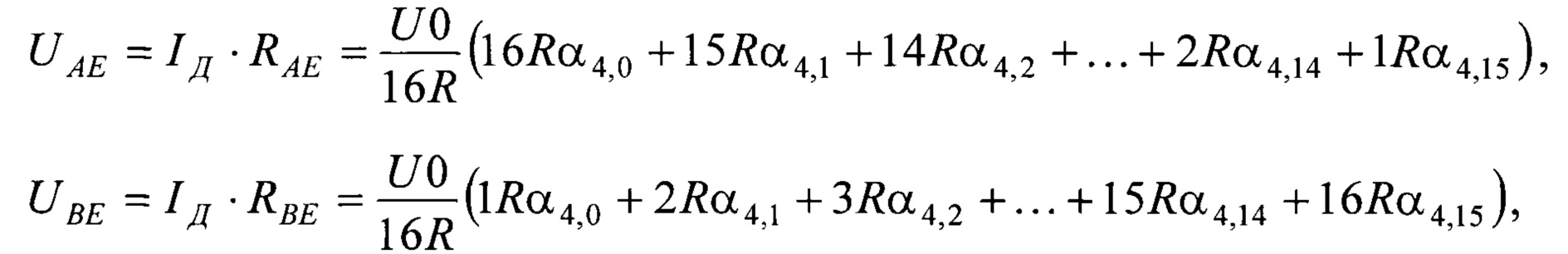

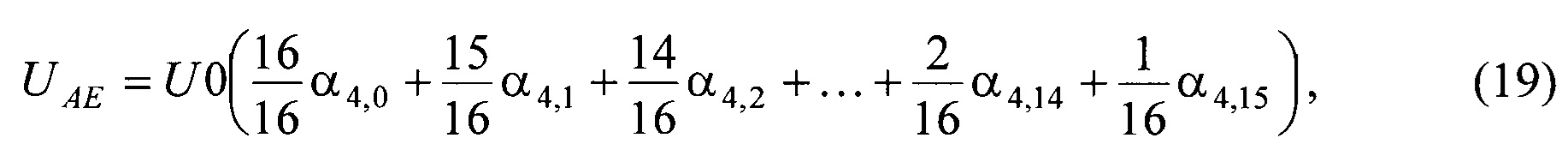

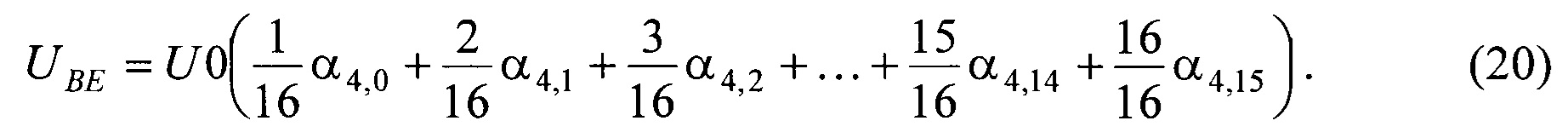

Изменение коэффициентов деления резистивных делителей реализуют схемами, приведенными на фиг. 10 и фиг. 11, которые включают по два резистивных делителя RD1 и RD2, каждый из которых представляет собой 16 последовательно соединенных одинаковых резисторов R. Выходы А и В резистивных делителей RD1 и RD2 коммутируют последовательно во времени контактами 1 и 2 ключей S0-S15 и S0*-S15*. Для этого входы управления 0-15 ключами S0-S15 и S0*-S15* типа КР590КН5 [10] (Приложение 7. Стр. 375) соединяют с выходами α1,0…α1,15 или α2,0…α2,15, α3,0…α3,15 либо α4,0…α4,15 генератора однополярных прямоугольных импульсов ГОПИ. При соединении α4,0…α4,15 ГОПИ с выходами управления 3 электронными ключами от 0 до 15 на выходах делителя RD1 между точками А и Е получают ступенчатое изменение сопротивления во времени от 16R до 1R, а между точками В и Е делителя RD2 - от 1R до 16R (см. фиг. 10, фиг. 11). Графики изменения сопротивлений (напряжений) между точками A, Е и B, Е приведены соответственно на фиг. 12 и фиг. 13.

Формализованное описание изменений сопротивлений делителей RD1 и RD2 между точками A, Е и B, Е с учетом напряжений управления α1,0…α1,15 ключами S0-S15 и S0*-S15* отображают следующими равенствами:

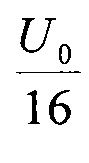

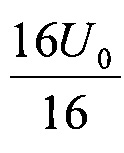

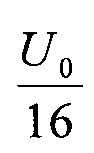

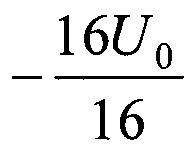

Для формирования изменения коэффициентов деления резистивных делителей в соответствии с порождающими функциями (8) вход 16 модуля формирования умножения (МФУ1) соединяют с источником постоянного напряжения U0 фиг. 10. В результате этого в каждом из делителей RD1 и RD2 протекает ток:

а на выходах делителей после коммутации во времени получают напряжения:

Из (19) и (20) очевидно, что выходные напряжения UАЕ и UВЕ являются произведениями напряжения U0 на коэффициенты деления делителей RD1 и RD2 (фиг. 12 и фиг. 13).

Для формирования однополярных ступенчатых пилообразных напряжений, изменяющихся ступенчато от

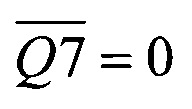

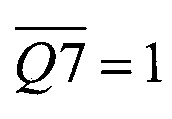

Для формирования двуполярного напряжения, изменяющегося тождественно Sld1(t), используют повторитель на базе операционного усилителя ОУ3 с коэффициентом передачи минус 1 фиг. 10 и ключ SФ2. Контакт 2 ключа SФ2 соединяют с выходом 3 ключа SФ1. Вход 1 ключа SФ2 соединяют с выходом операционного усилителя ОУ3 фиг. 10. Вход 4 управления ключа SФ2 соединяют с выходом

β1(t)=U0Sld1(t).

Далее источник напряжения U0 на входе 16 МФУ1 (см. фиг. 10) заменяют на источник сигнала F(t). На выходе 20 МФУ1 получают напряжение, пропорциональное произведению сигнала F(t) на изменение коэффициентов деления делителей RD1 и RD2

Сравнивая схемы формирования базисных функций (10) фиг. 10 и фиг. 11 со схемами формирования базисных функций в прототипе [1] (Приложения 8. Фиг. 6 и фиг. 8) находим, что схемы фиг. 10 и фиг. 11 в предлагаемом формирователе не содержат интегрирующих и стабилизирующих рабочие напряжения элементов в отличии от схем прототипа [1] (Приложение 7 фиг. 6 и фиг. 8).

Для формирования произведения сигнала F(t) на Sld3(t) и Sld15(t) используют еще два модуля МФУ1.

Для формирования произведения

входы МФУ1 0, 1, 2, …15 соответственно соединяют с выходами α3,0…α3,15 ГОПИ, вход 16 соединяют с выходом источника сигнала F(t), а входы 17 и 18 МФУ1 соединяют с выходами

Для формирования произведения

входы МФУ1 0, 1, 2,…, 15 соответственно соединяют с выходами α1,0…α1,15 ГОПИ, вход 16 соединяют с выходом источника сигнала F(t), а входы 17 и 18 МФУ 1 соединяют с выходами

Для формирования произведения сигнала F(t) на изменяющиеся коэффициенты делителей Cld2(t), Cld4(t), Cld8(t) используют модули МФУ2, схема которого приведена на фиг. 11. В состав каждой схемы входят также два резистивных делителя RD1 и RD2 и ключи S0-S15 и S0*-S15*, повторители П1 и П2* на операционных усилителях ОУ1, ОУ2 и ОУ3, ключи SФ1, SФ2 как и в схеме МФУ1 фиг. 10. Схема МФУ2 отличается от схемы МФУ1 тем, что вместо повторителя П2 фиг. 10 с коэффициентом передачи +1 используют повторитель П2* с коэффициентом передачи -1. Кроме этого выходы делителей A и Б соединены в соответствие со схемой фиг. 11.

Для формирования произведений сигнала F(t) на изменяющиеся коэффициенты деления делителей

входы 0, 1, 2, …, 15 МФУ2 соединяют соответственно с выходами α4,0…α4,15 ГОПИ, вход 16 МФУ2 соединяют с выходом источника U0, а входы 17 и 18 соответственно соединяют с выходами

При

При

Таким образом, на всей временной оси на выходе 20 МФУ2 формируют ступенчатое напряжение

Далее вместо напряжения U0 на вход 16 МФУ2 подают напряжение сигнала F(t), в результате чего на выходе 20 МФУ2 получают произведение сигнала на изменение коэффициентов деления делителей RD1 и RD2 (20).

Для формирования произведений сигнала F(t) на изменяющиеся коэффициенты деления делителей

используют два модуля МФУ2, входы 16 которых соединяют с выходом источника сигнала F(t). Входы 0, 1, 2, 15 одного из модулей МФУ2 соединяют соответственно с выходами α3,0…α3,15 ГОПИ, а входы 17 и 18 соединяют с выходами

Для формирования F(t)Cld8(t) входы 0, 1, 2, 15 второго модуля МФУ2 соединяют с выходами α2,0…α2,15 ГОПИ, а входы 17 и 18 соединяют с выходами

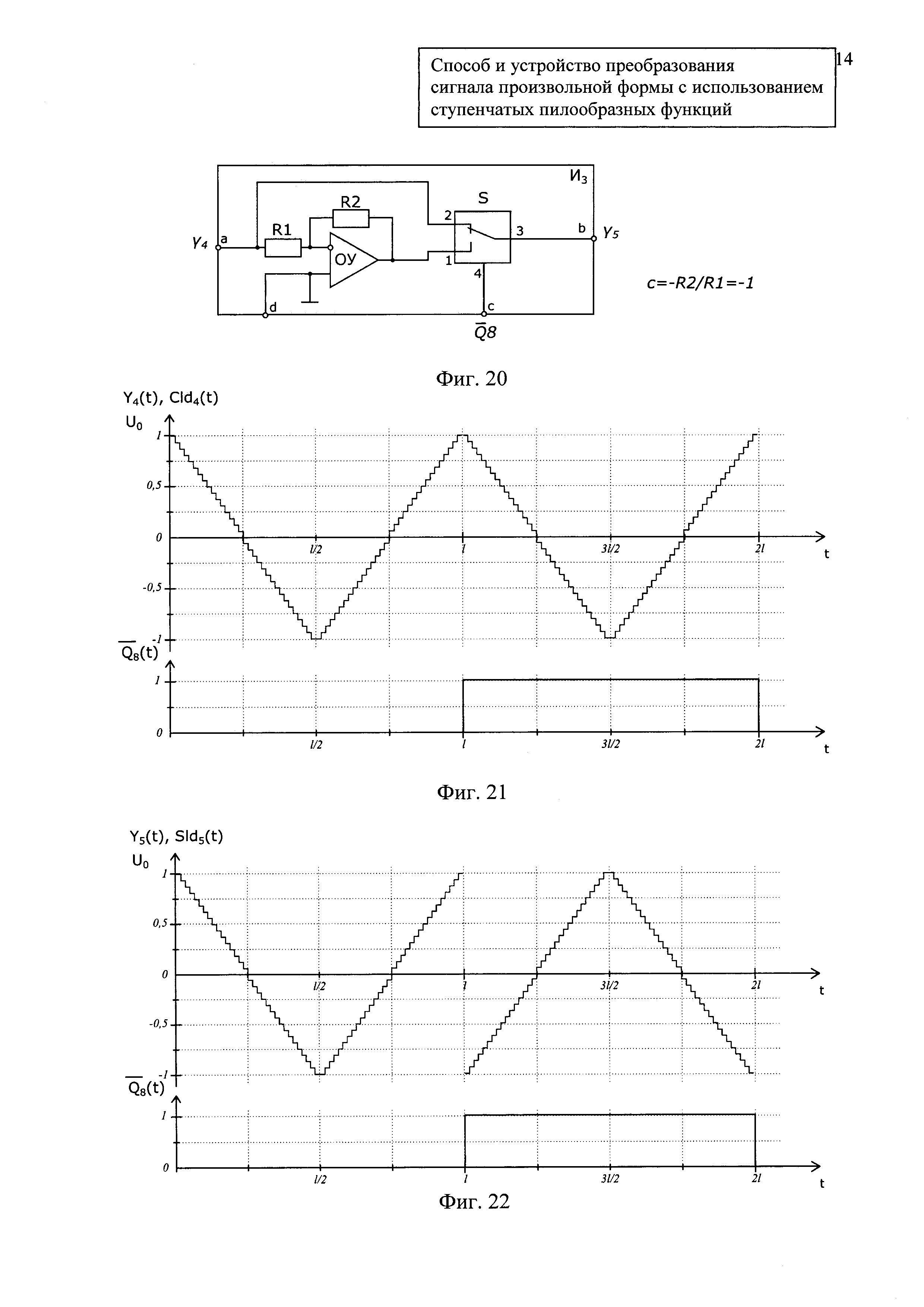

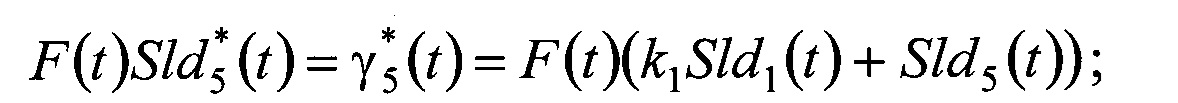

Для формирования произведений сигнала F(t) на Sld5(t), Cld6(t), Sld7(t), Cld10(t), Sld11(t), Cld12(t), Sld13(t), Cld14(t) используют схему И3 изменения знака напряжения сигнала на коэффициенты делителях RD1 и RD2, приведенную на фиг. 20, и модули МФУ1 или МФУ2 фиг. 10, фиг. 11. Схема И3 фиг. 20 состоит из повторителя на операционном усилителе с коэффициентом передачи -1, входа которого соединяют с контактом 2 ключа S, а выход повторителя соединяют с контактом 1 ключа S. Выход 3 ключа S соединяют с выходом в схемы И3. Вход управления 4 ключа S соединяют с одним из выходов Q4-Q8 ГОПИ. Схема работает следующим образом: при подаче на вход а схемы И3 напряжения γ4(t)=U0Cld4(t), а на вход управления С напряжения

График напряжения фиг. 22 на выходе в схемы И3 приведен для случая, когда F(t)=U0=const. Из графика очевидно, что на выходе в схемы И3 формирует напряжение

При изменяющемся во времени сигнале F(t) схема И3 формирует напряжение

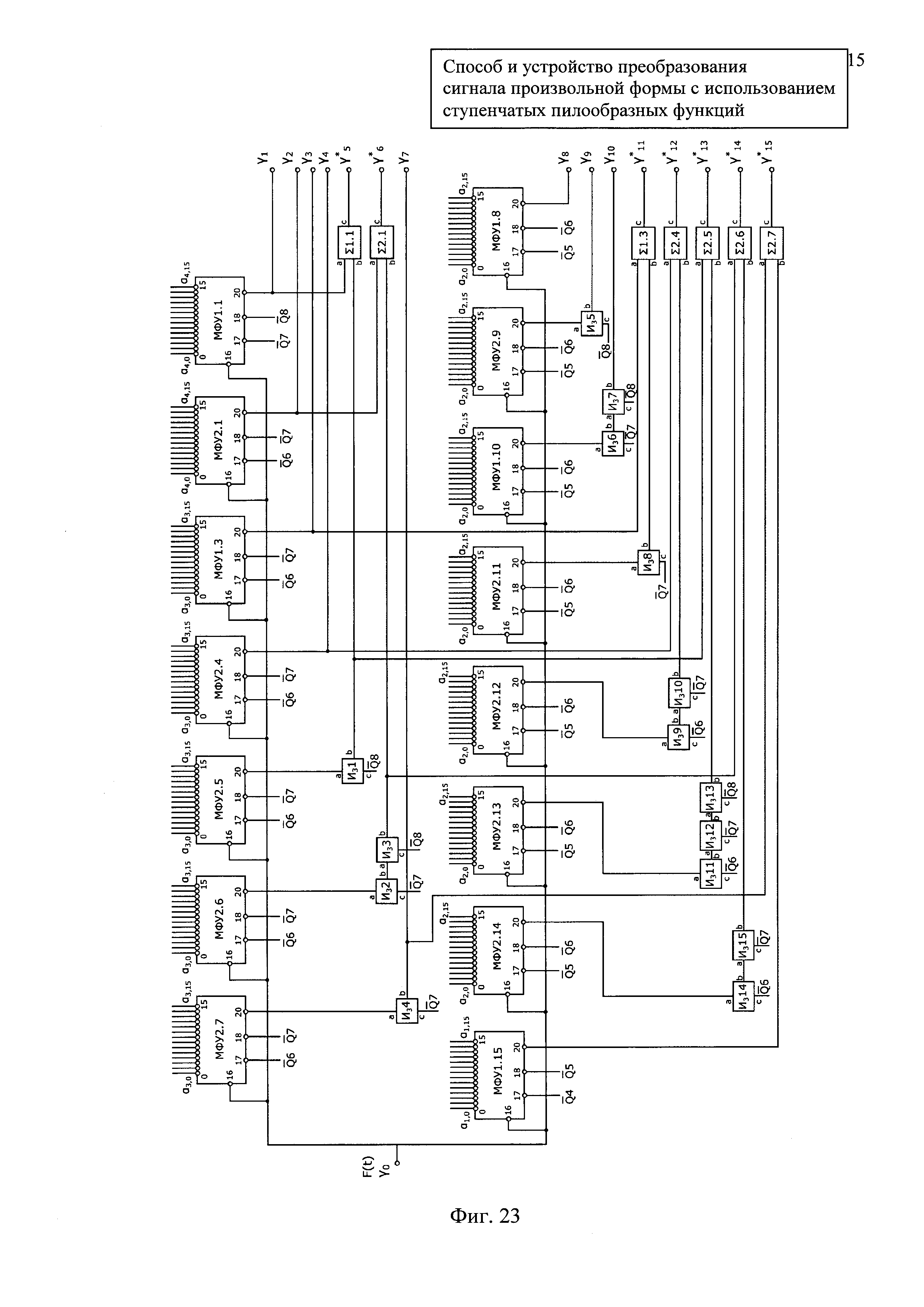

На фиг. 23 приведена схема блока умножения сигнала и коэффициентов деления делителей (БУСКДД) напряжений для всех функций (10).

На фиг. 23 приведены соединения модуля МФУ2.5 и схемы И31 для реализации (28).

Для формирования произведений

используют еще два модуля МФУ2.6 и МФУ2.7, входы 0, 1, 2, 15 которых соединяют соответственно с выходами α3,0…α3,15 ГОПИ. Входы 17 соединяют параллельно с выходом

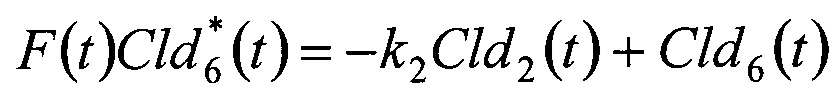

Для формирования напряжения γ6(t)=F(t)Cld6(t) выход 20 МФУ2.6 соединяют с входом а схемы И32 фиг. 23; вход с схемы И32 соединяют с выходом

Для формирования напряжения γ7(t)=F(t)Sld7(t) выход 20 МФУ2.7 соединяют с входом а схемы И34 фиг. 23; вход с И34 соединяют с выходом

Для формирования произведений сигнала F(t) на изменения коэффициентов деления γ9(t)-γ14(t) используют модули МФУ2.9-МФУ2.14, входы 0, 1, 2, 15 которых соединяют соответственно с выходами α2,0…α2,15 ГОПИ фиг. 23, входы 16 соединяют с выходом источника сигнала F(t). На выходах 20 этих модулей формируют γ8(t)=F(t)Cld8(t). Вход управления с схемы И35 соединяют с выходом

Для формирования напряжения γ10(t)=F(t)Cld10(t) выход 20 МФУ2.10 соединяют с входом а двух последовательно соединенных схем И36 и И37; вход с И36 соединяют с выходом

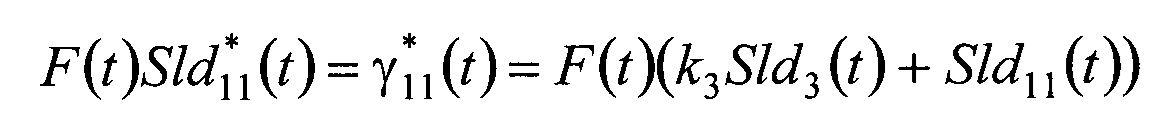

Для формирования напряжения γ11(t)=F(t)Sld11(t) выход 20 МФУ2.11 соединяют с входом а схемы И38; вход с И38 соединяют с выходом

Для формирования напряжения γ12(t)=F(t)Cld12(t) выход 20 МФУ2.12 соединяют с входом а схемы И39, выход в которой соединяют с входом а схемы И310; вход с схемы И39 соединяют с выходом

Для формирования напряжения γ13(t)=F(t)Sld13(t) выход 20 МФУ2.13 соединяют с входом а трех последовательно соединенных схем И311, И312, И313; входы управления с схем И311, И312, И313 соответственно соединяют с выходами

Для формирования напряжения γ14(t)=F(t)Cld14(t) выход 20 МФУ2.14 соединяют с входом а схемы И314, выход в которой соединяют с входом а схемы И315; вход с схемы И314 соединяют с выходом

В результате этих операций на выходах 20 схем МФУ1.1, МФУ1.3, МФУ1.15, МФУ2.2, МФУ2.4, МФУ2.8 и выходах в схем И31, И33, И34, И35, И37, И38, И310, И313, И315 получают все 15 произведений сигнала на функции изменений коэффициентов деления резистивных делителей RD1 и RD2.

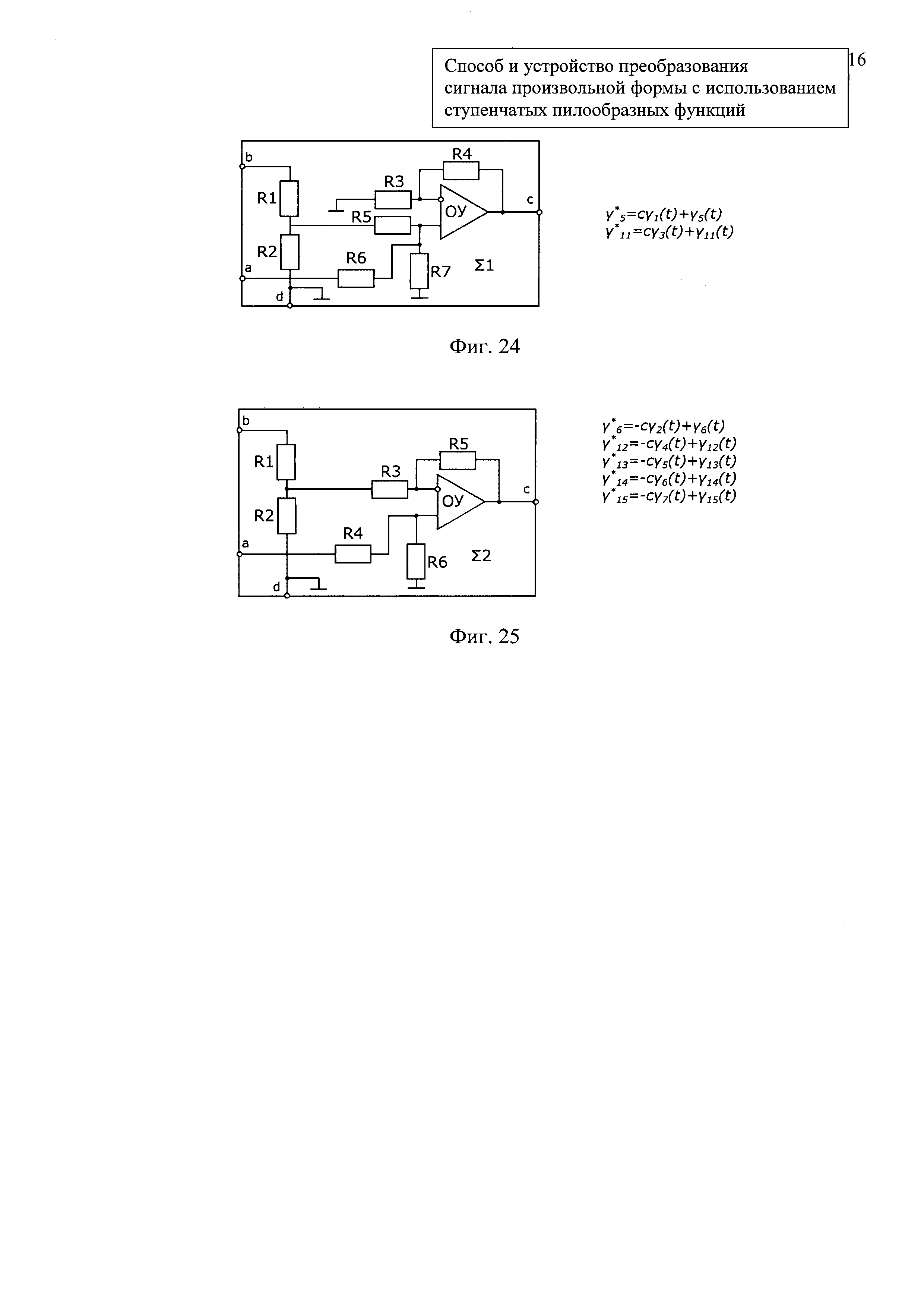

На этапе приведения произведений сигнала F(t) на ортогональные функции изменений коэффициентов деления делителей (10) используют сумматоры на операционных усилителях фиг. 24, 25.

Для формирования сумм произведений

используют две схемы сумматора типа Σ1 фиг. 24. Вход а Σ1.1 (фиг. 23) соединяют с выходом 20 МФУ 1.1, а вход в сумматора Σ1.1 соединяют с выходом в схемы И31. На выходе с сумматора Σ1.1 получают

Для формирования разностей произведений

используют схемы сумматоров Σ2 фиг. 25.

Входы а сумматоров Σ2.1 и Σ2.4 соединяют соответственно с выходами 20 МФУ2.1 и МФУ2.4. Входы в сумматоров Σ2.1 и Σ2.4 соответственно соединяют с выходами в схем И33 и И310 на выходах с Σ2.1 и Σ2.4 формируют

Вход а сумматора Σ2.5 соединяют с выходом с И31, а вход в сумматора Σ2.5 соединяют с выходом в схемы И313. На выходе с схемы Σ2.5 формируют

Вход а сумматор Σ2.7 соединяют с выходом в схемы И34, а вход в схемы Σ2.7 соединяют с выходом 20 схемы МФУ1.15. На выходе с сумматора Σ2.7 формируют

В результате выполненных операций на выходах γ0(t), γ1(t), γ2(t), γ3(t), γ4(t),

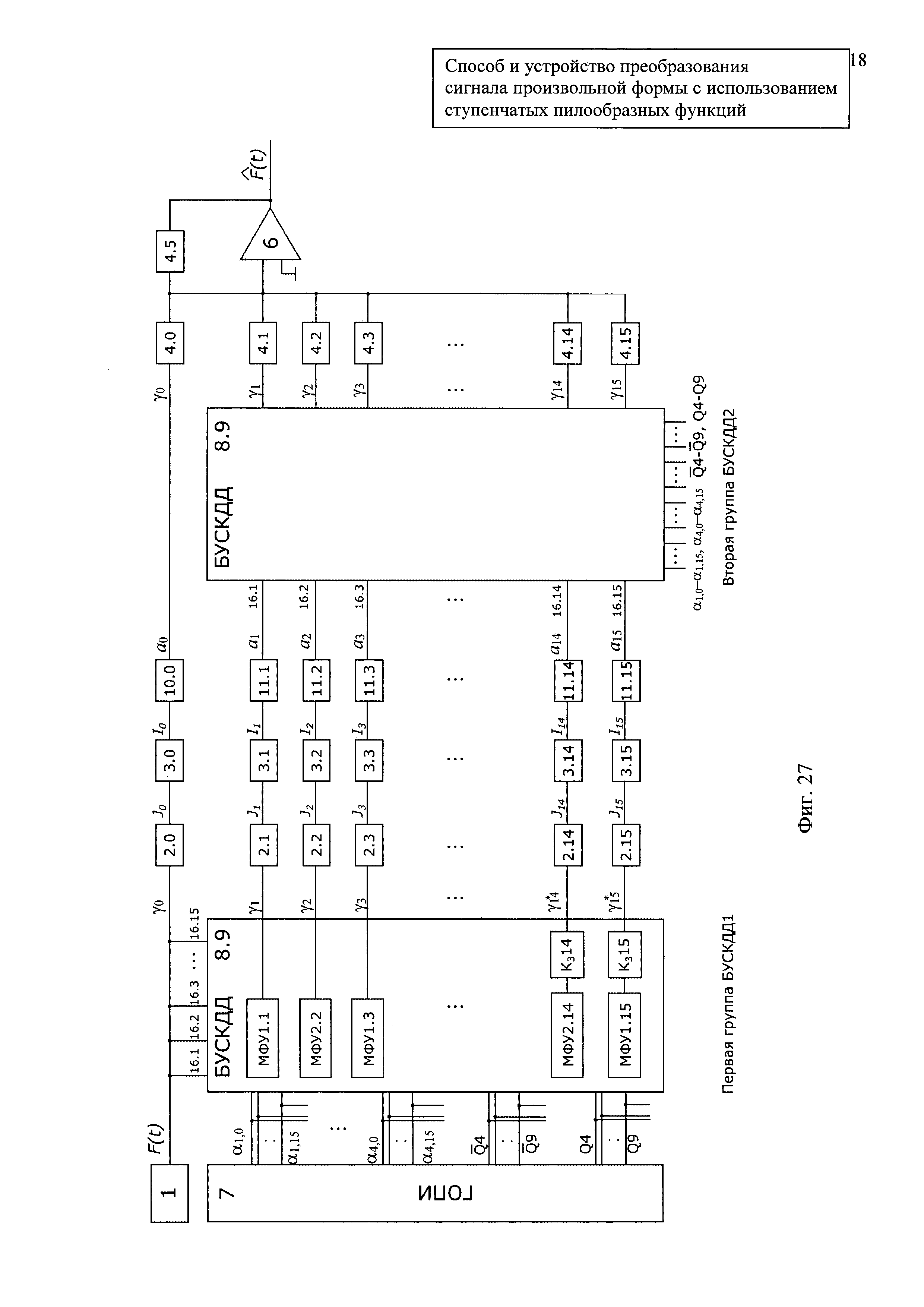

На следующем этапе выполняют интегрирование полученных напряжений γ(t) фиг. 27 с помощью интеграторов 2.0-2.15 и схем отсчитывания и запоминания 3.0-3.16, используемых в [1] и [9] (Приложение 9. Стр. 161, 162). Затем с учетом коэффициентов, стоящих перед интегралами, в соответствии с (11) вычисляют коэффициенты разложения a0-а15 по ступенчатым пилообразным функциям (10).

При обратном преобразовании используют ГОПИ и БУСКДД (фиг. 27). Входы 16 модулей МФУ1 и МФУ2 БУСКДД2, в соответствии с нумерацией после точки, от 1 до 15 соединяют с выходами а1-а15 схем вычисления коэффициентов, на выходах которых эти коэффициенты представлены в виде напряжений. Второй блок БУСКДД2 на выходах

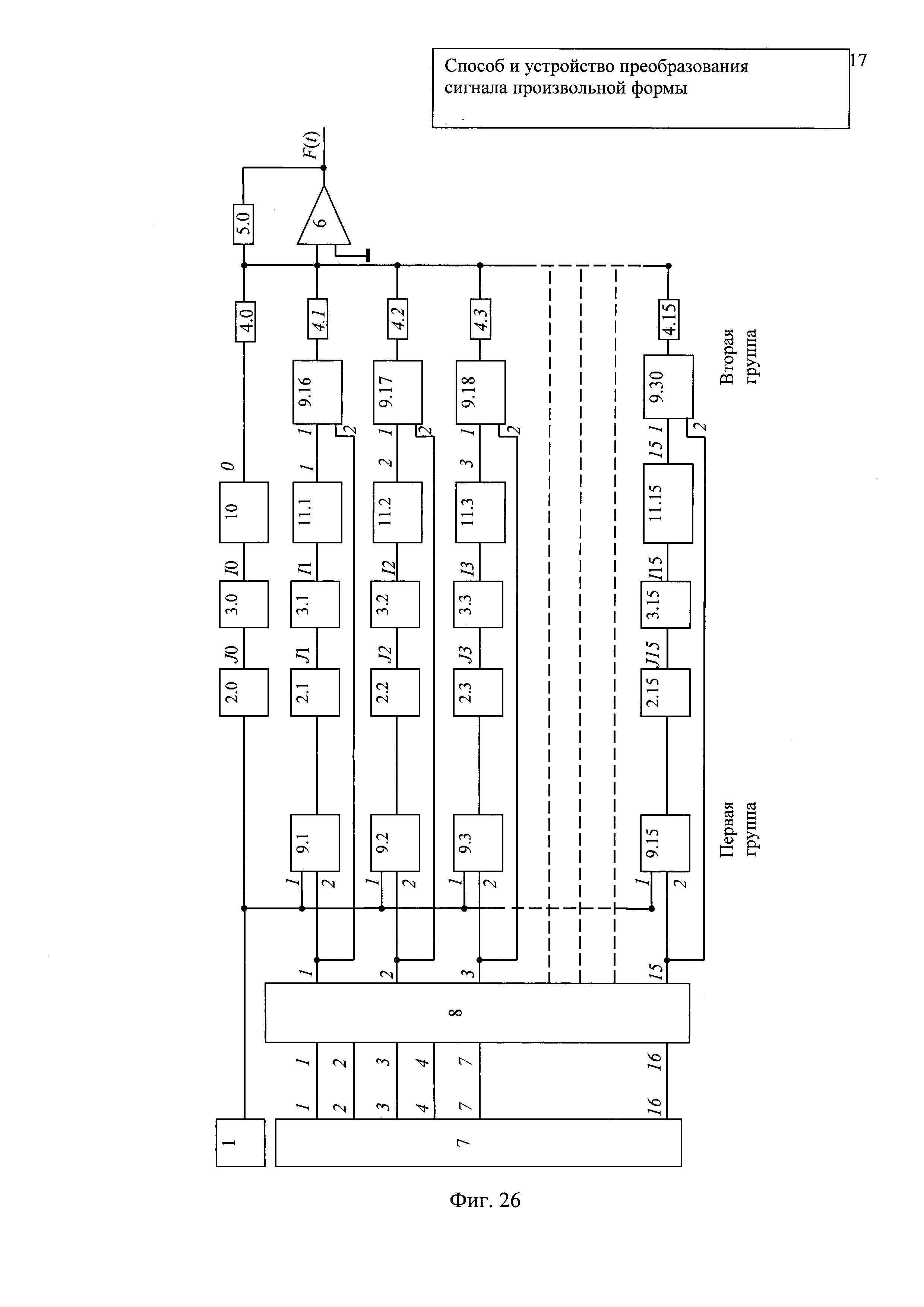

Сравнивая сущность операций преобразования с использованием пилообразных напряжений [1] фиг. 26 с сущностью операций преобразования с использованием ортогональных ступенчатых пилообразно изменяющихся коэффициентов деления резистивных делителей находим:

- что при прямом преобразовании в предлагаемом способе и устройстве формирование (генерация) ступенчатых пилообразно изменяющихся коэффициентов деления резистивных делителей коренным образом отличаются от генерации пилообразных напряжений и обладает более высокой точностью формирования базисных ортогональных функций (10), так как резисторы делителей изготовляются гораздо точнее, чем конденсаторы в интеграторах [1]; кроме этого величины резисторов делителей напряжений при малых токах практически не зависят от температуры;

- в способе, основанном на применении пилообразных напряжений, на этапе формирования ортогонального базиса (Приложение 8) используют интеграторы на операционных усилителях, в обратной связи которых устанавливают конденсаторы, которые обладают достаточно большими погрешностями Приложение 4;

- умножение напряжения сигнала F(t) на коэффициенты деления резистивных делителей RD1 и RD2 не требует применения аналоговых схем на операционных усилителях в режимах с большими коэффициентами усиления, к тому же в предлагаемом способе и устройстве совмещены операция умножения сигнала и формирование базисных функций [10]. На этапе умножения напряжения сигнала F(t) на базисные пилообразные напряжения в [1] используются аналоговые умножители типа AD539, которые также построены на основе операционных усилителей;

- интегрирование и отсчитывание произведений напряжения сигнала F(t) на пилообразные напряжения и на коэффициенты деления резистивных делителей совпадают, за исключением того, что в схемах 10, 11-11, 15 [Приложение 5, фиг. 5, модули М01-M15] для вычисления коэффициентов преобразования устанавливаются другие номиналы резисторов делителей в соответствии с коэффициентами (11);

- для восстановления сигнала в способе и устройстве [1] используют также пилообразные напряжения, формируемые интеграторами на операционных делителях, обладающими такими же недостатками;

- при обратном преобразовании в предлагаемом устройстве вместо схем умножения на базе умножители AD539 используют схемы формирования изменений ступенчатых пилообразно изменяющихся коэффициентов резистивных делителей, объединенных в блок БУСКДД2 фиг. 27, как и при прямом преобразовании;, погрешность которых гораздо меньше интегратора и определяется точностью изготовления резисторов делителей;

- на этапе восстановления сигнала - суммирования произведений коэффициентов а0-а15 преобразования, представленных в виде напряжений, на базисные ступенчатые функции (10), используются идентичные схемы суммирования 6 прототипа [1] и [2] (Приложение 10, фиг. 5), отличающиеся в схемах только номиналами резисторов в сумматора 6 и устанавливаются в соответствии с (11).

Из сравнения одноименных операций преобразования с использованием пилообразных напряжений и преобразования с использованием ступенчатых пилообразно изменяющихся коэффициентов деления делителей напряжений следует, что преобразования отличаются операциями формирования базисных функций и операциями умножения напряжения сигнала на базисные функции, как при прямом так и обратном преобразованиях.

В предлагаемых способе и устройстве с использованием ступенчатых пилообразно изменяющихся коэффициентов деления делителей напряжений последовательность выполнения операций аналогична последовательности операций в устройстве преобразования [1], поэтому устройство, представленное в [1], наиболее близко к предлагаемому устройству, и поэтому выбрано в качестве прототипа.

Устройство прототипа, реализующее преобразование сигнала по пилообразным напряжениям, представлено в виде секвентного фильтра, который в равной мере используется как в преобразователях сигналов (вокодерах), так и в секвентных фильтрах (см. [1, 2]). Секвентный фильтр общего вида согласно [2] представлен схемой, приведенной в Приложении 9, фиг. 2.1.3-8, а секвентный фильтр, используемый в [1], в Приложении 10, фиг. 5.

Для выполнения преобразования с использованием ступенчатых пилообразно изменяющихся коэффициентов деления делителей блок 8 и схемы умножения 9.1-9.30 заменяют на блок умножения ступенчатых пилообразно изменяющихся коэффициентов деления делителей БУСКДД фиг. 26, в котором операции формирования ступенчатых напряжений совмещены с операцией умножения этих напряжений на входной сигнал. На выходах БУСКДД2

Блоки интеграторов 2.0-2.15 и блоки отсчитывания и запоминания 3.0-3.15 в предлагаемом устройстве используют без изменений.

В блоках 4.0-4.15; 5 и 6 изменены номиналы резисторов сумматора R/k(0)-R/k(s), R в соответствии с коэффициентами (11).

В схемах вычисления коэффициентов преобразования 10, 11.1, 11.2, …, 11.15, (Приложение 10, фиг. 10) заменены величины резисторов (Приложение 11, фиг. 14) на значения, которые обеспечивают вычисление коэффициентов, стоящих перед интегралами, в (10).

В результате отмеченных дополнений и замены получена схема устройства преобразования сигнала с использованием ступенчатых пилообразно изменяющихся коэффициентов деления резистивных делителей напряжений, в которой выходы

Выходы

Выходы интеграторов 2.0-2.15 соответственно соединяют с входами отсчитывающих и запоминающих элементов 3.0-3.15. На выходах отсчитывающих и запоминающих элементов получают и сохраняют значения интегралов I0-I15 в виде напряжений.

Выходы отсчитывающих и запоминающих элементов 3.0-3.15 соединяют с входами схем вычисления коэффициентов преобразования 10, 11.1-11.15 (фиг. 27), на выходах этих схем в соответствии с (10) получают коэффициенты преобразования, начиная с а0 по а15 по ступенчатым пилообразно изменяющимся коэффициентам деления делителей напряжения (10).

Для выполнения обратного преобразования (фильтрации) фиг. 27 выходы а0-а15 схем вычисления коэффициентов преобразования 10.0, 11.1-11.15 соединяют соответственно с входами модулей 16.0-16.15 БУСКДД2. На выходах

Таким образом, схема преобразования с использованием ступенчатых пилообразно изменяющихся коэффициентов деления делителей напряжений отличается от схемы преобразования с использованием пилообразных напряжений [1] следующими новыми блоками:

1. Генератором однополярных прямоугольных импульсов фиг. 5.

2. Схемами фиг. 10 и фиг. 11 формирования базисных функций (10), построенных на основе изменения коэффициентов деления резистивных делителей.

3. Схемами умножения базисных функций (10) на входной сигнал фиг. 10 и фиг. 11.

4. Схемой формирования однополярных прямоугольных импульсов, осуществляемой делителями частоты тактовых импульсов D1, D2, D3; дешифраторами D6-D9 и инверторами D4, D5, D10-D21.

На фиг. 23 приведена схема блока умножения сигнала F(t) на ортогональные ступенчатые пилообразно изменяющиеся коэффициенты делителя напряжений, включающая 15 модулей формирования и умножения, 15 схем инвертирования и 7 сумматоров приведения (10) к ортогональному виду.

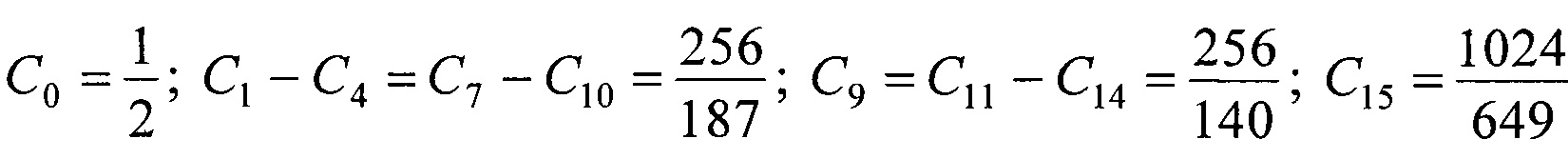

Из (11) находим при l=1 коэффициенты, стоящие перед интегралами:

Умножая значения интегралов J0-J15 фиг. 23 на соответствующие коэффициенты получают значение коэффициентов преобразования аn по ступенчатым пилообразно изменяющимся коэффициентам деления делителей напряжения (10).

Для вычисления а0 используют резистивный делитель из двух последовательно соединенных одинаковых резисторов, а для всех остальных используют операционные усилители с соответствующими коэффициентами Сn усиления (Приложение 11, фиг. 14).

Предложенный способ отличается от преобразования по пилообразным функциям тем, что в преобразовании используются ступенчатые ортогональные функции в виде ступенчатых пилообразно изменяющихся коэффициентов деления делителей напряжений, которые формируют путем управления ключами коммутации выходов резистивных делителей, приводят к ортогональному виду и умножают на напряжение сигнала F(t), интегрируют полученные в результате умножения напряжения на промежутках длинной 2l и, используя полученные значения интегралов, вычисляют значения коэффициентов преобразования аn в виде напряжений;

- при обратном преобразовании (восстановлении, фильтрации) сигнала по ступенчатым пилообразным напряжениям:

- параллельно умножают ступенчатые ортогональные пилообразные напряжения, сформированные резистивными делителями, на напряжения, соответствующие значениям коэффициентов разложения;

- параллельно суммируют полученные напряжения, восстанавливают сигнал либо, положив отдельные коэффициенты равными нулю, фильтруют сигнал F(t).

Достигнутый технический результат заключается в уменьшении аппаратной среднеквадратичной погрешности, максимального уклонения восстановленного сигнала от исходного.

Промышленная применимость изобретения определяется тем, что предлагаемый способ практически реализуем в устройстве, которое может быть изготовлено на базе широко применяемых комплектующих изделий и технологического оборудования.

Данный способ и реализующее его устройство преобразования сигнала произвольной формы могут найти очень широкое применение в разнообразных областях (измерительная техника, связь, запись-воспроизведение аудио и видео-произведений и т.д.).

На основании вышеизложенного и по результатам проведенного патентно-информационного поиска считаем, что предлагаемый способ и устройство преобразования сигнала произвольной формы отвечают критериям «Новизна», «Изобретательский уровень» и «Промышленная применимость» и могут быть защищены патентом РФ на изобретение.

Графические материалы, поясняющие суть изобретения

Фиг. 1. Графики исходного сигнала F(t) и восстановленного G(t) с использованием пилообразных напряжений.

Фиг. 2. Графики исходного сигнала F(t) и восстановленного с использованием ступенчатых пилообразно изменяющихся коэффициентов деления делителей напряжений.

Графики отражают близость методических погрешностей рассматриваемых способов.

Фиг. 3. Графики системообразующих (порождающий) ступенчатых пилообразно изменяющихся коэффициентов деления делителей напряжений.

Фиг. 4. Графики упорядоченных по числу секвент 15 ступенчатых пилообразно изменяющихся коэффициентов деления делителей напряжений.

Фиг. 5. Генераторы однополярных прямоугольных импульсов, в которой на выходах Q счетчиков сформированы частоты с коэффициентами деления 2, 4, 8, 18, 32, 64, 128, 256, 512 и 1024, а также дешифрированные параллельно четырех разрядные коды в импульсные последовательности напряжений, формируемых на одном из 16 выходов дешифраторов α1.0-α1.15; …;α4.0-α4.15. Для управления ключами делителей напряжений.

Фиг. 6-9. Графики входных напряжений четырех дешифраторов, иллюстрирующие характер изменения напряжений на входах ключей коммутации выходов делителей напряжений.

Фиг. 10. Схема модуля формирования умножения (МФУ1) ступенчатых пилообразно изменяющихся коэффициентов деления делителей напряжения, схожих с синусоидальными функциями.

Схема поясняет процесс формирования ступенчатых пилообразных изменений коэффициентов деления двух делителей напряжения и формирования умножения сигнала на ступенчатые функции (9).

Фиг. 11. Схема модуля формирования умножения (МФУ2) формирования ступенчатых пилообразно изменяющихся коэффициентов деления делителей напряжений аналогичных изменению функции косинуса.

Фиг. 12 и фиг. 13. Графики изменения коэффициентов деления делителей RD1 и RD2 и напряжения на выходах этих делителей.

Фиг. 14 и фиг. 15. Графики напряжений управления ключами в МФУ1 формирования двуполярных ступенчатых пилообразно изменяющихся коэффициентов деления и их изменения знаков.

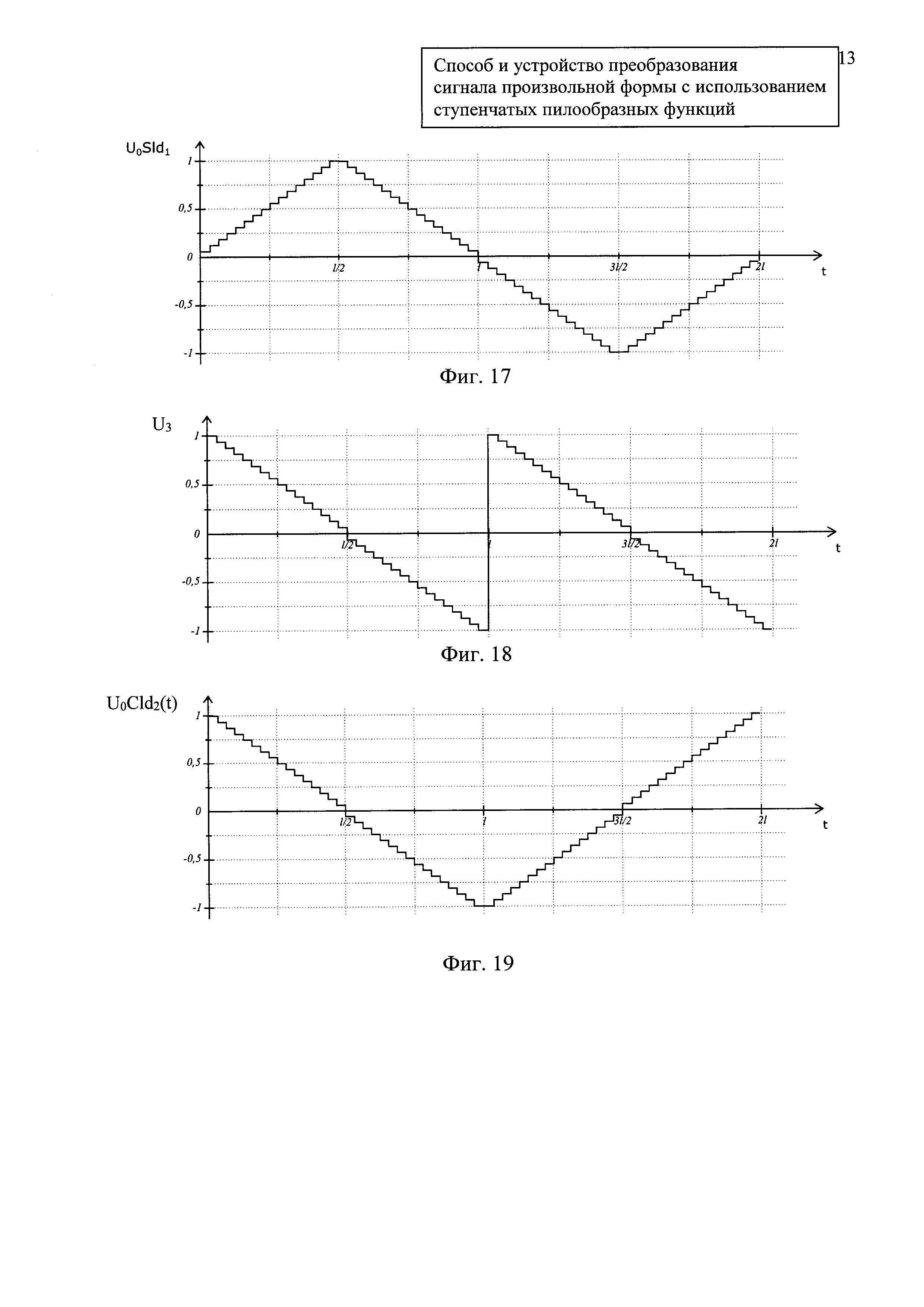

Фиг. 16 и фиг. 17. Графики формирования напряжений на выходе u3МФУ1 и выход самого модуля.

Фиг. 18 и фиг. 19. Графики изменений коэффициентов деления делителей в схеме формирования ступенчатых пилообразных коэффициентов деления напряжений, схожих с функциями косинуса.

Фиг. 20. Схема изменения знака напряжений для формирования функций с числами секвент 5, 6, 7, 9, 10, 11, 12, 13, 14.

Фиг. 21. График изменения коэффициентов деления с четырьмя секвентами как исходный график сигнала управления ключом s.

Фиг. 22. График изменения коэффициентов деления с пятью секвентами, формируемые схемой фиг. 20.

Фиг. 23. Схема блока умножения сигнала и коэффициентов деления делителей (БУСКДД).

Схема содержит три модуля формирования умножения МФУ1 и двенадцать моделей формирования умножения МФУ2, а также 15 схем изменения знака напряжений и семь схем суммирования, с помощью которых формируются ортогональные функции в виде ступенчатых пилообразно изменяющихся коэффициентов деления делителей напряжений в соответствии с (10) и выполняется умножение на напряжение сигнала F(t).

Фиг. 24. Схема формирования напряжений. Схема выполняет приведение функций Sld5(t) и Sld11(t) к ортогональному виду:

Фиг. 25. Схема вычитания напряжений. Схема выполняет приведение функций Cld6(t); Cld12(t); Sld13(t); Cld14(t) и Sld15(t) к ортогональному виду:

Фиг. 26. Схема устройства-прототипа преобразования с использованием пилообразных напряжений.

Фиг. 27. Предлагаемая схема преобразования сигнала произвольной формы с использованием ступенчатых пилообразно изменяющихся коэффициентов деления делителей напряжений.

В предлагаемой схеме вновь введены:

- генератор однополярных импульсов (ГОПИ);

- два блока умножения сигнала и коэффициента деления делителей (БУСКДД), каждый из которых включает по 15 модулей формирования умножения (МФУ), в которых с помощью электронных ключей выполняются переключения выходов делителей напряжений и тем самым формируются ступенчатые пилообразно изменяющиеся коэффициенты деления в соответствие с (10). В схемах 10.0; 11.1-11.15 изменено несколько резисторов, а все остальные составляющие сохранены без изменений.

ИСТОЧНИКИ ИНФОРМАЦИИ

1. Горепекин А.В., Горепекин Р.А., Циклаури Д.З. Способ и устройство преобразования сигнала произвольной формы. Патент RU 2576591 С2, кл. G06F 17/14, дата публикации 10 марта 2016 г.

2. Хармут Х.Ф. Теория секвентного анализа. Основы и применения. - М.: Мир, 1980. - 576 с.

3. Добеши И. Десять лекций по вейвлетам. - Ижевск: НИЦ «Регулярная и хаотическая динамика», 2001. - 464 с.

4. Фолькенберри Л.М. Применение операционных усилителей и линейных ИС. - М.: Мир, 1985. - 572 с.

5. Микросхема AD539 умножения аналоговых сигналов. http://www/analog.com/static/imported-files/data_sheets/AD539/pdf.

6. Ермаков В.Ф. Устройство для выполнения преобразований Уолша (его варианты). Патент RU 2203506 С2, кл. G06F 17/14, дата публикации 27 апреля 2003 г.

7. Авторское свидетельство СССР №203911, кл. G06R 7/62, 1982.

8. Смирнов В.И. Курс высшей математики. Т.2, изд. 16 - М.: Из-во физ.-мат. лит-ры. 1958.

9. Шило В.Л. Популярные цифровые микросхемы. - М.: Радио и связь, 1987. - 352 с.

10. Справочное пособие под редакцией С.В. Якубовского. Аналоговые и цифровые интегральные микросхемы. - М.: Радио и связь, 1985. - 430 с.

Реферат

Группа изобретений относится к области измерений, вычислительной технике и предназначено для прямого и обратного преобразований сигналов произвольной формы. Техническим результатом является уменьшение аппаратной среднеквадратичной погрешности, максимального уклонения восстановленного сигнала от исходного сигнала. Устройство содержит источник сигнала произвольной формы, блоки интеграторов, блоки отсчитывания и запоминания, резисторы, операционный усилитель, генератор однополярных прямоугольных импульсов, блоки умножения ступенчатых пилообразно изменяющихся коэффициентов деления делителей, блоки вычисления коэффициентов преобразования. 2 н.п. ф-лы, 27 ил.

Формула

Комментарии