Способ и устройство преобразования сигналов произвольной формы с использованием пилообразных ступенчатых вейвлетов - RU2682860C2

Код документа: RU2682860C2

Чертежи

Описание

Изобретение относится к области измерений, вычислений, импульсной техники и предназначено для прямого и обратного преобразования, а также анализа сигналов произвольной формы.

С помощью различных базисов можно полнее выявить и подчеркнуть те или иные свойства, содержащиеся в сигналах.

Подавляющее большинство материнских вейвлетов и базисов на их основе являются достаточно сложными функциями [1].

Генерация напряжений, тождественно изменяющихся в соответствие с функциями материнских вейвлетов [1] и полученных вейвлетов в результате сжатия и их сдвигов, затруднено, и поэтому для реализации вейвлет-преобразований используют дискретизированные вейвлет-преобразования [5, 6]. При этом скорость, объем и сложность вычислений играют существенную роль.

Наиболее простым и быстродействующим вейвлет-преобразованием, требующим минимум операций умножений, является преобразование, основанное на использовании вейвлет-напряжений Хаара, полученных путем сжатия и сдвига [1, 2].

Однако преобразование Хаара при преобразовании непрерывных сигналов обладает существенным недостатком, заключающимся в большой ступенчатости восстановленного сигнала, обусловленной тем, что вейвлеты Хаара принимают только три значения ±1 и ноль [2].

В отличие от преобразования Хаара преобразование, основанное на использовании пилообразных вейвлет-напряжений [4], значительно уменьшает ступенчатость, во много раз уменьшает как методическую среднеквадратичную погрешность, так и максимальное уклонение восстановленного сигнала относительно исходного.

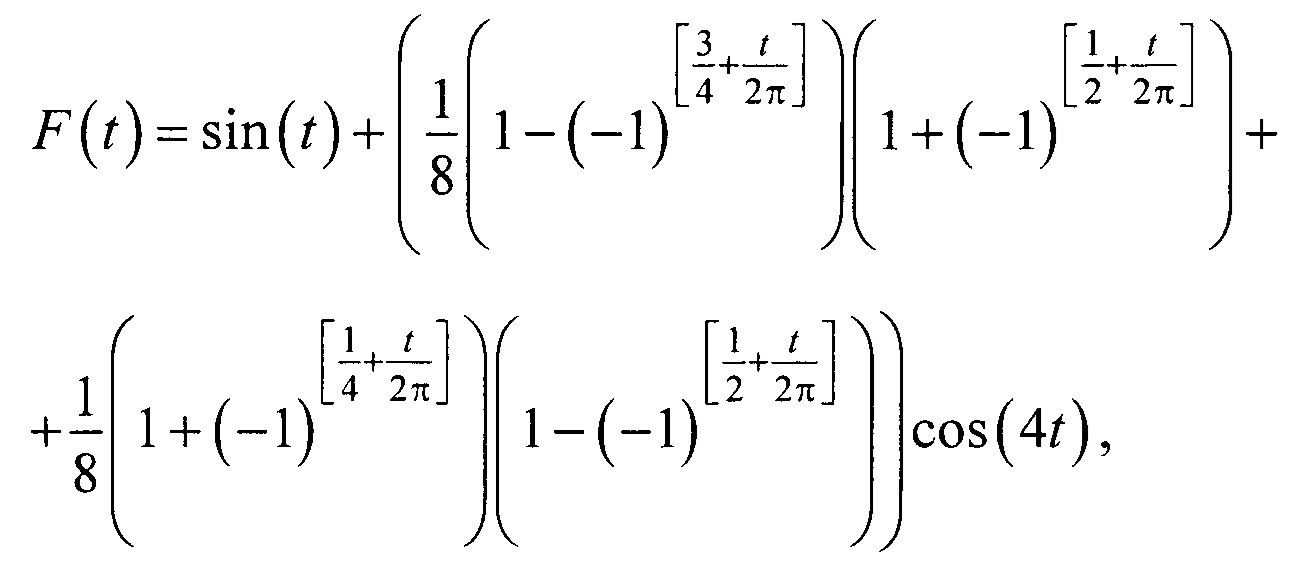

В соответствие с [4] базисные пилообразные вейвлет-напряжения формируют в результате следующих операций.

Напряжение Уолша [2] с числами секвент 0, 1, 2, 4, 8 с помощью интеграторов на операционных усилителях [8] интегрируют, в результате этого формируют однополярные пилообразные напряжения, далее путем суммирования однополярного напряжения U0(t), формируют двуполярные пилообразные напряжения с амплитудой

Два первых пилообразных напряжения Ga1(t) и Ga2(t) сохраняют без изменений и обозначают Gaν1(t) и Gaν2(t).

Напряжение Ga4(t) умножают на два сдвинутых во времени ортогональных импульса γ1,1(t) и γ1,2(t), формируют напряжение Gaν3(t) и Gaν4(t); напряжение Ga8(t) умножают на группу следующих однополярных импульсов γ2,1(t) - γ2,4(t), формируют четыре вейвлет-напряжения Gaν5(t) - Gaν8(t). Напряжение Ga16(t) умножают на группу однополярных импульсов γ3,1(t) - γ3,8(t) формируют еще восемь вейвлет-напряжений Gaν9(t) - Gaν16(t).

Затем полученные пилообразные вейвлет-напряжения объединяют в базис [4].

Для прямого преобразования напряжение сигнала F(t) умножают на пилообразные вейвлет-напряжения, затем на промежутках преобразования длиной 1, вычисляют значение интегралов от этих произведений. Используя значения этих интегралов, вычисляют коэффициенты преобразования, а при обратном преобразовании вейвлет-напряжения умножают на напряжения, тождественные коэффициентам преобразования. Результаты умножений параллельно суммируют и тем самым восстанавливают сигнал.

Аппаратная реализация пилообразных напряжений с использованием аналоговой техники существенно увеличивает погрешность преобразования по сравнению с методической погрешностью способа с использованием пилообразных вейвлет-напряжений.

Увеличение аппаратной погрешности до 5% связана с погрешностью интеграторов на операционных усилителях, формирующих пилообразные вейвлет-напряжения [2, 8]. Умножение сигнала F(t) на пилообразные вейвлеты выполняют с помощью микросхемы АД539, которая также построена на операционных усилителях и которая также обладает аппаратной погрешностью.

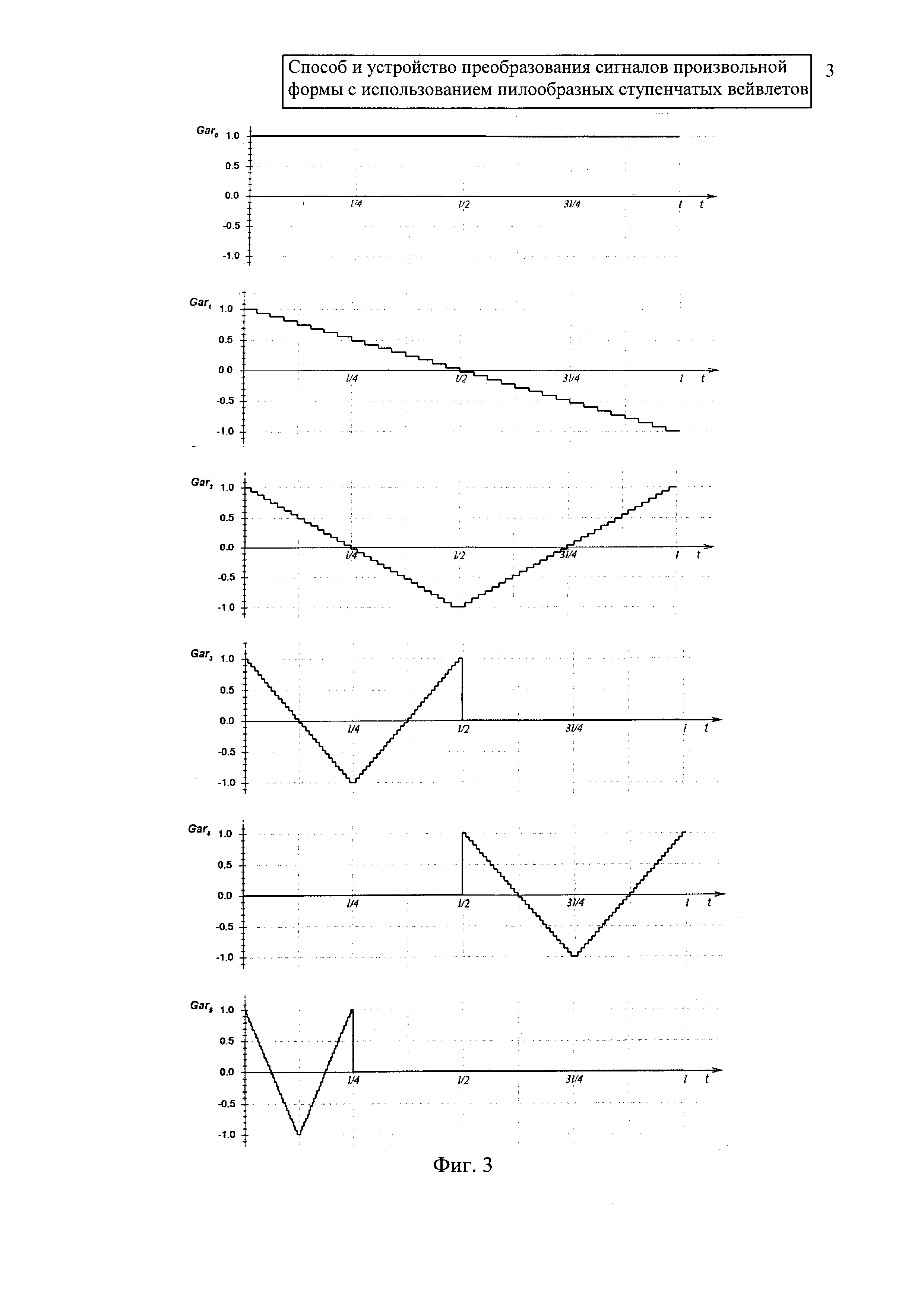

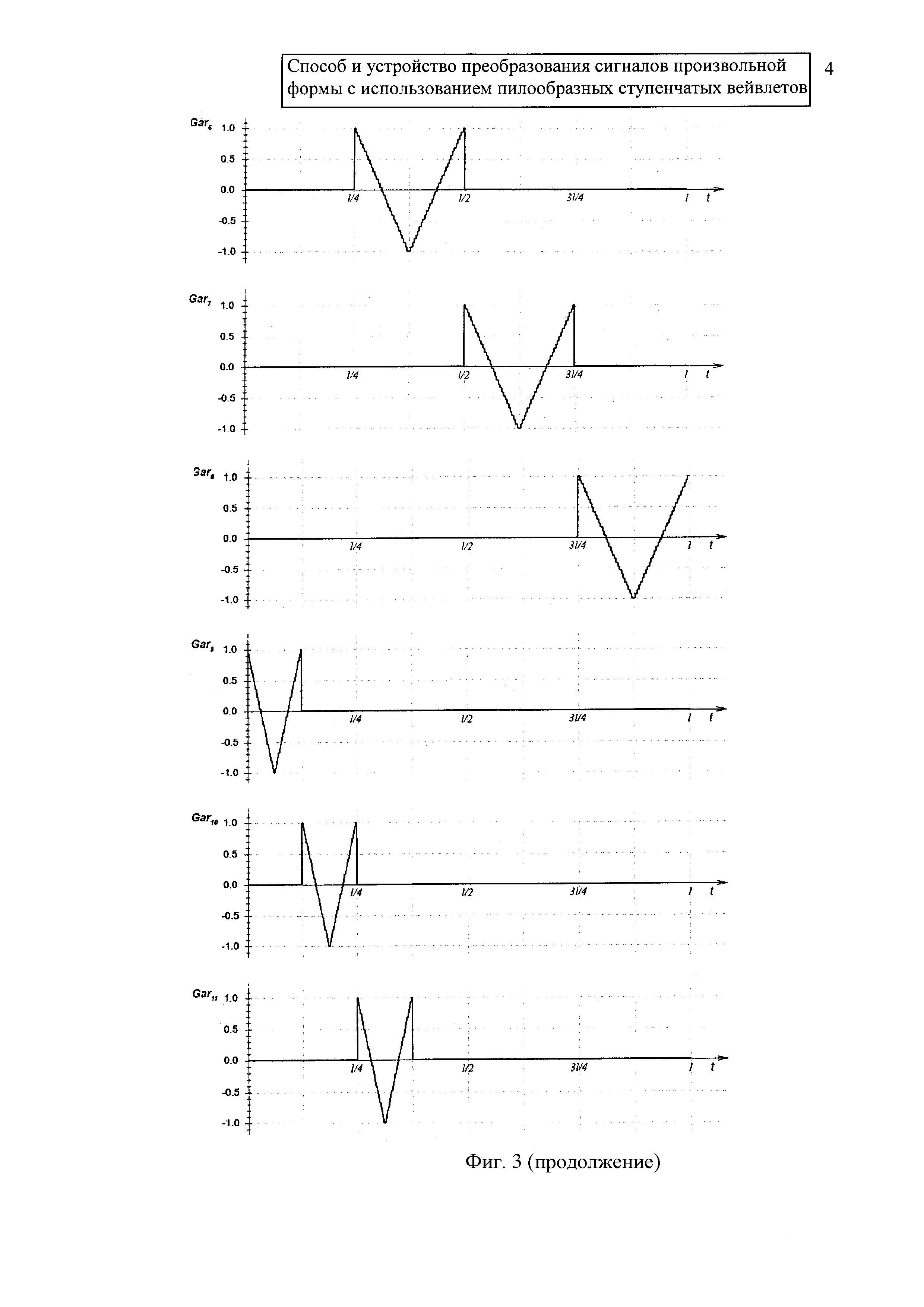

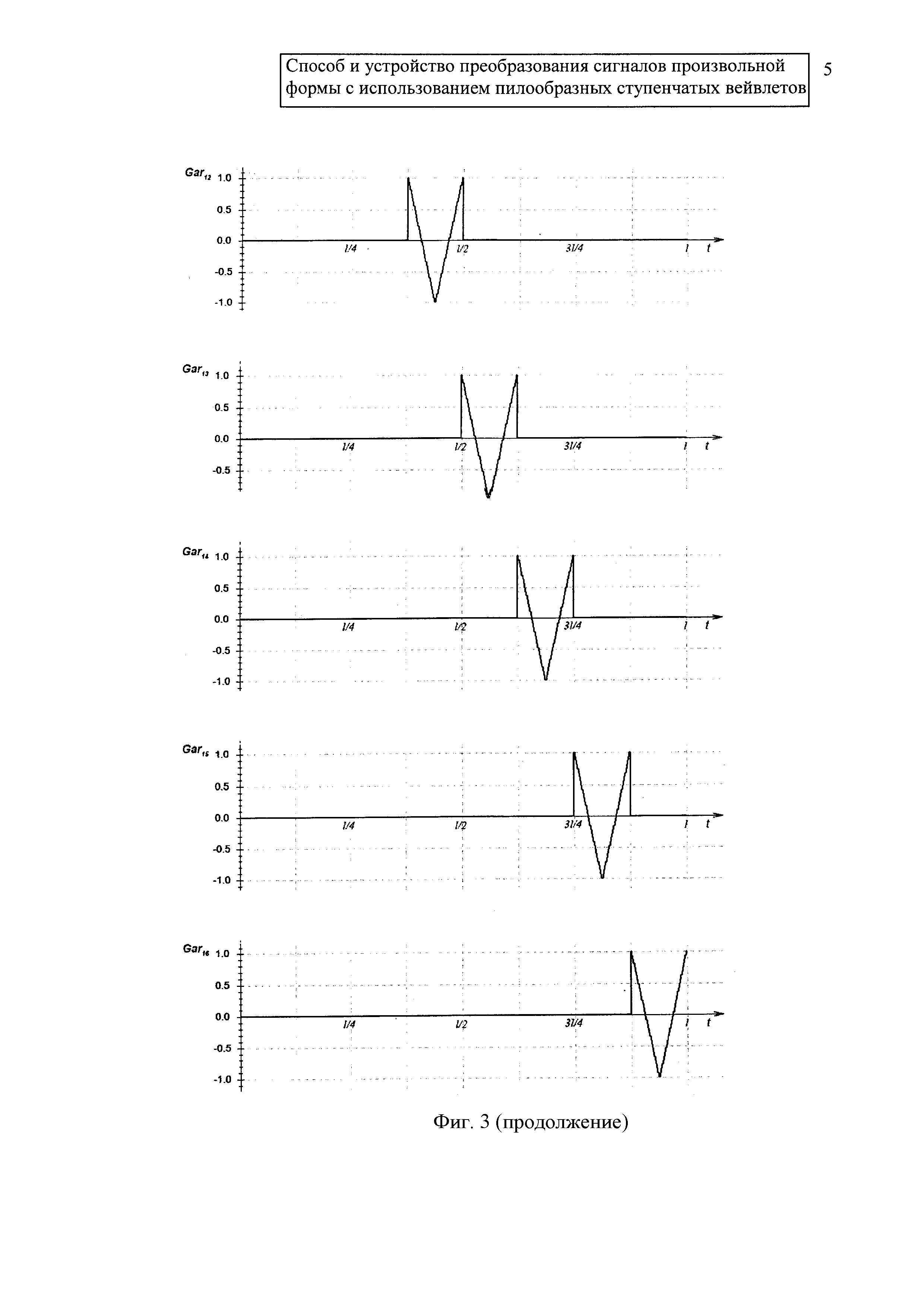

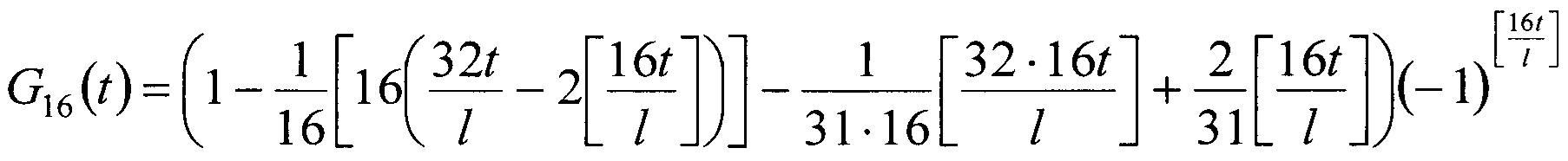

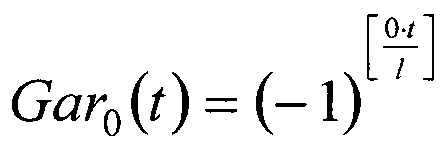

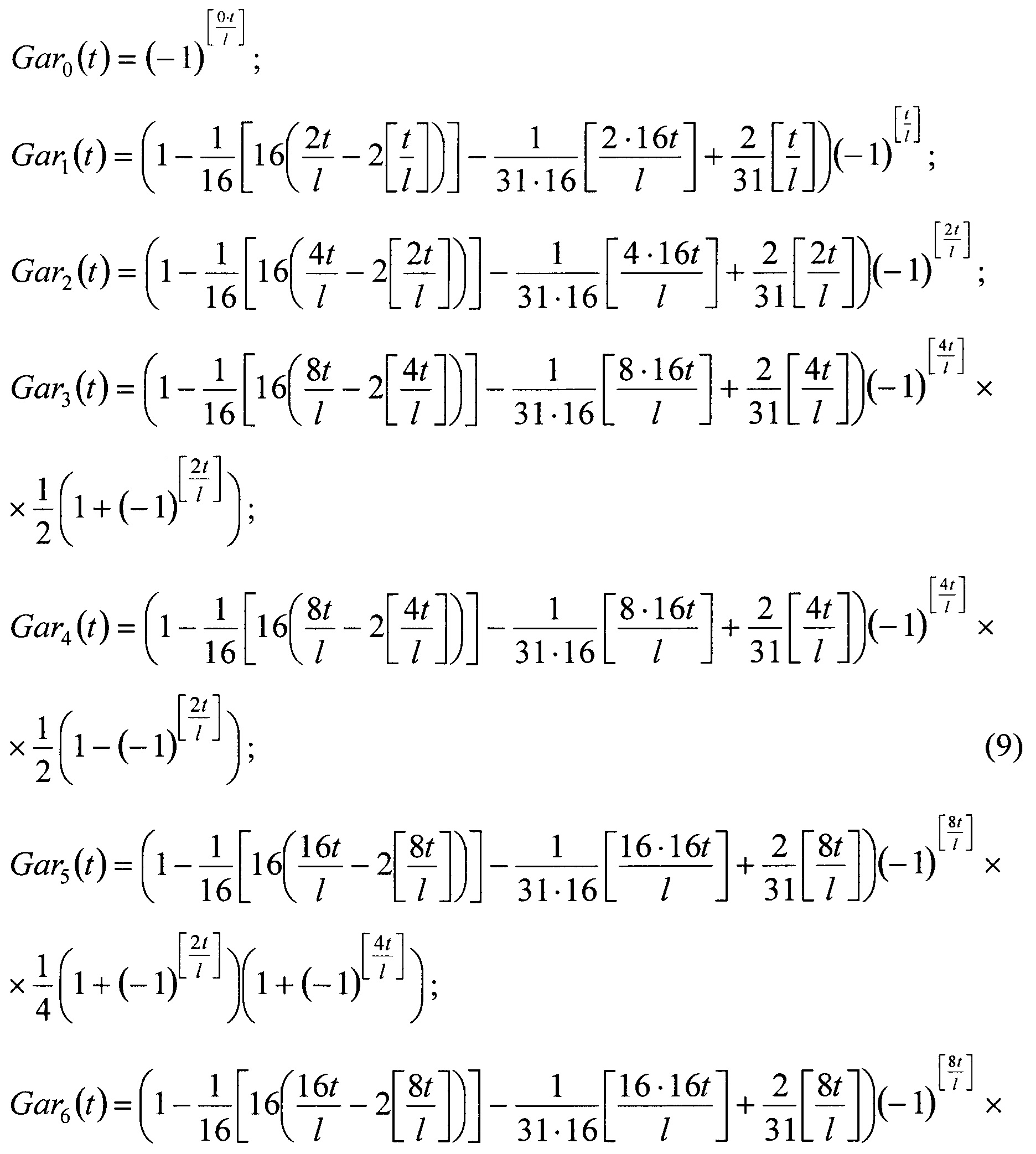

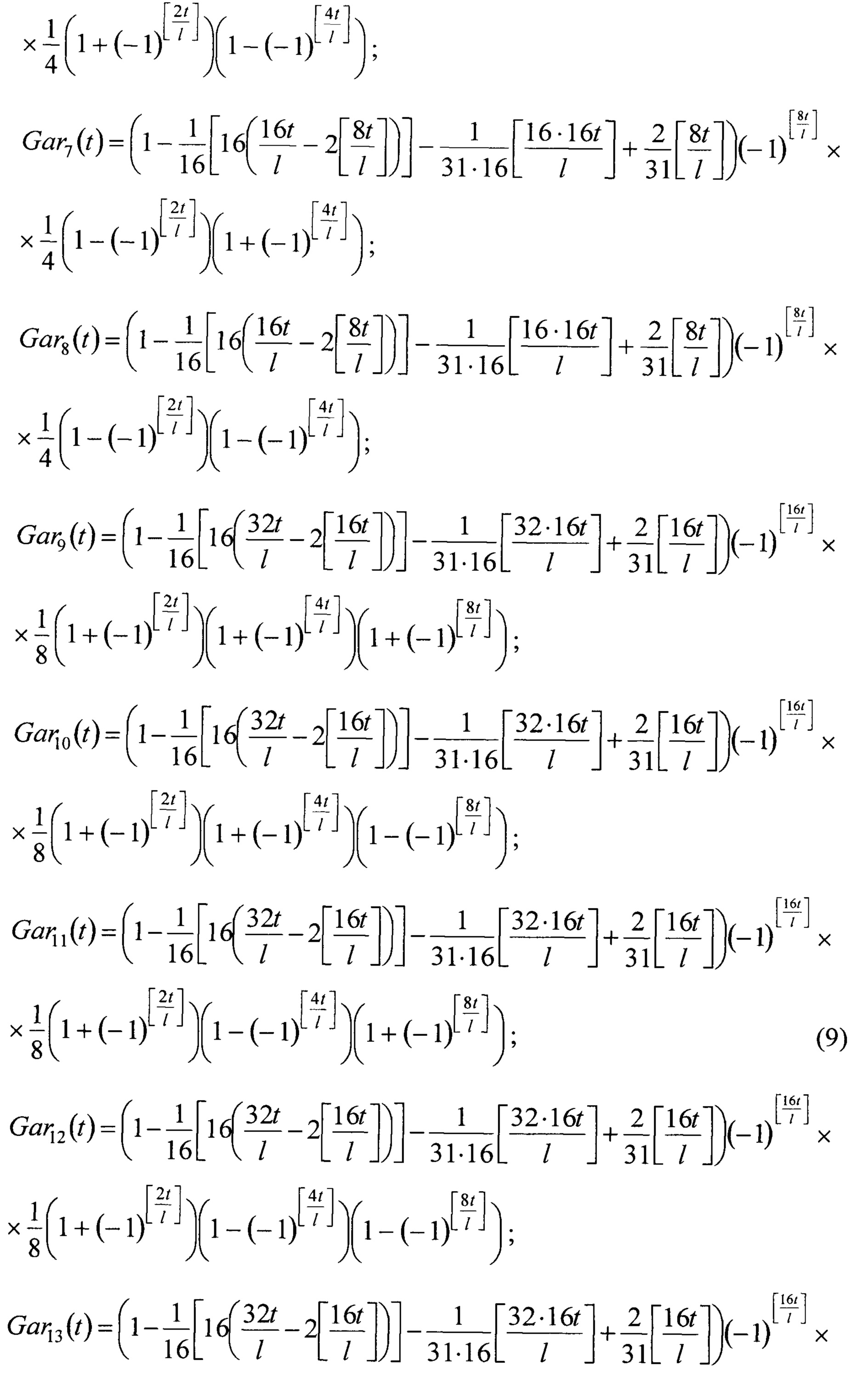

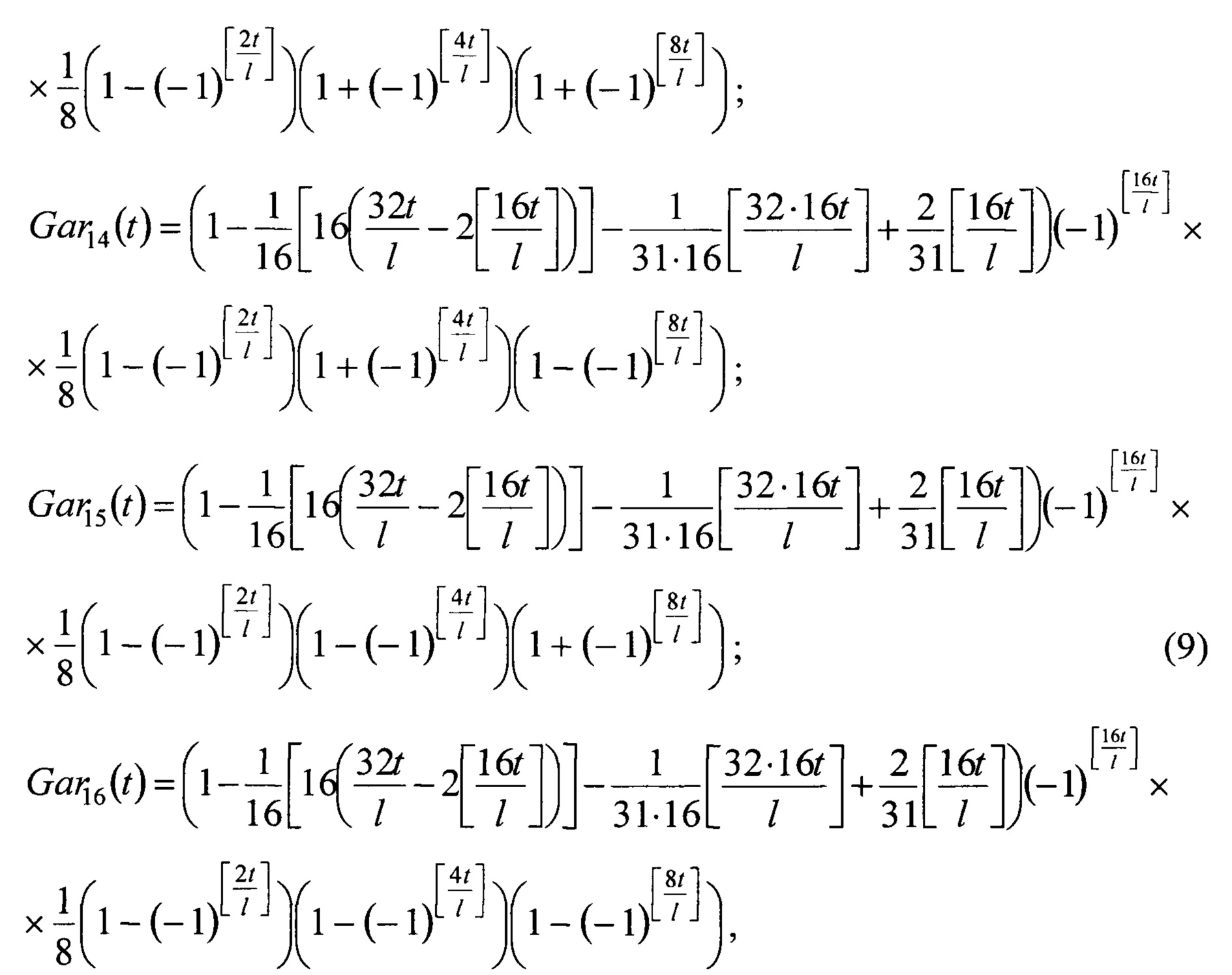

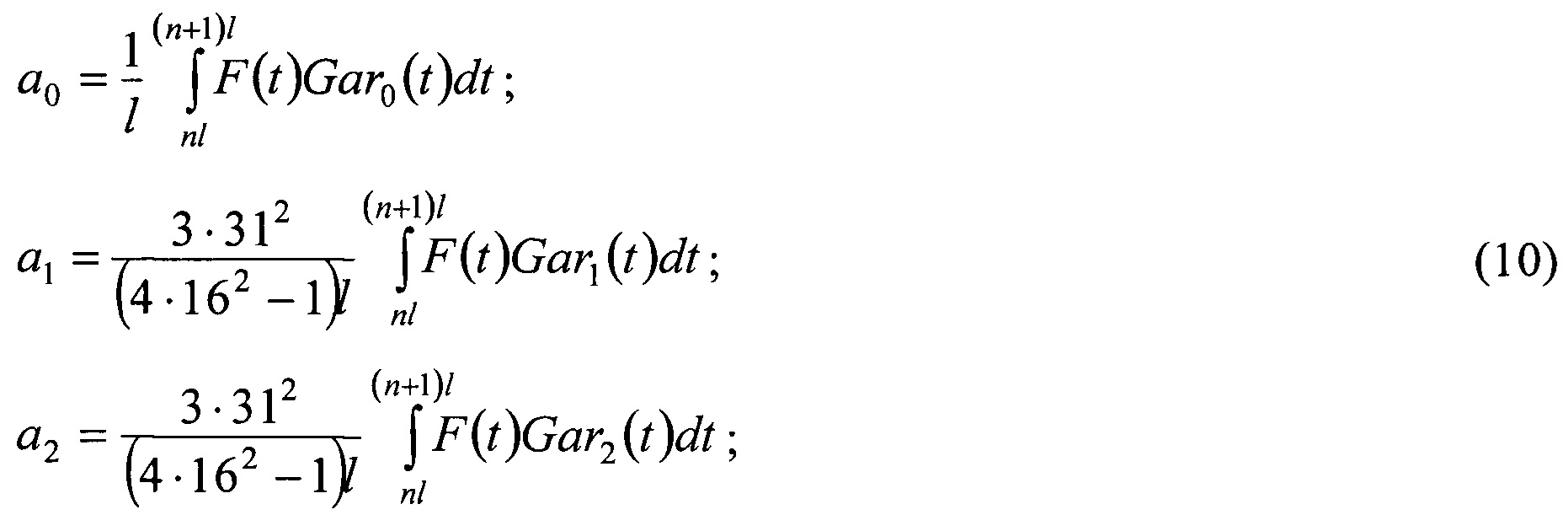

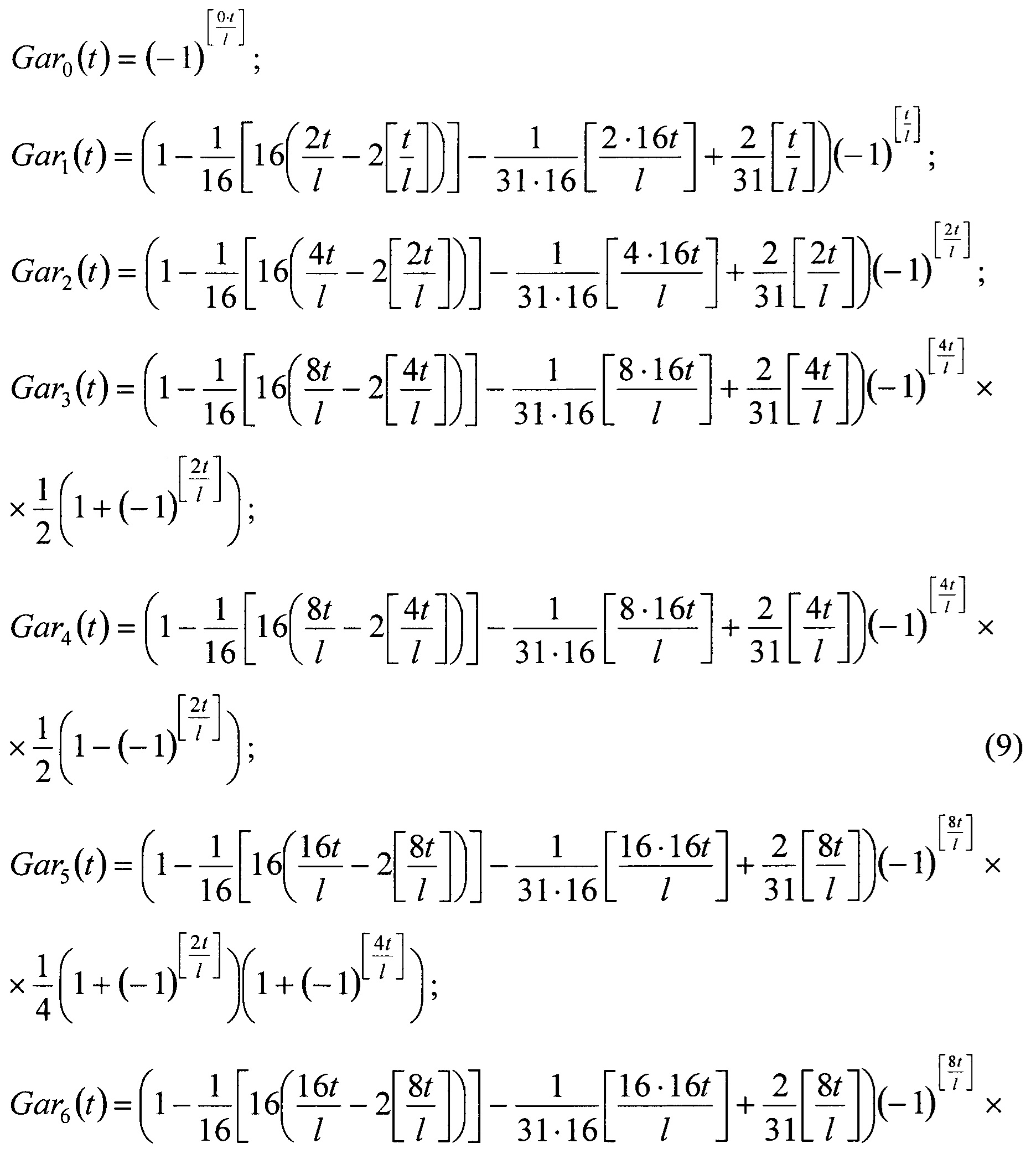

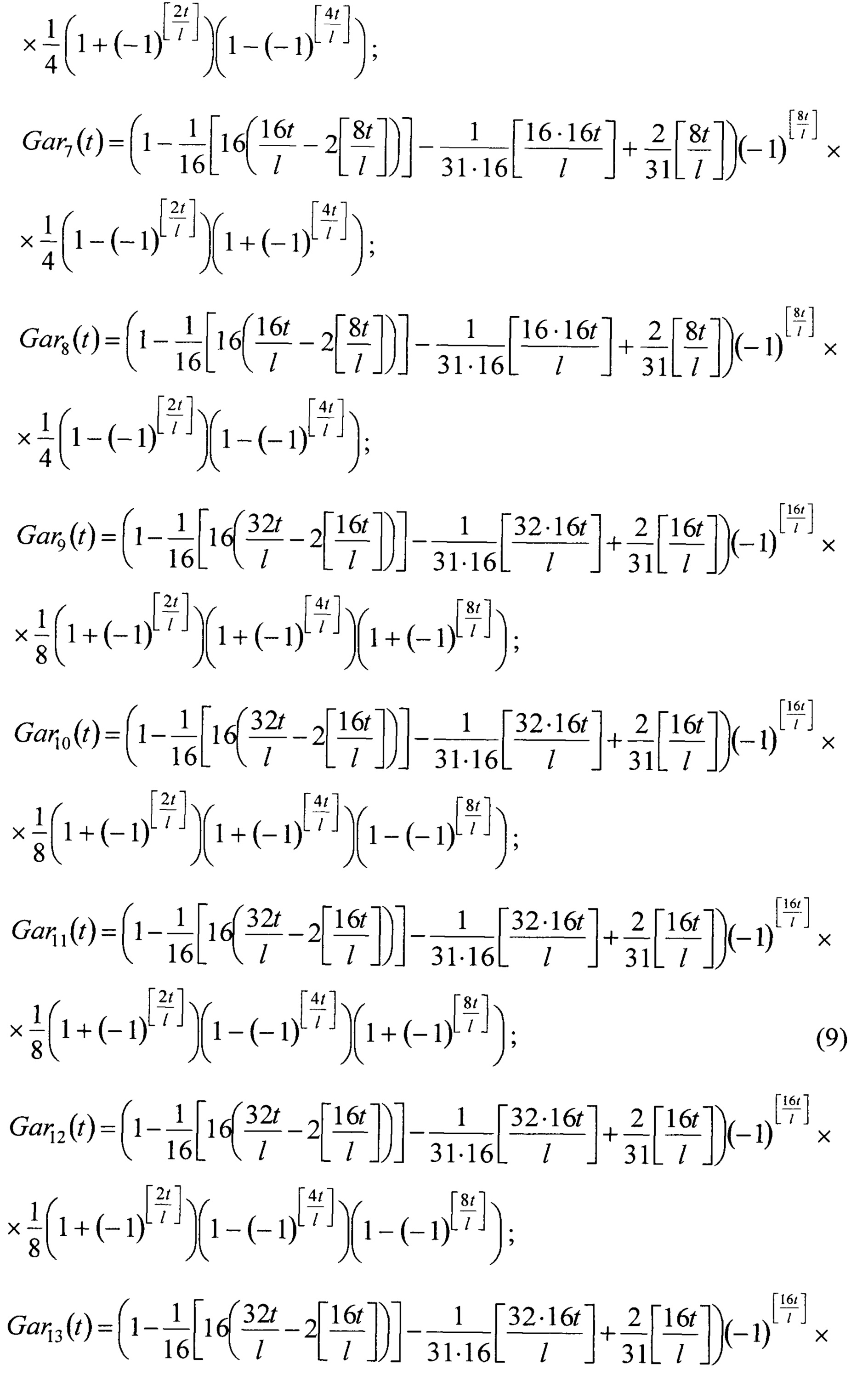

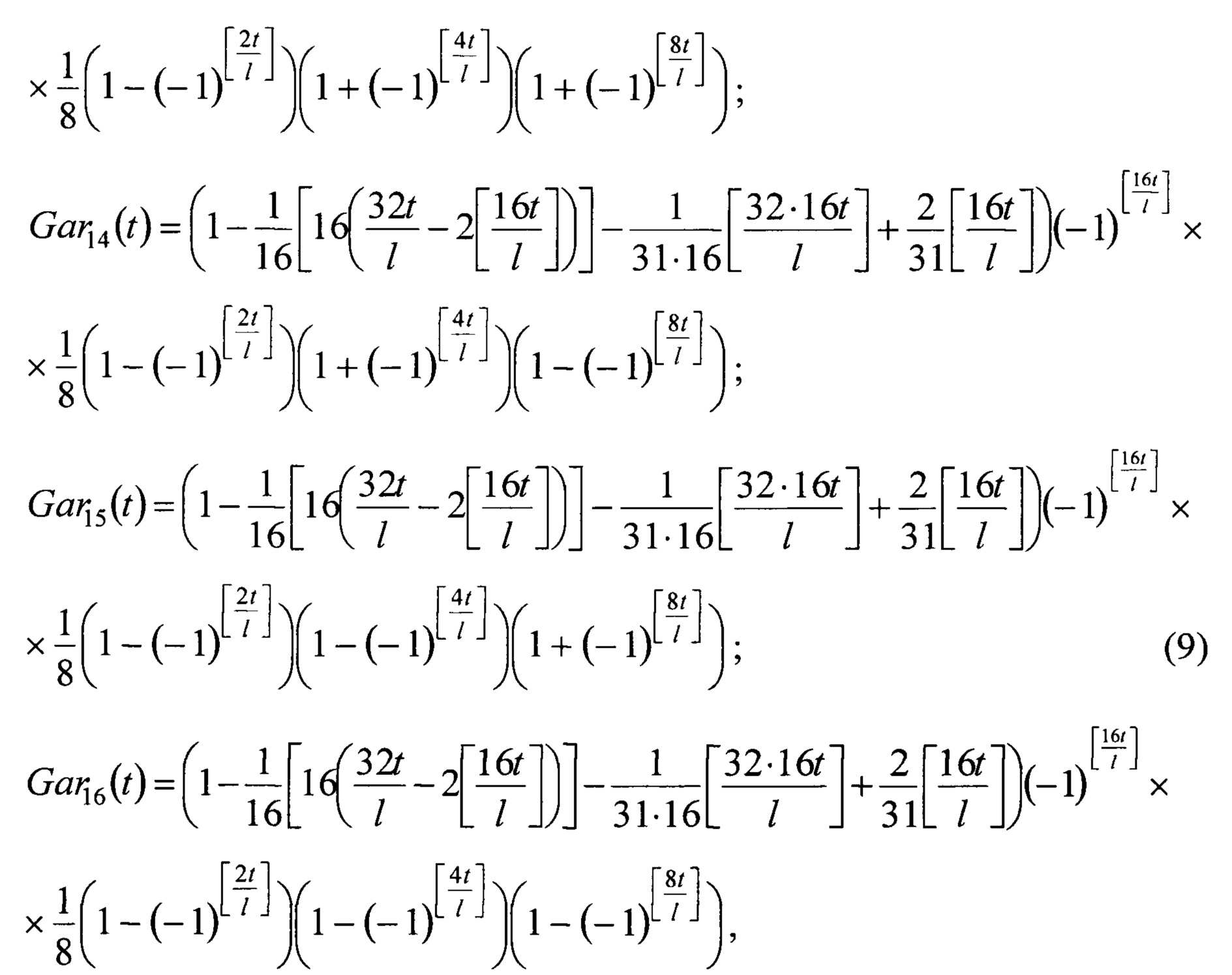

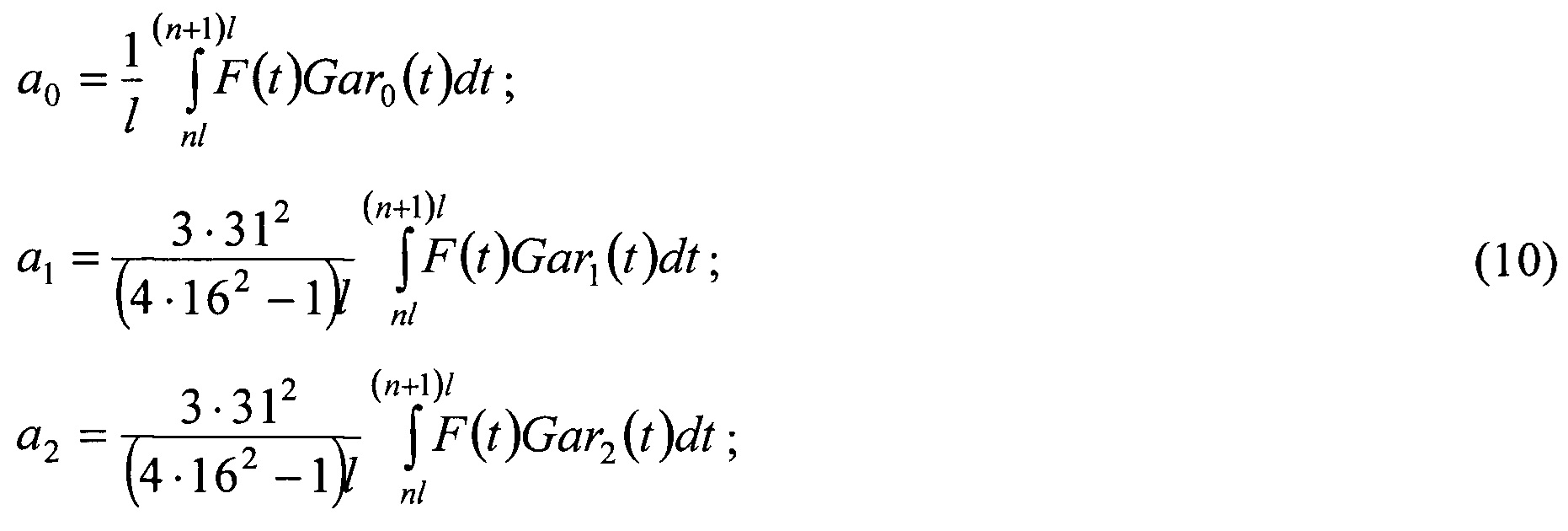

Структура построения базиса предлагаемого способа, основанного на использовании пилообразных ступенчато-изменяющихся коэффициентах деления делителей напряжений (9), (10, (11), фиг. 3, полностью совпадает со структурой базисов, построенных на основании функций Хаара и пилообразных вейвлет-напряжений, поэтому способ преобразования Хаара выбран в качестве аналога, а пилообразно вейвлет-преобразование [4], как наиболее близкое к предлагаемому способу с использованием ступенчатых пилообразных вейвлетов, выбран в качестве прототипа.

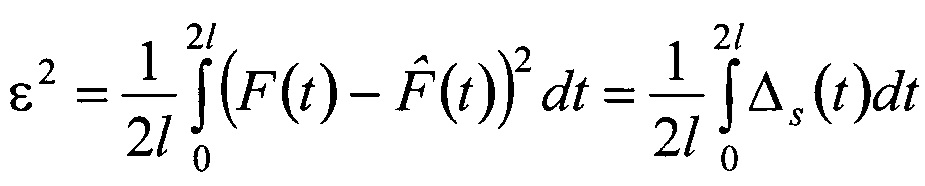

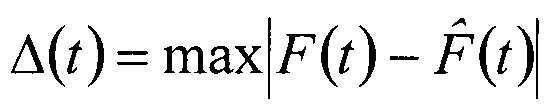

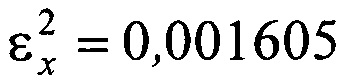

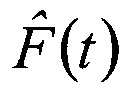

Для сравнения методических погрешностей преобразований по функциям Хаара [2], пилообразным вейвлет-напряжениям [4] и предлагаемому методу, основанному на использовании пилообразных ступенчато-изменяющихся коэффициентах деления делителей напряжения (9), (10) и (11), используем среднеквадратическую погрешность и максимальное уклонение [8].

где

t - время,

[…] - выделение целой части.

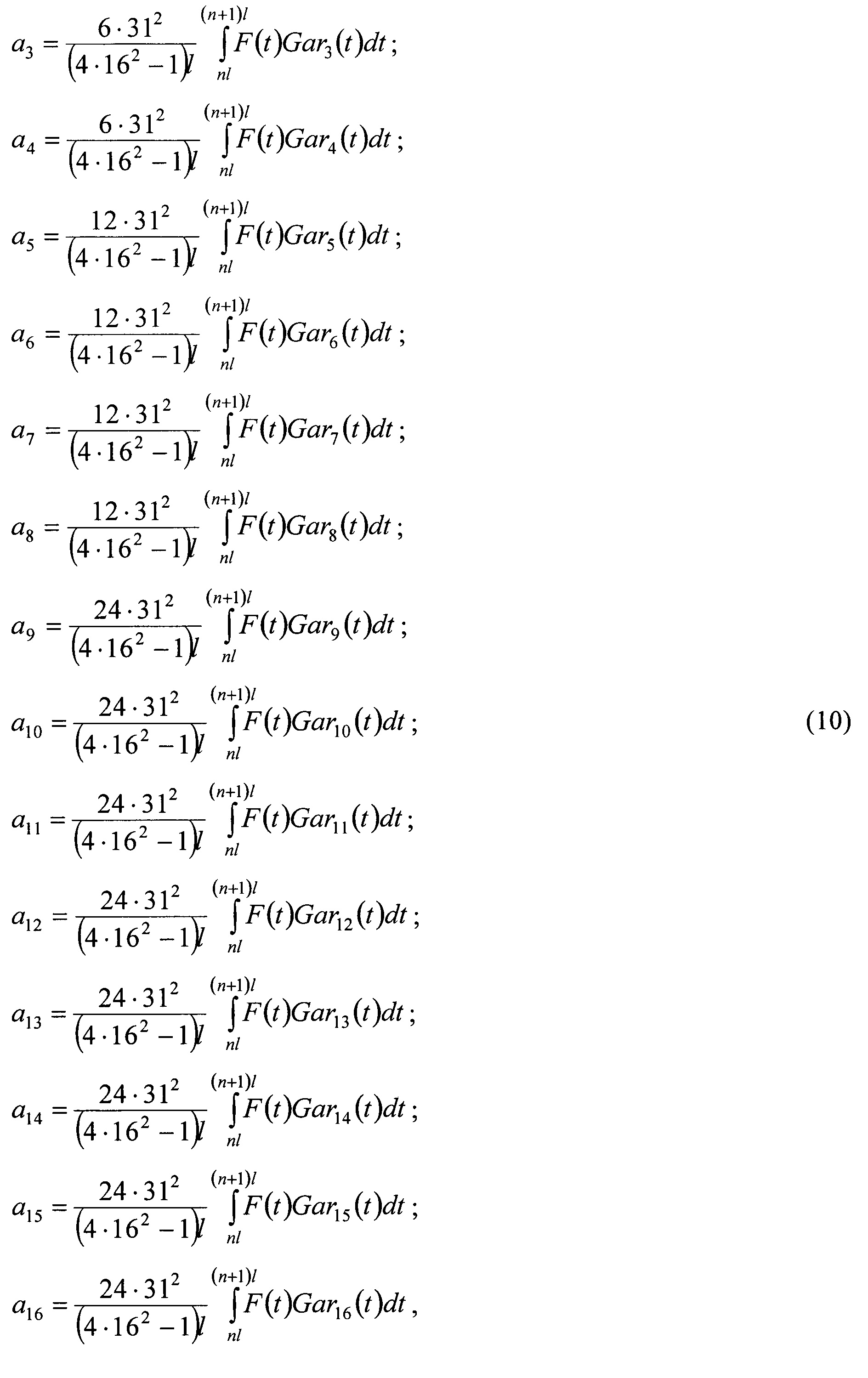

В результате преобразованный по функциям Хаара

Сравнение результатов преобразований показывает, что методическая погрешность

Учитывая то, что делители напряжений, составленные из одинаковых по величине резисторов и изготовленных по одной технологии, могут быть изготовлены с высокой точностью (±0,03%; 0,1%; 0,25%; …) и очень малым температурным коэффициентом изменения [11] и тем самым позволяют сформировать ступенчатые вейвлеты (9) с погрешностью, определяемой точностью резисторов делителей.

Предлагаемый способ (9), (10) и (11) фиг. 3 в наибольшей степени близок к способу [4], основанному на использовании пилообразных вейвлет-напряжений, как по характеру изменения на промежутках преобразования, так и по расположению на временной оси t, и поэтому [4] выбран в качестве прототипа.

Целью настоящего изобретения является уменьшение аппаратной погрешности преобразования сигнала на этапах формирования базисных функций и умножения их на сигнал.

Поставленная цель достигается тем, что для преобразования сигнала вместо базисных пилообразных вейвлет-напряжений [4] используют базисные пилообразные ступенчатые вейвлеты, которые формируют в виде изменяющихся во времени коэффициентов деления делителей напряжений, составленных из одинаковых по величине и изготовленных по одной технологии резисторов следующим образом.

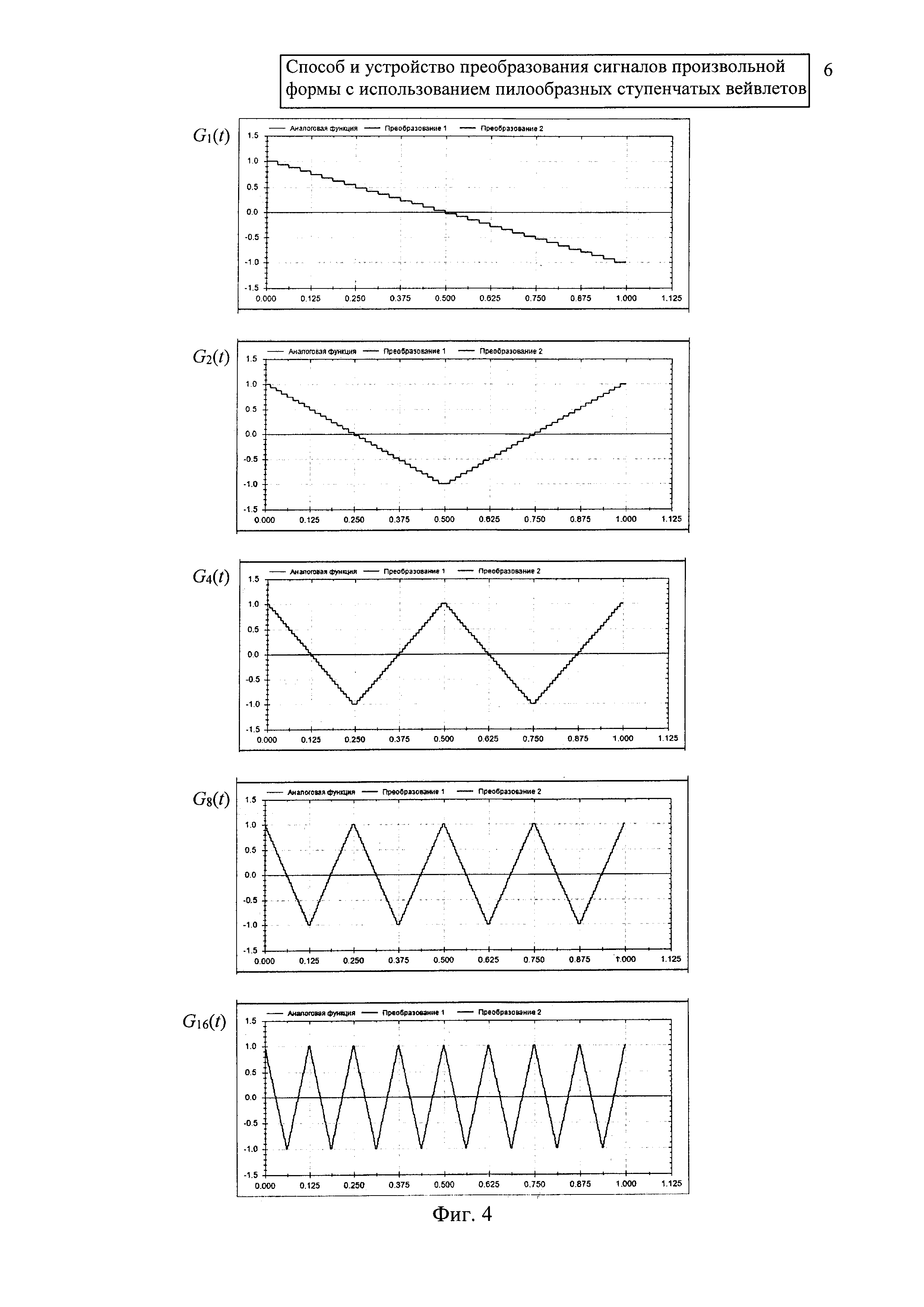

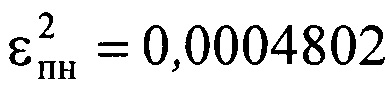

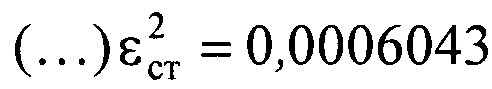

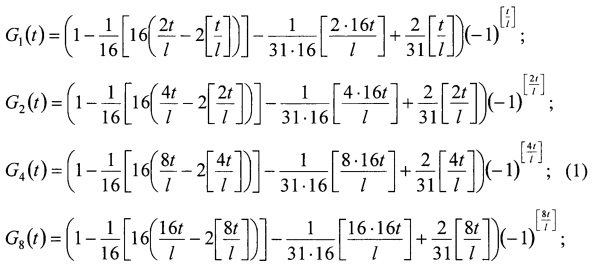

Для достижения поставленной цели на первом этапе формируют порождающие пилообразные ступенчато-изменяющиеся функции в виде изменяющихся коэффициентов деления делителей напряжений с числами секвент 1, 2, 4, 8 и 16(1) фиг. 4.

где: t - время;

[…] - выделение целой части.

Графики этих функций приведены на фиг. 4.

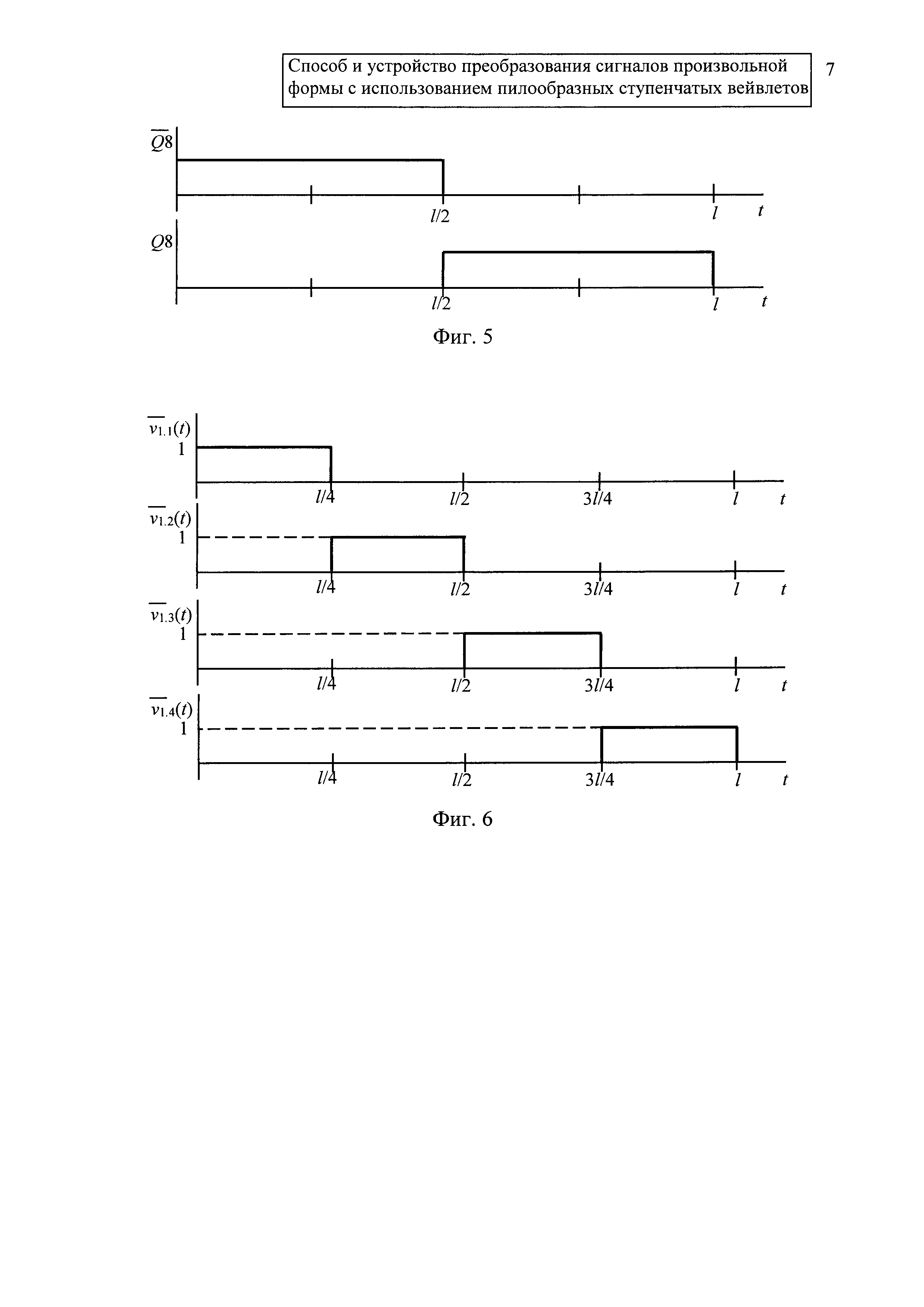

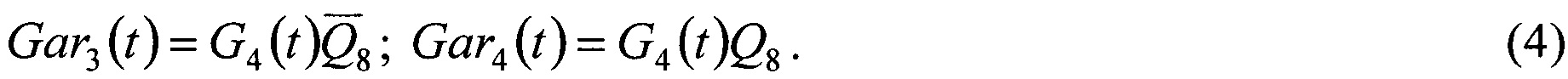

Функции G1(V), G2(t) сохраняют без изменения и обозначают

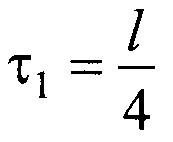

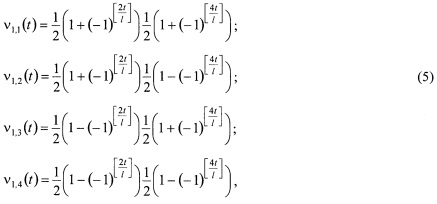

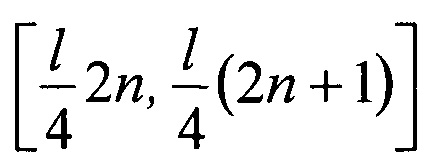

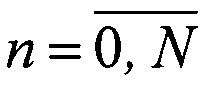

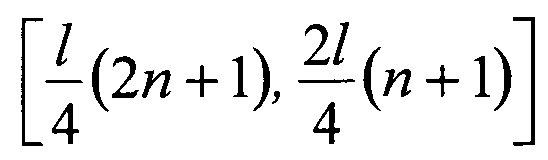

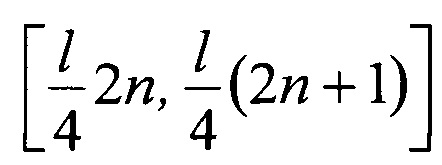

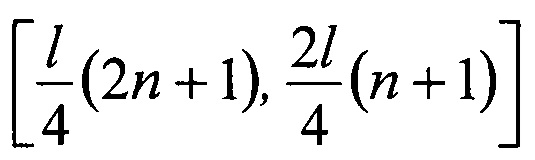

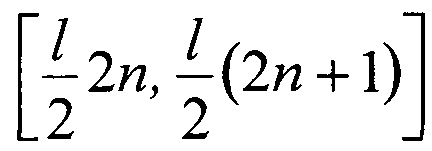

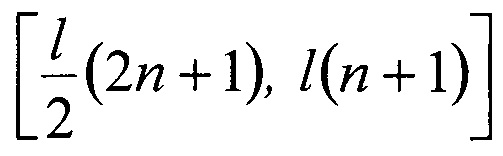

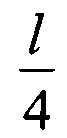

а функции G4(t), G8(t) и G16(t) умножают в следующей последовательности на однополярные импульсы. Функцию G4(t) умножают на однополярные импульсы длительностью

формируют пилообразные ступенчатые вейвлеты

В результате умножения двух однополярных импульсов формируют импульсы с длительностью

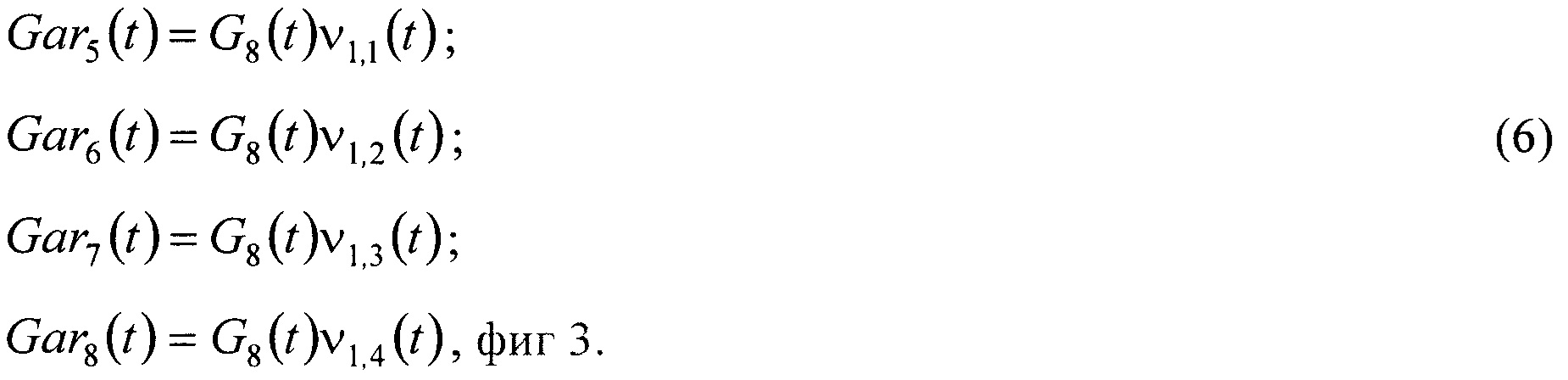

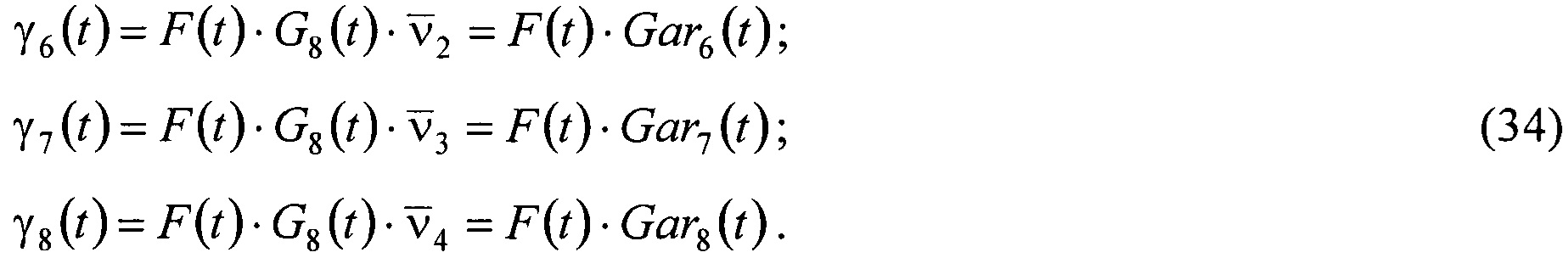

которые далее умножают на функцию G8(t), формируют пилообразные ступенчатые вейвлеты:

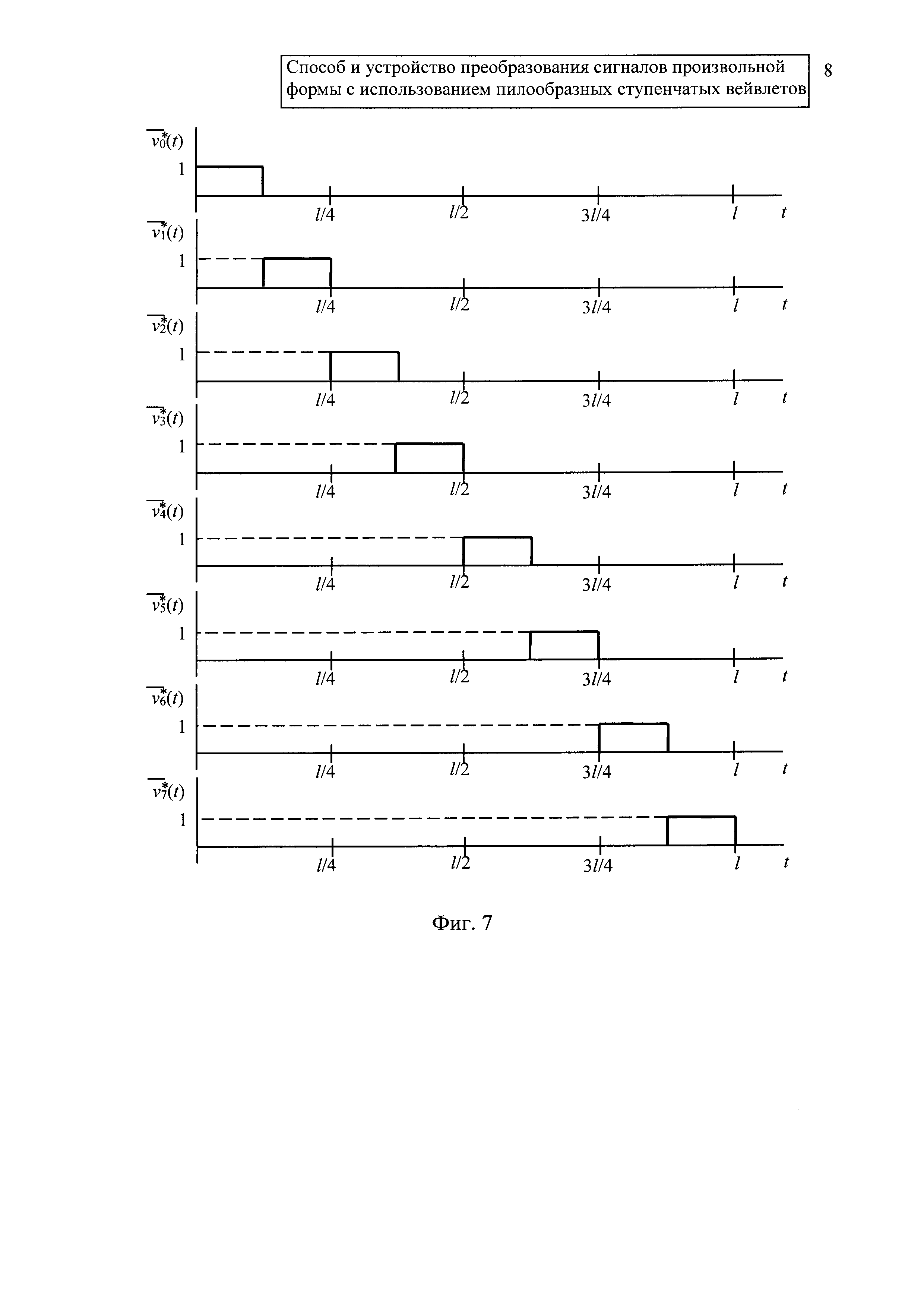

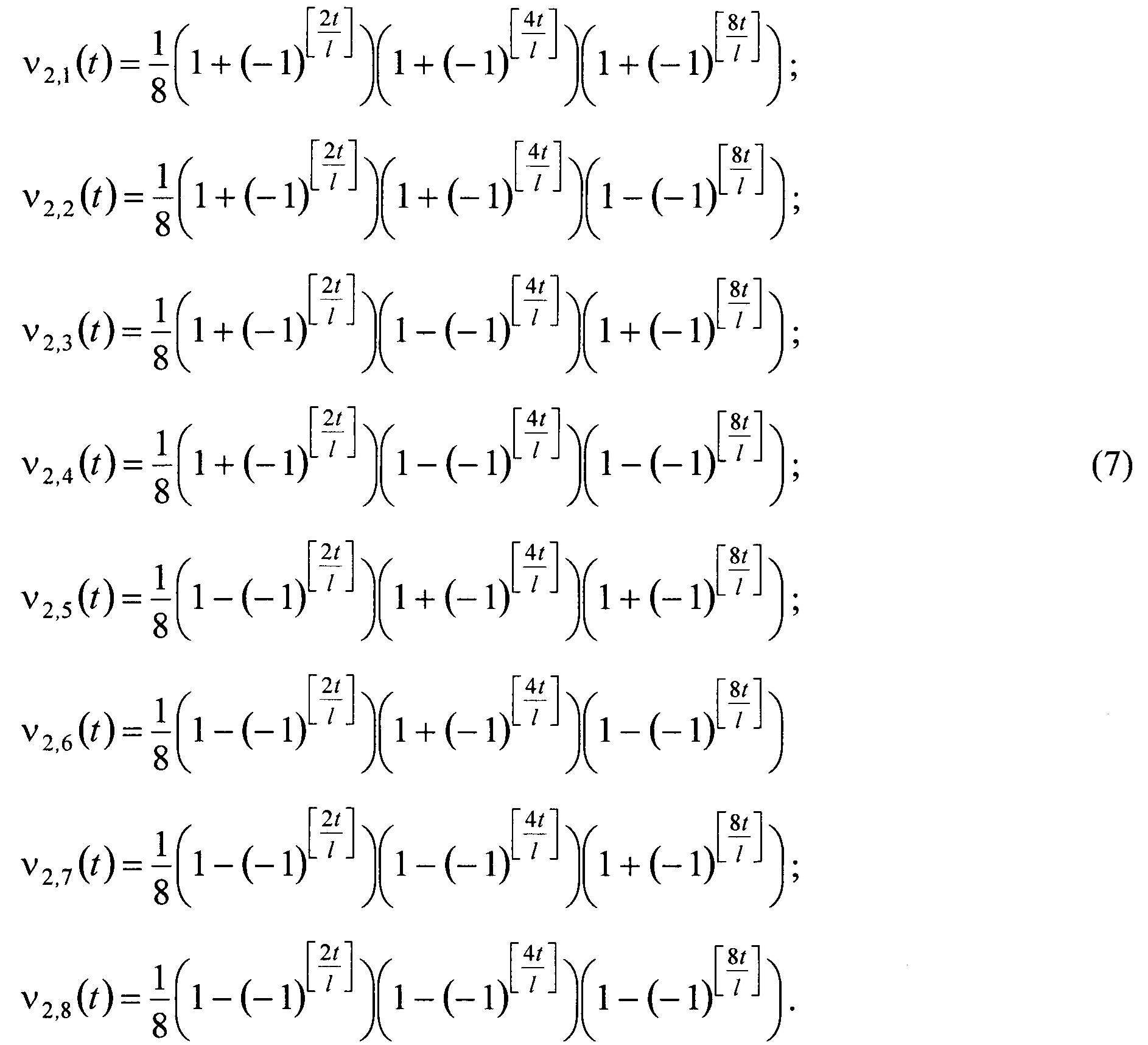

Функцию G16(t) умножают на произведения следующих трех однополярных импульсов:

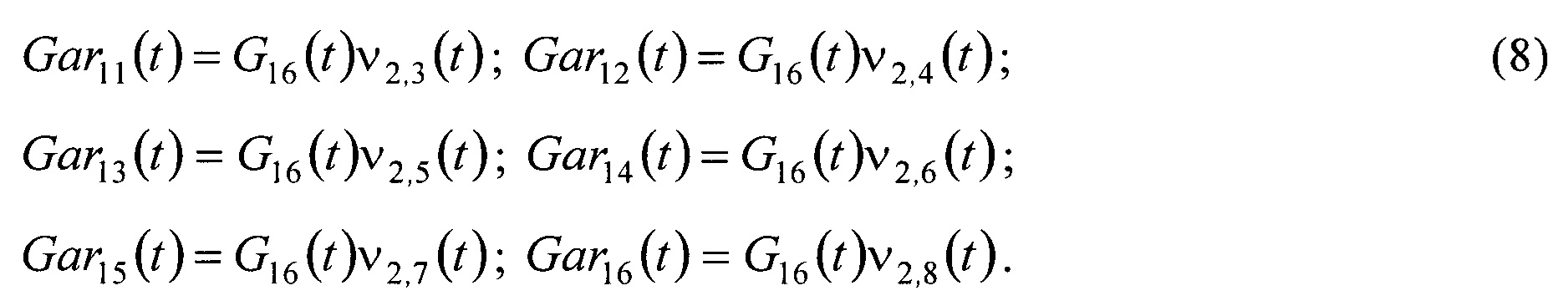

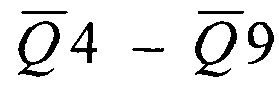

фиг. 7. В результате умножений G16(t) на (7) формируют пилообразные ступенчатые вейвлеты:

Gar9(t) = G16(t)ν2,1(t); Gar10(t) = G16(t)ν2,2(t);

Полученные пилообразные ступенчатые вейвлеты (2), (4), (6) и (8) объединяют, дополнив вейвлетом

где: t - время;

[…] - выделение целой части, фиг. 4.

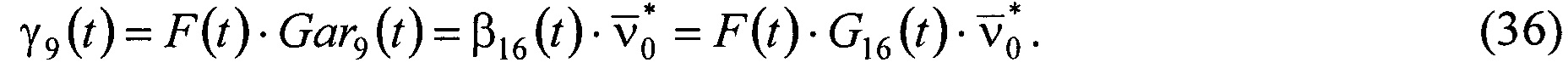

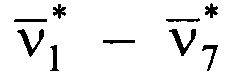

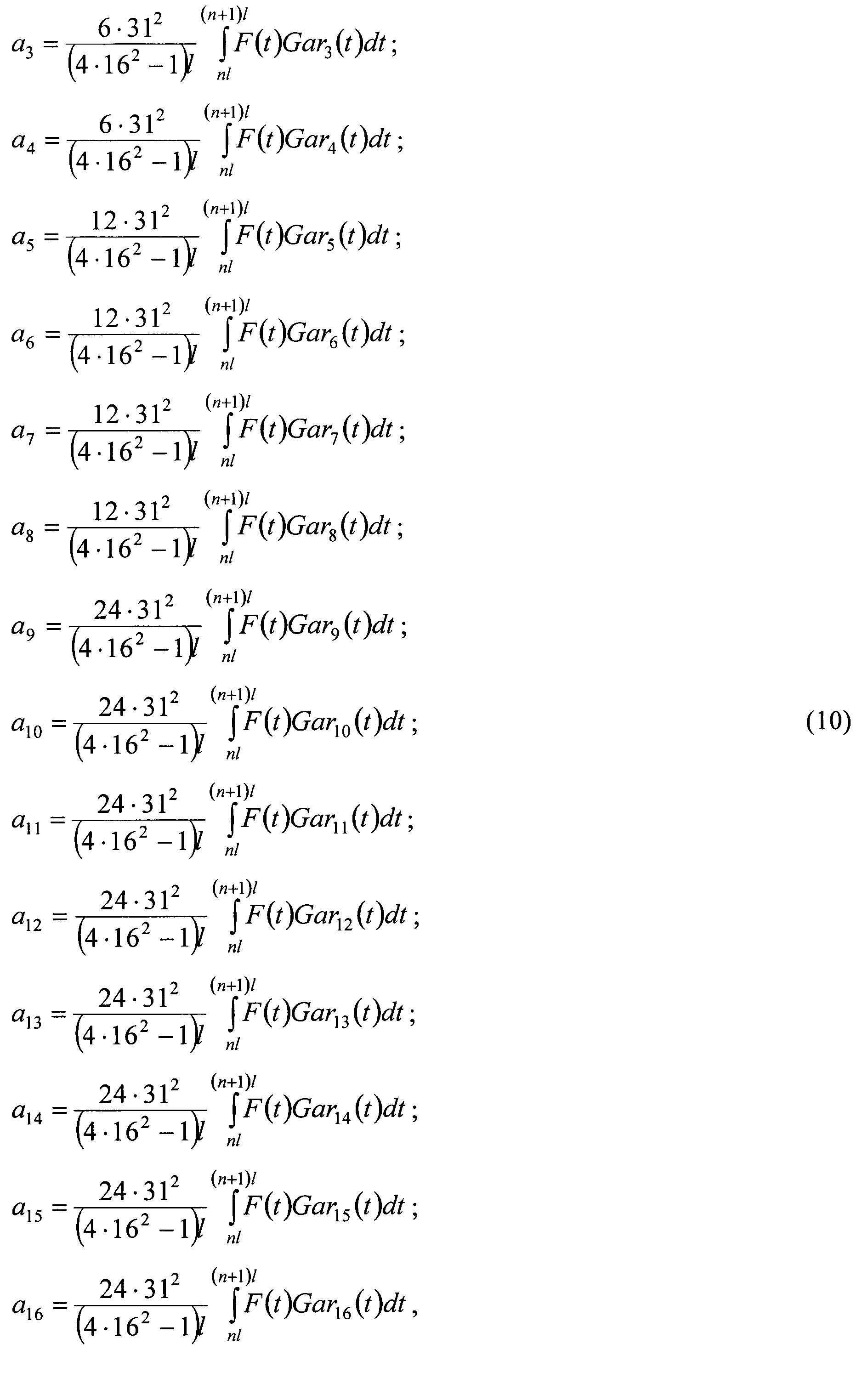

При прямом преобразовании базисные вейвлеты (9) одновременно умножают на сигнал F(t) получают 17 произведений в виде напряжений от γ0=F(t)Gar0(t) до γ16=F(t)Gar16(t), которые интегрируют; далее используя значения интегралов, вычисляют значения коэффициентов из равенств (10).

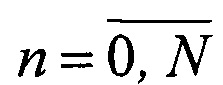

где n=0, 1, 2, ….

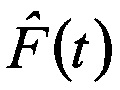

При обратном преобразовании значения коэффициентов а0-а16 в виде напряжений параллельно умножают на соответствующие базисные вейвлеты (9), полученные результаты параллельно суммируют и тем самым восстанавливают сигнал

Способ реализуется следующим образом.

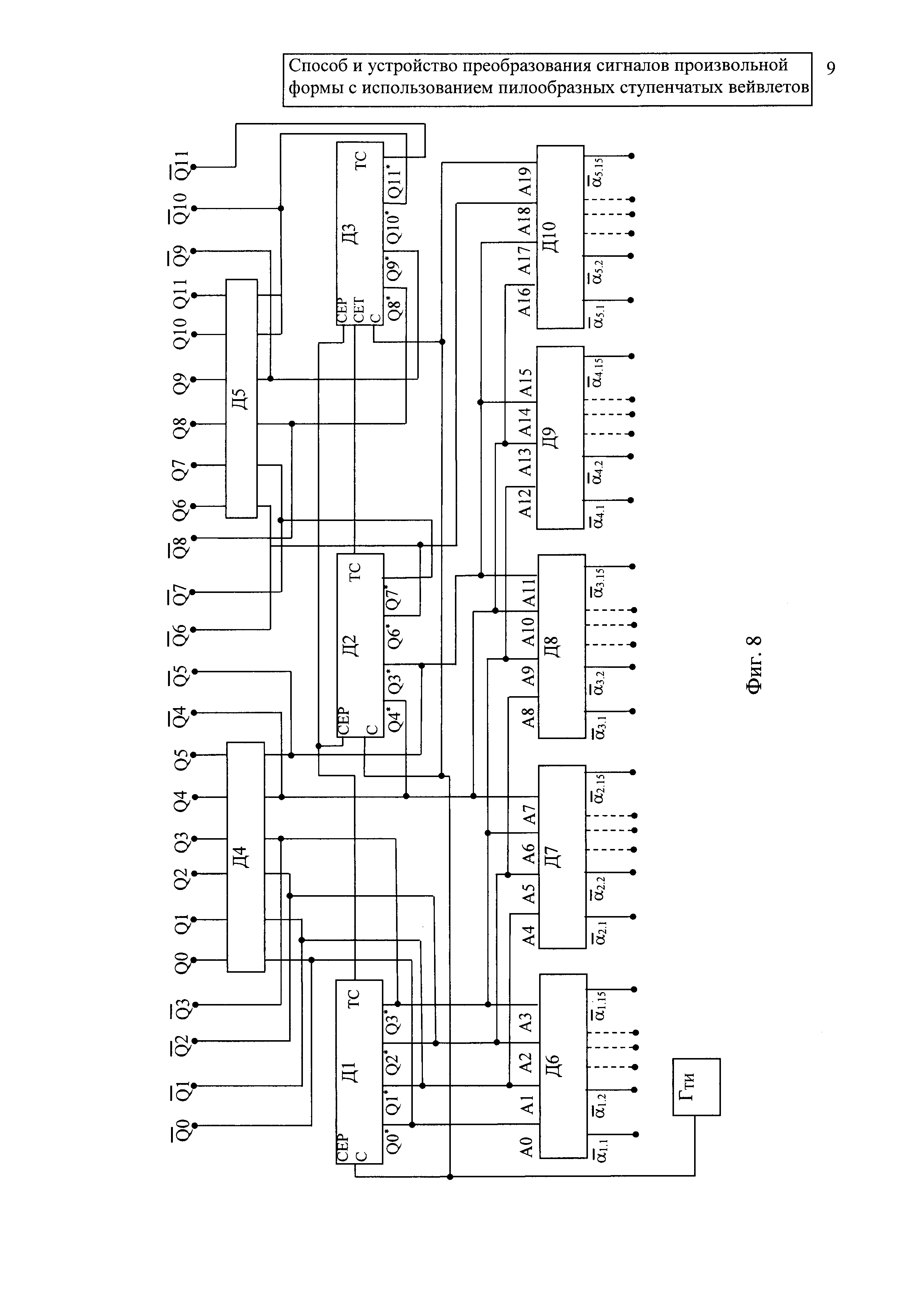

Тактовую частоту генератора ƒТ фиг. 8 делят с помощью трех последовательно соединенных синхронных двоичных счетчиков Д1, Д2, Д3 (типы К155ИЕ9) [10].

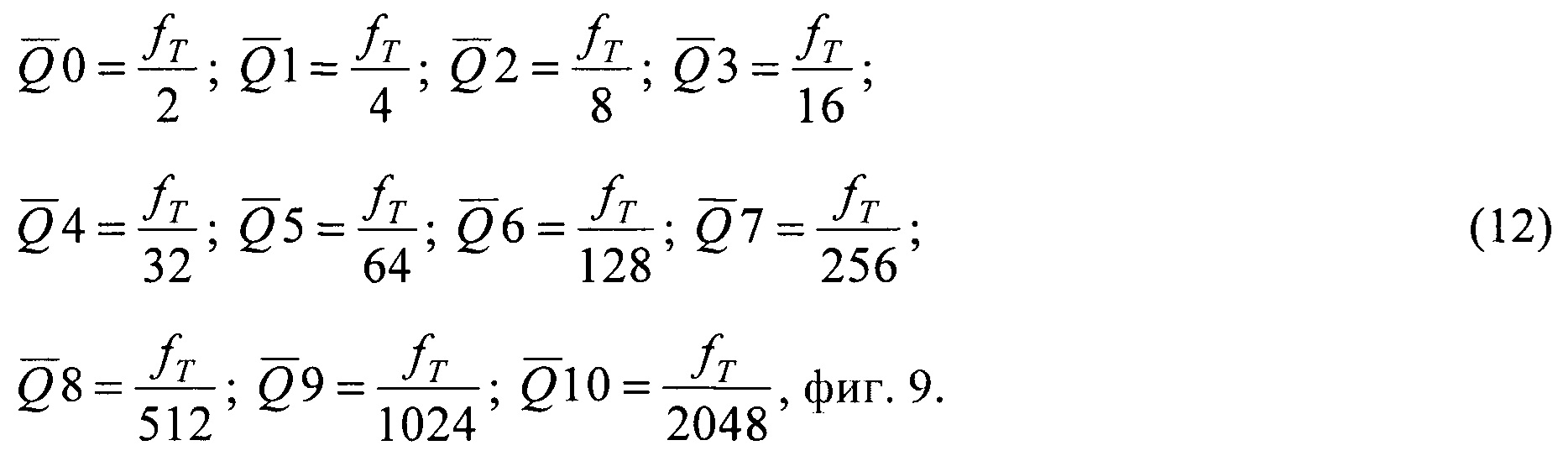

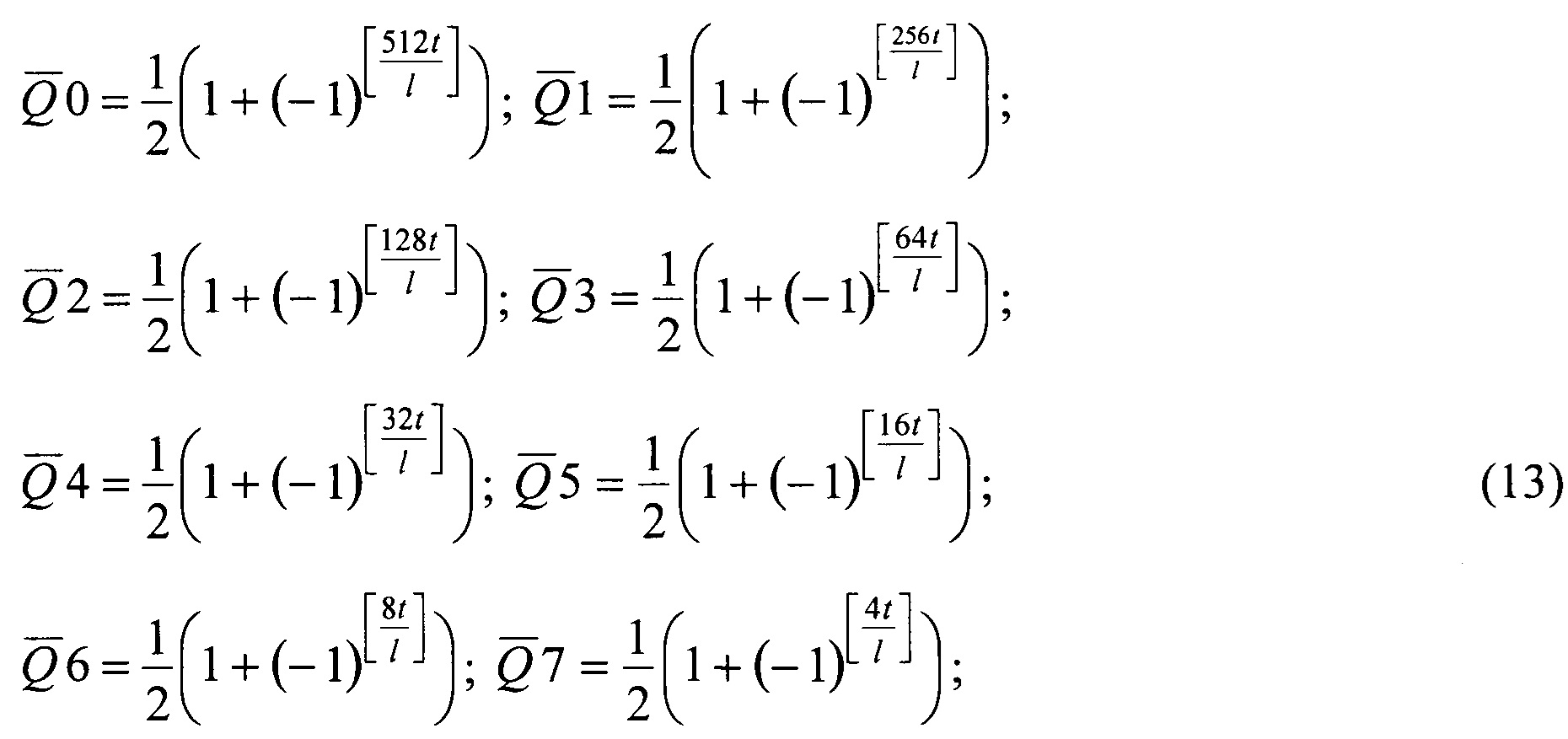

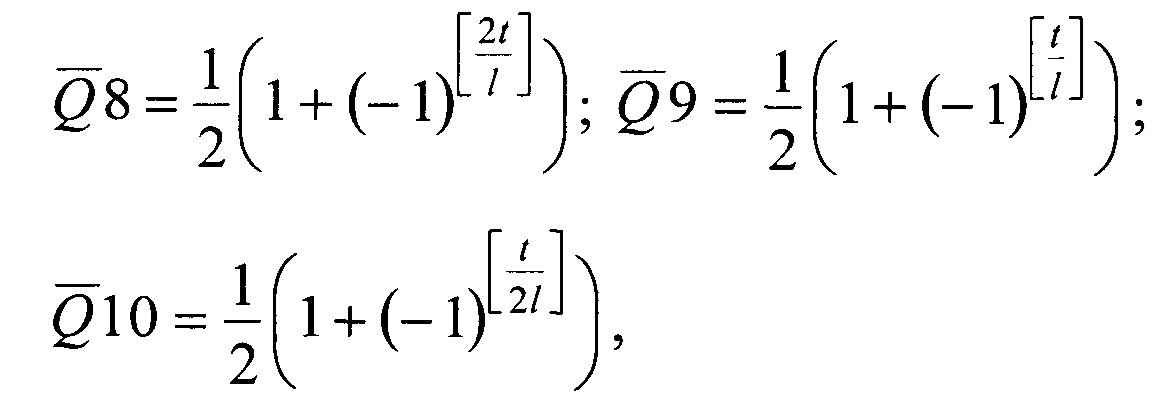

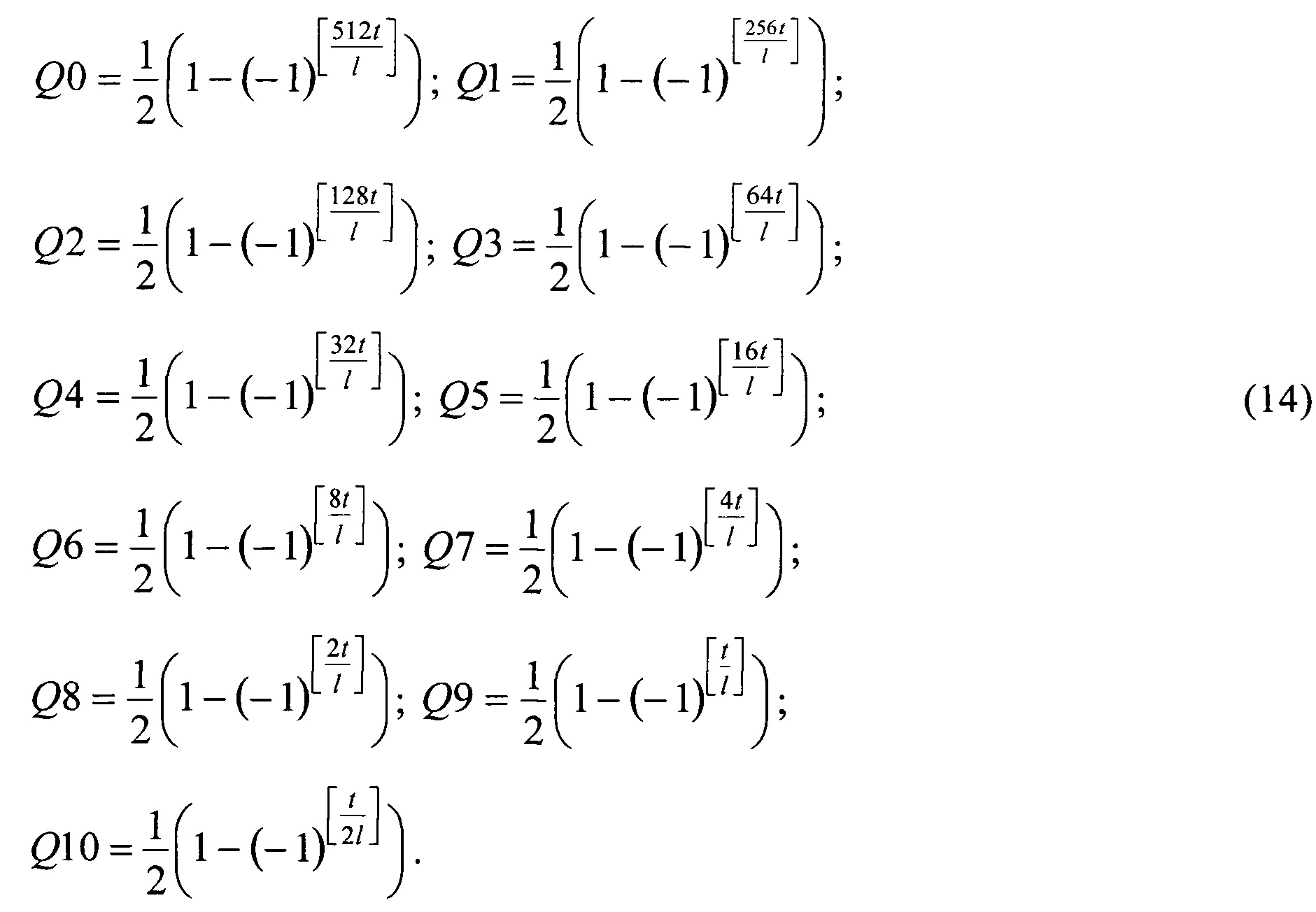

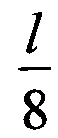

В результате деления на выходах

Формализовано эти частоты записываются в следующем виде

а их инверсии

Например, графики функций

Выходы

Кроме этого выходы

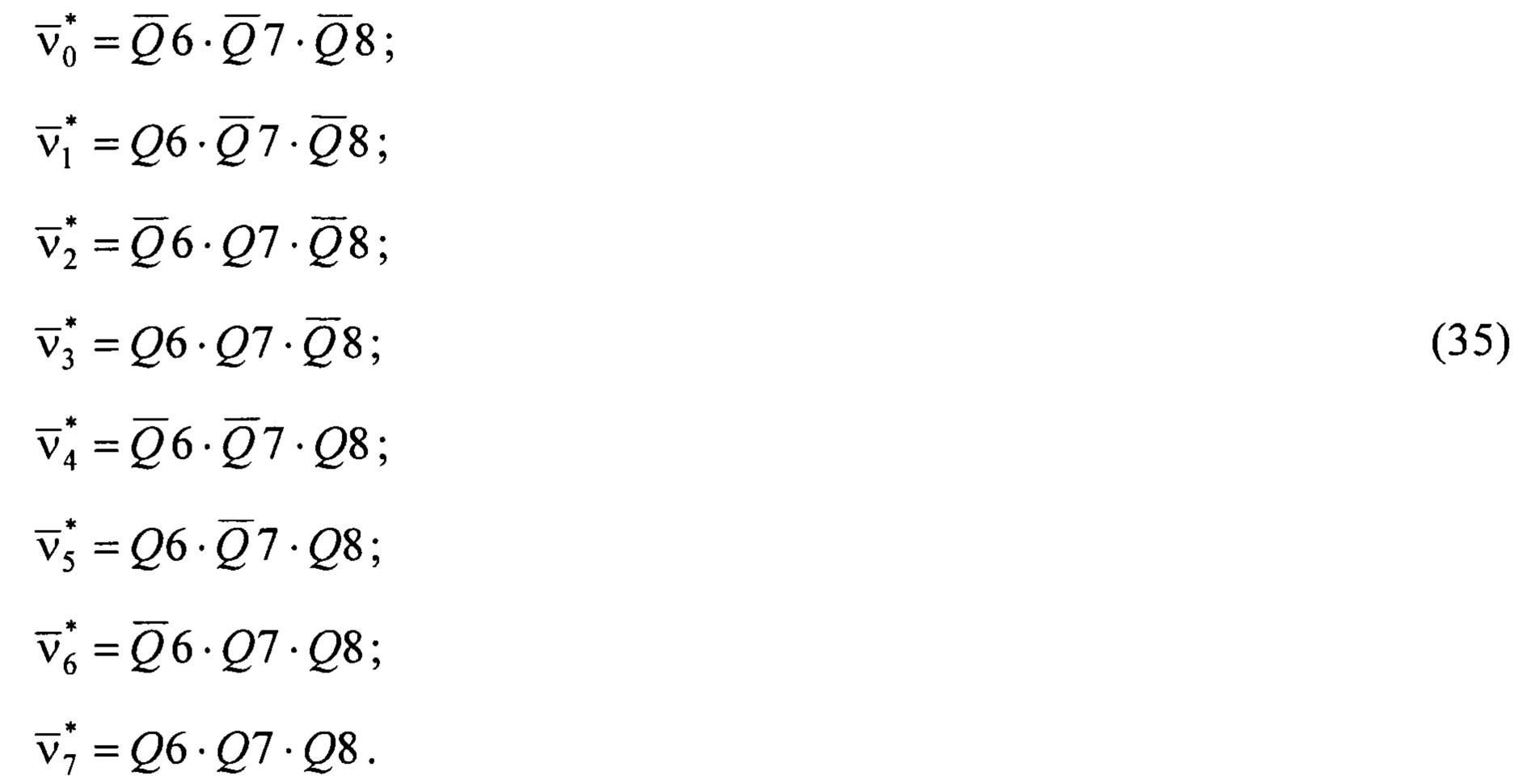

Дешифраторы Д6-Д10 четырехразрядные коды частот (12)

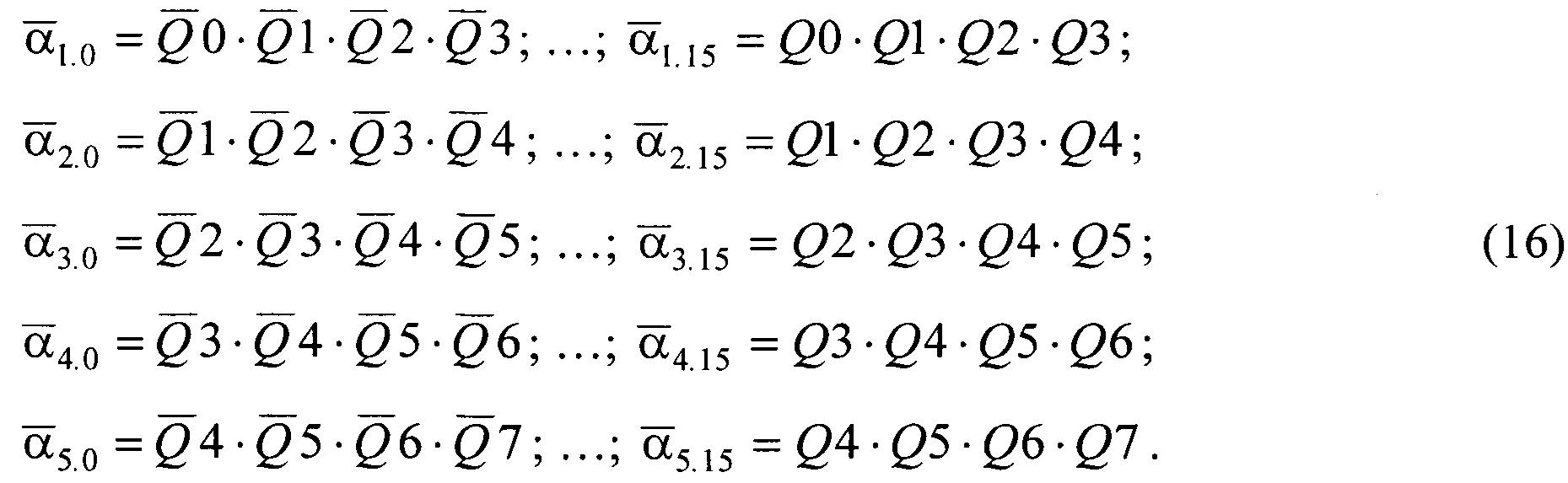

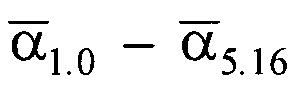

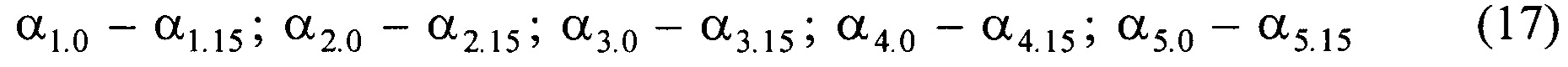

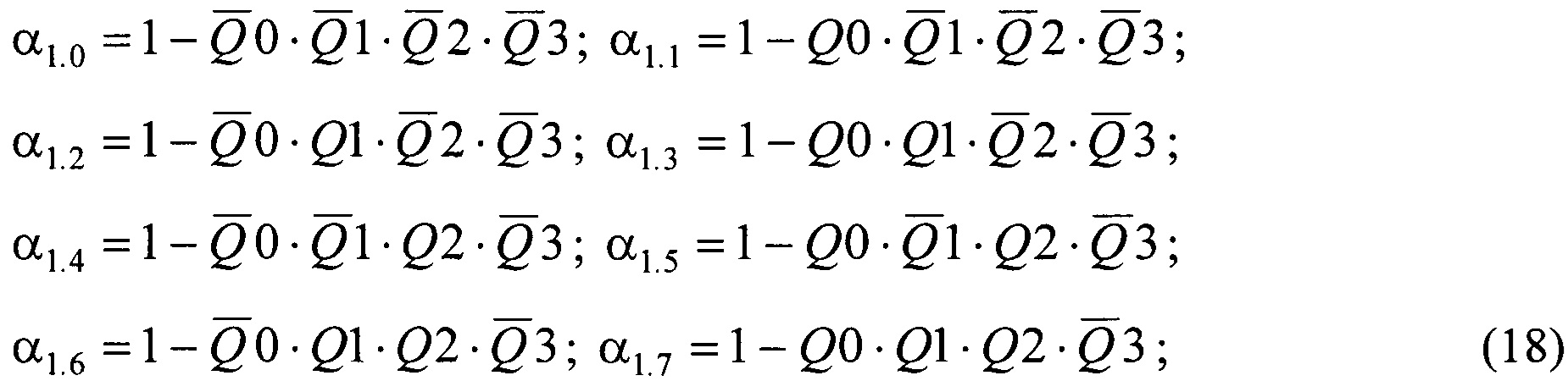

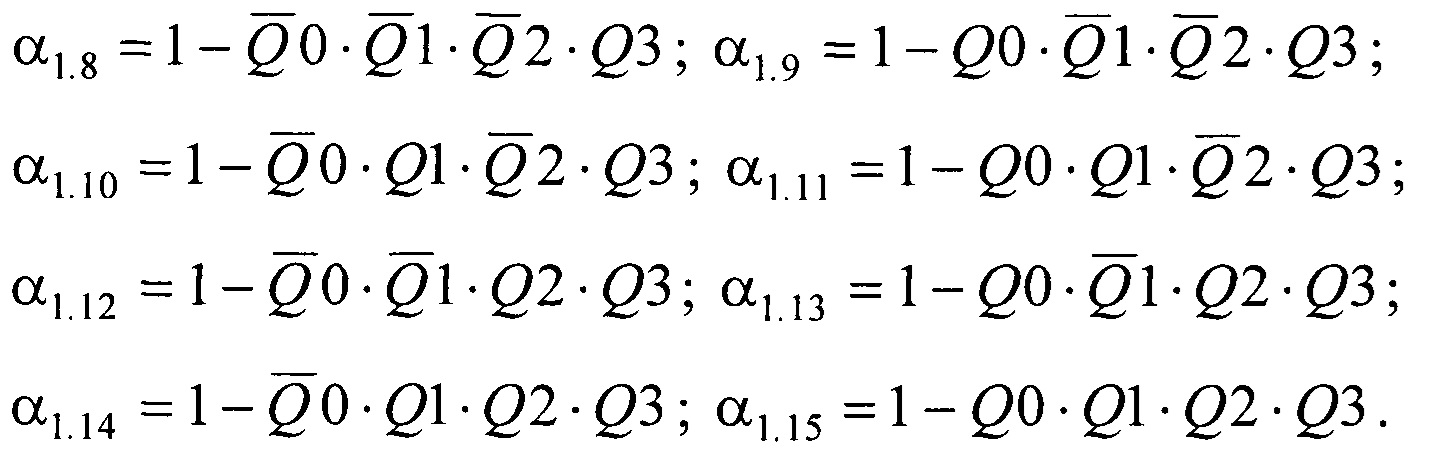

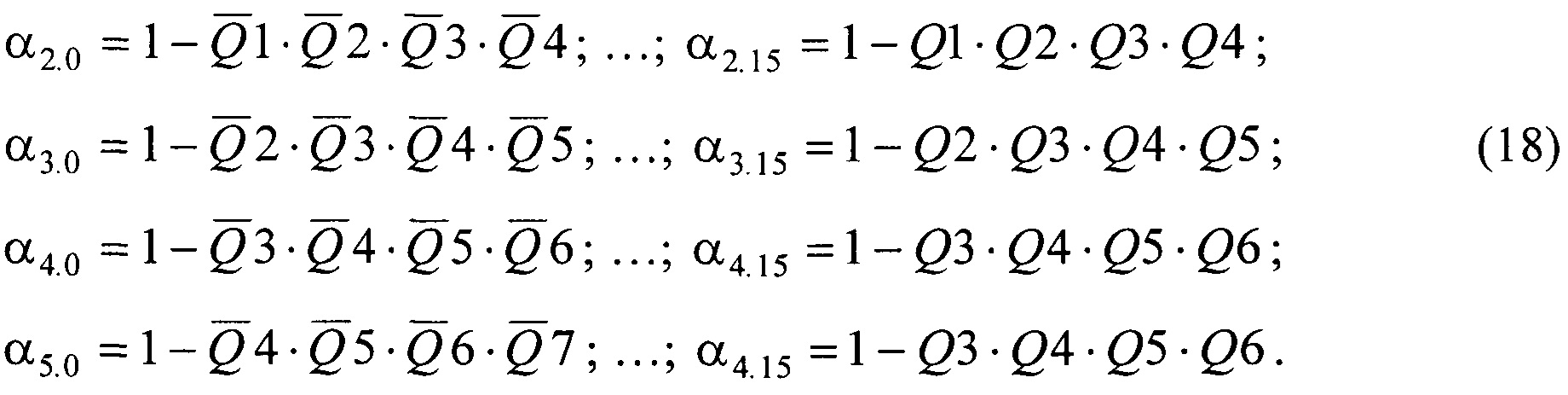

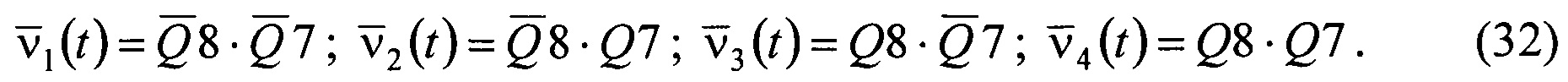

которые представляют собой логические произведения (16), (17) и (18), которые отображаются следующими равенствами:

Импульсы, формируемые делителями частоты Д1, Д2, Д3 инвертирующих схем Д4, Д5 и дешифраторов Д6-Д10, объединены в виде генератора однополярных импульсов (ГОПИ).

Выходы

фиг. 11 - фиг. 15. Однополярные импульсы МИ (17) используют для управления ключами делителей напряжений S0-S15 и S0*-S15* модулей формирования ступенчатых вейвлетов.

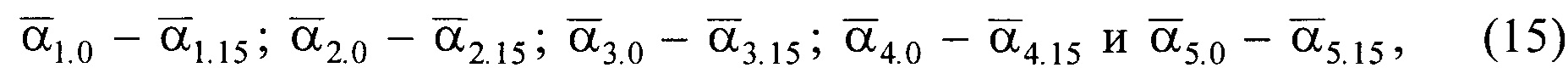

Формализовано (17) представляют в следующем виде.

Первая группа представляет собой следующие произведения:

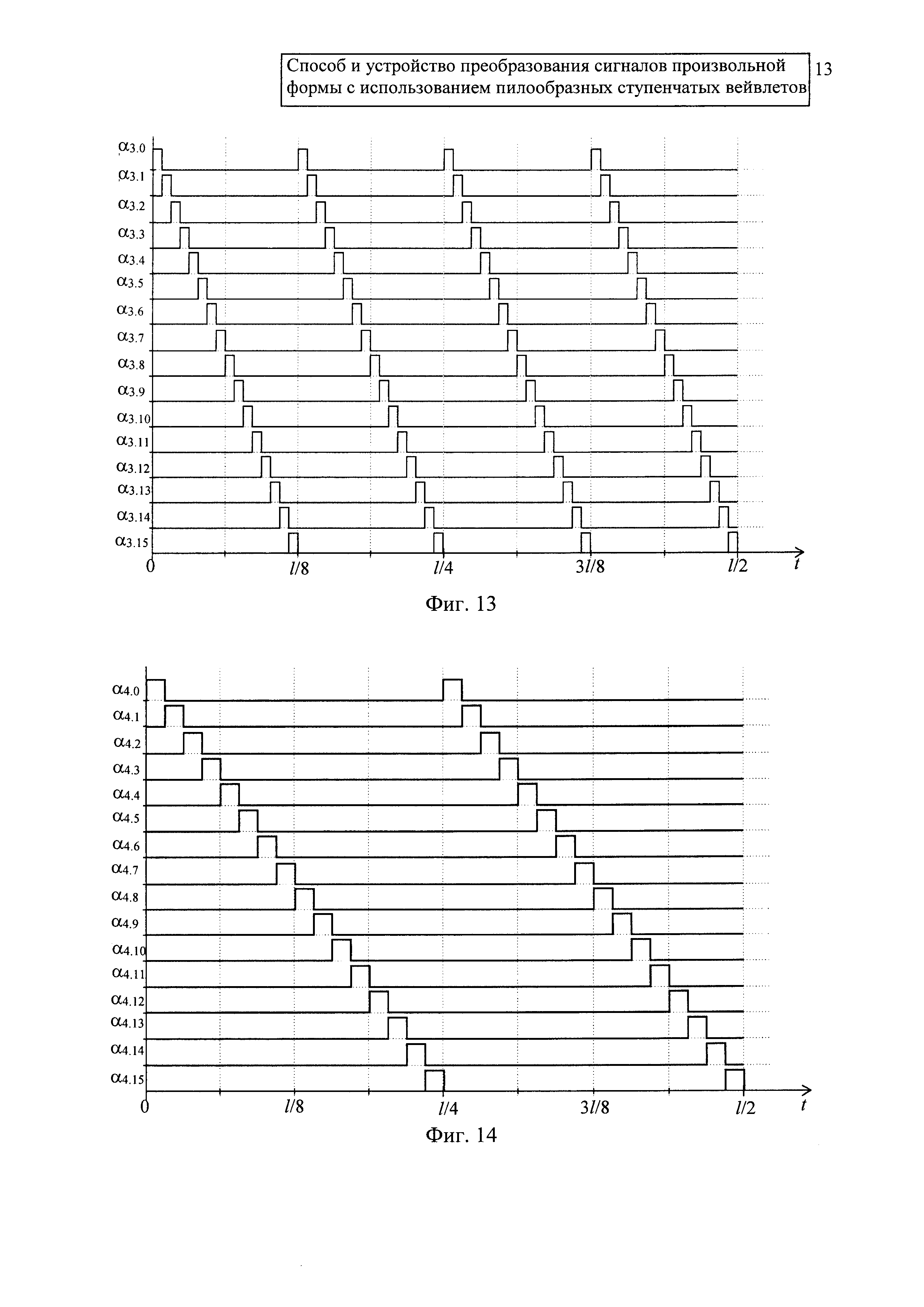

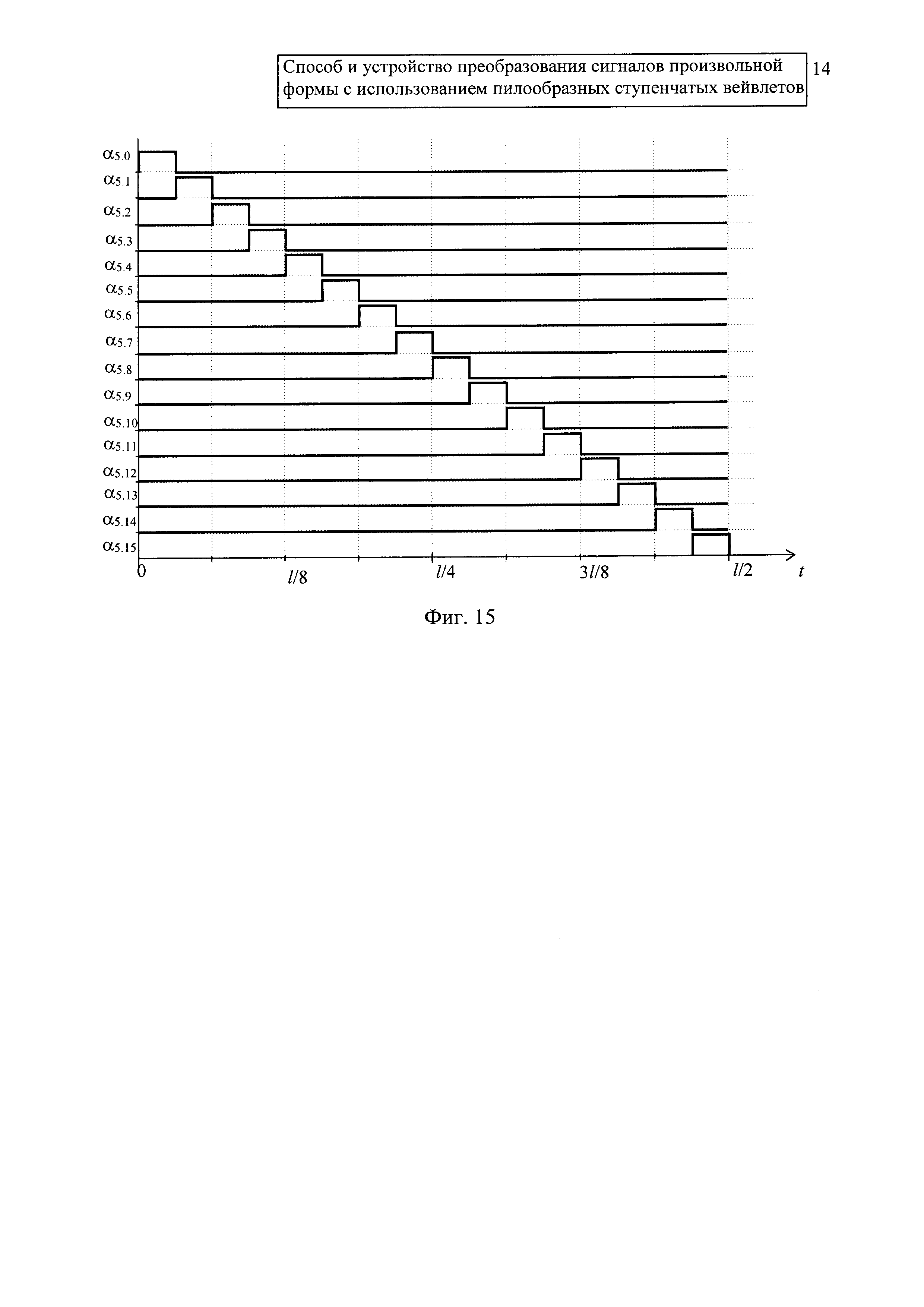

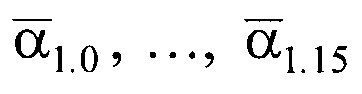

Аналогично формируются группы α2.0_α2.15; α3.0-α3.15; α4.0-α4.15 и α5.0-α5.15.

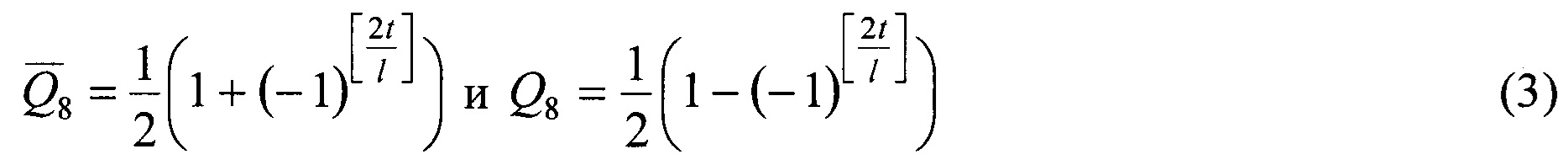

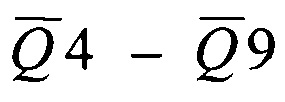

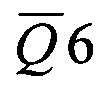

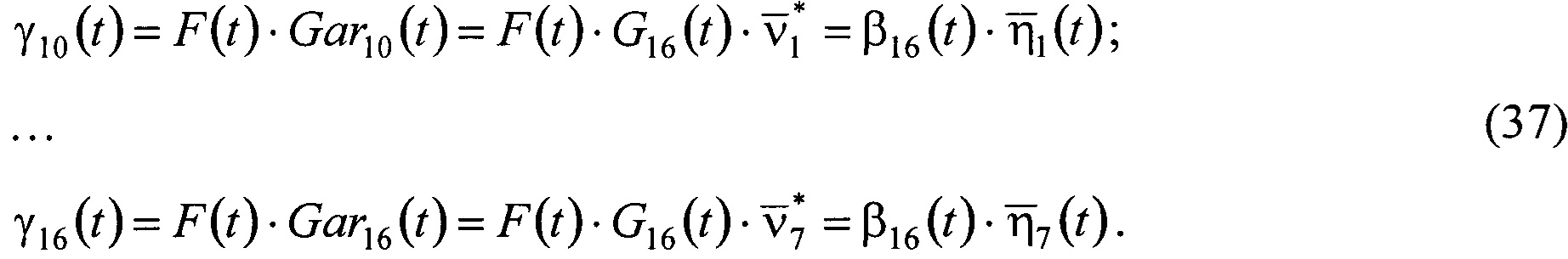

Кроме однополярных импульсов (18) для формирования ступенчатых вейвлетов (9) используют импульсы Q4-Q9 и

Сравнение двуполярных напряжений Уолша, используемые в патенте [4] для формирования пилообразных вейвлет-напряжений и напряжений однополярных импульсов фиг. 11 - фиг. 15, формируемых ГОПИ и МИ, свидетельствуют об их существенном отличии.

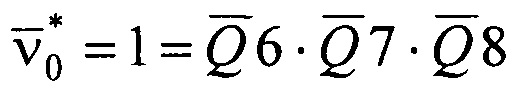

На следующем этапе, используя импульсы ГОПИ, МИ и делители напряжения, составленные из одинаковых резисторов, формируют порождающие функции изменений коэффициентов деления делителей напряжений (1).

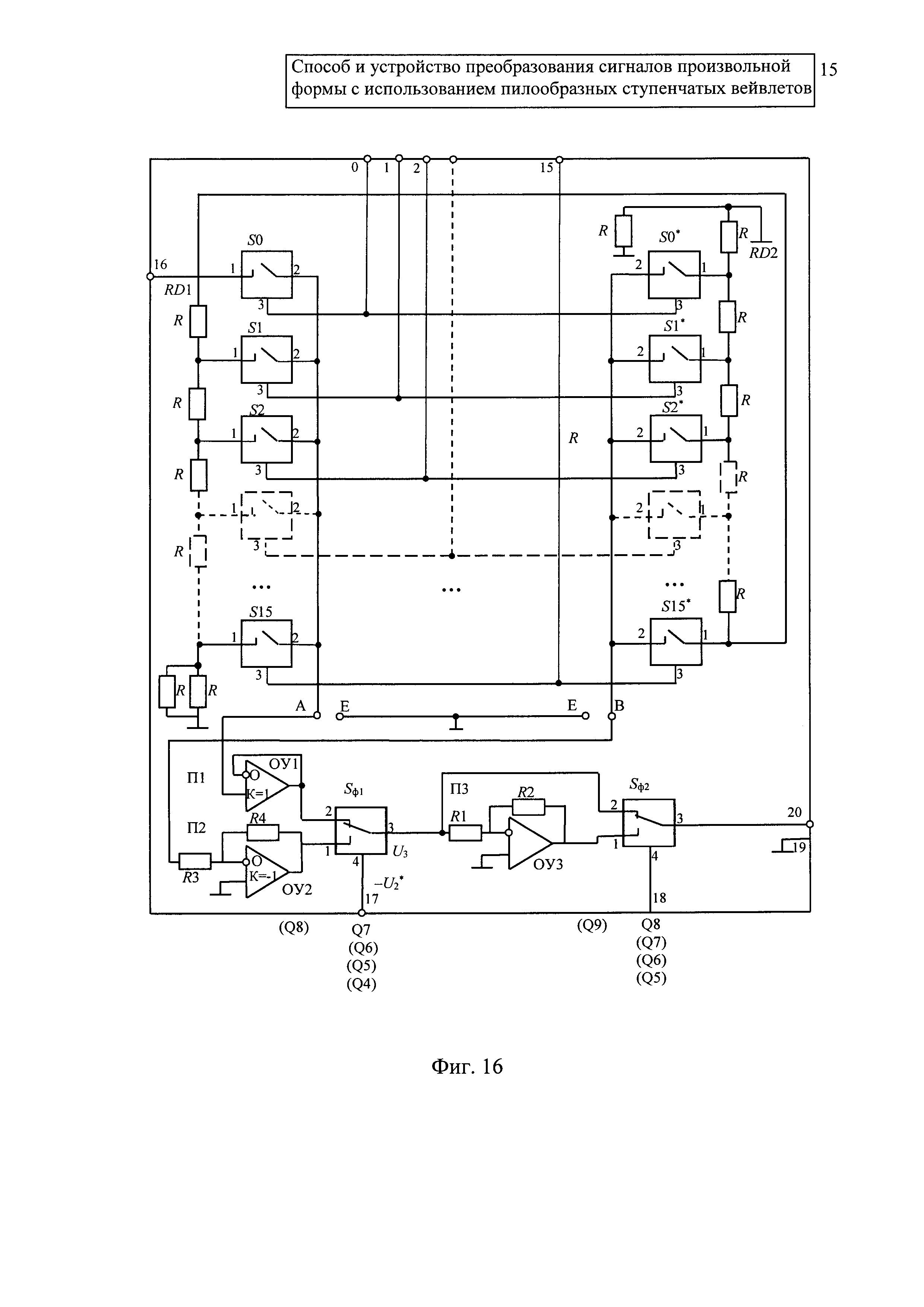

Изменение коэффициентов деления резистивных делителей реализуют схемой модуля формирования и умножения сигнала (МФУС) фиг. 16, которая включает два резистивных делителя RD1 и RD2, каждый из которых представляет собой 16 последовательно соединенных одинаковых резисторов R. Выходы А и В резистивных делителей RD1 и RD2 коммутируют последовательно во времени контактами 1 и 2 ключей S0-S15 и S0*-S15*. Для управления ключами S0-S15 и S0*-S15* входы 0-15 МФУС (типа КР590КН5 [2]) соединяют с выходами α1.0-α1.15 или α2.0-α2.15, α3.0_α3.15, α4.0-α4.15 либо α5.0-α5.15 модуля инвертирования (МИ) фиг. 16.

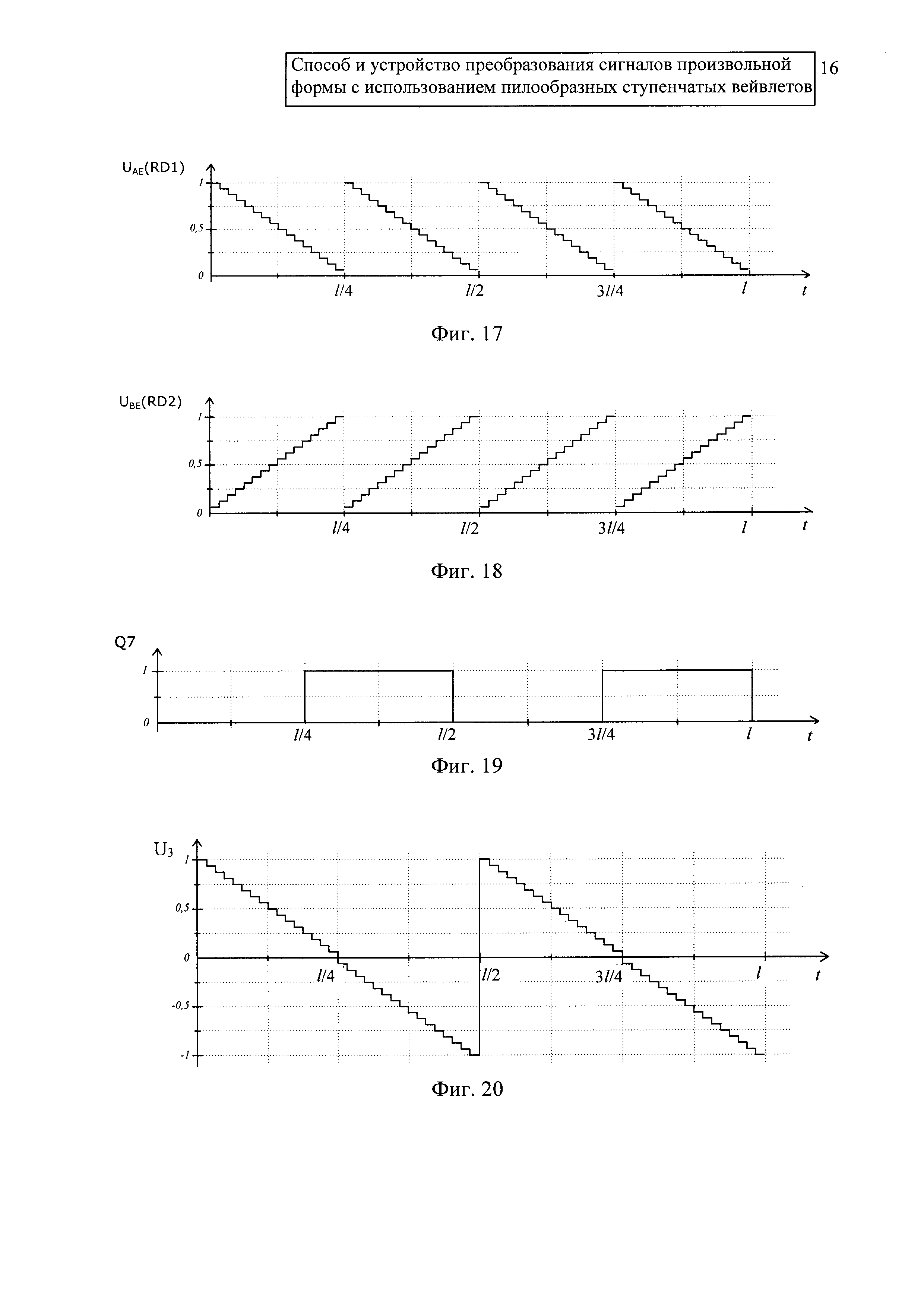

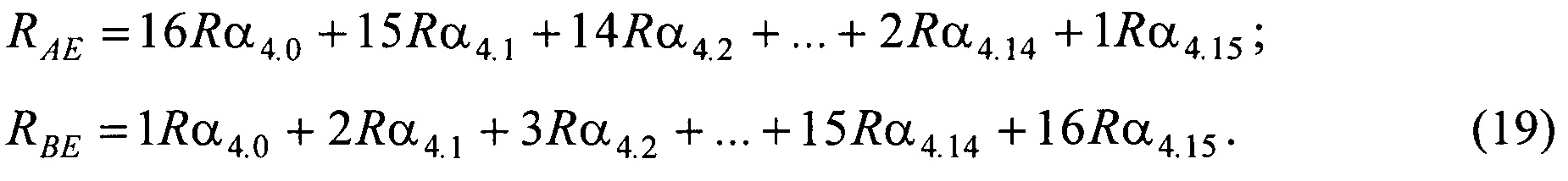

При соединении выходов а40 - а415 МИ с входами управления 3 электронными ключами от 0 до 15 на выходах делителя RD1 между точками А и Е получают ступенчатое изменение сопротивления во времени от 16R до 1R, а между точками В и Е делителя RD2 - от 1R до 16R. Графики изменения сопротивлений (напряжений) между точками А, Е и В, Е приведены соответственно на фиг. 17 и фиг. 18.

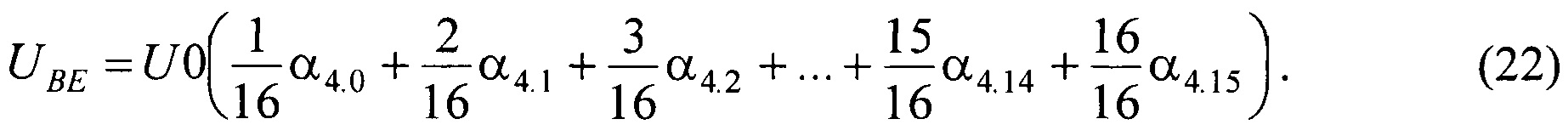

Формализованное описание изменений сопротивлений делителей RD1 и RD2 между точками А, Е и В, Е с учетом напряжений управления α4.0-α4.15 ключами S0-S15 и S0*-S15* отображают следующими равенствами:

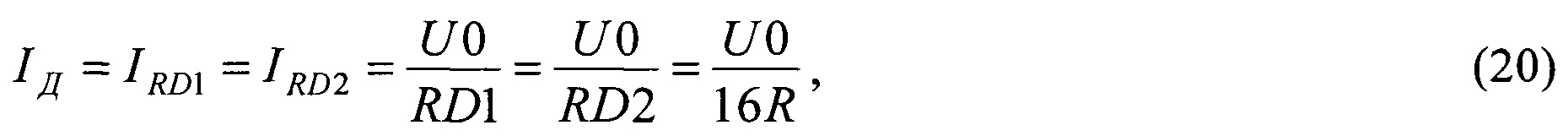

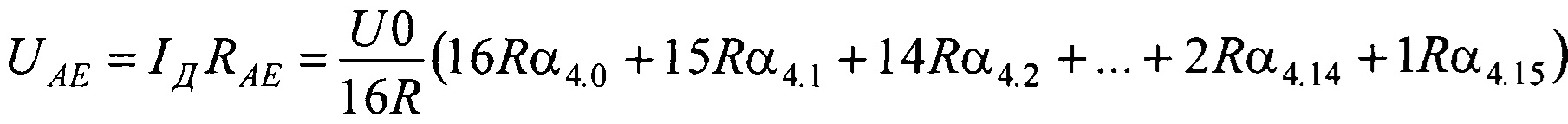

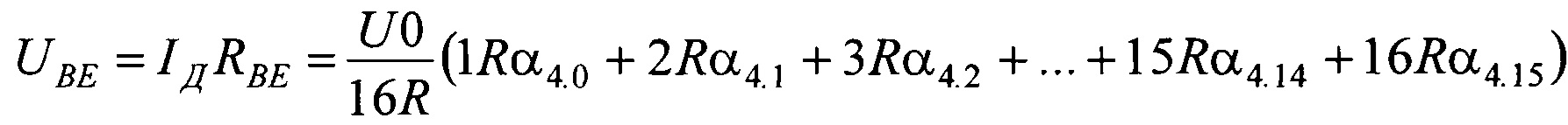

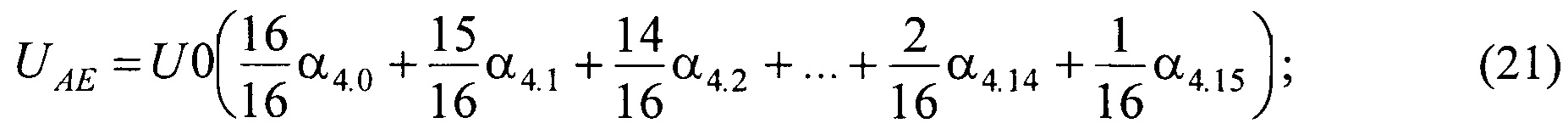

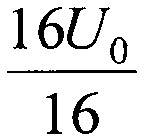

Для последовательного формирования изменения коэффициентов деления резистивных делителей напряжений в соответствии с порождающими функциями (1) вход 16 модуля формирования умножения (МФУС) соединяют с источником постоянного напряжения U0 фиг. 16. В результате этого в каждом из делителей RD1 и RD2 протекает ток:

а на выходах делителей после коммутации во времени получают напряжения:

или

Из (21) и (22) очевидно, что выходные напряжения UAE и UBE являются произведениями напряжений U0 на коэффициенты деления делителей RD1 и RD2 (21) и (22).

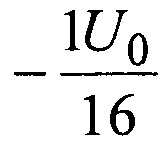

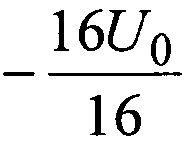

Для формирования двуполярных ступенчатых пилообразных напряжений, изменяющихся ступенчато от

На всей оси времени с помощью ключа SФl формируют двуполярное ступенчатое напряжение U3 фиг. 20.

Для формирования двуполярного напряжения, изменяющегося аналогично G2(t), используют повторитель П3 на базе операционного усилителя ОУ3 с коэффициентов передачи минус 1 фиг. 16 и ключ SФ2. Контакт 2 ключа SФ2 соединяют с выходом 3 ключа SФl. Вход 1 ключа SФ2 соединяют с выходом операционного усилителя ОУ3. Вход 4 управления ключа SФ2 соединяют с выходом Q8 ГОПИ. На промежутках

Для уменьшения ступеньки фиг. 12 в точках перехода функцией оси времени и приведения к функциям (9) параллельно резисторам, соединенных с общей точкой, подключают резисторы такой же величины, что и в делителях, см. фиг. 16 формируют напряжения

η0(t)=U0G2(t)=U0Gar2(t).

Далее источник напряжения U0 на входе 16 МФУС (см. фиг. 16) заменяют на источник сигнала F(t). На выходе 20 МФУС получают напряжение, пропорциональное произведению сигнала F(t) на изменение коэффициентов деления делителей RD1 и RD2

Сравнивая схемы формирования ступенчатых вейвлетов (9) фиг. 16 со схемой формирования базисных функций в прототипе [4] находим, что схемы фиг. 16 в предлагаемом формирователе не содержат интегрирующих и стабилизирующих элементов рабочих напряжений.

Для формирования произведения сигнала F(t) на порождающие функции G1(t), G4(t), G8(t) и G16(t) из (1) используют еще четыре модуля МФУС, фиг. 23.

Для формирования произведения

входы МФУ1 0, 1, 2, …, 15 соответвенно соединяют с выходами α5.0, …, α5.15 МИ вход 16 соединяют с выходом источника сигнала F(t), а входы 17 и 18 МФУС соединяют с выходами Q8 и Q9. На выходе 20 получают напряжение сигнала, умноженного на Gar1(t), фиг. 23.

Для формирования произведения

входы МФУС 0, 1, 2, …, 15 соответственно соединяют с выходами α3.0, …, α3.15 МИ, вход 16 соединяют с выходом источника сигнала F(t), а входы 17 и 18 МФУ1 соединяют с выходами Q6 и Q7 ГОПИ, фиг. 23.

Для формирования произведений сигнала F(t) на изменяющиеся коэффициенты деления делителей напряжений

входы 0, 1, 2, …, 15 МФУ соединяют соответственно с выходами α2.0, α2.1, …, α2.15 МИ, а входы 17 и 18 МФУ соответственно с выходами ГОПИ Q5 и Q6.

Формирование произведений сигнала F(t) на изменения коэффициентов деления делителей напряжений

выполняют следующим образом: входы 0, 1, 2, …, 15 МФУС соединяют соответственно с выходами α1.0, α1.1, …, α1.15 МИ, а входы 17 и 18 с выходами Q4 и Q5 ГОПИ.

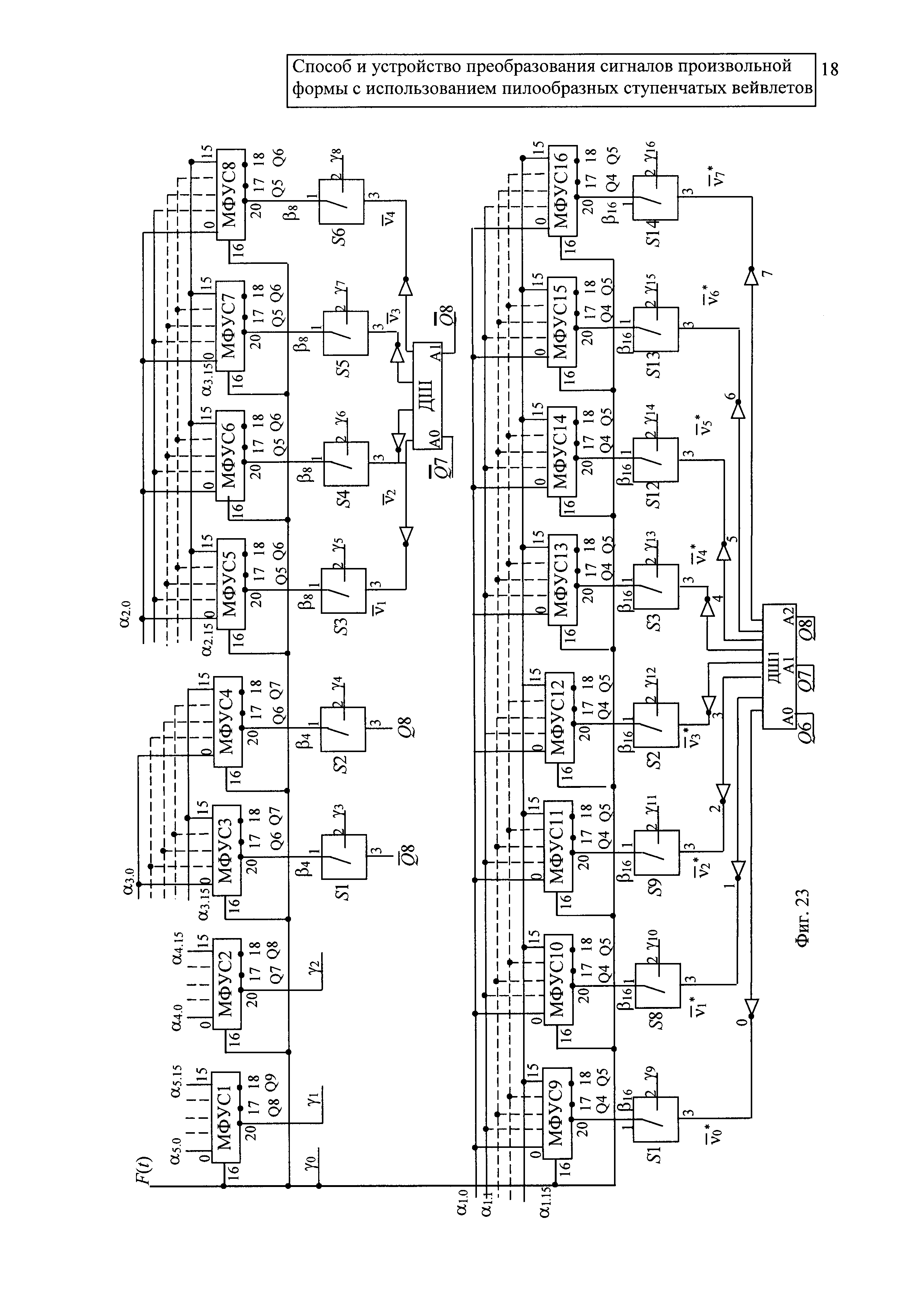

Для параллельного формирования произведений сигнала F(t) на ступенчатые вейвлеты (9) используют 16 одинаковых модулей формирования и умножения МФУС1 - МФУС16, 14 ключей S1-S14, два дешифратора и инвертирующие схемы, которые объединяют в блок формирования ступенчатых вейвлетов и умножения сигнала (БФСВУС) фиг. 23.

Для формирования произведения сигнала F(t) на пилообразные ступенчатые вейвлеты G1(t) и G2(t) из (1) входы 17 и 18 МФУС1 соединяют с Q8 и Q9, а входы 17 и 18 МФУС2 с выходами Q7, Q8. Входы 0-15 модуля МФУС1 соединяют соответственно с выходами модуля инверторов МИ α5.0, …, α5.15, а входы 0-15 МФУС2 соединяют с выходами α4.0, …, α4.15 МИ в результате этих соединений на выходах 20 модулей МФУС1 и МФУС2 в соответствии с (23) и (24) формируют

которые сохраняют без изменений.

Входы 0-15 двух модулей МФУС3 и МФУС4 соединяют попарно параллельно и соединяют с выходами α3.0, …, α3.15 МИ фиг. 23. Входы 17 и 18 этих модулей соединяют попарно параллельно и соединяют с выходами Q6 и Q7, на выходах 20 модулей МФУ1 и МФУ2 формируют два одинаковых произведения сигнала и порождающей функции G4 (t).

Выход 20 МФУС3 фиг. 23 соединяют с контактом 1 ключа S1, аналогично выход 20 МФУС4 соединяют с контактом 1 ключа S2. Вход 3 управления 3 ключа S1 соединяют с выходом

При

на промежутках

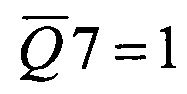

При Q8=1 на промежутках

Далее входы 0-15 четырех модулей МФУС5 - МФУС8 по четыре соединяют параллельно и соединяют с выходами

Входы 17 и 18 этих модулей также соединяют по четыре и соединяют с выходами Q5 и Q6 ГОПИ. На выходах 20 МФУС5 - МФУС8 формируют четыре одинаковых произведений сигнала F(t) и порождающие напряжения G8(t):

Выходы 20 МФУ5 - МФУ8 соединяют соответственно с входами 1 ключей S3-S6.

Входы 3 управления ключей S3-S6 через инверторы соединены с выходами дешифратора ДШ (тип К513НД14), входы А0 - А1 которого подключают к выходам

На выходах дешифратора ДШ через инверторы формируют четыре сдвинутых одиночных импульса:

фиг. 6.

При

Аналогично на входы управления 3 ключей S4-S6 поступают управляющие напряжения

На выходах 2 ключей S4-S6 соответственно формируют произведения:

Для формирования следующих произведений входы 0-15 модулей МФУС9 - МФУС16 параллельно соединяют по восемь и затем их соединяют с выходами

На выходах 20 МФУС9 - МФУС16 формируют восемь произведений сигнала F(t) на порождающую функцию G16(t).

β16=F(t)⋅G16(t).

Входы управления 3 ключей S7-S14 через инверторы соединяют с выходами дешифратора ДШ1 фиг. 23 (типа К155ИД7). Входы А0, А1 и А2 дешифратора ДШ1 соединяют с выходами

При

Аналогично под воздействием управляющих напряжений

В результате выполненных соединений фиг. 23 и воздействия управляющих напряжений на выходах γ1-γ16 блока формирования ступенчатых вейвлетов и умножения на сигнал (БФСВУС) фиг. 23 формируют все 16 произведений сигнала F(t) на пилообразные ступенчато изменяющиеся коэффициенты деления делителей напряжений (28), (29), (30), (33), (34), (36) и (37).

Известны устройства, реализующие преобразования Уолша, Хаара и с использованием пилообразных напряжений [2, 3, 4].

В [2], рис. 2.1.3-8 на стр. 162 представлено устройство, полностью реализующее операции преобразования Уолша и Хаара в виде секвентного фильтра общего вида.

В [3] представлено устройство, реализующее использование ортогональных пилообразных напряжений.

В способе и устройстве, представленных в [5], предложены решения, направленные на сокращение объема вычислений за счет изменения шага дискретизации, а в [6] предложены решения на уменьшение числа модулей и их связей в устройстве.

В предлагаемом устройстве с использованием пилообразных ступенчатых вейвлетов в виде изменяющихся коэффициентов деления резистивных делителей напряжений, как следует из [2, 3, 4], последовательности операций в устройствах преобразования сигнала сводятся к умножению сигнала на базисные функции в виде напряжений, интегрирования напряжений произведений, используя значения интегралов, вычисление коэффициентов аналогично в предлагаемом устройстве (9), (10) и (11).

В связи с тем, что в устройстве преобразования [3] используют порождающие пилообразные напряжения с числами секвент 2, 4 и 8, которые по характеру изменения и числу секвент, аналогичных изменениям ступенчатым порождающим вейвлетом (1), устройство [3], как наиболее близкое к устройству, реализующему (9), (10), выбрано в качестве прототипа.

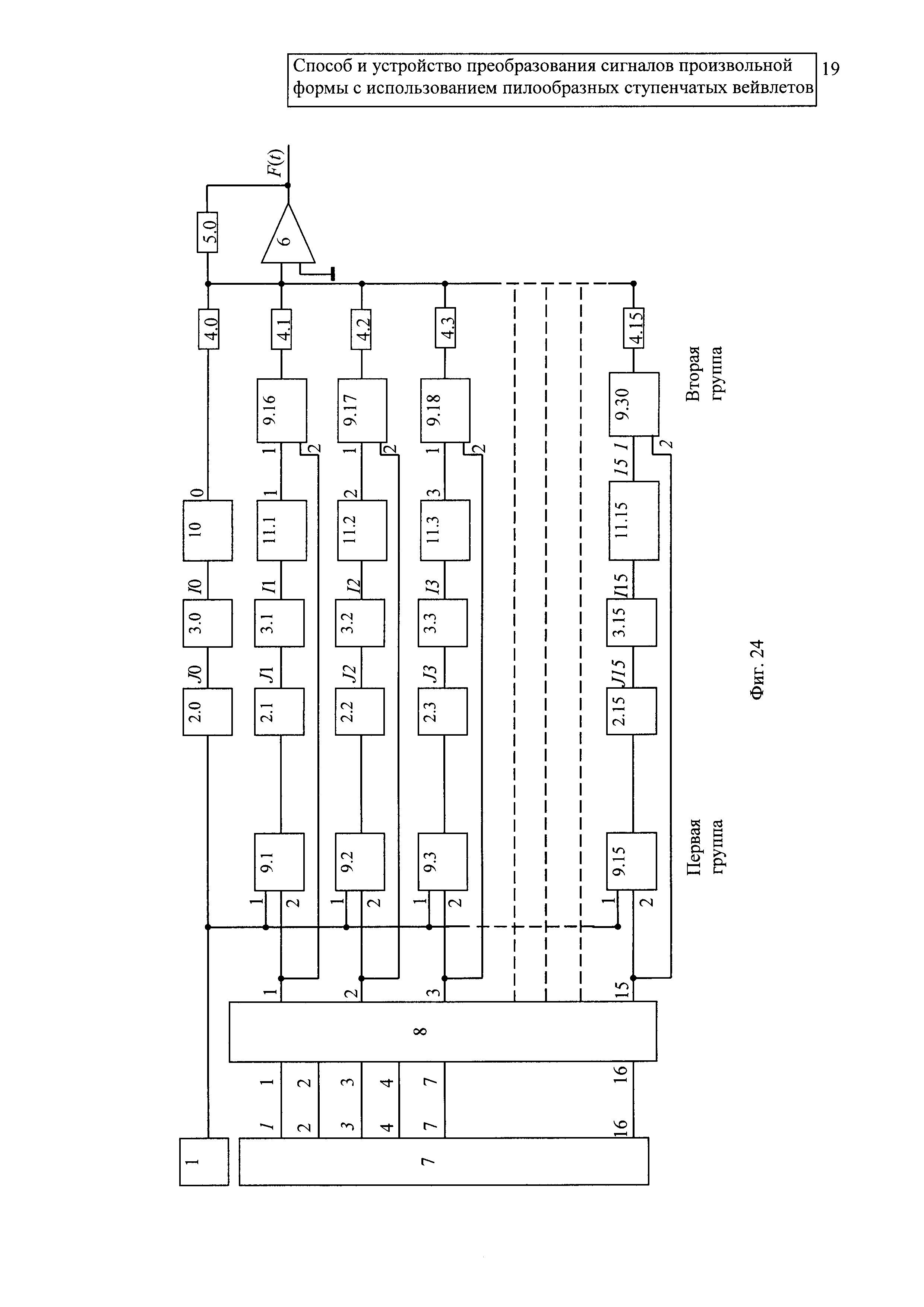

Схема устройства - прототипа [3] преобразования сигнала произвольной формы с использованием ортогональных пилообразных напряжений включает следующие блоки, их связи:

1 - источник сигнала;

2.0-2.15 - интеграторы;

3.0-3.15 - отсчитывающие и запоминающие устройства;

4.0-4.15 и 5.0 - резисторы сумматоров напряжений;

6 - операционный усилитель;

7 - генератор напряжений Уолша:

8 - формирователи ортогональных пилообразных напряжений;

9.0-9.30 - схемы умножения двух одновременно изменяющихся напряжений;

10, 11.1-11.15 - блоки вычисления коэффициентов преобразования по пилообразным напряжениям.

В схеме генератора напряжений Уолша 7 выходы 1-16 соединяют с одноименными входами формирователя ортогональных пилообразных напряжений 8, а выходы блока 8 соединяют с входами 2 умножителей 9.1-9.15 первой группы, а входы 1 с выходом источника сигнала, выходы умножителей соединяют с входами интеграторов 2.0-2.15, а их выходы I0-I15 соединяют с одноименными входами отсчитывающих и запоминающих схем 3.0-3.15. Входы последних I0-I15 соединяют с входами схем вычисления коэффициентов преобразования 10.0; 11.1-11.15, в результате этого завершают этап прямого преобразования.

Для обратного преобразования выходы 0-15 схем вычисления коэффициентов преобразования 10.0; 11.1-11.15 соединяют с одноименными входами 1 схем умножения второй группы 9.16-9.30, а входы 2 схем умножения соединяют с выходами формирователя ортогональных пилообразных напряжений 8.

В результате параллельного умножения 16 коэффициентов в виде напряжения на ортогональные пилообразные напряжения, а также параллельного суммирования с помощью сумматора 4.0-4.15; 5.0 и 6 на выходе восстанавливают сигнал

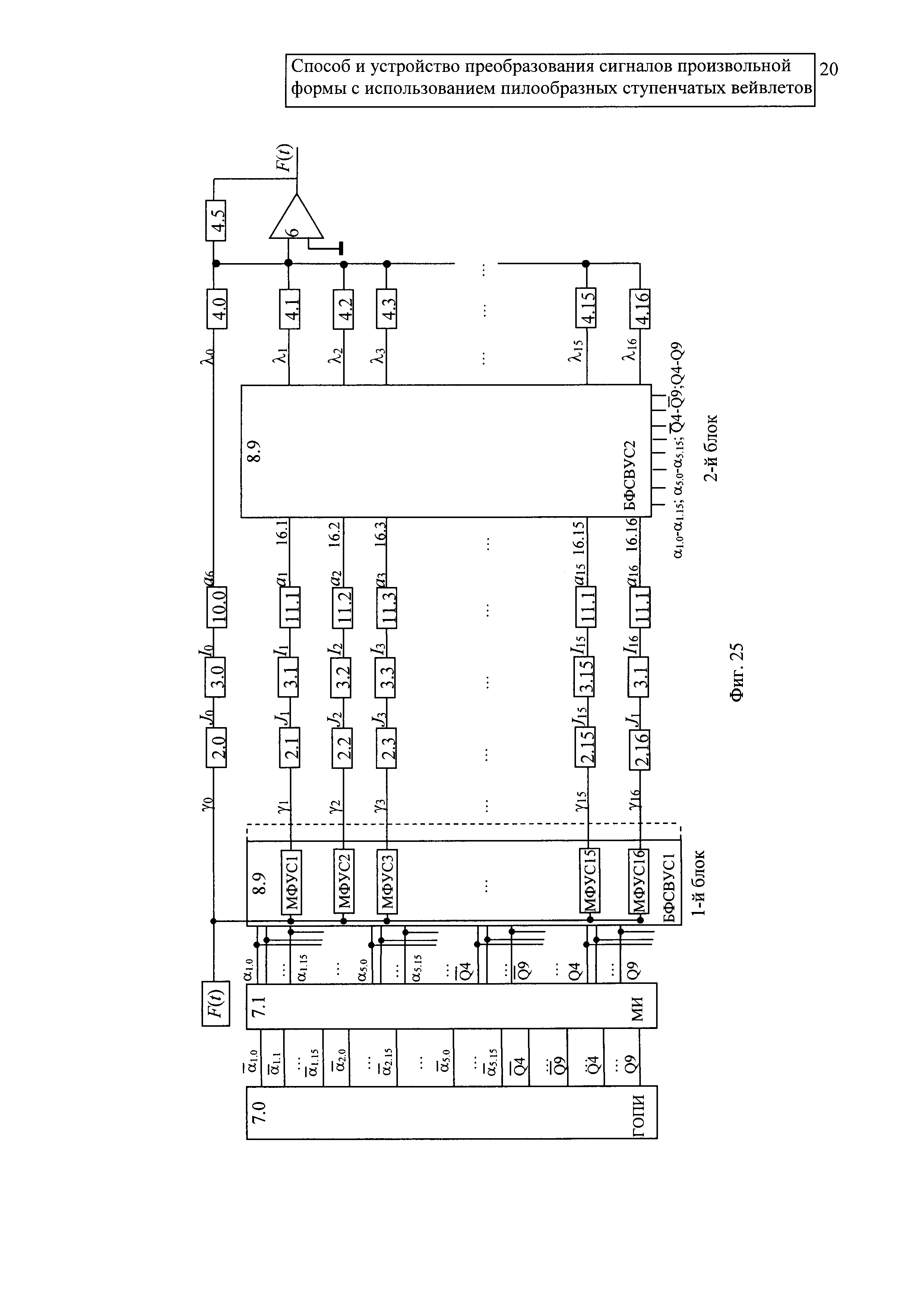

Для выполнения преобразования с использованием пилообразных ступенчатых вейвлетов в соответствии с (9)-(11) в схеме секвентного фильтра фиг. 24 (фиг. 5 прототип):

- исключены схема умножения 9.1-9.30 типа AD539, так как в предлагаемом устройстве в модулях формирования пилообразных ступенчато изменяющихся коэффициентов деления делителей напряжения МФУС1-МФУС16 см. фиг. 23 совмещается операция формирования ступенчатых вейвлетов и операция умножения на сигнал фиг. 16;

- формирователи пилообразных напряжений 8 в [3] с использованием интеграторов на операционных усилителях заменены на модули формирования и умножения фиг. 16;

- генератор 7 двуполярных напряжений Уолша схема фиг. 24 заменен на генератор однополярных прямоугольных импульсов ГОПИ 7.0, фиг. 8, и модуль инвертирования МИ 7.1 фиг. 10, которые формируют пять последовательностей однополярных импульсов управления ключами делителей напряжений фиг. 11 - фиг. 15 (17) и три последовательности однополярных импульсов фиг. 5 - фиг. 7 формирования вейвлетов Gar3(t) - Gar16(t).

В предлагаемом устройстве выходы

Входы 16.1-16.16 модулей МФУС1-МФУС16 первого блока БФСВУС 1 параллельно соединяют с выходом источника сигнала 1. Выходы γ1-γ16 БФСВУС 1 соединяют с входами интеграторов 2.1-2.16. Входы 16.1-16.16 второго БФУСВ 8.9 соединяют соответственно с выходами блоков вычисления коэффициентов a1-a16.

Все остальные блоки секвентного фильтра прототипа (фиг. 5) фиг. 24 и их связи используются без изменений:

блоки интегралов 2.0 - 2.16 тождественные блокам I0-Is; блоки отсчитывания и запоминания 3.0-3.16 тождественные блокам Н0-Hs; блоки 4.0-4.16, 5 и 6 тождественные сумматору R/k(0) - R/k(s), R и операционному усилителю.

Сравнивая фиг. 5 прототипа и фиг. 25 находим, что в схеме преобразования с использованием пилообразных напряжений исключены схемы умножения 9.1-9.30, как самостоятельные элементы. Генератор двуполярных напряжений Уолша 7 заменен генератором однополярных прямоугольных импульсов 7.0 и инвертором 7.1; формирователь пилообразных напряжений 8 заменен на модуль формирования умножения сигнала на ступенчатые вейвлеты МФУС фиг. 16.

Таким образом, схема фиг. 25 преобразования с использованием ступенчатых вейвлетов (9)-(11), формируемых в виде изменяющихся во времени коэффициентов деления делителей напряжений фиг. 16, отличается от схемы преобразования с использованием пилообразных напряжений фиг. 5 и формирователем напряжений [3, 4] следующими элементами:

1. Генератором однополярных импульсов 7.0 и инвертором 7.1.

2. Модулем формирования и умножения сигнала МФУС1 фиг. 16, объединенных в блок формирования умножения сигнала на ступенчатые вейвлеты, которые совмещают две операции: формирование ступенчатых функций и умножения на сигнал, построенных с использованием делителей напряжений, изготовленных по одной технологии и одинаковой величины с погрешностью 0,05-2,25% [11], что обеспечивает такую же погрешность формирование произведения сигнала на ступенчатые вейвлеты, в отличии от формирования пилообразных вейвлет-напряжений и умножения в схеме на основе операционных делителей с погрешностью до 5%.

3. Исключением из устройства (фиг. 5) схем умножения 9.1-9.30 типа AD539, построенных на основе операционных усилителей.

Достигнутый технический результат заключается в уменьшении аппаратной погрешности при использовании пилообразных ступенчатых вейвлетов (9) в виде пилообразных ступенчато изменяющихся коэффициентов деления делителей напряжений из одинаковых резисторов.

Промышленная применяемость изобретения определяется тем, что предлагаемый способ практически реализуем в устройстве, которое может быть изготовлено на базе известных и серийно выпускаемых изделий и технологического оборудования.

Предложенный способ и реализующее его устройство преобразования сигнала произвольной формы могут найти очень широкое применение в разнообразных областях: измерительная техника, связь, запись-воспроизведение аудио- и видеоконтентах и др.

На основании вышеизложенного и по результатам проведенного патентно-информационного поиска считаем, что предлагаемый способ и устройство преобразования сигнала произвольной формы отвечает критериям «Новизна», «Изобретательский уровень», «Промышленная применимость» и могут быть защищены патентом РФ на изобретение.

Источники информации

1. Добеши И. Десять лекций по вейвлетам. - Ижевск: НИЦ «Регулярная и хаотическая динамика», 2001. - 464 С.

2. Хармут Х.Ф. Теория секвентного анализа. Основы и применения. -М.: Мир, 1980.

3. Горепекин А.В., Горепекин Р.А., Циклаури Д.Б. Патент РФ №2576591 «Способ и устройство преобразования сигнала произвольной формы», 08.02.2016 г.

4. Горепекин А.В., Горепекин Р.А. Патент РФ№2557754 «Способ вейвлет-преобразования сигналов произвольной формы», 29.06.2015 г.

5. Сапрыкин В.А., Малый В.В., Лопухин Р.В. Патент РФ №2246132. С2, «Способ и устройство быстрого вычисления вейвлет-преобразования сигнала с произвольным шагом дискретизации масштабных коэффициентов», 10.02.2005.

6. Хамухин А.А. Патент РФ №2437147. С1, «Устройство для вычисления дискретизированного непрерывного сигнала.

7. Смирнов В.И. Курс высшей математики. - М.: Наука, 21 изд. стереот. Т.2. - 1974. -656 с.

8. Фолькенберри Л.М. Применение операционных усилителей и линейных ИС. - М.: Мир, 1985. - 572 с.

9. Микросхема AD539 умножения аналоговых сигналов. http://www/analog.com/static/imported-files/data_sheets/AD539/pdf.

10. Шило В.Л. Популярные цифровые микросхемы. Справочник. - М.: Радио и связь, 1987. - 352 с.

11. Каталог ОАО НПОН «ЭРКОН».

12. Справочное пособие под редакцией С.В. Якубовского Аналоговые и цифровые интегральные микросхемы. - М.: Радио и связь, 1985. - 430 с.

Графические материалы, поясняющие суть изобретения

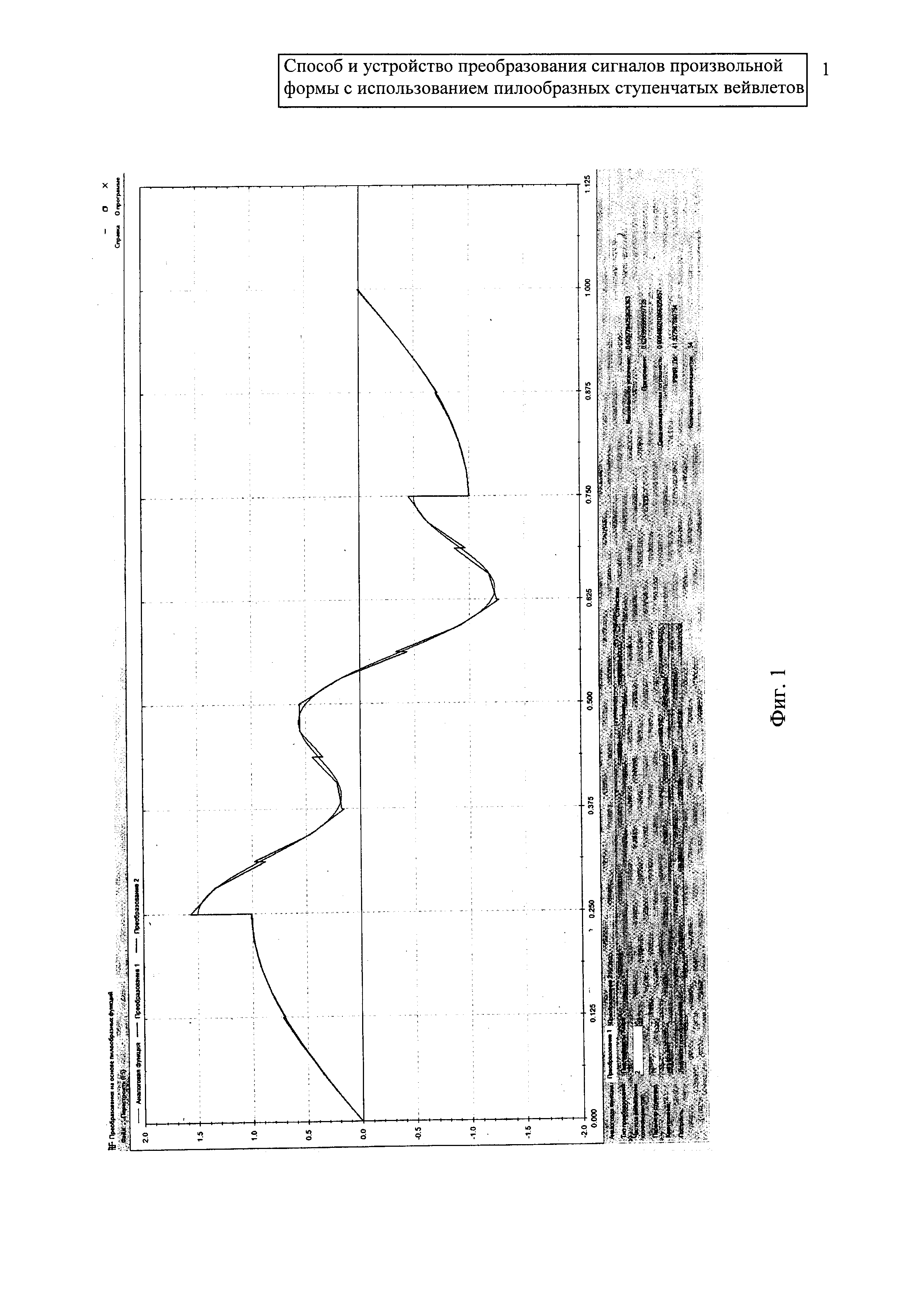

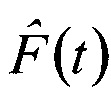

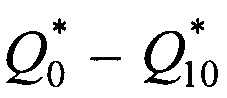

Фиг. 1. Графики исходного сигнала F(t) и восстановленного

График отражает характер изменения восстановленного сигнала и его близость к исходному.

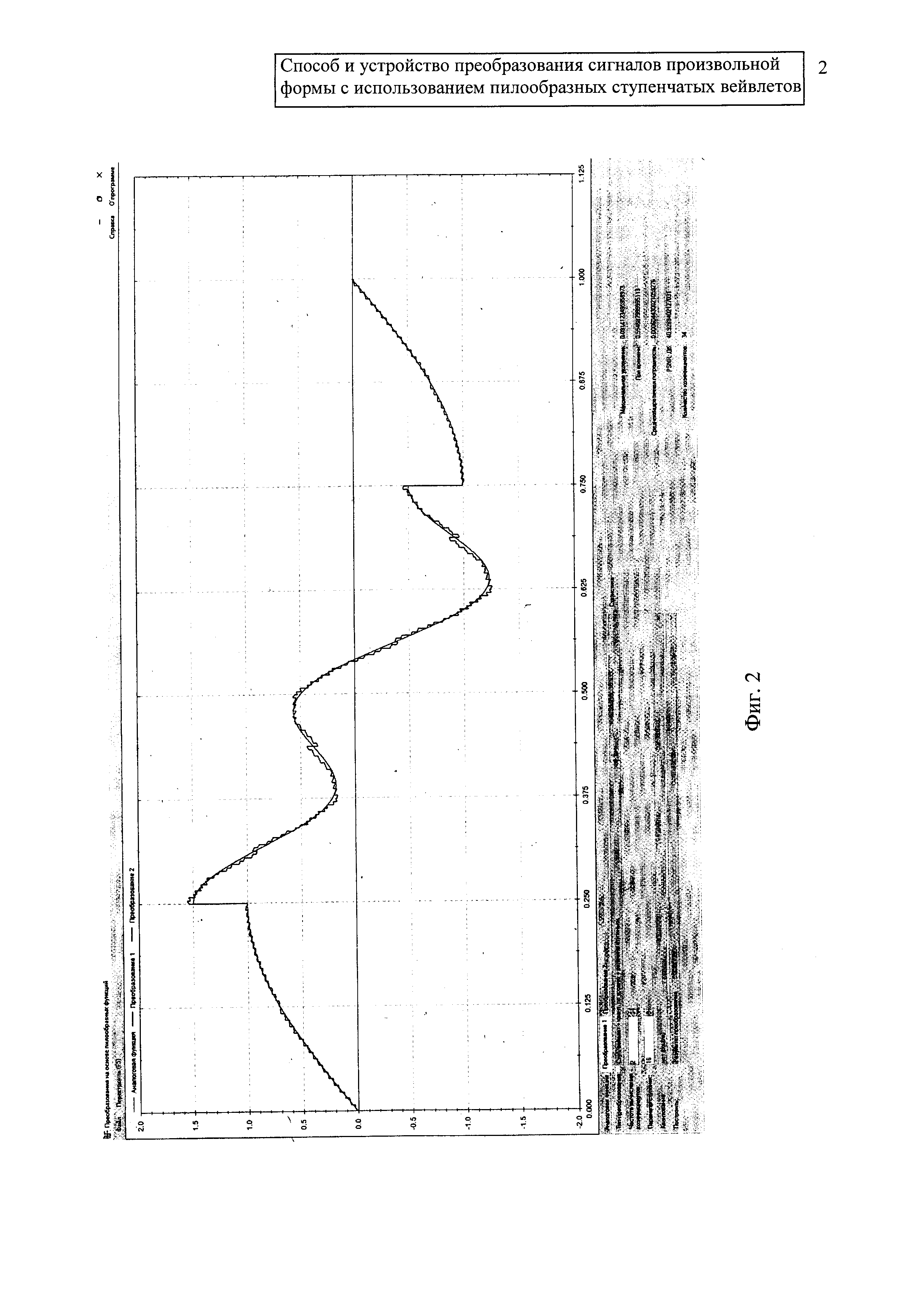

Фиг. 2. Графики исходного сигнала F(t) и восстановленного с использованием пилообразных ступенчато-изменяющихся вейвлетов.

График отражают характер изменения восстановленного сигнала и его близость к исходному и полученному в результате преобразования по пилообразным ступенчато изменяющимися вейвлетам.

Фиг. 3. Графики пилообразных ступенчатых вейвлетов Gar1(t) - Gar16(t).

Фиг. 4. Графики порождающих пилообразных ступенчато-изменяющихся функций с числами секвент 1, 2, 4, 8 и 16.

Фиг. 5. Графики однополярных импульсов формирования ступенчатых вейвлетов Gar3(t) и Gar4(t) путем умножения их на функцию G4(t).

Фиг. 6. Графики однополярных импульсов формирования вейвлетов Gar5(t) - Gar8(t) путем умножения их на функцию G8(t).

Фиг. 7. Графики однополярных импульсов формирования вейвлетов Gar9(t) - Gar16(t) путем умножения их на функцию G16(t).

Фиг. 8. Схема генератора однополярных прямоугольных импульсов (ГОПИ).

Отражает структуру и элементную базу.

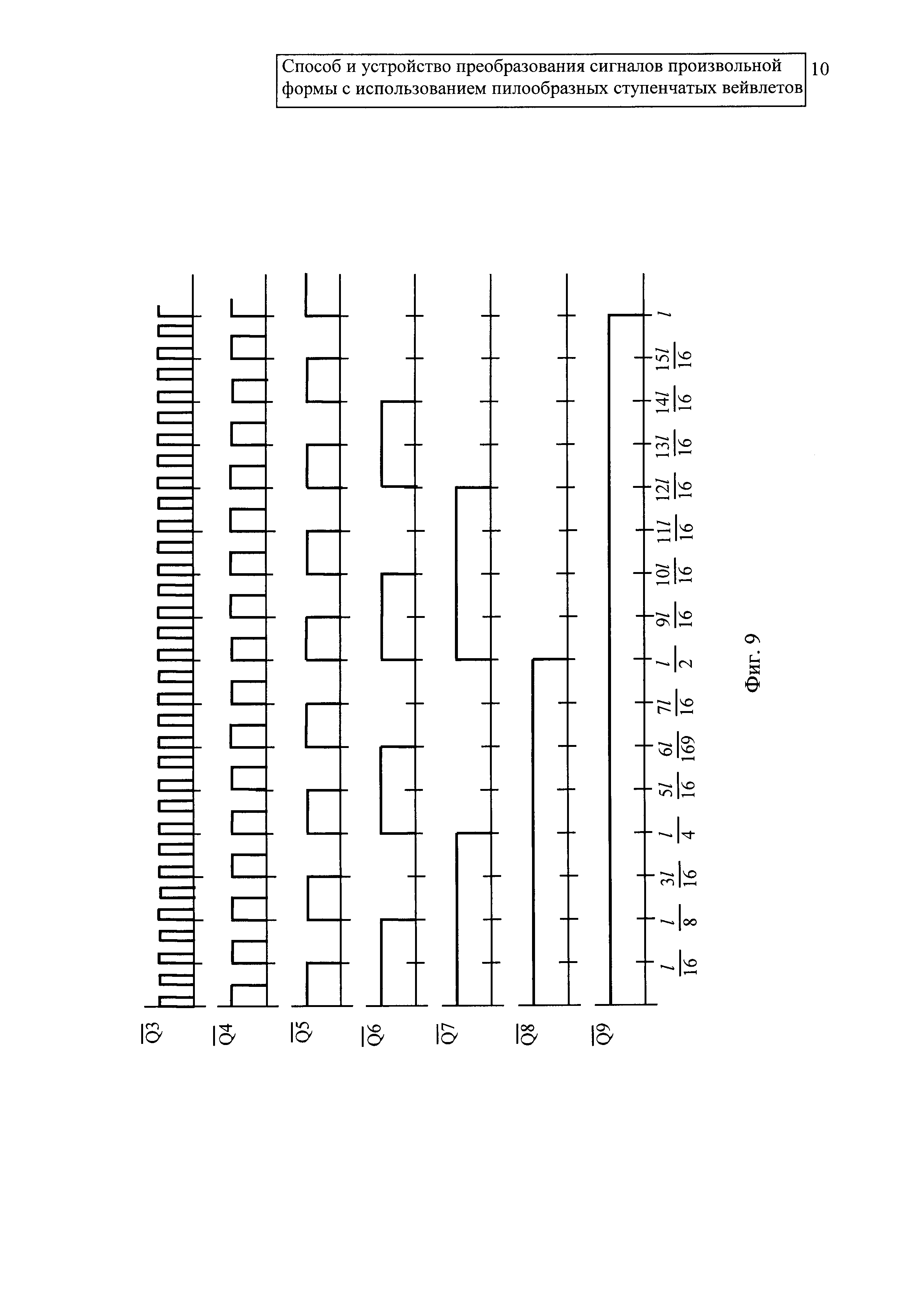

Фиг. 9. Графики однополярных прямоугольных импульсов формирования синхронными счетчиками Д1, Д2 и Д3 фиг. 8.

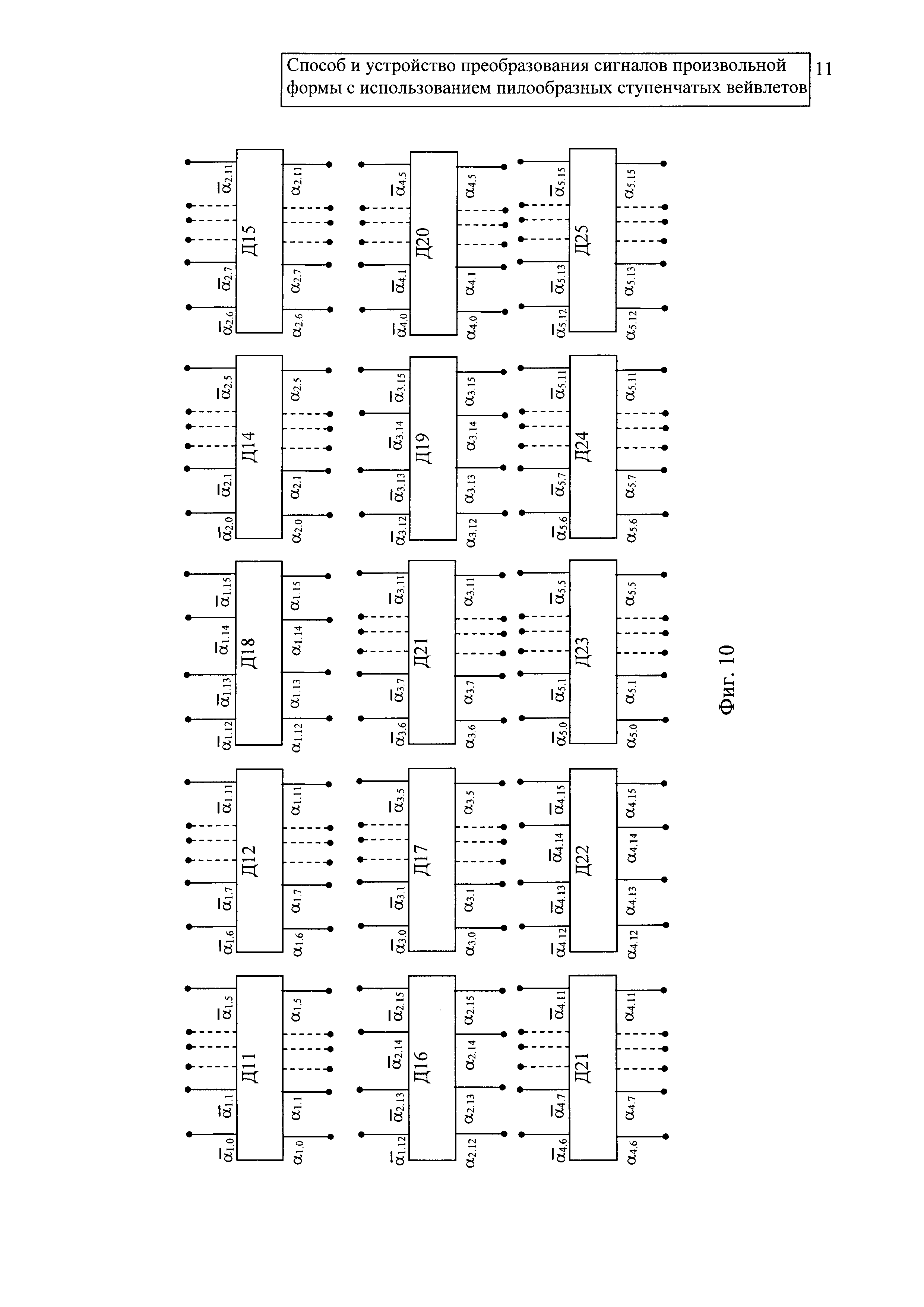

Фиг. 10. Модуль инвертирования (МИ) однополярных импульсов α1.0-α1.15; α2.0-α2.15; α3.0-α3.15; α4.0-α4.15; α5.0_α5.15 ГОПИ для управления ключами S0-S15 и S0*-S15* фиг. 16.

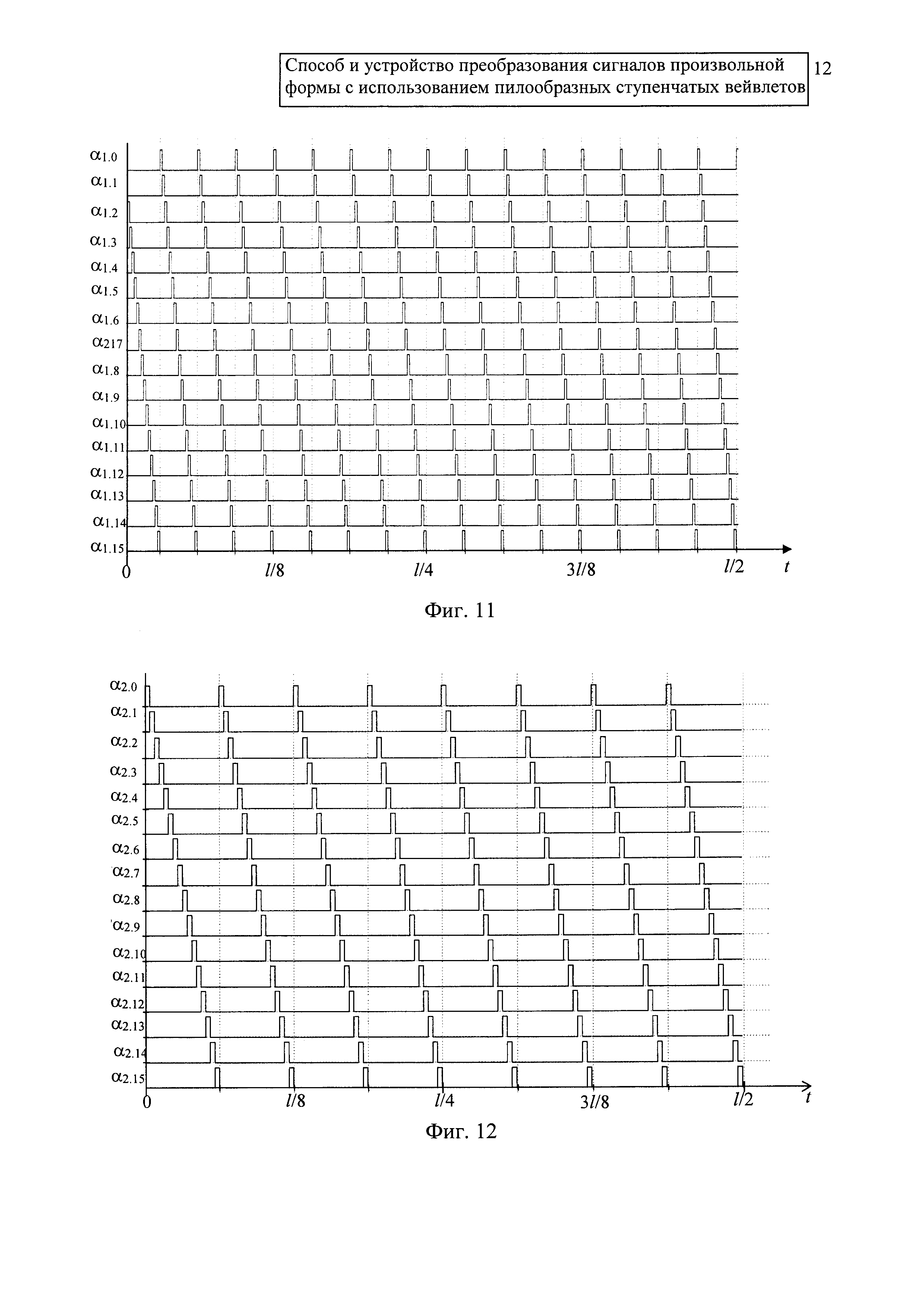

Фиг. 11 - фиг. 15. Графики однополярных импульсов α1.0-α5.15управления ключами S0-S15 и S0*-S15* отражают взаимное расположение состояний ключей как в одном формирователи порождающих функций, так и между состояниями ключей в других порождающих формирователях.

Фиг. 16. Схема модуля формирования и умножения (МФУС) ступенчатых вейвлетов на сигнал.

Отражает способ подключения делителей напряжения и их коммутации выходов с помощью электронных ключей. В скобках приведены импульсы (Q4; Q5; Q6; Q7) формирования порождающих функций G1(t), G4(t), G8(t) и G16(t).

Фиг. 17. График изменения напряжения (сопротивления) делителя напряжений RD1 UAE при F(t)=U0.

Фиг. 18. График напряжения (сопротивления) делителей напряжений RD2 UBE при F(t)=U0.

Фиг. 19. График однополярных импульсов Q7 для управления ключом Sф1 фиг. 16 и для формирования двуполярного ступенчатого напряжения U3, фиг. 20.

Фиг. 20. График изменения напряжения на контакте 3 ключа Sф1 фиг. 16.

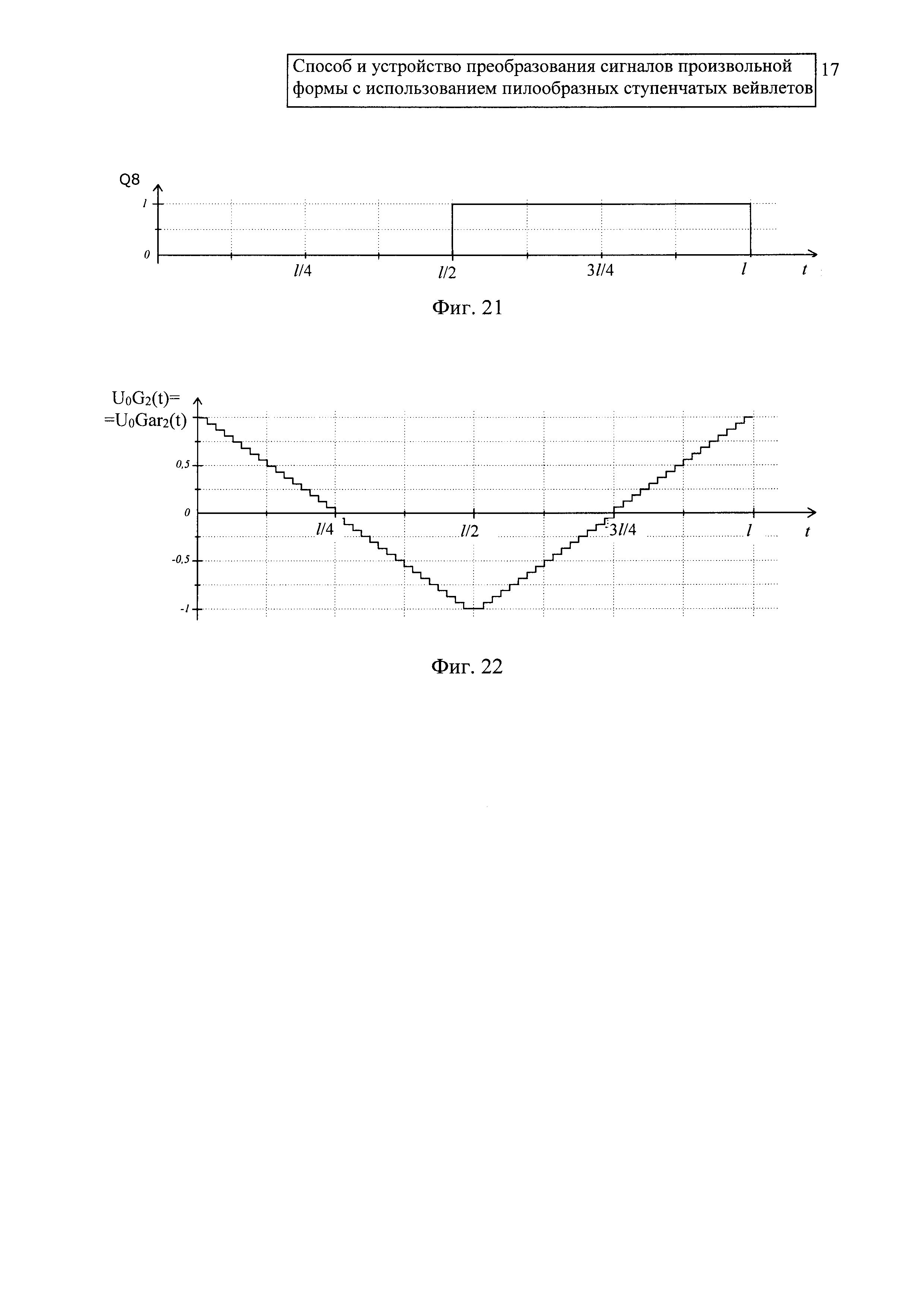

Фиг. 21. График однополярных импульсов Q8, используемых для формирования ступенчатого вейвлета Gar2(t) путем управления ключом Sф2 фиг. 16.

Фиг. 22. График произведения напряжения U0=F(t) на пилообразный вейвлет Gar2(t), сформированный с помощью двух делителей напряжений RD1 и RD2 и импульсов управления ключами коммутации S0-S15 и S0*-S15* и импульсов формирования Q7 и Q8.

Фиг. 23. Блок формирования ступенчатых вейвлетов Gar1(t)-Gar16(t) и умножения сигнала (БФСВУС).

Фиг. 24. Схема устройства прототипа [3], включающая следующие блоки и их связи:

1 - источник сигнала;

2.0-2.15 - интеграторы;

3.0-3.15 - отсчитывающие и запоминающие устройства;

4.0-4.15 и 5.0 - резисторы сумматоров напряжений;

6 - операционный усилитель;

7 - генератор напряжений Уолша:

8 - формирователи ортогональных пилообразных напряжений;

9.0-9.30 - схемы умножения двух одновременно изменяющихся напряжений;

10, 11.1-11.15 - блоки вычисления коэффициентов преобразования по пилообразным напряжениям.

В схеме выхода 1-16 генератора напряжений Уолша 7 соединяют с одноименными входами формирователя ортогональных пилообразных напряжений 8, а выходы 1-15 блока 8 соединяют с входами 2 умножителей 9.1-9.15 первой группы, а вход 1 с выходом источника сигнала, выходы умножителей 9.1-9.15 соединяют с входами интеграторов 2.0-2.15, а их выходы I0-I15 соединяют с одноименными входами отсчитывающих и запоминающих схем 3.0-3.15. Входы последних I0-I15 соединяют с входами схем вычисления коэффициентов преобразования 10.0; 11.1-11.15, в результате этого завершают этап прямого преобразования.

Для обратного преобразования выходы 0-15 схем вычисления коэффициентов преобразования 10.0; 11.1-11.15 соединяют с одноименными входами 1 схем умножения второй группы 9.16-9.30, а входы 2 схем умножения соединяют с выходами формирователя ортогональных пилообразных напряжений 8.

В результате параллельного умножения 16 коэффициентов в виде напряжения на ортогональные пилообразные напряжения, а также параллельного суммирования с помощью сумматора 4.0-4.15; 5.0 и 6 на выходе восстанавливают сигнал

Фиг. 25. Схема устройства, реализующего способ с использованием пилообразных ступенчато-изменяющихся вейвлетов в виде изменяющихся во времени коэффициентов деления делителей напряжений из одинаковых по величине резисторов.

Согласно фиг. 25 предлагаемое устройство включает следующие блоки из прототипа [3]:

блок 1 - генератор сигнала произвольной формы;

блоки 2.0-2.16 - интеграторы на операционных усилителях;

блоки 3.0-3.16 отсчитывания и запоминания;

блоки 10.0-10.16 вычисления коэффициентов преобразования;

блок суммирования 6 с резисторами 4.0-4.16 и резистором обратной связи 5.0. вновь введенные;

- блок 7.0 - генератор однополярных прямоугольных импульсов (ГОПИ), формирующий восемь групп сдвинутых во времени однополярных импульсов;

- блок 7.1. - формирования пяти групп инвертированных импульсов (ГОПИ) для управления ключами делителей напряжения, изготовленных из одинаковых резисторов;

первый и второй блоки формирования ступенчатых вейвлетов и умножения сигнала БФСВУС1 и БФСВУС2 8.9 фиг. 25, включающие 16-ть модулей формирования и умножения сигнала (фиг. 16) МФУС1 - МФУС16.

Блоки устройства, реализующие пилообразные ступенчато-изменяющиеся вейвлеты, объединены следующим образом.

Выходы

Входы 16 модулей МФУС1 - МФУС16 БФСВУС1 соединены параллельно и подключены к выходу источника сигнала произвольной формы; выходы γ1 модуля МФУС1 через последовательно соединенные блоки интегрирования 2.1, блоки отсчитывания и запоминания 3.1, блок вычисления первого коэффициента преобразования 11.1 a1; выход γ2модуля МФУС2 через последовательно соединенные блок интегрирования 2.2, блок отсчитывания и запоминания 3.2 и блок вычисления второго коэффициента преобразования α2; …, выход γ16 модуля МФУС16 через блок интегрирования 2.16, блок отсчитывания и запоминания 3.16 и блоки вычисления шестнадцатого коэффициента разложения a16; выход a1 блока вычисления первого коэффициента подключен к входу 1 второго блока формирования ступенчатых вейвлетов и умножения на сигнал БФСВУС2; выход а2 второго блока вычисления коэффициента подключен к входу 2 БФСВУС2; …, выход а16 БФСВУС2 подключен к 16 входу БФСВУС2;

выходы λ1-λ16 БФСВУС2 подключены соответственно с входами резисторов 4.1-4.16 блока суммирования на операционном усилителе 6 и резисторе обратной связи 5.

Реферат

Изобретение относится к области измерений, вычислительной техники и предназначено для прямого и обратного преобразований сигнала. Техническим результатом является уменьшение аппаратной погрешности. Устройство содержит источник сигнала произвольной формы, генератор однополярных прямоугольных импульсов, формирующий восемь групп импульсов, модуль инвертирования этих импульсов, два блока формирования ступенчатых вейвлетов и умножения на сигнал, каждый из которых включает по 16 модулей формирования пилообразных ступенчатых вейвлетов, блоки интегрирования напряжений произведения сигнала на коэффициенты деления делителей напряжений, блоки запоминания и хранения значений результатов интегрирования, блоки вычисления коэффициентов преобразования; резисторы, сумматор. 2 н.п. ф-лы, 25 ил.

Формула

Комментарии