Электронно-вычислительная машина - RU180783U1

Код документа: RU180783U1

Чертежи

Описание

Полезная модель относится к устройству электронно-вычислительных машин (далее ЭВМ), предназначенных для моделирования и тестирования оборудования, например коммутационного, созданного на основе MIPS архитектуры.

Известна электронно-вычислительная машина на процессоре Loongson (MIPS архитектуры) из документа CN 204065943 U, опубл. 31.12.2014, которая включает системную плату, экран дисплея, привод CD, жесткий диск. Недостатком данной ЭВМ является низкая эффективность, при моделировании и тестировании оборудования, например коммутационного, созданного на основе MIPS архитектуры.

Также известна электронно-вычислительная машина, из документа CN 203773424 U, опубл. 13.08.2014, принята за прототип, которая включает системную плату с центральным процессором MIPS архитектуры, оперативное запоминающие устройство, жесткий диск, USB хост-контроллер. Недостатком данной ЭВМ является низкая эффективность, при моделировании и тестировании оборудования, например коммутационного, созданного на основе MIPS архитектуры.

Задача полезной модели является создание ЭВМ для моделирования и тестирования оборудования, созданного на основе MIPS архитектуры.

Технический результат - повышение эффективности моделирования и тестирования оборудования, созданного на основе MIPS архитектуры.

Технический результат достигается за счет того, что ЭВМ включает системную плату с центральным процессором MIPS архитектуры, оперативное запоминающие устройство, жесткий диск, USB хост-контроллер, графический сопроцессор, дисплей, USB хаб, Wi-Fi и Bluetooth модуль, модуль подключения SD карт, сетевой интерфейс, контроллер клавиатуры, клавиатуру, часы реального времени, при этом центральный процессор MIPS архитектуры имеет два вычислительных ядра с общей кэш-памятью и снабжен встроенными контроллерами периферийных устройств. Встроенными контроллерами периферийных устройств являются контроллер памяти DDR3, контроллер SATA 3.0, контроллер Ethernet 1 Гбит/с, контроллер PCIe Gen.3 x4, контроллер UART интерфейса, контроллер I2C интерфейса, контроллер стартовой загрузки.

Полезная модель поясняется чертежами, где:

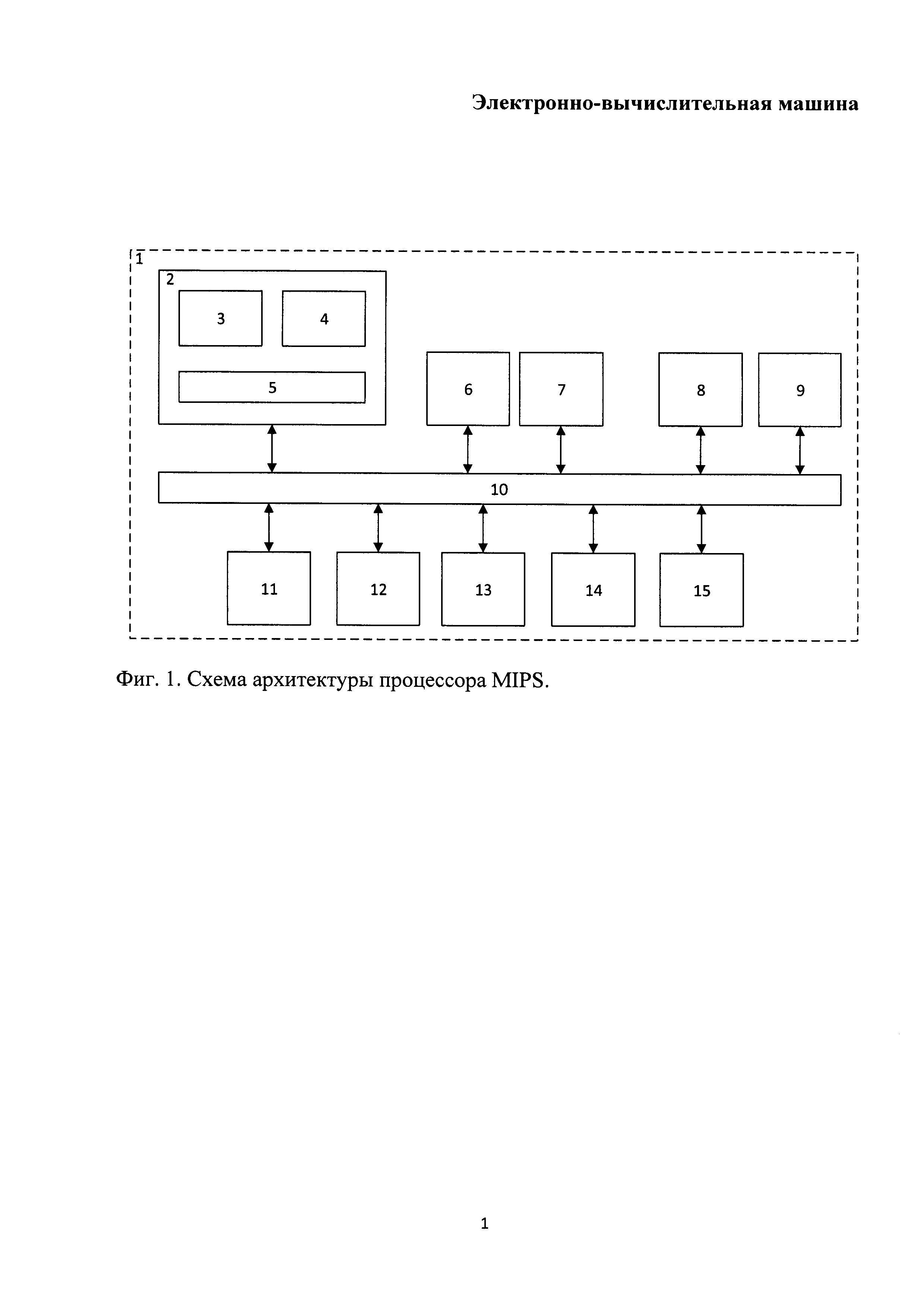

Фиг. 1 - схема архитектуры процессора MIPS,

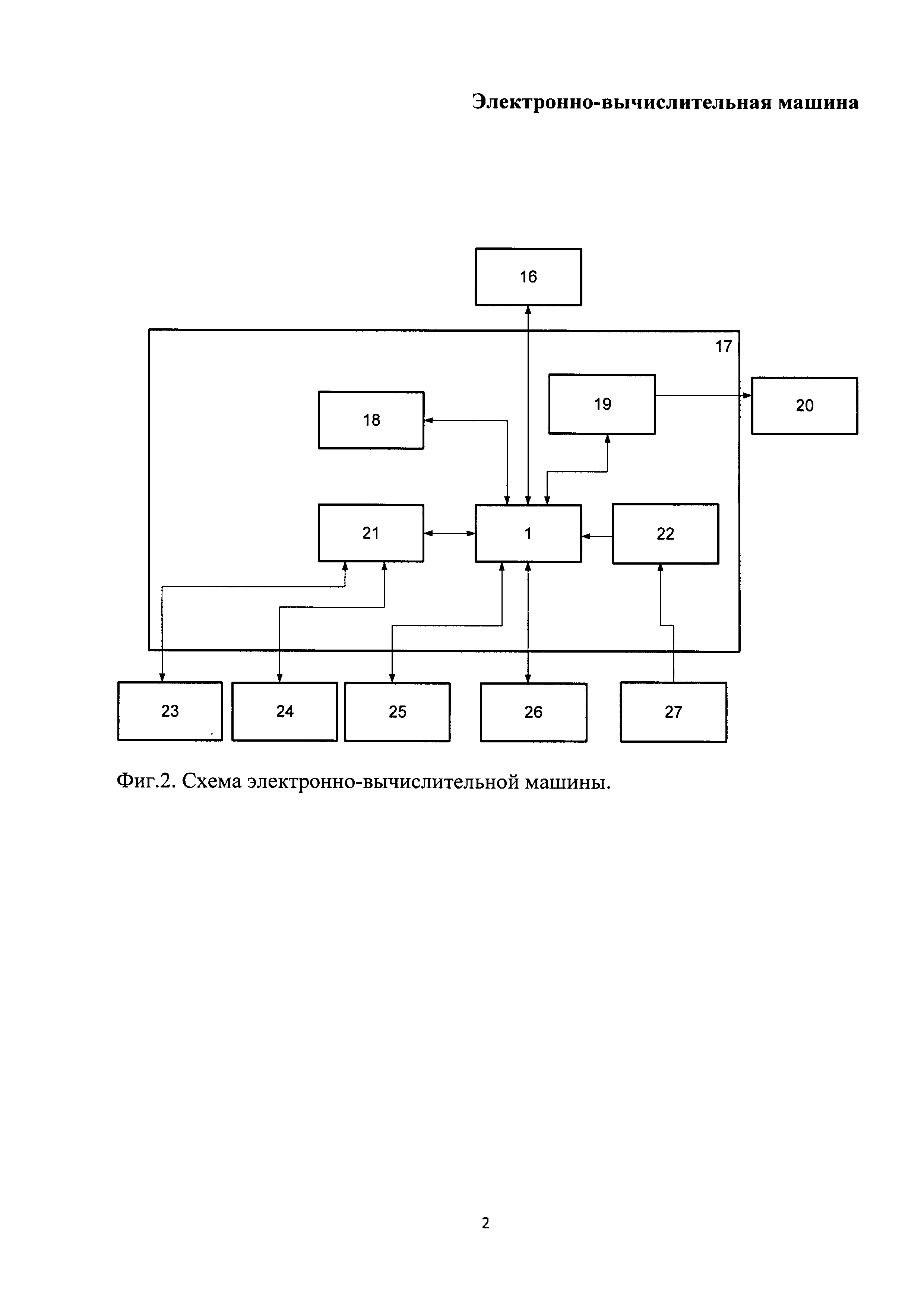

Фиг. 2 - схема электронно-вычислительной машины.

На фигуре 1 показана схема архитектуры процессора MIPS, на которой 1 - центральный процессор MIPS архитектуры, 2 - вычислительный блок, 3, 4 - вычислительные ядра, 5 - кэш-память, 10 - системная шина процессора, встроенные контроллеры периферийных устройств: 6 - USB хост-контроллер, 7 - контроллер памяти DDR3, 8 - контроллер SATA 3.0, 9, 11 - контроллер Ethernet 1 Гбит/с, 12 - контроллер PCIe Gen.3 х4, 13 - контроллер UART интерфейса, 14 - контроллер I2C интерфейса, 15 - контроллер стартовой загрузки.

На фигуре 2 показана схема электронно-вычислительной машины, которая содержит 1 - центральный процессор MIPS архитектуры, 16 - оперативное запоминающие устройство (ОЗУ) с интерфейсом DDR3, 17 - системную плату, 18 - часы реального времени, 19 - графический сопроцессор, 20 - дисплей, 21 - USB хаб, 22 - контроллер клавиатуры, 23 - Wi-Fi и Bluetooth модуль, 24 - модуль подключения SD карт, 25 - жесткий диск, 26 - сетевой интерфейс, 27 - клавиатуру.

Вычислительный блок (2) центрального процессора MIPS архитектуры (1), состоящий из вычислительных ядер (3, 4), кэш-памяти (5) взаимодействует с набором периферийных контроллеров: USB хост-контроллером (6), контроллером памяти DDR3 (7), контроллером SATA 3.0 (8), контроллерами Ethernet 1 Гбит/с (9, 11), контроллером PCIe Gen.3 х4 (12), контроллером UART интерфейса (13), контроллером I2C интерфейса (14), контроллером стартовой загрузки (15) по средствам системной шины процессора (10). Центральный процессор MIPS архитектуры (1) устанавливается на системную плату (17), к нему подключаются ОЗУ с интерфейсом DDR3 (16) к контроллеру памяти DDR3 (7), USB хаб (21) к USB хост-контроллеру (6), графический сопроцессор (19) к контроллеру PCIe Gen.3 х4 (12), дисплей (20) к графическому сопроцессору (19), часы реального времени (18) к контроллеру I2C интерфейса (14), жесткий диск 25 к контроллеру SATA 3.0 (8)/PCIe Gen.3 х4 (12), модуль подключения SD карты (24) к USB хабу (21), сетевой интерфейс (26) к контроллеру Ethernet 1 Гбит/с (9), Wi-Fi и Bluetooth модуль (23) к USB хабу (21) (см. фиг. 1 и фиг. 2).

При включении ЭВМ осуществляет первичную загрузку с помощью контроллера стартовой загрузки (15) и инициализацию собственных модулей и режимов работы процессора MIPS архитектуры (1), установленного на системную плату (17), и ОЗУ с интерфейсом DDR3 (16), подключенного к контроллеру памяти DDR3 (7). Для этой цели используется программное обеспечение (далее ПО) загрузчика, реализованное на базе ПО с открытым исходным кодом U-Boot. После этого происходит загрузка ядра ОС Linux с жесткого диска (25), подключенного к встроенному в процессор контроллеру SATA 3.0 (8), в ОЗУ с интерфейсом DDR3 (16). Затем управление передается ядру ОС Linux, которое проводит дополнительную инициализацию оборудования и загружает ПО пользовательского уровня. ПО ядра ОС Linux считывается из ОЗУ с интерфейсом DDR3 (16) вычислительным блоком (2), состоящим из двух вычислительных ядер (3, 4), в кэш-память (5), увеличивающую скорость обмена между вычислительными ядрами (3, 4) и внешним ОЗУ с интерфейсом DDR3 (16), через системную шину (10). Использование кэш-памяти (5), повышает эффективность моделирования и тестирования коммуникационного оборудования за счет увеличения скорости работы вычислительного блока (2) с внешнем ОЗУ с интерфейсом DDR3 (16).

ЭВМ моделирует и тестирует устройства со встроенным программным обеспечением, в которых традиционно используются процессоры с архитектурой MIPS. Сетевой интерфейс (26), подключенный к контроллеру Ethernet 1 Гбит/с (9, 11), Wi-Fi и Bluetooth модулю (23) позволяют моделировать поведение оборудования, где один из интерфейсов играет роль внешнего, а другой внутреннего, работающего в режиме трансляции сетевых адресов NAT. Количество сетевых интерфейсов может быть расширено за счет внешних USB Ethernet модулей подключаемых к USB хабу (21). USB хаб (21), подключенный к USB хост-контроллеру (6), с достаточным количеством поддерживаемых USB интерфейсов, используемых для моделирования и тестирования функционала сетевого хранилища, альтернативного канала подключения по 3G/4G сетям, перепрошивки встроенного ПО сетевого устройства. Модуль подключения SD карт (24), который используется для моделирования и тестирования отчуждаемого хранилища данных для конфигурирования моделируемого оборудования и ведения журнала работы оборудования, в том числе журнала событий. Встроенный дисплей (20) отображает процесс моделирования и вывода отладочной информации. Графическая информация о процессе моделирования формируется в графическом сопроцессоре (19), подключенном к встроенному в центральный процессор (1) контроллеру PCIe Gen.3 х4 (12). При задании режимов работы процесса моделирования и тестирования оборудования, а так же для ввода команд управления в процессе тестирования, используется клавиатура (27), подключенная к контроллеру клавиатуры (22). Контроллер клавиатуры (22) непрерывно опрашивает состояние клавиш на клавиатуре (27) и формирует скан-коды нажимаемых клавиш, после этого сформированные скан-кода поступают из контроллера клавиатуры (22) в контроллер UART интерфейса (13) встроенного в центральный процессор (1). Часы реального времени (18), подключенные к встроенному контроллеру I2C интерфейса процессора (14), используются для моделирования ведения журнала событий с привязкой ко времени и дате - моделирование и тестирование работы сетевого оборудования по заранее заданным сценариям с привязкой ко времени. Применение данной ЭВМ повышает эффективность моделирования и тестирования оборудования, созданного на основе MIPS архитектуры.

Применение данного ЭВМ для моделирования и тестирования устройств со встроенным программным обеспечением не ограничивается домашним и профессиональным сегментом сетевого оборудования, но также возможно для моделирования промышленных систем автоматизации, измерительных приборов, систем видеонаблюдения, систем выдачи талонов, инвентаризации, автоматизированных складских весов и весов торгового зала, бортовых систем компьютерного зрения и прочих систем, где существуют дополнительные требования по температурному диапазону работы, пассивному охлаждению и энергопотреблению.

Реферат

Полезная модель относится к устройству электронно-вычислительных машин, предназначенных для моделирования и тестирования оборудования, созданного на основе MIPS архитектуры. Электронно-вычислительная машина включает системную плату с центральным процессором MIPS архитектуры, оперативное запоминающие устройство, жесткий диск, USB хост-контроллер. Электронно-вычислительная машина дополнительно включает графический сопроцессор, дисплей, USB хаб, Wi-Fi и Bluetooth модуль, модуль подключения SD карт, сетевой интерфейс, контроллер клавиатуры, клавиатуру, часы реального времени. Центральный процессор MIPS архитектуры имеет два вычислительных ядра с общей кэш-памятью и снабжен встроенными контроллерами периферийных устройств. Достигается повышение эффективности моделирования и тестирования оборудования, созданного на основе MIPS архитектуры. 1 з.п. ф-лы; 2 ил.

Комментарии