Запоминающее устройство и ведущее устройство - RU2348992C2

Код документа: RU2348992C2

Чертежи

Описание

Эта заявка основана на и притязает на приоритет по заявкам на выдачу патентов Японии № 2004-204028, зарегистрированный 12 июля 2004 г., и № 2004-342275, зарегистрированный 26 ноября 2004 г., полное содержание которых включено в материалы настоящей заявки посредством ссылки.

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Настоящее изобретение относится к запоминающему устройству и ведущему устройству (электронному устройству), использующему запоминающее устройство. В частности, настоящее изобретение относится к запоминающему устройству, такому как энергонезависимое полупроводниковое запоминающее устройство, и карте памяти, его использующей. Настоящее изобретение также относится к электронному устройству, такому как записывающее устройство; например, цифровая фотокамера и цифровая видеокамера, содержащие встроенное запоминающее устройство. Например, запоминающее устройство, такое как флэш-память с универсальной последовательной шиной (USB), и электронное устройство, такое как персональный компьютер (ПК, PC) и персональный цифровой секретарь (PDA), включены в категорию по настоящему изобретению.

УРОВЕНЬ ТЕХНИКИ

В последние годы карта памяти, содержащая встроенную энергонезависимую полупроводниковую память, вошла в широкое употребление в качестве запоминающего устройства, хранящего различные виды цифровой информации, такой как данные изображения и музыкальные данные. Данные энергонезависимой полупроводниковой памяти находятся вне риска потери, даже если отключается источник питания, и являются перезаписываемыми. Память NAND flash™ часто используется в качестве энергонезависимой памяти (например, смотрите публикацию № 2003-30993 KOKAI патентной заявки на выдачу патента Японии).

В последнее время емкость памяти флэш-памяти возросла из-за продвижений в технологии производства полупроводников.

Например, запоминающее устройство, такое как карта памяти, содержащее встроенную флэш-память, используется ведущим устройством. В этом случае ведущее устройство непосредственно контролирует флэш-память, встроенную в запоминающее устройство в обычных условиях. Так, ведущее устройство воспринимает время программирования флэш-памяти и, по времени программирования, может до некоторой степени прогнозировать быстродействие памяти и допустимое для хранения время.

Однако в настоящее время является частым случай, когда запоминающее устройство имеет встроенный контроллер; по этой причине управление стало осложненным. Как результат, невозможно предсказать быстродействие памяти с использованием простого расчета. Параметр скорости передачи шины, соединяющей ведущее устройство и запоминающее устройство, определяется. Однако он не является реальной скоростью, когда ведущее устройство записывает данные в запоминающее устройство. По этой причине скорость передачи не работает в качестве средства для идентификации быстродействия.

Для того чтобы прогнозировать быстродействие запоминающего устройства, включающего в себя память NAND flash™, требуется расчет в сочетании со способом блочной обработки посредством ведущего устройства. По этой причине затруднительно определять быстродействие с использованием только запоминающего устройства.

Соответственно, желательно предоставить электронное устройство, которое может простым образом до некоторой степени прогнозировать быстродействие запоминающего устройства, даже если запоминающее устройство большой емкости управляется через контроллер, и способ прогнозирования быстродействия и запоминающее устройство.

РАСКРЫТИЕ ИЗОБРЕТЕНИЯ

Согласно первому аспекту настоящего изобретения, предоставлено запоминающее устройство, содержащее: полупроводниковую память, сохраняющую данные; контроллер, выполняющий инструкции для записи данных в полупроводниковую память в соответствии с запросом, который контроллер принимает; и регистр, удерживающий информацию класса быстродействия, показывающую один класс быстродействия, требуемый, чтобы предоставить запоминающему устройству возможность демонстрировать наилучшее быстродействие, которое поддерживает запоминающее устройство, из классов быстродействия, заданных в соответствии с быстродействием.

Согласно второму аспекту настоящего изобретения, предоставлено ведущее устройство, считывающее данные из запоминающего устройства, которое хранит данные и информацию класса быстродействия, показывающую один класс быстродействия, требуемый, чтобы предоставить запоминающему устройству возможность демонстрировать наилучшее быстродействие, которое запоминающее устройство поддерживает, из классов быстродействия, заданных в соответствии с быстродействием, ведущее устройство записывает данные в запоминающее устройство, один класс быстродействия, требуемый, чтобы предоставить ведущему устройству демонстрировать наилучшее быстродействие, которое поддерживает ведущее устройство, из классов быстродействия, являющихся установленными для ведущего устройства.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

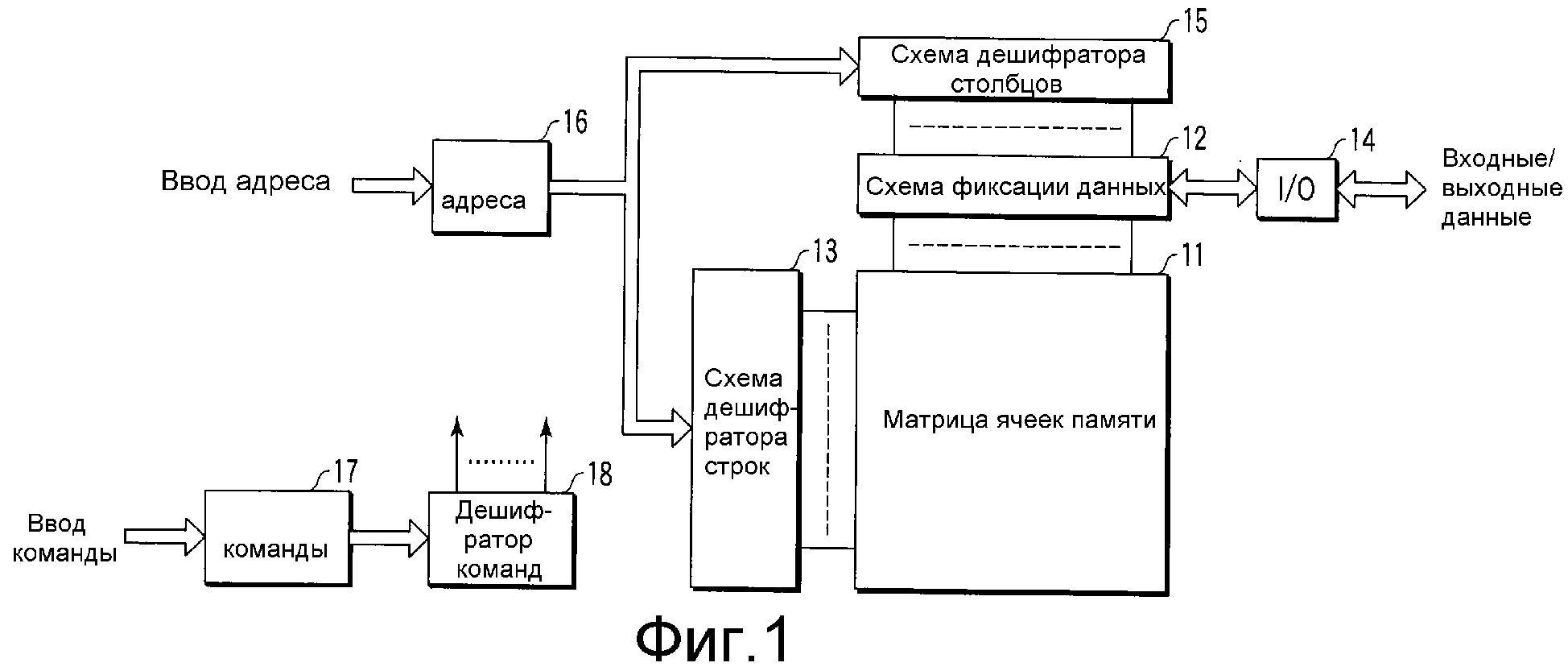

Фиг.1 - структурная схема, показывающая конфигурацию памяти NAND flash™ согласно первому варианту осуществления настоящего изобретения;

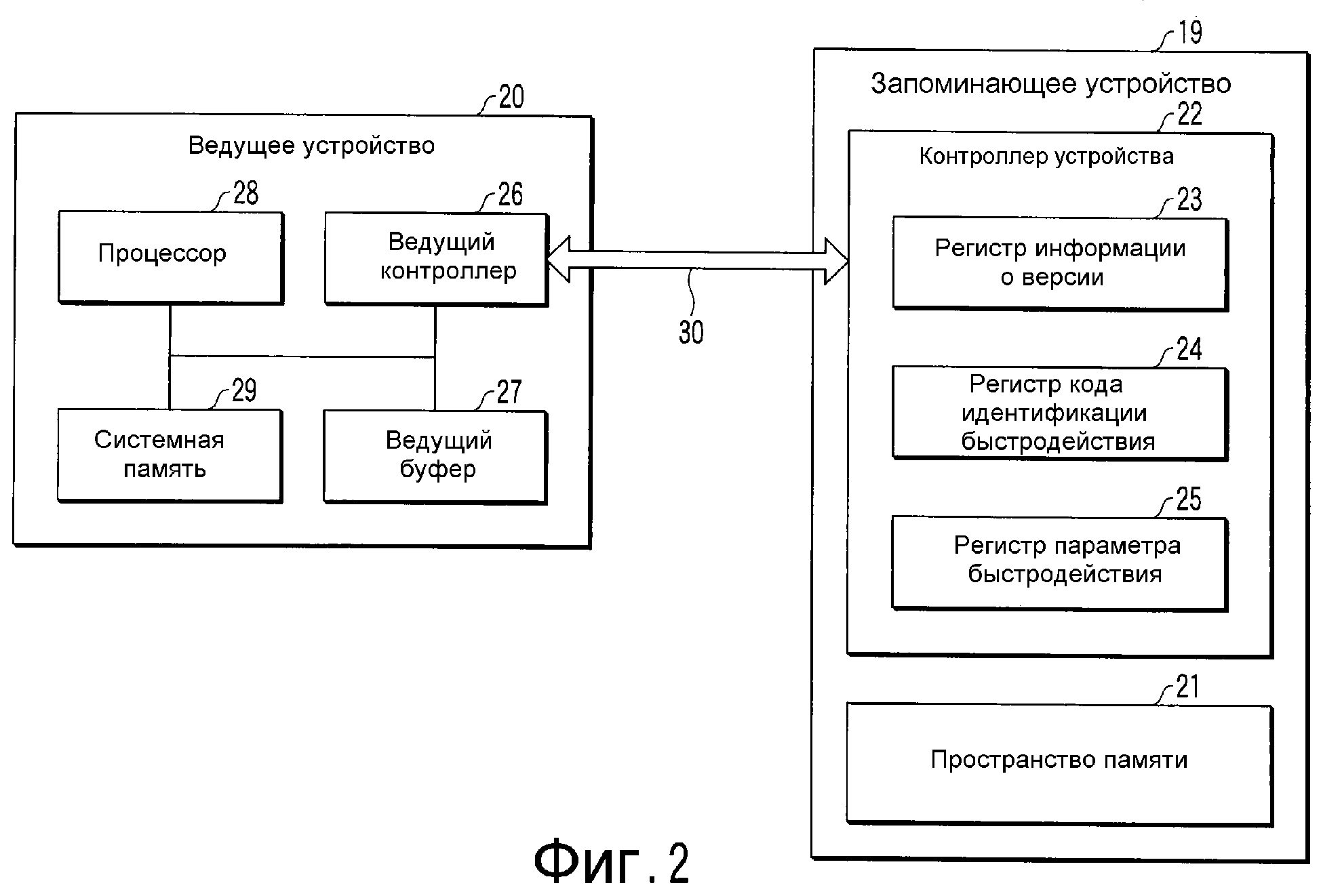

фиг.2 - структурная схема, показывающая конфигурацию запоминающего устройства, содержащего встроенную память по первому варианту осуществления, и ведущее устройство, использующее запоминающее устройство;

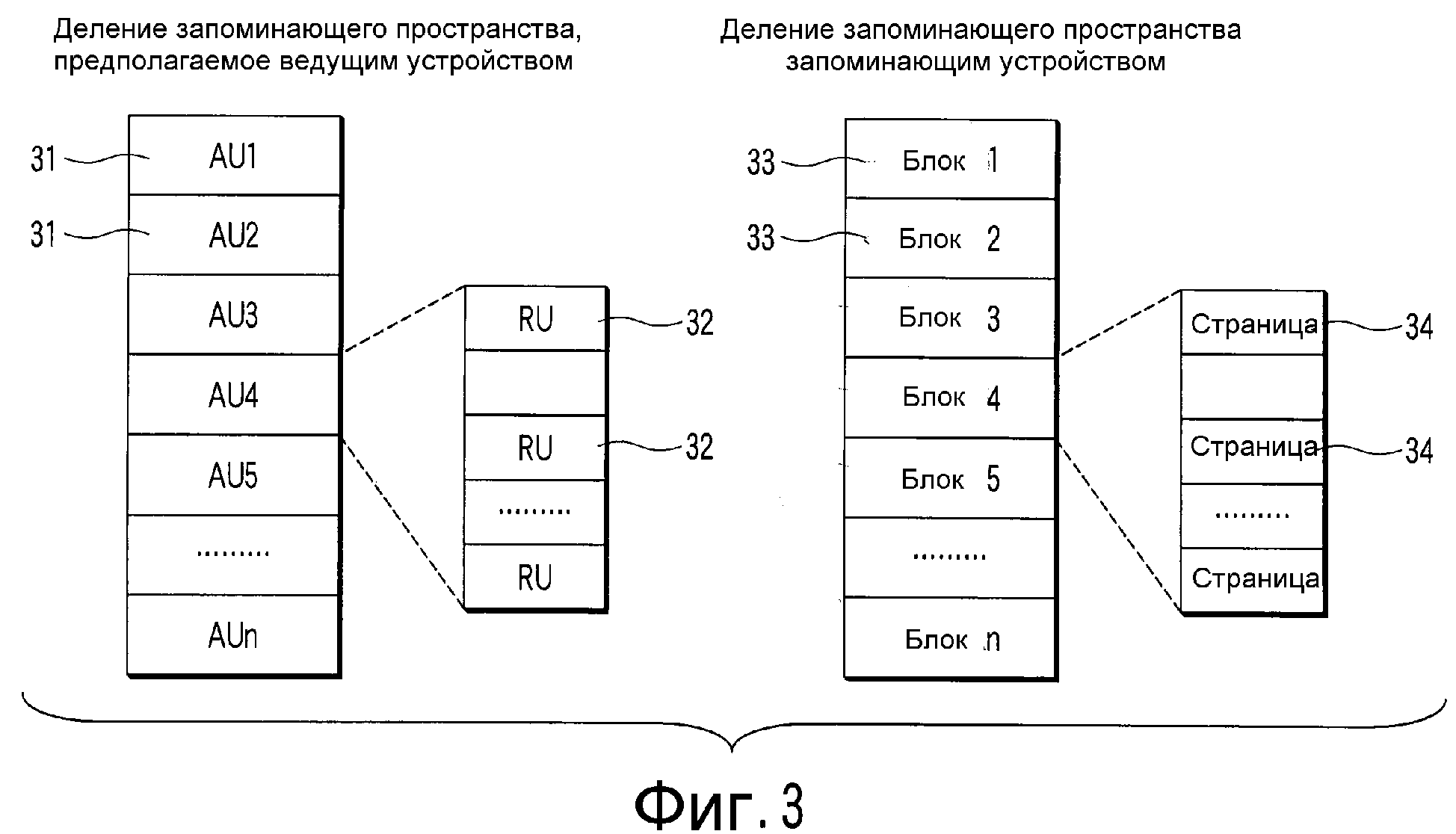

фиг.3 - представление для пояснения деления пространства запоминающего устройства, предполагаемого ведущим устройством в первом варианте осуществления, и реальное деление пространства в запоминающем устройстве;

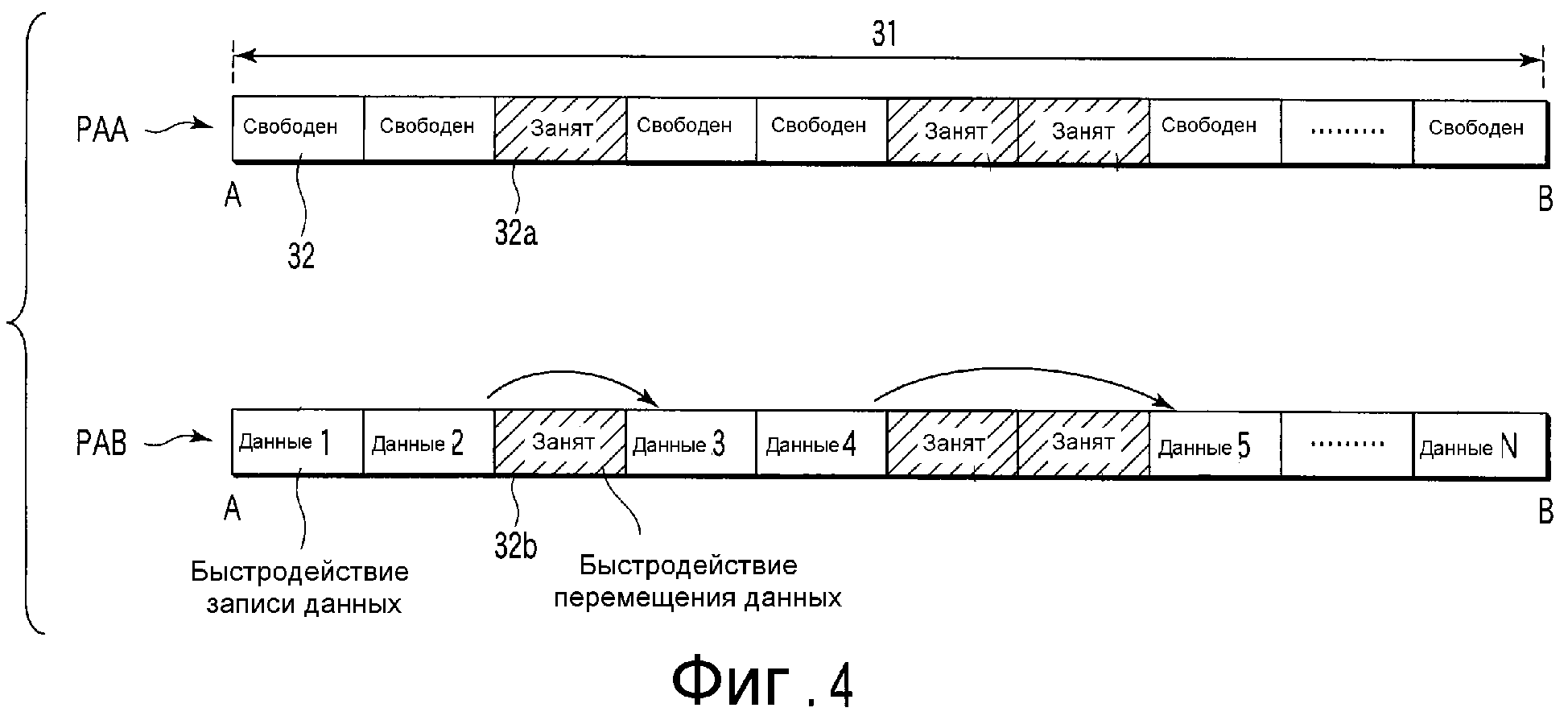

фиг.4 - представление для пояснения перемещения данных в первом варианте осуществления;

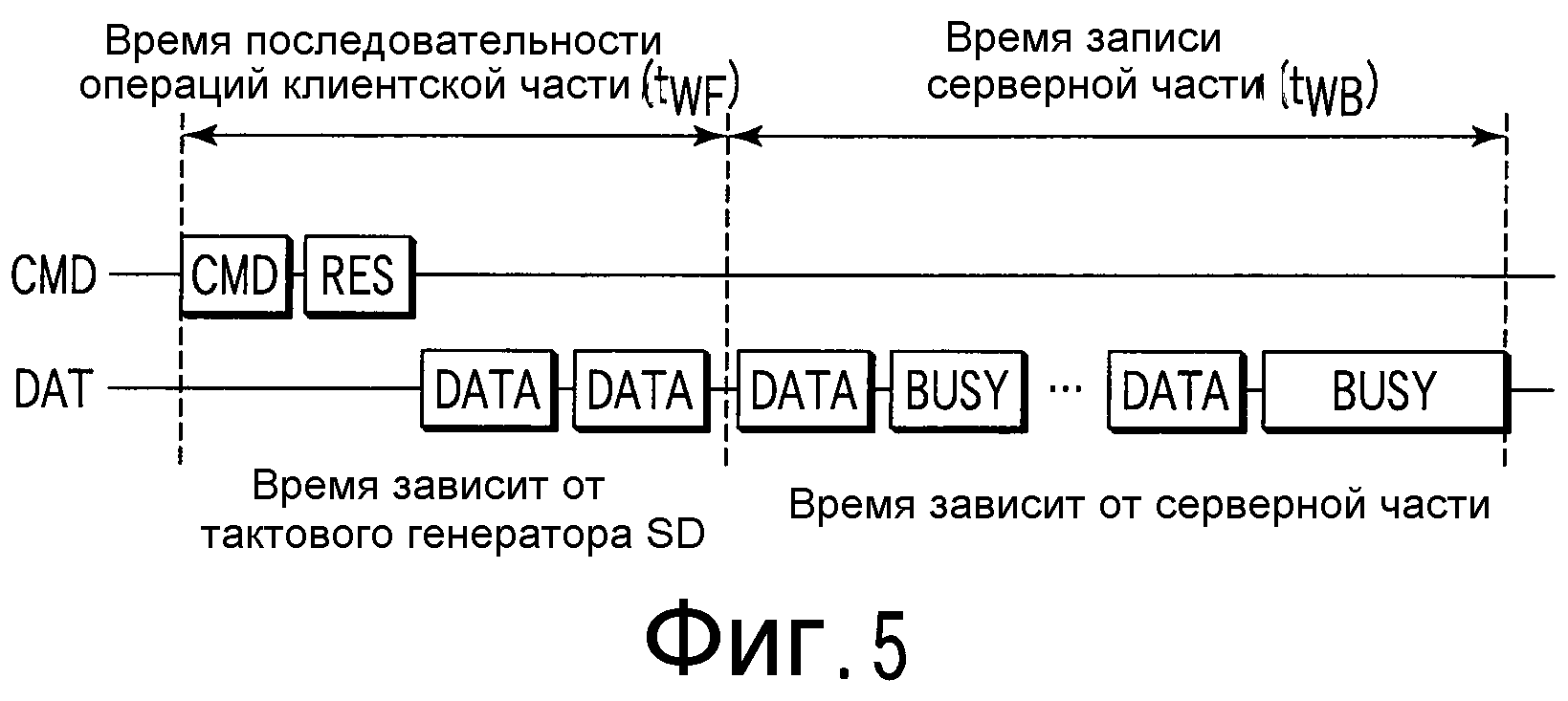

фиг.5 - представление для пояснения временных характеристик операции записи при использовании команды многоблочной записи;

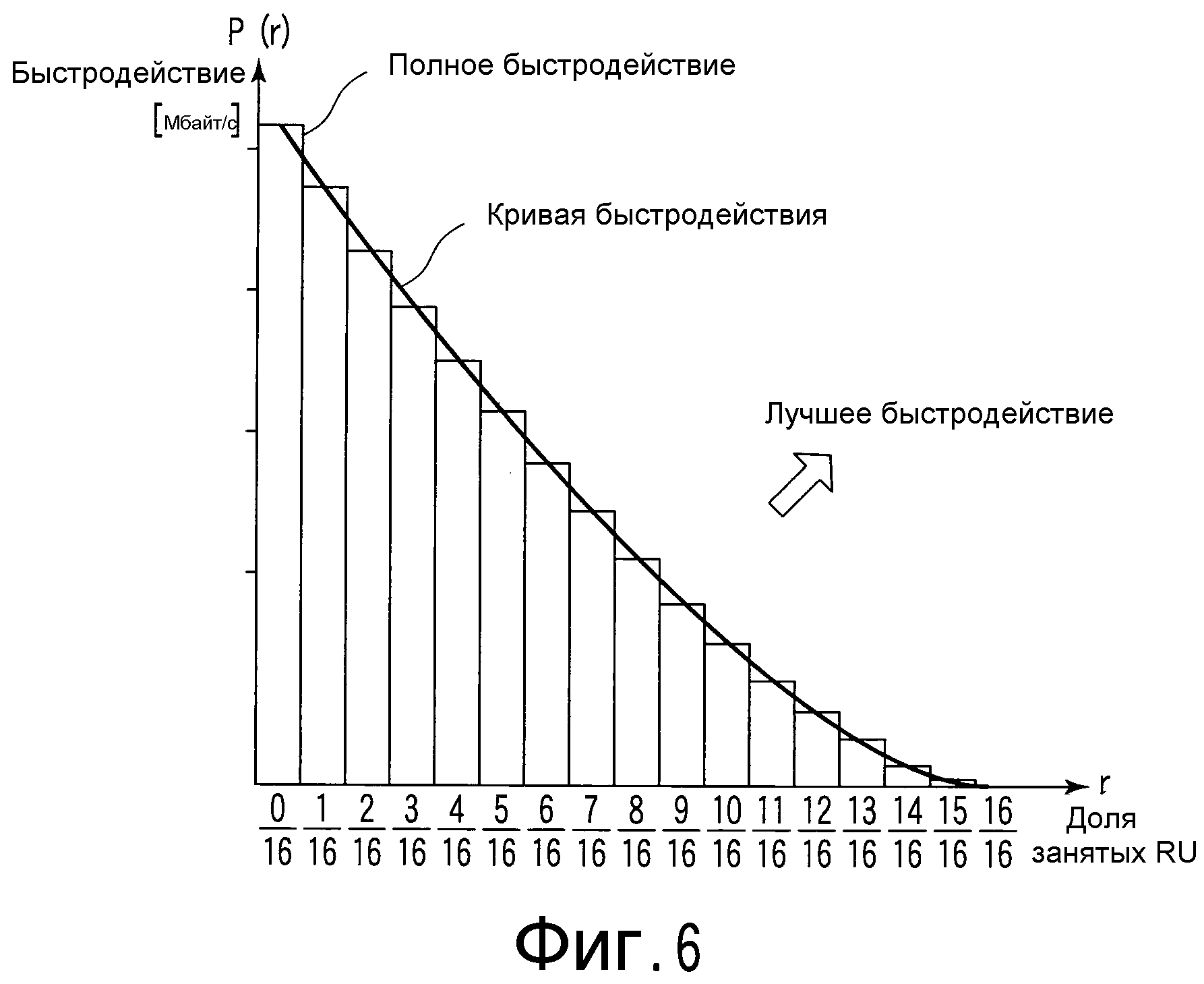

фиг.6 - представление, показывающее пример кривой быстродействия в первом варианте осуществления;

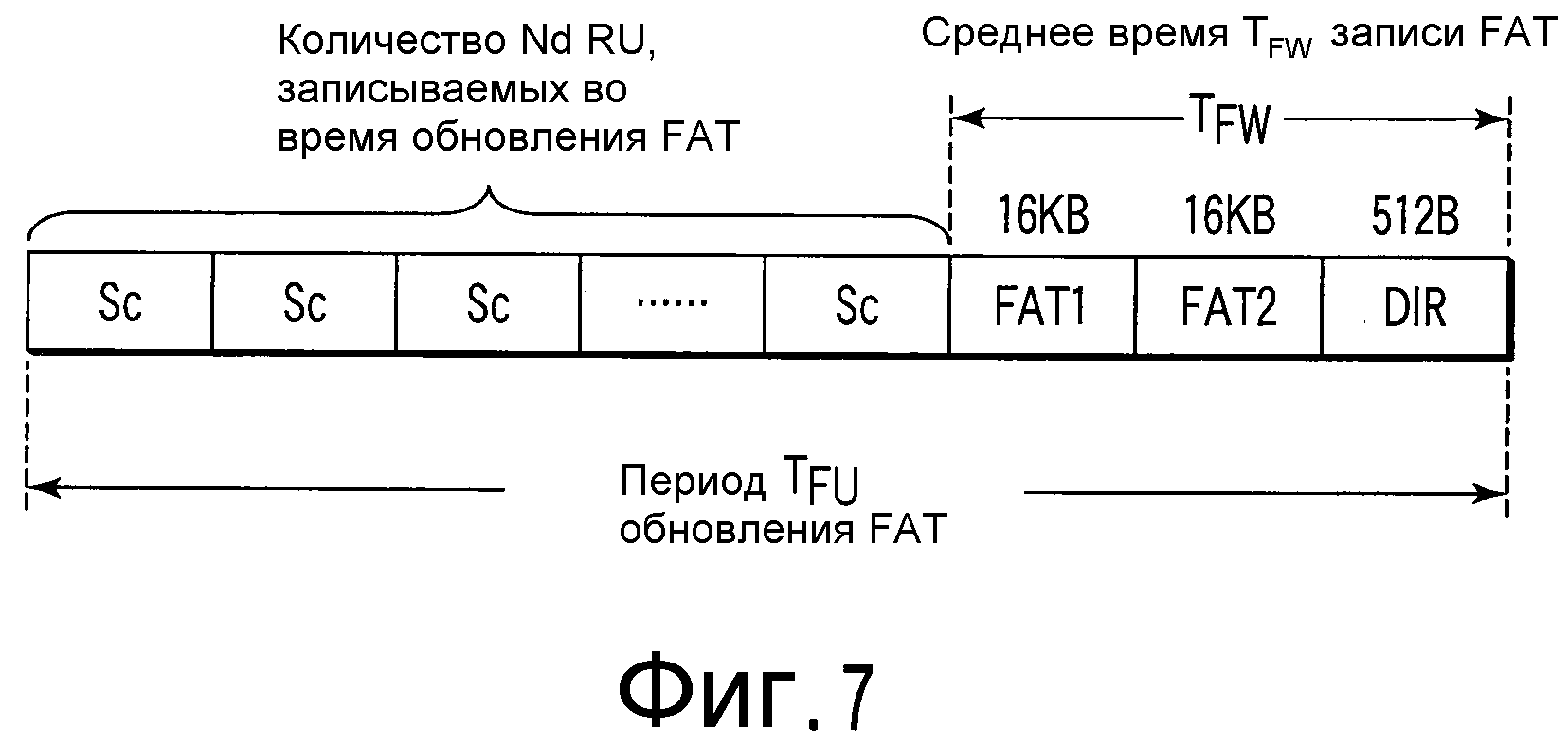

фиг.7 - представление для пояснения обновления файловой системы во время записи в реальном времени в первом варианте осуществления;

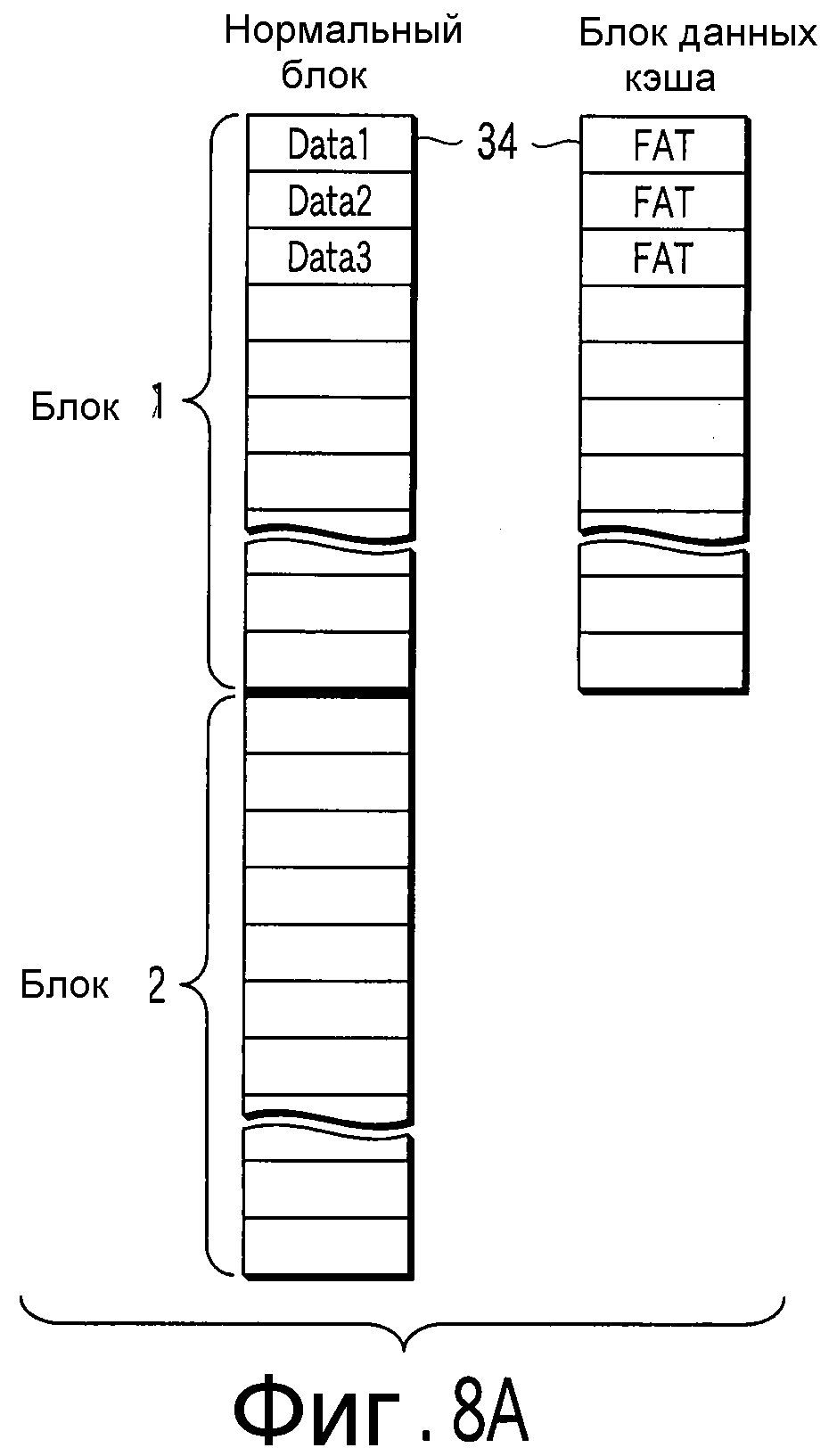

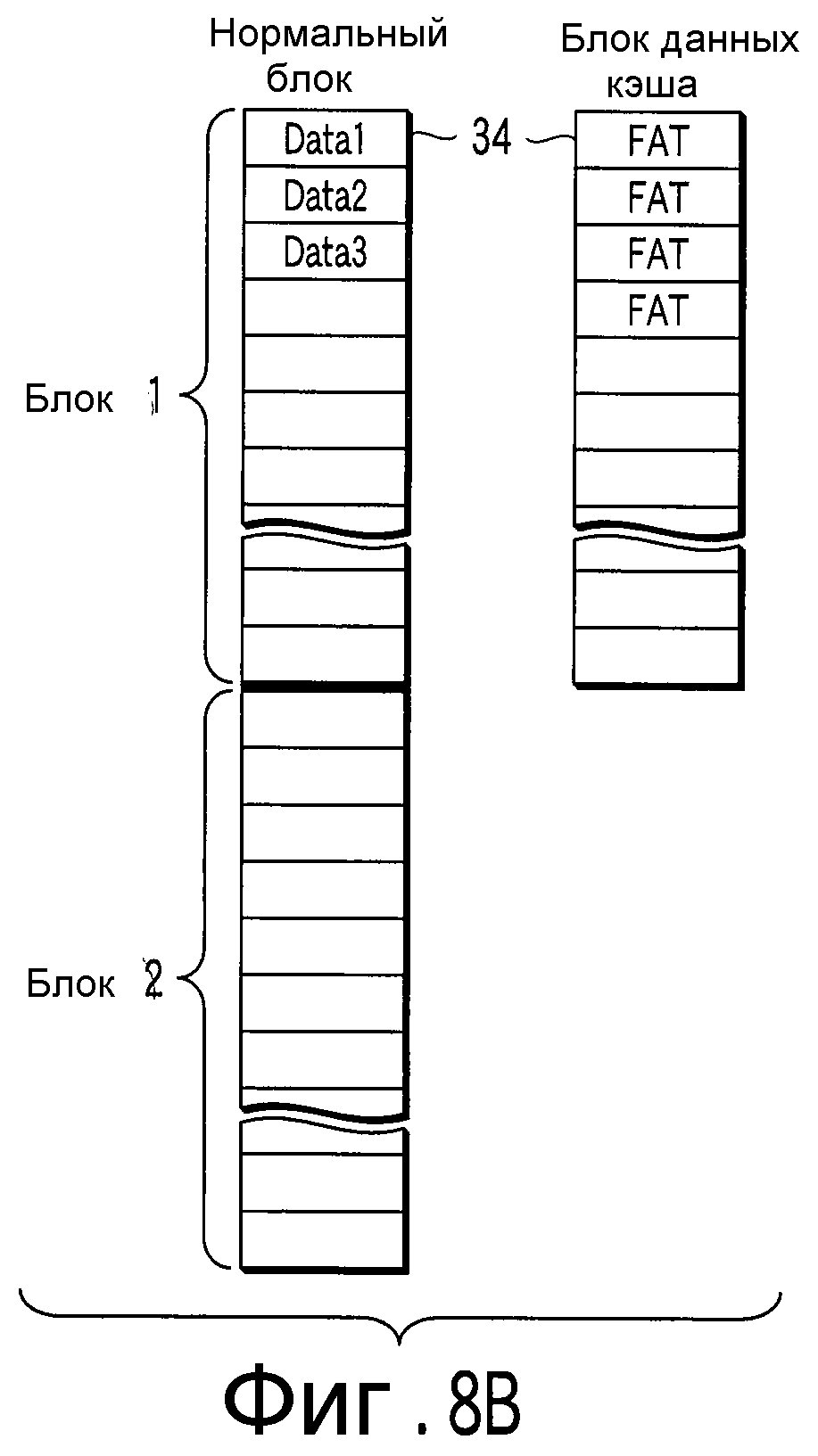

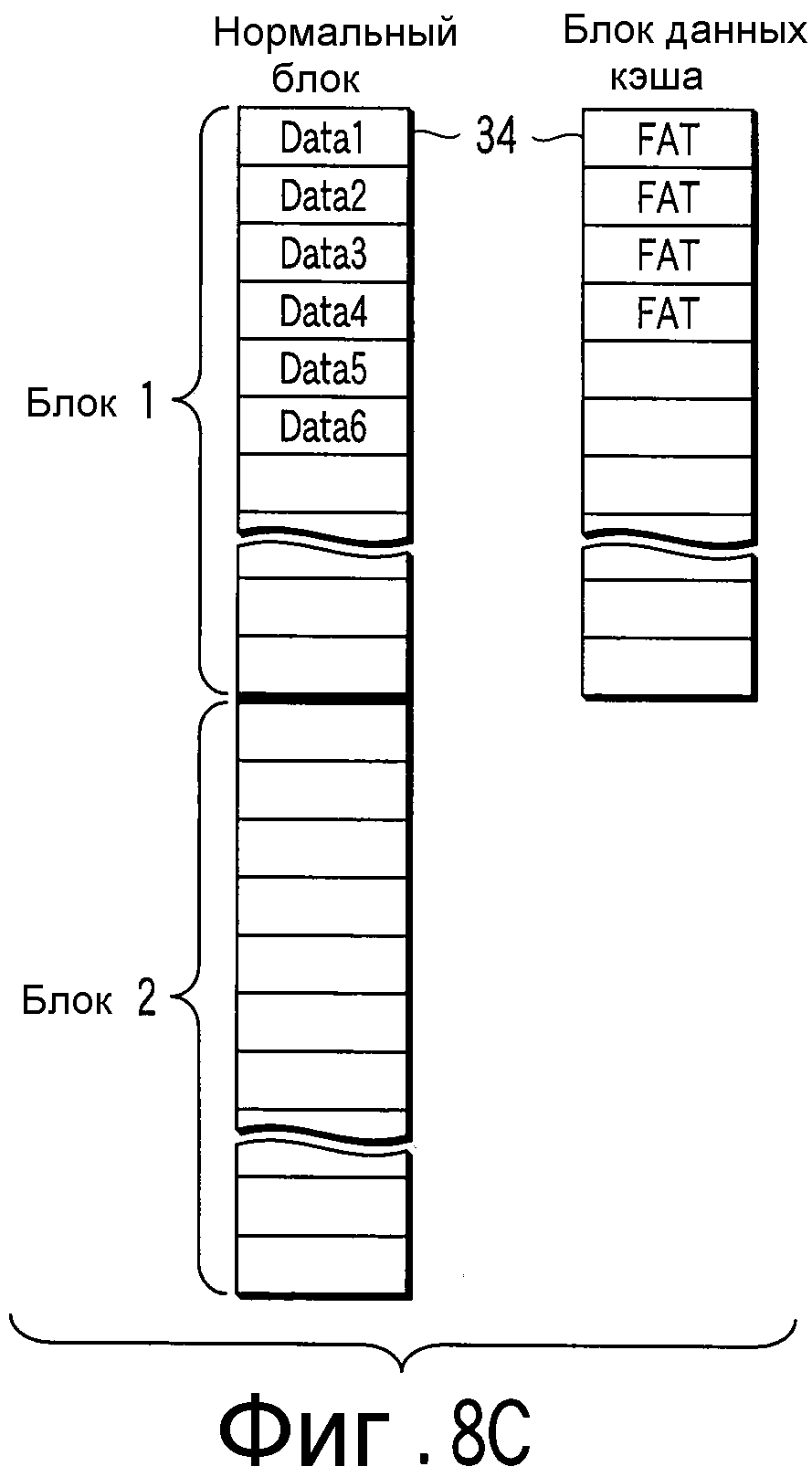

фиг.с 8A по 8C - представления, показывающие последовательность записи;

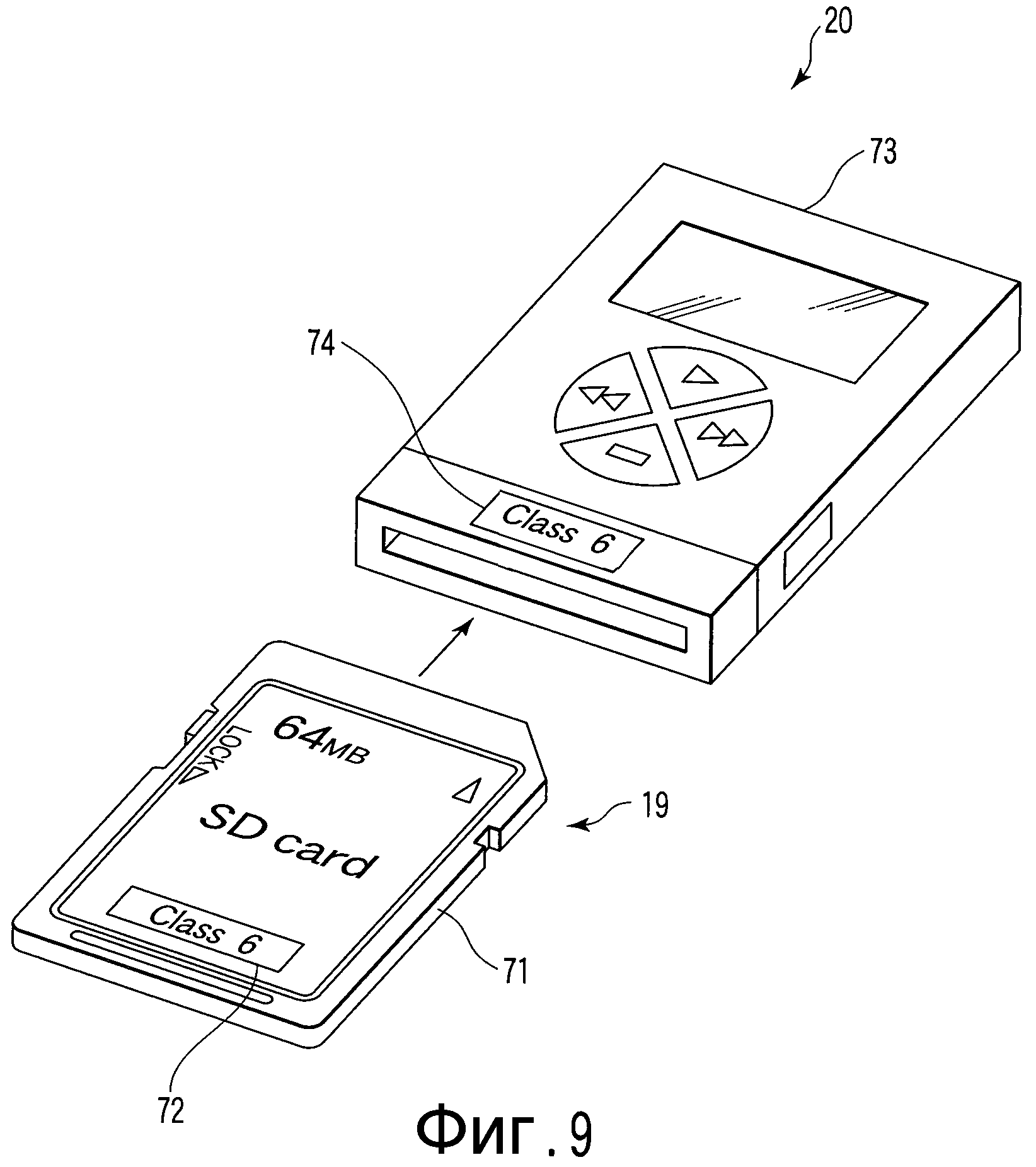

фиг.9 - вид в перспективе, показывающий внешний вид ведущего устройства и запоминающего устройства согласно первому варианту осуществления;

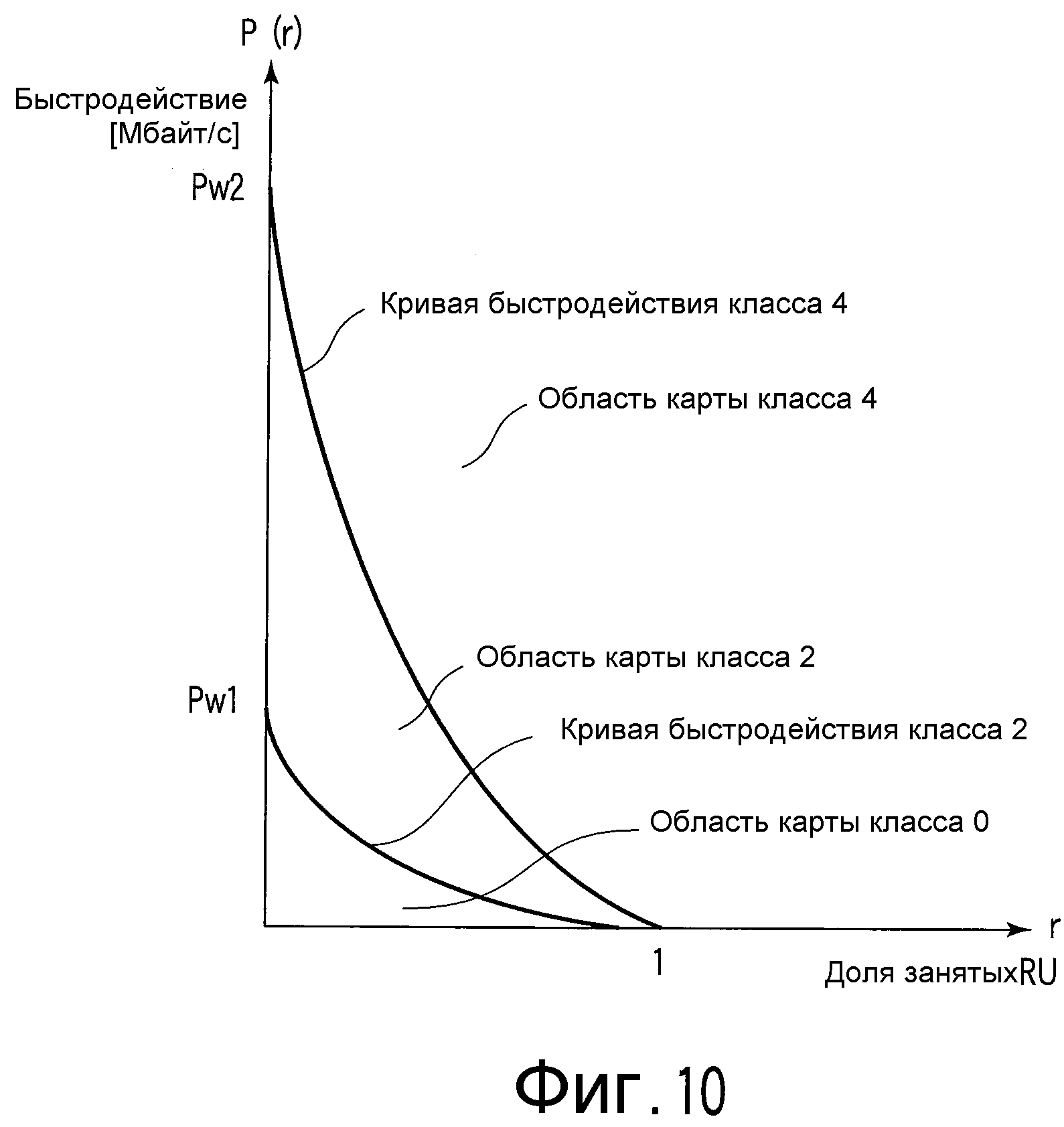

фиг.10 - представление, показывающее классификацию кривых быстродействия в первом варианте осуществления;

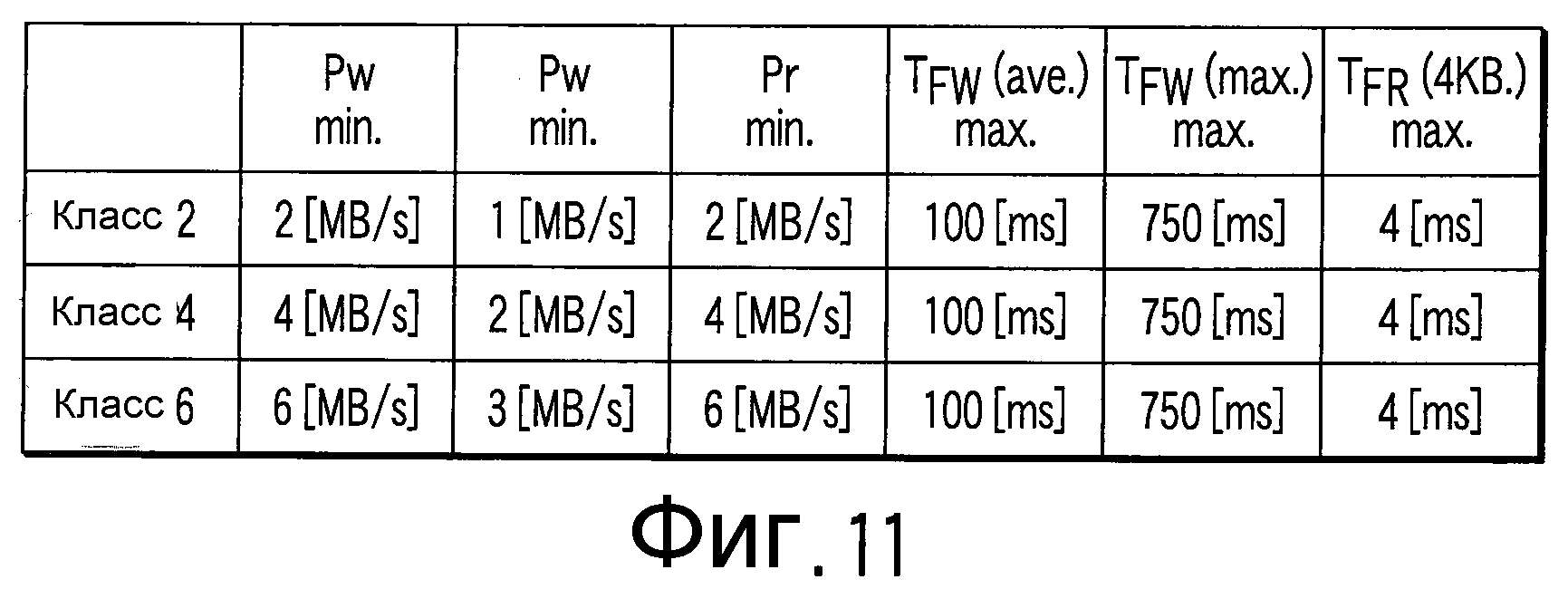

фиг.11 - таблица, показывающая требуемые характеристики карты каждого класса;

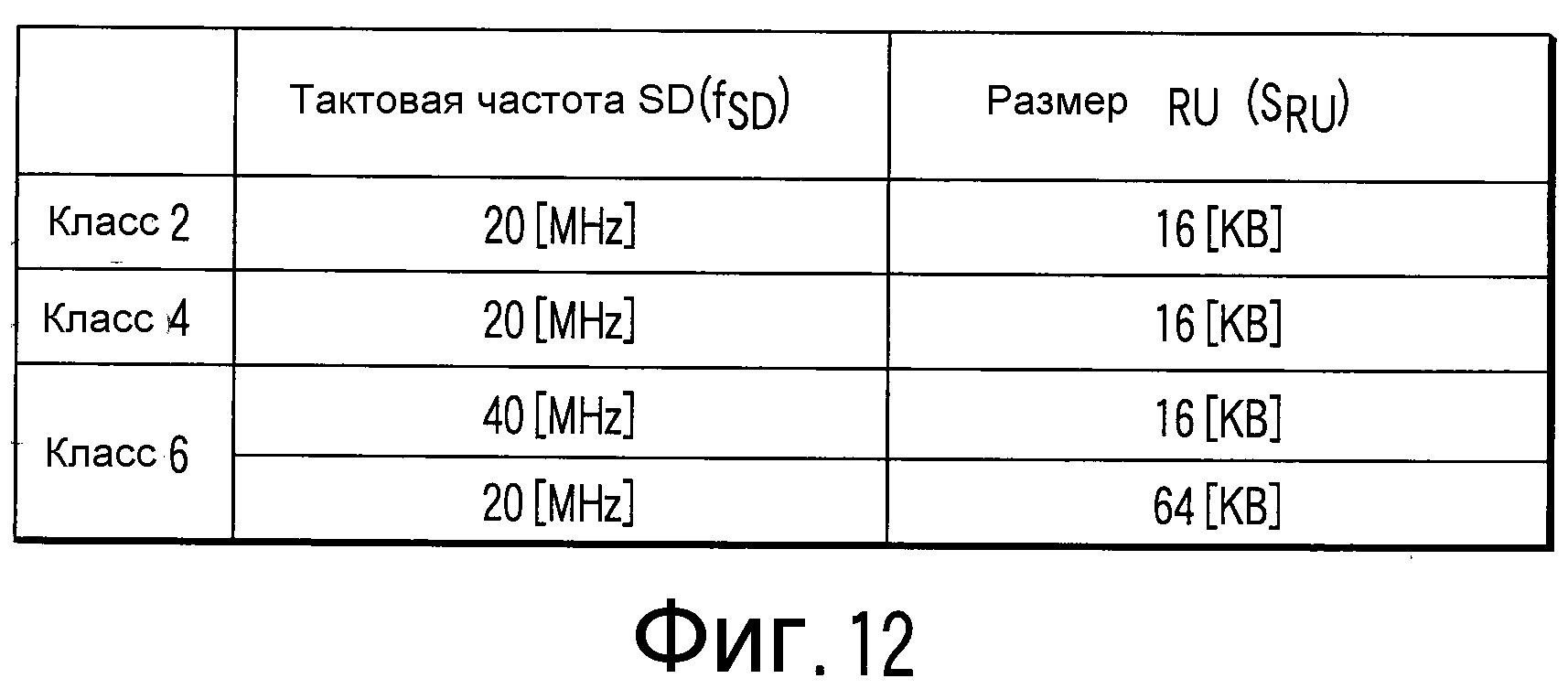

фиг.12 - таблица, показывающая условия измерения требуемых характеристик карты каждого класса;

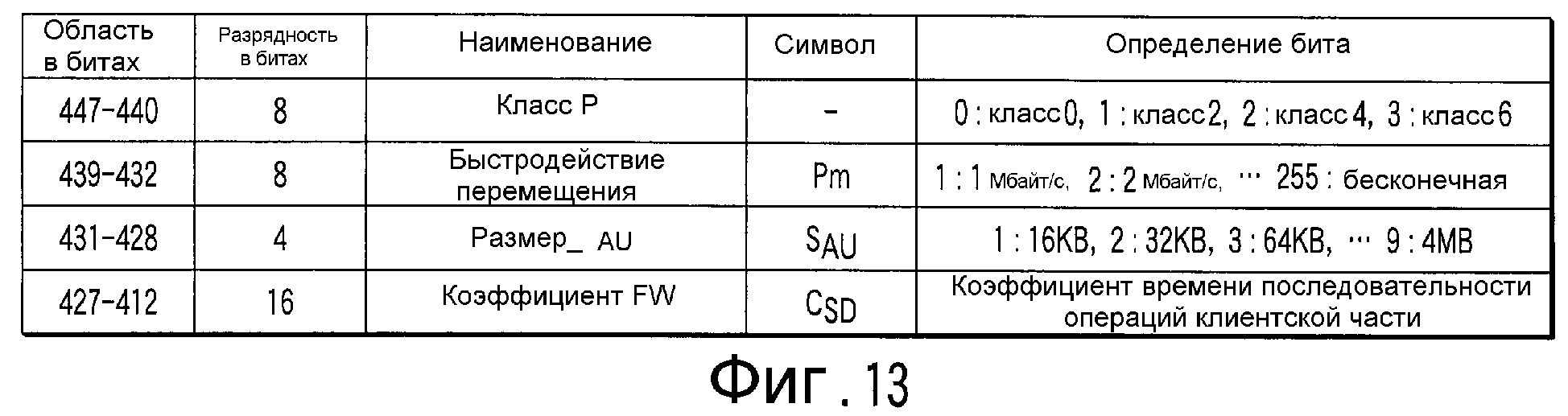

фиг.13 - представление, показывающее контент, хранимый в регистре карты памяти SD™;

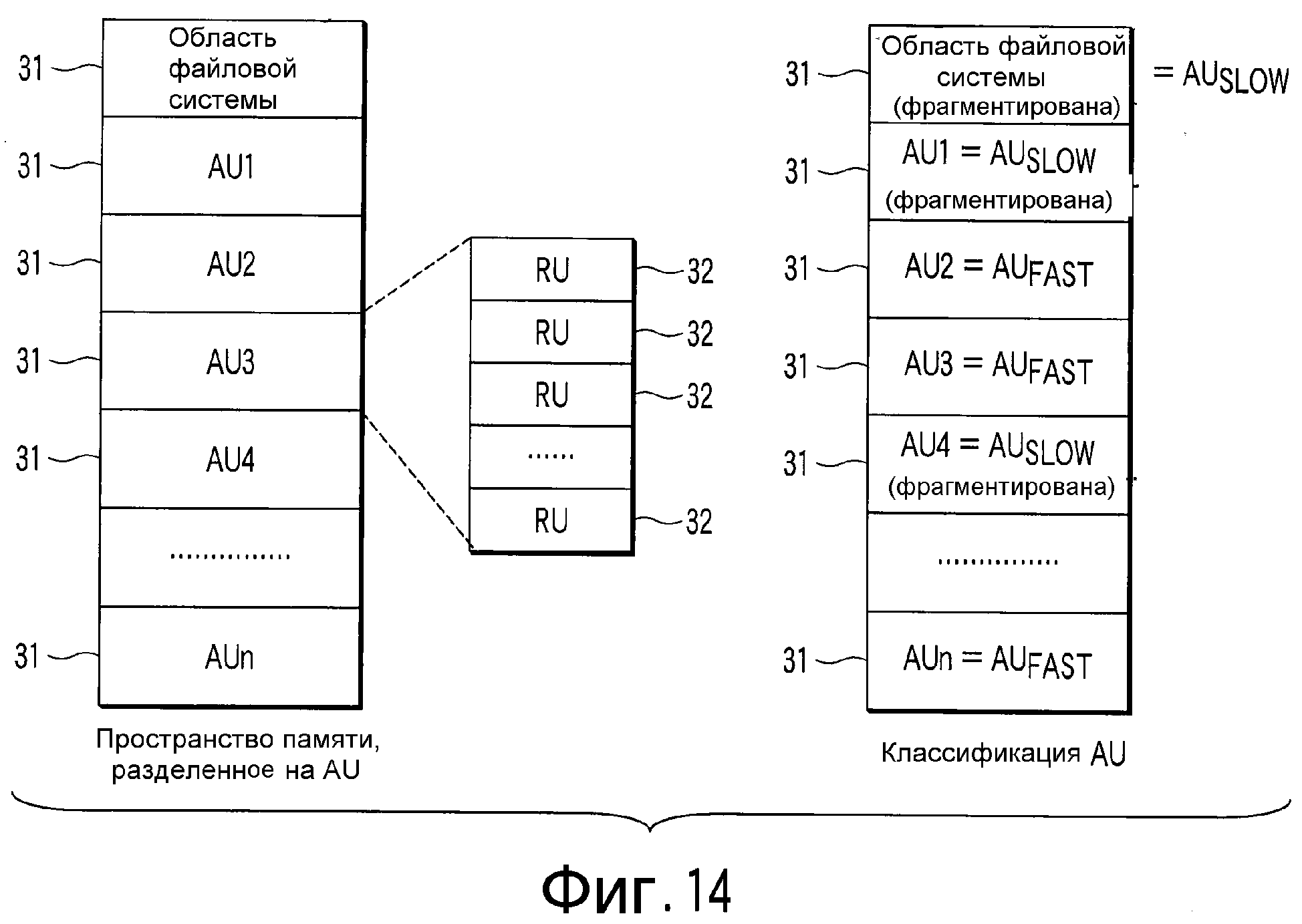

фиг.14 - представление, показывающее классификацию AU относительно области карты памяти в первом варианте осуществления;

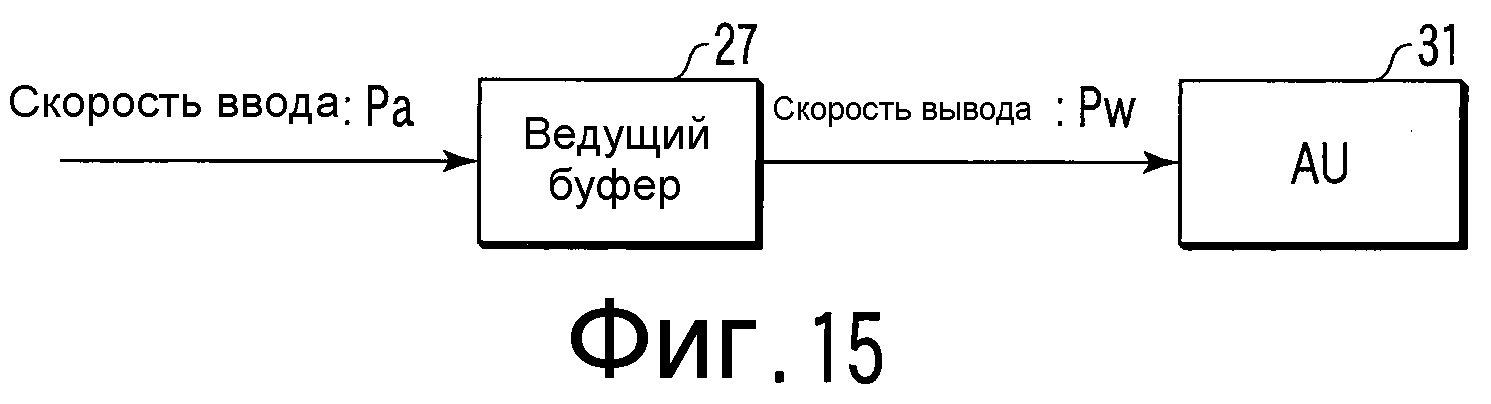

фиг.15 - представление для пояснения принципа ведущего буфера в первом варианте осуществления;

фиг.16 - представление, показывающее случай, где все используемые RU собраны в передней позиции AU;

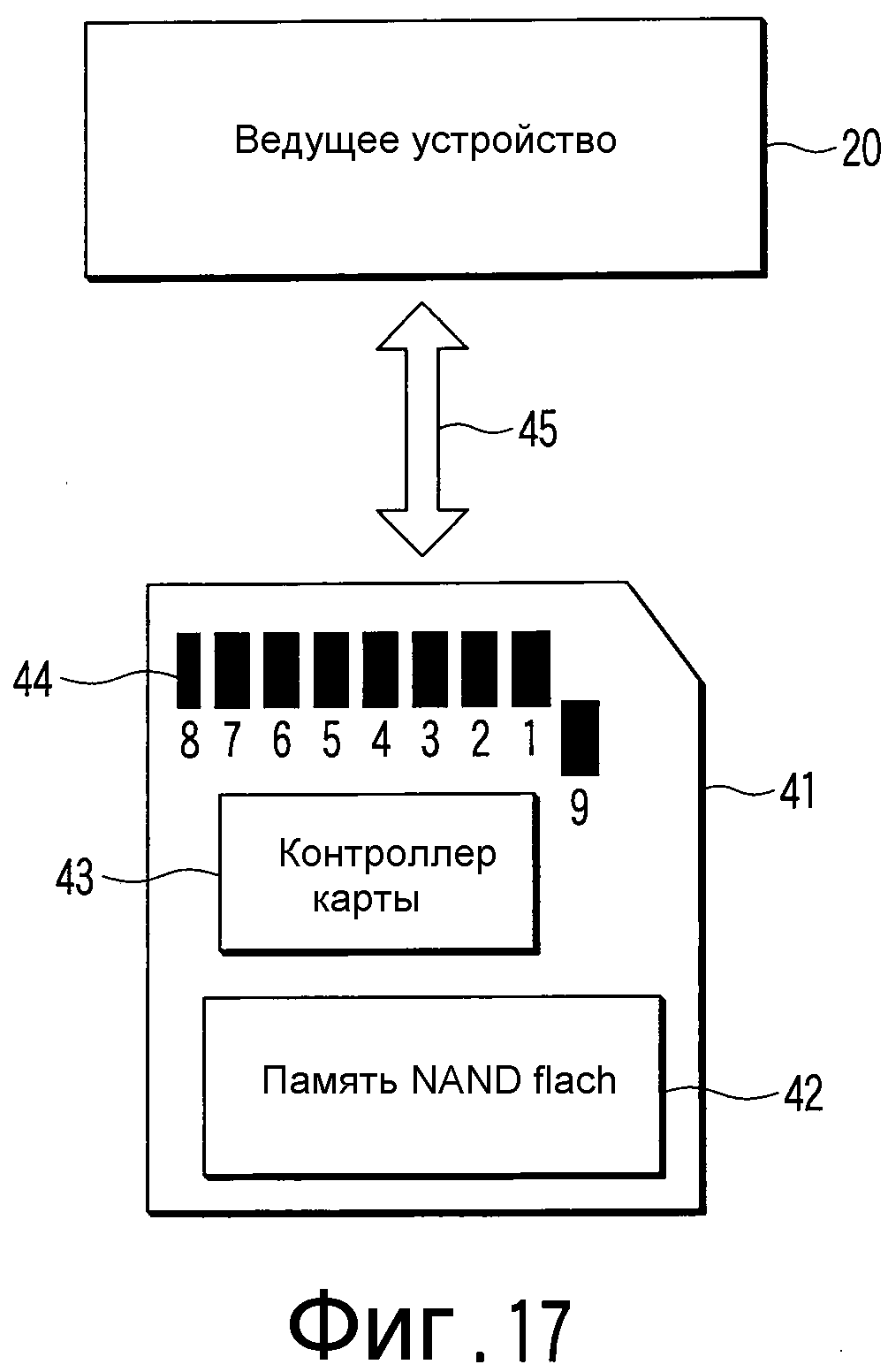

фиг.17 - представление, показывающее конфигурацию карты памяти согласно второму варианту осуществления настоящего изобретения;

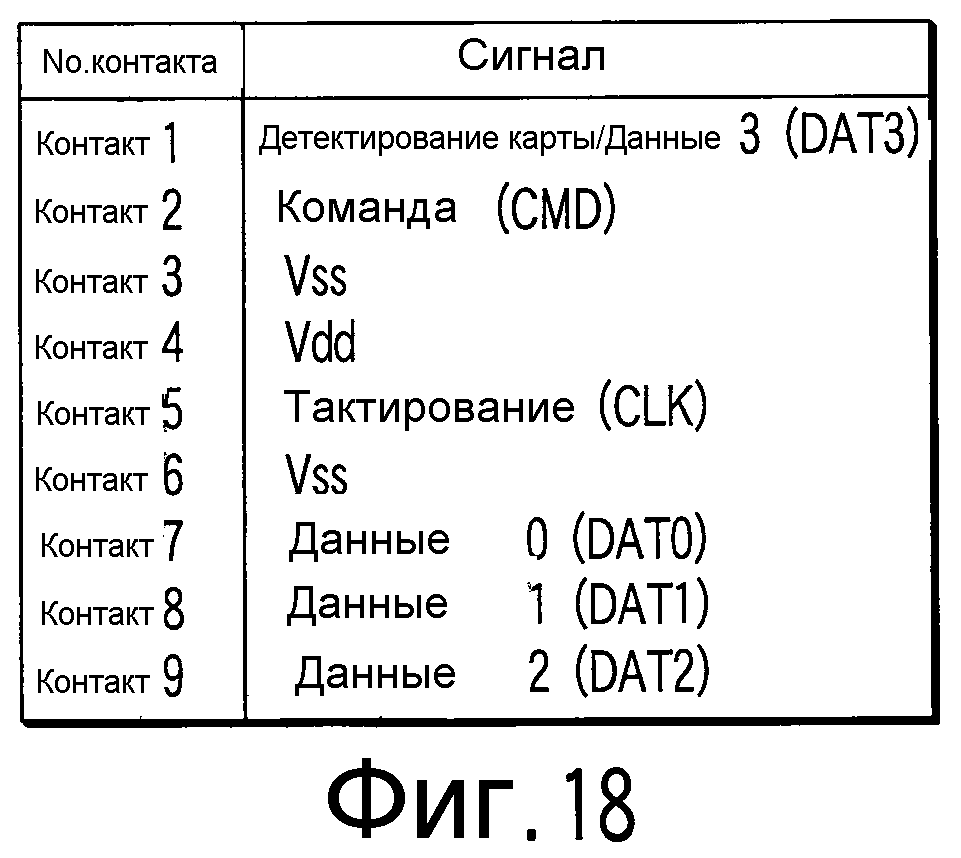

фиг.18 - таблица для пояснения распределения сигналов относительно сигнальных контактов в карте памяти по второму варианту осуществления;

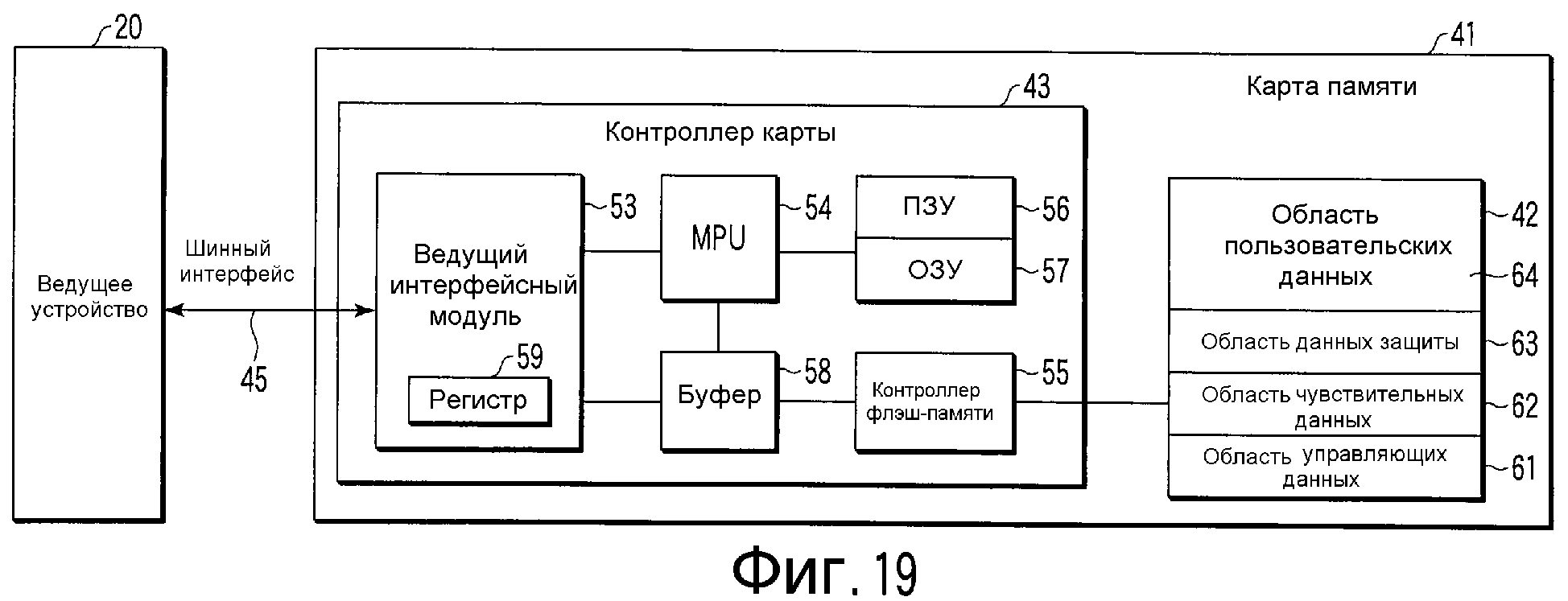

фиг.19 - структурная схема, показывающая конфигурацию аппаратных средств карты памяти по второму варианту осуществления;

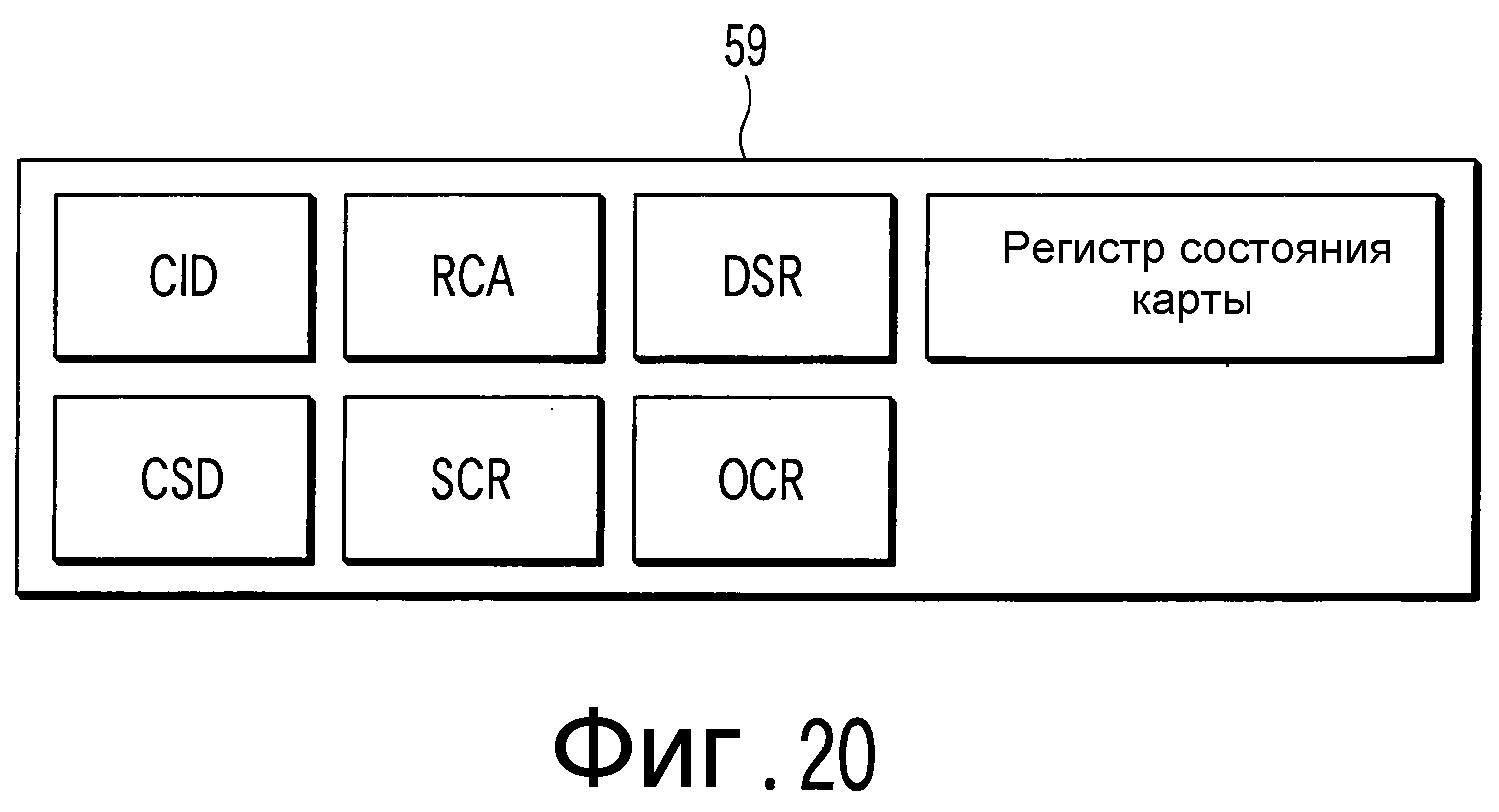

фиг.20 - структурная схема, показывающая конфигурацию регистра карты памяти по второму варианту осуществления;

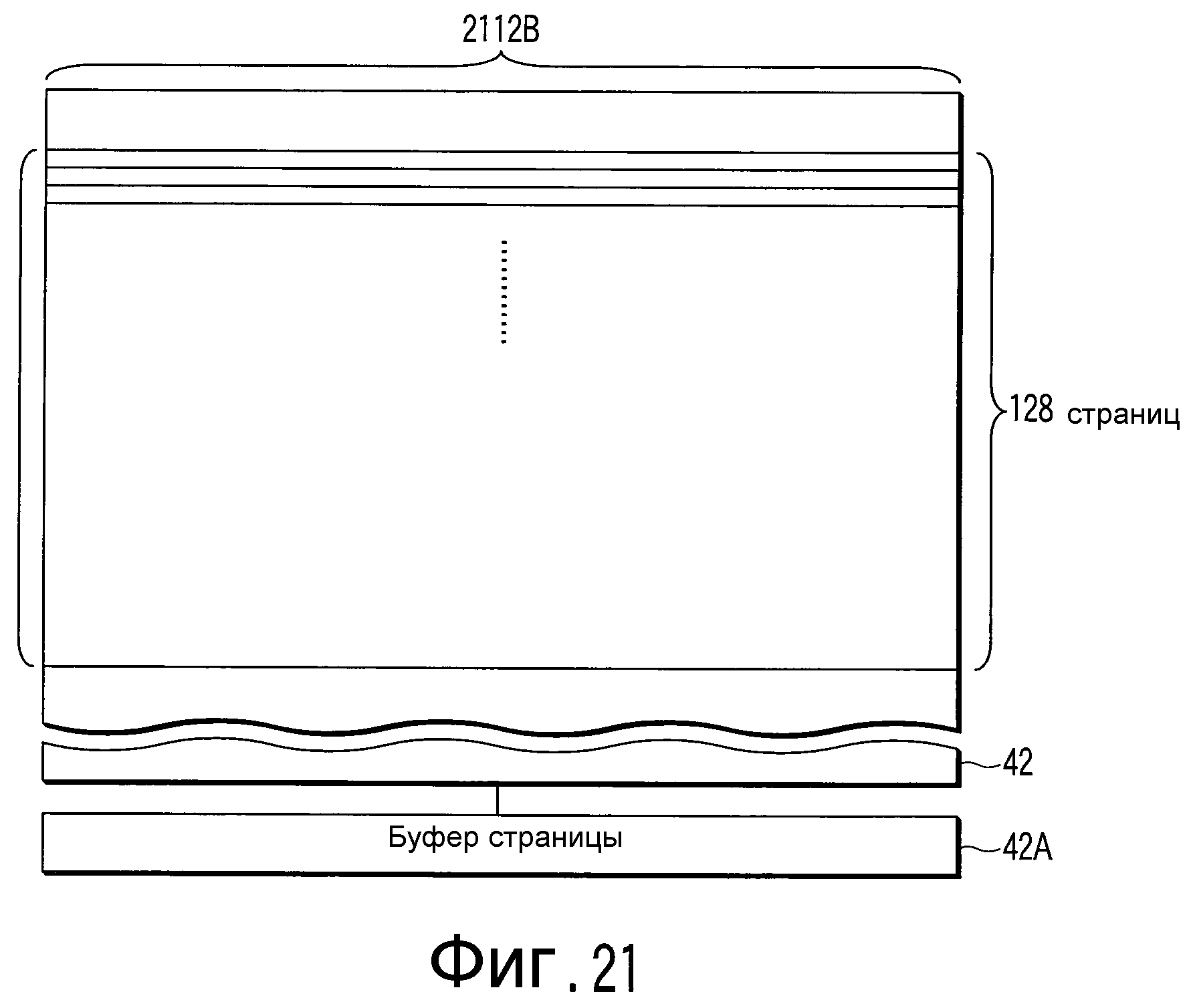

фиг.21 - представление, показывающее конфигурацию ячейки памяти и буфера в карте памяти по второму варианту осуществления; и

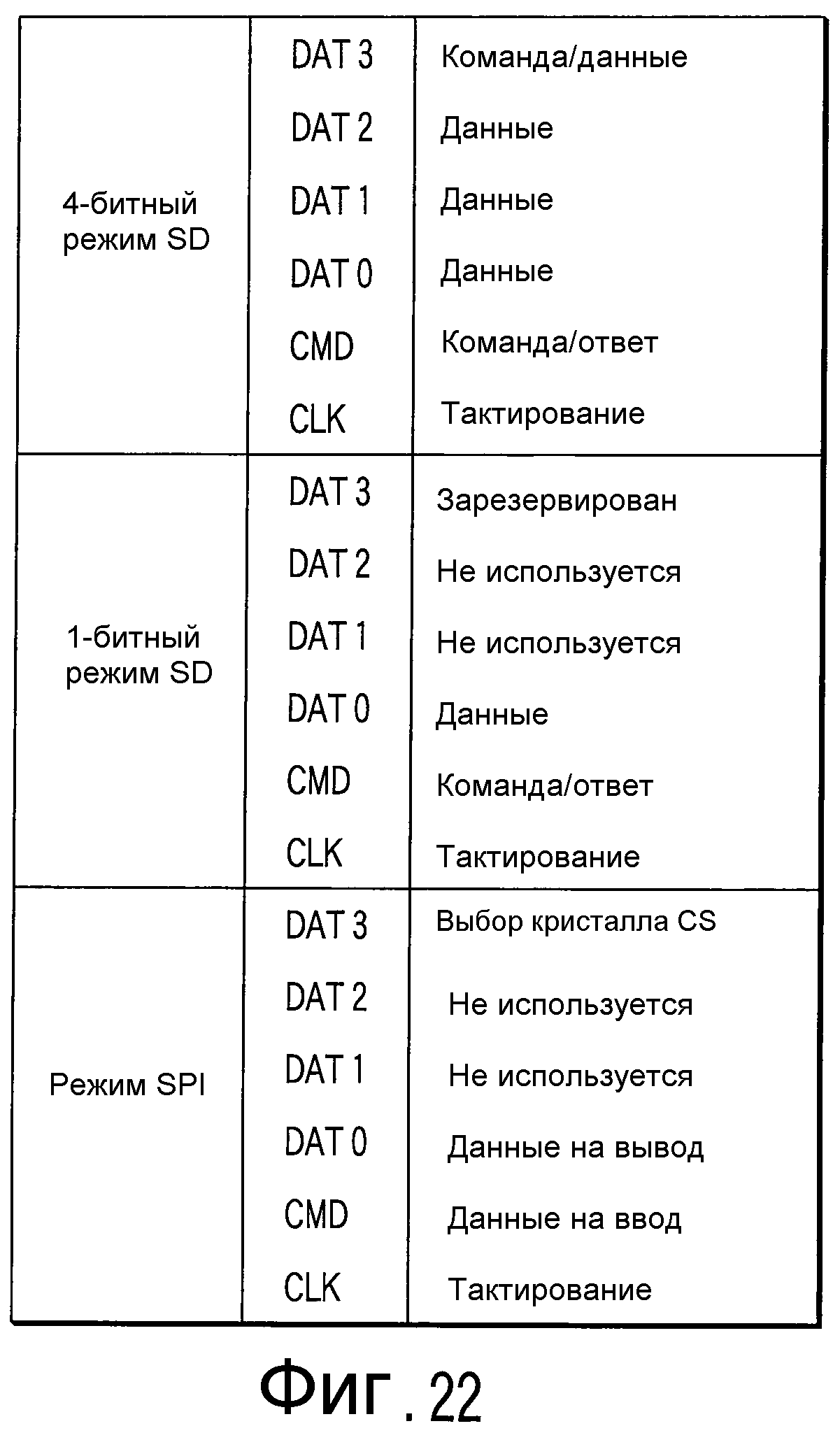

фиг.22 - таблица для пояснения распределения сигналов относительно сигнальных контактов шины SD в различных режимах работы.

ОСУЩЕСТВЛЕНИЕ ИЗОБРЕТЕНИЯ

Варианты осуществления настоящего изобретения будут описаны ниже со ссылкой на сопроводительные чертежи. Эти варианты осуществления не ограничивают настоящее изобретение.

(Первый вариант осуществления)

Первый вариант осуществления относится к запоминающему устройству, содержащему встроенное энергонезависимое полупроводниковое запоминающее устройство, и к ведущему устройству, использующему запоминающее устройство.

[1] Конфигурация запоминающего устройства и ведущего устройства

В последующем описании память NAND flash™ используется в качестве энергонезависимого полупроводникового запоминающего устройства, встроенного в запоминающее устройство, используемое для ведущего устройства согласно первому варианту осуществления настоящего изобретения.

Фиг.1 - структурная схема, показывающая конфигурацию полупроводникового запоминающего устройства (полупроводниковой памяти) в случае реализации полупроводникового запоминающего устройства согласно первому варианту осуществления с использованием памяти NAND flash™.

На фиг.1 номер 11 ссылки обозначает матрицу ячеек памяти. Матрица 11 ячеек памяти снабжена несколькими числовыми линиями, линиями стробирования выборки и разрядными линиями (не показаны). Несколько числовых линий и разрядных линий соединены в несколько ячеек памяти (не показаны). Несколько ячеек памяти поделены на несколько блоков, как описано позже.

Матрица 11 ячеек памяти присоединена к схеме 12 фиксации данных и схеме 13 дешифратора строк. Схема 12 фиксации данных содержит большое количество схем-защелок. Схема 13 дешифратора строк избирательно возбуждает несколько числовых линий и линий стробирования выборки.

Схема 12 фиксации данных временно удерживает данные, считываемые через разрядную линию при чтении данных из матрицы 11 ячеек памяти. Схема 12 фиксации данных временно удерживает данные записи при записи данных по отношению к матрице 11 ячеек памяти, а затем подает их в матрицу 11 ячеек памяти через разрядную линию.

Схема 12 фиксации данных присоединена к буферу 14 ввода/вывода (буферу I/O) и схеме 15 дешифратора столбцов. При чтении данных считываемые данные, удерживаемые в схеме 12 фиксации данных, то есть только выбранные данные, считываются наружу полупроводникового запоминающего устройства с помощью и в соответствии с выходным сигналом схемы 15 дешифратора столбцов. При записи данных данные записи, подаваемые снаружи полупроводникового запоминающего устройства через буфер 14 ввода/вывода, фиксируются схемой-защелкой схемы 12 фиксации данных, которая выбрана в соответствии с выходным сигналом схемы 15 дешифратора столбцов.

Схема 13 дешифратора строк избирательно возбуждает упомянутые числовые линии и линии стробирования выборки, включенные в матрицу 11 ячеек памяти, при чтении и записи данных. При таком образе действий ячейки памяти, соответствующие одной странице матрицы 11 ячеек памяти, выбираются одновременно.

Защелка 16 адреса защелкивает входной сигнал адреса, а затем подает адрес строки в схему 13 дешифратора строк наряду с подачей адреса столбца на схему 15 дешифратора столбцов.

Защелка 17 команды принимает входной сигнал команды. Защелка 17 команды присоединена к дешифратору 18 команд. Дешифратор 18 команд декодирует команду для вывода разнообразных управляющих сигналов. На основании управляющих сигналов, выведенных из дешифратора 18 команд, управляется работа схемы 12 фиксации данных, схемы 13 дешифратора строк, буфера 14 ввода/вывода, схемы 15 дешифратора столбца и защелки 16 адреса.

В памяти NAND flash™ защелка адреса и защелка команды присоединены к буферу 14 ввода/вывода (не показан). Таким образом, адрес и команда подаются с входного/выходного контакта памяти NAND flash™.

Полупроводниковое запоминающее устройство снабжено схемой генератора высокого напряжения и промежуточного напряжения (не показана), в дополнение к этим схемам. Схема генератора высокого напряжения и промежуточного напряжения формирует высокое напряжение и промежуточное напряжение, подаваемое в схему 13 дешифратора строк и матрицу 11 ячеек памяти при записи и стирании данных.

Фиг.2 показывает запоминающее устройство, в которое встроена память по фиг.1, и ведущее устройство, использующее запоминающее устройство. Запоминающим устройством 19 является карта памяти, например карта памяти SD™. Пояснение случая использования карты памяти SD™ будет приведено позже.

Как показано на фиг.2, флэш-память (то есть пространство 21 памяти на фиг.2) и контроллер 22 для управления флэш-памятью встроены в карту памяти. Флэш-память имеет конфигурацию, показанную на фиг.1.

Контроллер 22 устройства включает в себя регистр 23 информации о версии, регистр 24 кода идентификации быстродействия и регистр 25 параметра быстродействия. Регистр 23 информации о версии удерживает информацию о версии. Информация о версии используется для идентификации версии карты памяти. Регистр 24 кода идентификации быстродействия удерживает код идентификации быстродействия. Код идентификации быстродействия используется для идентификации группировки быстродействия (класса быстродействия). Регистр 25 параметра быстродействия удерживает параметр быстродействия (описан позже) запоминающего устройства.

Когда запоминающее устройство 19 присоединено к ведущему устройству 20, ведущее устройство 20 управляет встроенным ведущим контроллером 26 с использованием встроенного процессора 28 для выполнения обмена данными с запоминающим устройством 19.

Для того чтобы отправить данные с ведущего устройства 20, данные временно фиксируются в ведущем буфере (буферной памяти) 27, а после этого отправляются в запоминающее устройство 19 через ведущий контроллер 26. В этом случае ведущий буфер 27 может до некоторой степени демпфировать изменения быстродействия запоминающего устройства в зависимости от времени.

Ведущий буфер 27 может быть реализован с использованием части системной памяти 29. При таком образе действий нет необходимости предоставления специальной памяти, такой как ведущий буфер 27, и, в дополнение, является эффективным резервировать его в системной памяти 29, так как обычно требуется большой ведущий буфер 27.

Ведущее устройство 20 может записывать данные с использованием единовременной команды многоблочной записи (то есть команды для записи нескольких непрерывных блоков с использованием одной команды записи).

[2] Определение быстродействия по стандартам карты

Запоминающее устройство 19 удерживает класс быстродействия, соответствующий собственному быстродействию и различной информации параметров быстродействия, с тем, чтобы ведущее устройство 20 могло узнать быстродействие запоминающего устройства 19. Определение параметра быстродействия будет пояснено ниже. В последующем пояснении карта памяти, в частности карта памяти SD™, дана в качестве примера запоминающего устройства 19.

Быстродействие передачи данных из ведущего устройства 20 в запоминающее устройство (карту памяти) 19 принимается в качестве скорости передачи по шине 30 управления. В этом случае шина 30 управления соответствует толстой стрелке, в двух направлениях соединяющей ведущий контроллер 26 и контроллер 22 устройства на фиг.2. Скорость передачи задана при допущении, что ведущее устройство выполняет запись в оптимальном состоянии.

[2-1] Определение кривой быстродействия

[2-1-1] Разделение пространства памяти

Сначала ниже будет пояснено разделение пространства памяти ведущим устройством 20 и запоминающим устройством 19. Так как это необходимо для пояснения кривой быстродействия, используемой для задания класса быстродействия.

Ведущее устройство 20 разделяет пространство 21 памяти на элементы, требующие элемента записи (RU) 16 килобайт для записи данных, таких как видеоданные, для каждого RU. Более точно, RU (пространство модуля записи) эквивалентен элементу, записанному единовременной командой многоблочной записи.

Например, RU является таким же, как кластер, определенный файловой системой SD™, или имеет размер целых кратных количеств кластера.

Элемент RU может быть задан как 32 килобайта, 64 килобайта, 128 килобайт и т.д. Как описано позже, ведущее устройство 20 подсчитывает количество RU, допускающих запись данных, и тем самым может рассчитать оставшееся время записи.

Фиг.3 показывает деление пространства 21 памяти, предполагаемое ведущим устройством 20, и реальное деление пространства 21 памяти согласно карте 19 памяти. Левая сторона фиг.3 соответствует делению пространства 21 памяти, предполагаемому ведущим устройством 20. С другой стороны, правая сторона фиг.3 соответствует фактическому делению пространства 21 памяти устройством 19 памяти.

Как видно из фиг.3, RU 32 является элементом памяти, в то время как рассматривается с ведущего устройства 20. Элемент 31 выделения (AU) определен как набор нескольких RU 32. AU (область элемента управления) является элементом управления и определен как элемент, используемый для деления всего пространства 21 памяти запоминающего устройства 19 на размер SAU AU.

Отношение между RU 32 и AU 31 подобно отношению между страницей 34 и блоком 33 при рассмотрении пространства 21 памяти из запоминающего устройства 19 (контроллера 22 устройства). Страница 34 является элементом доступа, когда контроллер 22 устройства выполняет запись или чтение по отношению к пространству 21 памяти. Блок 33 состоит из нескольких страниц 34 и используется в качестве элемента, когда контроллер 22 устройства стирает пространство 21 памяти.

Например, если память NAND flash™ TC58512FT, произведенная корпорацией Тошиба, используется в качестве пространства 21 памяти, размером страницы 34 является 512 байт, а размером блока 33 является 16 килобайт. (В этом случае избыточная емкость игнорируется для упрощения). Память NAND flash™, чьим размером страницы является 2 килобайта или 4 килобайта, также может использоваться.

Страница 34 и RU 32 не нуждаются в соответствии друг другу. RU 32 может быть установлен в целые кратные количества страниц 34. Подобным образом размер SAU AU является целым кратным количеством размера RU. AU 31 может быть установлен в целые кратные количества блока 33. В последующем будет приведено пояснение использования RU 32 и AU 31 в качестве основного элемента.

[2-1-2] Как определить кривую быстродействия

Кривая быстродействия будет описана ниже со ссылкой на фиг.4, представляющую следующий случай в качестве примера. А именно, ведущее устройство 20 подряд записывает данные элемента RU с позиции А до позиции В в пространстве 21 памяти.

Типично область от А до В соответствует AU 31. В последующем описании данные вновь записываются в AU, включающий в себя RU 31 в качестве примера. Как показано на фиг.4, логический адрес AU 31 задан как LA. Когда данные вновь записываются в каждый RU 32 AU 31, фактически требуются следующие действия. Сначала данные в RU 32 (показанном посредством «Занят» на фиг.4), который удерживает данные в существующем физическом блоке PAA, записываются в RU другого физического блока PAB. Затем в него должны быть записаны новые данные записи. В таком случае физический блок PAB вновь отображается на логический адрес LA.

Время новой записи данных в RU 32 (показанный посредством «Свободен» на фиг.4), который изначально не удерживает данных, соответствует времени записи. Время записи определяется в качестве быстродействия Pw записи.

С другой стороны, когда уже записанные данные копируются в другой RU 32, время отнимается на чтение данных из старого RU 32 (например, RU 32a), в дополнение ко времени записи данных в RU32 (например, RU 32b) нового физического блока PAB.

Когда существует занятый RU 32 в старом физическом блоке PAA, занятый RU 32 пропускается, а данные записываются в свободный RU 32 (например, RU с «Данными 3»). Данным в занятом RU 32 необходимо записываться в RU 32 (например, RU 32b) назначения до того, как записаны новые данные. Запись новых данных останавливается, в то время как перемещаются данные в занятом RU 32. Время, потраченное на операцию, определяется в качестве быстродействия Pm перемещения данных. Таким образом, полное время, потраченное на запись новых данных, является суммой полного времени записи и полного времени перемещения.

По предшествующему пояснению, когда среднее быстродействие P(Nu) выражается формулой, получается следующее математическое выражение 1.

[Математическое выражение 1]

Среднее быстродействие:

P(Nu) = [Sc × (Nt - Nu)] / [Sc × (Nt - Nu) / Pw + Sc × Nu/Pm] = [(Nt - Nu) × Pm × Pw] / [(Nt - Nu) × Pm + Nu × Pw],

где

Sc: размер RU,

Nt: Полное количество RU, подряд записанных от А до В (количество RU, формирующих AU),

Nu: Количество занятых RU между А и В (количество занятых RU, включенных в AU),

Pw: Быстродействие записи (единица измерения: Мбайт/с),

Pm: Быстродействие перемещения (единица измерения: Мбайт/с)

Вышеизложенное математическое выражение определено при допущении, что быстродействие определяется с использованием быстродействия Pw записи и быстродействия Pm перемещения.

Быстродействие Pw записи изменяется в зависимости от времени программирования карты 19 памяти (флэш-памяти [пространства 21 памяти]). Более того, быстродействие Pw записи определено в качестве наименьшего значения среднего значения быстродействия, когда запись выполняется непрерывно во все RU 32 по AU 31, который состоит из трех RU 32.

Отметим, что быстродействие записи изменяется в зависимости от времени последовательности операций, расходуемого клиентской частью. Время последовательности операций клиентской части зависит от тактовой частоты, задаваемой картой памяти SD™, в качестве примера. Этот предмет будет описан ниже. Фиг.5 - представление, показывающее временные характеристики операции записи, когда используется команда многоблочной записи. На первой стадии операции записи серверная часть ожидает до тех пор, пока данные записи не поступают от клиентской части. На второй стадии серверная часть приводится в действие вместе с клиентской частью. Поэтому время записи, расходуемое на многоблочную запись, должно рассматриваться независимо от клиентской части и серверной части. На второй стадии время записи серверной части доминирует над временем записи по сравнению с временем последовательности операций клиентской части.

Время tWB записи серверной части является суммой времени до тех пор, пока не завершена вся запись, после того, как начата запись во флэш-память (пространство 21 памяти).

С другой стороны, время tWF последовательности операций клиентской части является суммой времени от начала команды многоблочной записи до начала записи во флэш-память. Как описано выше, если в качестве примера дана карта памяти SD™, время tWF последовательности операций клиентской части зависит от тактовой частоты SD. Поэтому время tWF последовательности операций клиентской части выражается с использованием коэффициента CSD и тактовой частоты fSD у SD. Таким образом, время tWF последовательности операций клиентской части выражается с использованием следующего математического выражения 2 в карте памяти SD™.

[Математическое выражение 2]

Время последовательности операций клиентской части:

tWF = CSD / fSD.

Если данные записываются в один AU 31, время tWF последовательности операций клиентской части пропорционально количеству команд записи. Количество команд записи равно количеству NRU RU 32. Если количество NRU возрастает, то есть размер SRURU становится малым, быстродействие записи снижается.

Быстродействие Pm перемещения определяется в качестве наименьшего значения среднего быстродействия перемещения. Быстродействие Pm перемещения рассчитывается как среднее значение, когда непрерывные RU 32 перемещаются, чтобы сформировать один завершенный AU 31. Время перемещения определяется на стороне серверной части и не находится под влиянием тактовой частоты SD. Если карта 19 памяти не нуждается в перемещении RU 32, быстродействие Pm перемещения определяется как являющееся бесконечным. Это выражено как «1 / Pm = 0».

Более того, быстродействие Pm перемещения изменяется в зависимости от времени чтения, описанного позже, и перемещения данных в добавление ко времени программирования флэш-памяти. В этом случае перемещение данных выполняется внутри карты 19 памяти; поэтому ведущее устройство 20 не контролирует перемещение данных непосредственно.

Следующие два значения определяются, когда рассматривается быстродействие чтения.

1) Быстродействие чтения относительно данных

Быстродействие чтения по отношению к данным (в дальнейшем указываемое ссылкой как быстродействие чтения) Pr определяется в качестве наименьшего значения среднего значения быстродействия при чтении данных среди элементов RU 32 случайным образом. Среднее значение может рассчитываться на основании 256-кратных случайных чтений среди элементов RU 32. Более того, наихудший случай должен рассматриваться во времени, потраченном для выполнения исправлений с использованием кода с исправлением ошибок (ECC) по отношению к каждому блоку 33. Быстродействие Pr чтения должно быть большим чем или по меньшей мере равным быстродействию Pw записи.

2) Время чтения файловой системы (FAT)

Время чтения TFR(4 кбайта) файловой системы, такой как таблица размещения файлов (FAT), определено в качестве максимального времени при считывании FAT в 4 кбайта. В этом случае чтение FAT должно быть возможным во время записи AU. Это происходит, так как, учитывая случай записи в реальном времени, ведущее устройство 20 должно считывать FAT между записями AU. Более того, наихудший случай должен рассматриваться во времени, потраченном для выполнения исправлений с использованием кода с исправлением ошибок (ECC) по отношению к каждому блоку 33. Время чтения FAT относительно размера файловой системы (размера FR) SFR выражается с использованием функции CEIL, как изложено ниже.

Время чтения FAT по отношению к размеру SFR [кбайт]:

[x] представляет функцию CEIL, которая преобразует десятичную дробь x в наименьшее целое число, меньшее или равное x.

Фиг.6 показывает быстродействие карты 19 памяти, рассчитанное согласно математическому выражению 1. На фиг.6 показано быстродействие, когда количество Nt RU 32, формирующих AU 31, установлено в качестве 16.

Как видно из фиг.6, быстродействие (вертикальная ось) определяется для каждой доли занятых RU (горизонтальная ось). Затем быстродействия по каждой доле r занятых RU соединяются и тем самым получается кривая быстродействия. Кривая быстродействия является важной информацией для изготовителей ведущих устройств.

Кривая быстродействия задана с использованием быстродействия Pw записи и быстродействия Pm перемещения. Быстродействие Pw записи равно полному быстродействию, когда доля r = 0 занятых RU.

Доля r занятых RU выражается в качестве следующего математического выражения с использованием количества Nt RU 32 из AU 31 и количества Nu занятых RU 32.

r = Nu / Nt

Это равенство также выражается, как изложено ниже.

Nu = r × Nt

Доля r занятых RU изменяется в диапазоне от 0 до 1. Когда r = 0, это означает, что все RU 32 незаняты. С другой стороны, когда r = 1, это означает, что все RU 32 заняты, то есть быстродействие составляет 0; другими словами, задано P(1) = 0.

Можно видеть, что любые кривые быстродействия проходят через точку (1, 0). При повторной записи математического выражения 1 с использованием «r» получается следующее математическое выражение 3.

[Математическое выражение 3]

Кривая среднего быстродействия:

P(r) = [(1 - r) × Pw × Pm] / [r × Pw + (1 - r) × Pm],

где 0 ≤ r ≤ 1.

Быстродействие изображено графически с использованием выражения 3, и тем самым получена кривая быстродействия, показанная на фиг.6.

[2-1-3] Положение области памяти и точность быстродействия

Если начальный адрес записи данных RU 32 не является границей блока 33 пространства 21 памяти, требуется следующее время. Более точно, время для перемещения записанных данных требуется с тем, чтобы начальная позиция записи соответствовала границе блока 33. По этой причине, в таком случае, фактическое быстродействие является худшим по отношению к ожидаемому быстродействию. Для того чтобы измерить точное быстродействие, необходимо удовлетворить требованиям, что адреса А и В соответствуют границе элемента стирания (блока 33). Задание элемента выделения вытекает из причины, описанной выше.

[2-2] Параметр, относящийся к обновлению файловой системы во время записи

Обновление файловой системы вставляется в последовательность записи, и тем самым общее (фактически полученное) быстродействие записи уменьшается. По этой причине ведущему устройству 20 требуются параметры, относящиеся к обновлению файловой системы, при расчете быстродействия карты 19 памяти, как описано позже. Ведущее устройство 20 может рассчитывать снижение фактического быстродействия оказанием влияния тем, что обновление файловой системы вставлено в последовательность записи.

Фиг.7 показывает типичную последовательность обновления файловой системы во время записи в реальном времени. В последующем описании FAT используется в качестве типичного примера файловой системы.

Обновление файловой системы (FAT), возможно, происходит после любой записи RU 32. FAT обновляется периодически. Количество RU 32, записанных между определенным обновлением файловой системы и следующим обновлением файловой системы, задано периодом TFU обновления файловой системы. Количеством RU 32, записываемых между обновлениями файловой системы, является Nd.

Цикл записи FAT содержит три операции записи. На фиг.7 FAT1 и FAT2 символизируют запись информации FAT, соответственно, в FAT1 и FAT2, с использованием одной команды многоблочной записи. Запись файловой системы (FAT) может начинаться с адреса произвольного байта и может определяться в качестве записи, находящейся в диапазоне от 16 килобайт до произвольной длины.

На фиг.7 DIR обозначает элемент каталога. DIR формируется перед записью, а запись выполняется только в порцию 512 байт, содержащую элемент каталога обмена. Время TFW записи файловой системы определено как полное время цикла записи файловой системы, то есть полное время записи FAT1, FAT2 и DIR. Время TFW записи файловой системы изменяется в зависимости от технических условий контроллера 22 устройства.

[2-2-1] Условия измерения среднего значения времени TFW записи файловой системы

Время TFW записи файловой системы определено в качестве значения, полученного из среднего значения нескольких измеренных значений. Последующее математическое выражение 4 используется для задания среднего времени TFW(ave.) записи файловой системы. Как видно из последующего математического выражения 4, наихудшее значение среднего значения произвольных восьмиразовых циклов записи файловой системы используется в качестве среднего времени записи файловой системы TFW(ave.).

[Математическое выражение 4]

Среднее время записи файловой системы:

(TFW(ave.)) = [max (TFW(1) + TFW(2) + ... TFW(7) + TFW(8))] / 8.

[2-2-2] Максимальное время записи файловой системы

Как описано позже, ведущее устройство 20 временно удерживает данные с использованием ведущего буфера 27 во время обновления файловой системы. Таким образом, максимальный период обновления файловой системы должен быть учтен при определении минимального размера ведущего буфера 27. Требования по размеру ведущего буфера 27 будут пояснены в последующем [4-5].

Следующее математическое выражение 5 используется для задания наихудшего значения времени записи файловой системы (FAT).

[Математическое выражение 5]

Наихудшее значение времени записи файловой системы (FAT): (TFW (max)) ≤ 750 [мс].

[2-2-3] Независимость записи данных и записи файловой системы

Запись файловой системы может вставляться между RU или AU в течение записи в реальном времени. Контроллеру 22 устройства необходимо быть способным осуществлять контроль без влияния на быстродействие Pw записи самих данных.

Влияние записи файловой системы на быстродействие Pw записи может быть устранено следующим образом. Более точно, возобновление записи после прерывания записи записью файловой системы выполняется с физической области, следующей за той, в которую данные записаны последними перед прерыванием.

Для того чтобы реализовать контроль, может быть предусмотрен блок данных кэша для записи файловой системы, а контроллер 22 устройства может осуществлять контроль, как описано ниже. Как показано на фиг.8А, пространство 21 памяти включает в себя нормальный физический блок и блок данных кэша. Когда запись файловой системы запрашивается во время последовательной записи непрерывных данных в нормальный физический блок, как показано на фиг.8А, информация управления файлами подряд записывается в свободную область (страницу 34) блока кэша данных, как изображено на фиг.8В. После этого, как видно из фиг.8С, запись данных возобновляется с области (страницы 34), следующей за таковой, в которую данные записаны последними перед прерыванием.

Когда запись прерванной записи данных возобновлена в физической области, которая не является следующей за физической областью (например, областью в новом блоке или блоке 2), в которой данные записаны последними перед возобновлением, подобно предшествующему уровню техники, происходит сопутствующая запись перемещения данных. Как результат, быстродействие Pw записи изменяется вследствие записи файловой системы.

Исследование адреса, размера и последовательности дает возможность классифицировать нормальные данные и информацию управления файлами.

[3] Классификация карты памяти

Для того чтобы без задержки сопоставлять быстродействие карты 19 памяти и быстродействие, требуемое ведущим устройством 20, карта 19 памяти классифицирована на несколько классов (классов быстродействия) в соответствии с быстродействием карты. Класс может быть классифицирован в соответствии с параметрами быстродействия, такими как кривая быстродействия, описанная раньше, и время TFW. Контроллер устройства удерживает информацию о классе в качестве кода 24 идентификации быстродействия карты 19 памяти.

Карта 19 памяти отображает свой собственный класс, соответственно. На фиг.9 показана метка, отображающая идентификацию класса. Фиг.9 показывает случай, где устройством 19 хранения является карта памяти SD™.

Как видно из фиг.9, карта 19 памяти имеет корпус 71 и метку 72, отображающую ее класс, на корпусе 71. Корпус 71 по меньшей мере частично покрывает пространство 21 памяти и контроллер 22 устройства.

Более того, ведущее устройство 20 имеет предварительно установленный класс. Класс на ведущем устройстве 20 означает, какое наилучшее быстродействие оно может продемонстрировать, когда оно использует карту 19 памяти с таким же классом, как у ведущего устройства 20. Ведущее устройство 20 может записывать информацию, когда оно использует карту 19 памяти более низкого класса, хотя его быстродействие не является наилучшим. Фиг.9 показывает, что корпус 73 ведущего устройства 20 имеет метку 74, отображающую его класс, на нем. Ведущему устройству не обязательно показывать свой класс.

[3-1] Требование со стороны приложения

Приложение в ведущем устройстве 20 требует высокого быстродействия от карты 19 памяти, используемой приложением. Типичные примеры будут описаны ниже.

(1) Цифровая видеозапись

В MPEG2 и JPEG движения требуется прямая запись в карту 19 памяти. Быстродействие карты приблизительно в 2 Мбайт/с требуется для того, чтобы получить качество и разрешение стандартного телевизионного изображения. Быстродействие карты приблизительно в 4 Мбайт/с требуется для записи высококачественного изображения.

(2) Цифровая фотокамера, имеющая функцию непрерывной съемки

Производители цифровых фотокамер требуют карты 19 памяти, обладающей высоким быстродействием для того, чтобы реализовать функцию непрерывной съемки. Производители цифровых фотокамер могут использовать быстродействие карты и способ контроля ведущего устройства для расчета пользователем имеющейся в распоряжении скорости непрерывной съемки.

[3-2] Классификация

Фиг.10 - график для пояснения взаимосвязи между кривой быстродействия и классом. На фиг.10 есть три области, разделенные двумя кривыми быстродействия. Как видно из фиг.10, область, сформированная вертикальной осью P(r) и горизонтальной осью r, поделена на три области кривыми быстродействия класса 2 и класса 4.Вертикальная ось P(r) представляет быстродействие, а горизонтальная ось r - долю занятых RU.

Традиционные карты памяти принадлежат области, нижней по отношению к началу координат, среди трех областей, то есть классу 0 (области карты класса 0 на фиг.10). На фиг.10 область включает в себя карты памяти, имеющие самое низкое быстродействие.

Кривая быстродействия класса 2 предполагает самое низкое быстродействие карт класса 2. Эта кривая быстродействия задана двумя параметрами Pw1 (пересечения кривой быстродействия класса 2 и оси Y) и Pm1.

Подобным образом кривая быстродействия класса 4 предполагает самое низкое быстродействие карт класса 4. Эта кривая быстродействия задана двумя параметрами Pw2 (пересечения кривой быстродействия класса 4 и оси Y) и Pm2.

Когда приложение порождает дополнительно повышенное требование, должны задаваться кривые быстродействия класса 8, класса 10, обладающие более высоким уровнем. Однако нет необходимости изменения принципа. Если определена кривая быстродействия класса 8, область класса 6 занимает область, указывающую более высокое быстродействие, чем кривая быстродействия класса 6, и более низкое, чем кривая быстродействия класса 8. Область класса 8 занимает область, указывающую более высокое быстродействие, чем кривая быстродействия класса 8.

Фиг.11 - таблица, показывающая характеристики, требуемые для карты каждого класса. Параметры, требуемые для карт класса 2 (Класса 2), класса 4 (Класса 4) и класса 6 (Класса 6), являются такими, как изложено ниже и как показано на фиг.11.

Класс 2: Pw = 2[Мбайт/с], Pm = 1[Мбайт/с], Pr = 2[Мбайт/с],

Класс 4: Pw = 4[Мбайт/с], Pm = 2[Мбайт/с], Pr = 4[Мбайт/с],

Класс 6: Pw = 6[Мбайт/с], Pm = 3[Мбайт/с], Pr = 6[Мбайт/с].

Среднее время TFW(ave.) записи файловой системы, максимальное время TFW(max) записи файловой системы и время чтения TFR(4 кбайт) файловой системы являются одинаковым параметром в каждом классе; например, 100 [мс], 750 [мс] и 4 [мс], соответственно.

Согласно параметрам, показанным на фиг.11, кривая быстродействия карты класса 2 пересекается с осью Y в точке 2 [Мбайт/с], а с осью X - в точке 1, и становится ближе к началу координат в середине. Область класса 2 занимает область, указывающую более высокое быстродействие, чем кривая быстродействия класса 2, и более низкое, чем кривая быстродействия класса 4 (описанная ниже), в первом квадранте.

Подобным образом кривая быстродействия класса 4 пересекается с осью Y в точке 4 [Мбайт/с], а с осью X - в точке 1, и отходит гораздо дальше от начала координат, чем кривая быстродействия карты класса 2. Областью карты класса 4 является область на стороне, противоположной началу кривой быстродействия карты класса 4.

Подобным образом определена кривая быстродействия класса 6, которая пересекается с осью Y в точке 6 [Мбайт/с].

Фиг.12 - таблица, показывающая условия измерения требуемых характеристик карты каждого класса, показанного на фиг.11. Как описано выше, время tWF последовательности операций клиентской части и размер SRU RU влияют на быстродействие Pw записи. Тактовая частота fSD SD влияет на время tWF последовательности операций клиентской части. Тактовая частота fSD SD и размер SRURU устанавливаются в значения, показанные на фиг.12, в качестве условия измерения требуемых характеристик каждого класса. Ведущему устройству 20 желательно осуществлять доступ к карте 19 памяти с использованием большего размера RU, для того, чтобы улучшить быстродействие.

[3-3] Взаимосвязь между емкостью и максимальным размером AU

Ведущее устройство 20 делает запрос другого параметра, относящегося к размеру блока. Регистр, отправляющий размер SAU AU, задан согласно физическим стандартам карты 19 памяти. Затем карта памяти может показать свой оптимальный размер SAU AU ведущему устройству 20. Как результат, ведущее устройство 20 эффективно использует AU 31. Размер, требуемый для ведущего буфера 27, задан согласно максимальному значению AU 31, как описано ниже.

Максимальный размер AU, соответствующий емкости карты 19 памяти, может быть таким, как изложено ниже.

Емкость карты/максимальный размер AU = от 16 до 128 Мбайт/128 кбайт, 256 Мбайт/256 кбайт, 512 Мбайт/512 кбайт, 1 Гбайт/1 Мбайт, 2 Гбайт/2 Мбайт, от 4 до 32 Гбайт/4 Мбайт.

[3-4] Требование быстродействия чтения

Быстродействие чтения по меньшей мере в 2 [Мбайт/с], 4 [Мбайт/с] и 6 [Мбайт/с] для карты класса 2, 4 и 6, соответственно, задано, когда чтение выполняется в элементах RU 32. Однако это не гарантирует быстродействие чтения ведущего устройства 20. Это происходит потому, что оборудование ведущего устройства 20 не принято во внимание в предшествующем пояснении.

[3-5] Требования определения физического стандарта карт

Когда быстродействие задано с использованием класса и различных параметров и стандартизовано, стандарту быстродействия необходимо учитывать стандарты как текущего, так и следующего поколения. Поэтому стандарт быстродействия должен учитывать карту памяти следующего поколения в дополнение к предшествующим стандартам. Так, в текущей карте памяти SDTM параметры, такие как быстродействие Pw записи, быстродействие Pm перемещения и время TFW записи файловой системы, должны быть заданы в соответствии с физическим стандартом 1.01, 1.10.

Дана карта 19 памяти определенного класса (например, высокого класса, определенного в будущем). Карта памяти класса не производится в соответствии с определенным физическим стандартом (например, физическим стандартом 1.01), так как существует ограничение условия (например, тактовой частоты SD), требуемого для определения класса. Эта разновидность карты 19 памяти должна производиться в соответствии с более высоким физическим стандартом. Например, карты класса 6 не могут производиться в соответствии физическому стандарту 1.01, так как они оснащены высокоскоростным режимом. Поэтому им необходимо соответствовать физическому стандарту 1.10.

[3-6] Хранение данных класса и параметров

Согласно новому стандарту, регистр может удерживать класс, размер SAU AU, быстродействие Pm перемещения и коэффициент CSD в качестве информации состояния карты памяти. Более точно, класс хранится в регистре 24 кода идентификации быстродействия. Размер SAU AU, быстродействие Pm перемещения и коэффициент CSD хранятся в регистре 25 параметра быстродействия.

Как описано выше, карта 19 памяти удерживает класс и параметры. В таком случае ведущее устройство 20, допускающее идентификацию класса, может более точно рассчитывать быстродействие наряду с эффективным использованием карты 19 памяти.

Фиг.13 - таблица, показывающая разрядность в битах информации регистра в карте памяти SD™. В карте памяти SD™ размер SAU AU, быстродействие Pm перемещения и коэффициент CSD описаны в регистре параметра быстродействия. Эти данные могут быть записаны в отдельно приготовленный регистр. Поля для этих данных могут удерживать 0 в карте памяти, которая не поддерживает стандарт быстродействия. Такая карта памяти распознается как карта класса 0.

Информация класса может устанавливаться в поле, которое удерживает постоянное значение (например, 0) в традиционном запоминающем устройстве. Таким образом, традиционные устройства, которые не поддерживают настоящий вариант осуществления, могут идентифицироваться как находящиеся вне объекта классификации быстродействия.

Отметим, что быстродействие Pw записи является уникальным в каждом классе (определено быстродействие записи, требуемое каждым классом). Таким образом, ведущее устройство 20 считывает класс, тем самым осведомляясь о быстродействии Pw записи.

Информация в регистре 24 кода идентификации быстродействия и регистре 25 параметра быстродействия может выводиться в ведущее устройство 20, когда карта 19 памяти принимает предопределенную команду из ведущего устройства 20.

Значение, установленное в регистре 24 кода идентификации быстродействия и регистре 25 параметра быстродействия, может быть записано в качестве предварительно рассчитанного значения при производстве, или может быть определено картой 19 памяти при инициализации.

Находящаяся в обращении карта памяти SD™ не имеет средств (выделенного регистра) для отображения параметра быстродействия. Код быстродействия и параметры быстродействия могут быть добавлены в зарезервированную область программируемого регистра. Ведущее устройство выявляет код быстродействия для осведомления о быстродействии карты. Следовательно, находящаяся в обращении карта памяти SD™ пригодна для использования без изменения текущего контроллера карты.

[4] Последовательность операций ведущего устройства при выполнении записи в реальном времени и требования

[4-1] Последовательность операций ведущего устройства при выполнении записи в реальном времени

При выполнении записи в реальном времени ведущее устройство 20 выполняет операцию записи наряду с выполнением расчетов, согласно следующей последовательности, с использованием кривой, класса и параметров быстродействия. Предпочтительно ведущее устройство 20 выполняет следующую последовательность при выполнении записи в реальном времени.

(1) Определить быстродействие (в материалах настоящей заявки, указанное ссылкой как быстродействие приложения) Pa, запрошенное у приложения, включенного в ведущее устройство 20.

(2) Выбрать надлежащее количество Nd RU записи между обновлениями файловой системы.

(3) Определить быстродействие Pc, требуемое для реализации быстродействия Pa приложения, учитывая обновление файловой системы.

(4) Определить максимальную долю r(Pc) занятых RU.

(5) Классифицировать AU 31 на AUfast и AUslow.

(6) Оценить имеющееся в распоряжении время Trec записи.

(7) Отрегулировать количество Nd RU, записываемых между обновлениями файловой системы. Когда количество Nd RU, записываемых между обновлениями файловой системы, больше, быстродействие улучшается.

(8) Когда достаточное быстродействие и достаточное имеющееся в распоряжении время записи не получаются после этих расчетов, требуется стирание карты.

Специальный способ выполнения операций с (1) по (8) и требования ведущего устройства 20 будут описаны ниже.

[4-2] Способ расчета быстродействия с обновлением файловой системы

Цикл обновления типичной файловой системы (FAT) при записи в реальном времени показан на фиг.7. Предпочтительно, чтобы ведущее устройство 20 выполняло такую последовательность при обновлении файловой системы.

[4-2-1] Условия быстродействия карты с учетом обновления файловой системы

Ведущее устройство 20 определяет быстродействие Pc карты, требуемое для удовлетворения Pa, по быстродействию Pa приложения и среднему времени TFW записи файловой системы. Как описано выше, вставляется последовательность записи файловой системы, и тем самым ухудшается быстродействие записи. Таким образом, ведущее устройство 20 требует карту, в общем, выдающую быстродействие Pc карты, более высокое, чем быстродействие Pa приложения.

Некоторые ведущие устройства 20 могут поддерживать некоторые разные виды режимов битовой скорости в соответствии с разновидностью приложения. В этом случае ведущее устройство 20 определяет быстродействие Pa приложения в соответствии с режимом, выбранным пользователями.

Желательно, чтобы ведущее устройство 20 было должно не отвергать карту 19 памяти, которая не совпадает с быстродействием Pa приложения, а подстраивать быстродействие ведущего устройства 20 в соответствии с классом карты 19 памяти.

Например, когда быстродействие карты у карты 19 памяти является худшим относительно быстродействия Pa приложения, желательно, чтобы ведущее устройство 20 изменяло режим на более низкий, требующий более низкого быстродействия Pa приложения. Например, может быть увеличен коэффициент сжатия данных, может быть уменьшено разрешение изображения или может быть снижена частота кадров, чтобы предоставить ведущему устройству 20 возможность соответствовать более низкому быстродействию Pa приложения. Для того чтобы реализовать способ, ведущее устройство 20 предпочтительно содержит некоторые разновидности режимов для использования карт 19 памяти, обладающих низким быстродействием.

Ведущее устройство 20 имеет несколько режимов, имеющих разное быстродействие записи, и тем самым оно может поддерживать запись на более низкой скорости, даже если происходит отказ. Отказ может происходить, когда используется карта класса 0, вследствие того, что ведущее устройство 20 не знает, может ли оно работать в определенном режиме до того, как оно фактически не попробует режим.

Быстродействие Pa приложения и быстродействие Pc карты, требуемые для удовлетворения Pa (в материалах настоящей заявки быстродействие карты), выражаются следующими математическими выражениями 6 и 7, соответственно.

[Математическое выражение 6]

Быстродействие, запрашиваемое приложением:

Pa = (Sc × Nd) / (Sc × Nd/Pc + TFW).

[Математическое выражение 7]

Быстродействие Pc, требуемое для удовлетворения:

Pc = (Sc × Nd × Pa) / (Sc × Nd - Pa × TFW).

Быстродействие Pc карты изменяется в зависимости от количества Nd RU записи между обновлениями файловой системы. Как видно из фиг.7, количество Nd RU записи между обновлениями файловой системы изменяется в зависимости от частоты обновления файловой системы. Таким образом, частота обновления файловой системы влияет на быстродействие Pc карты. Способ определения частоты обновления файловой системы будет описан в последующем [4-2-2].

[4-2-2] Условие периода обновления файловой системы

Время обновления файловой системы (FAT) (от обновления файловой системы до следующего обновления файловой системы) определено вставкой последовательности записи файловой системы в передачу данных. Поэтому период обновления файловой системы зависит от скорости записи; однако точность времени не важна. Простой способ может быть применен с тем, чтобы ведущее устройство 20 просто рассчитывало период обновления файловой системы.

Период обновления файловой системы выражается с использованием следующего математического выражения 8.

[Математическое выражение 8]

Период обновления файловой системы:

TPF = Sc × Nd / Pa

= Sc × Nd / Pc + TFW(ave.).

Ведущее устройство 20 может настраивать количество RU, записываемых между обновлениями файловой системы, учитывая снижение быстродействия карты, являющееся результатом записи файловой системы. В этом случае период TPF предпочтительно является одной секундой или большим.

Когда выбрано большее количество RU, быстродействие Pc карты приближается к быстродействию Pa приложения. При таком образе действий карта 19 памяти, обладающая низким быстродействием, способна к удовлетворению быстродействия Pa приложения.

Следующий способ предоставлен в качестве еще одного способа определения периода обновления файловой системы. Согласно способу, период TFU (эквивалентный TPF) определяется с использованием таймера, включенного в ведущее устройство 20. В этом случае TFU является постоянным. Обновление файловой системы вставляется между записями RU. Таким образом, количество RU, записываемых между обновлениями файловой системы, изменяется в зависимости от периода TFU обновления файловой системы.

В этом случае количество данных периода TFU обновления файловой системы выражается с использованием следующего математического выражения 9.

[Математическое выражение 9]

Количество данных по времени TFU: Pa × TFU.

Математическое выражение 9 преобразовано, и тем самым быстродействие Pc карты выражено с использованием следующего математического выражения 10.

[Математическое выражение 10]

Быстродействие карты для удовлетворения Pa:

Pc = (Pa × TFU) / (TFU - TFW(ave.)).

[4-3] Классификация элемента выделения (AU)

Ведущее устройство 20 определяет, какой AU 31 имеется в распоряжении для записи в реальном времени. Другими словами, ведущее устройство 20 определяет, удовлетворяет или нет каждый AU 31 запрошенному быстродействию Pc карты. Быстродействие каждого AU 31 изменяется в зависимости от доли занятых RU, как видно по фиг.6. Поэтому каждый AU 31 определяется с использованием доли занятых RU в качестве порогового значения.

[4-3-1] Максимальная доля занятых RU

Как показано на фиг.4, если позиция А начала записи и позиция В конца записи находятся на границе AU 31, быстродействие AU 31 рассчитывается с использованием математического выражения 3.

Таким образом, возможно вывести максимальную долю r(Pc) занятых RU из быстродействия Pc карты в качестве обратной функции математического выражения 3.

AU 31, имеющий долю r занятых RU, меньшую, чем максимальная доля r(Pc) занятых RU, является AU 31, удовлетворяющим быстродействию Pc карты. Чем меньше доля r занятых RU, которую имеет AU 31, тем больше подходит записи в реальном времени. AU 31 классифицируется на AUfast и AUslow с использованием максимальной доли r(Pc) занятых RU в качестве границы, как описано ниже.

Максимальная доля r(Pc) занятых RU выражается с использованием следующего математического выражения 11.

[Математическое выражение 11]

Максимальная доля занятых RU:

r(Pc) = [(Pw - Pc) × Pm] / [(Pw - Pm) × Pc + Pw × Pm].

[4-3-2] Классификация AU на две категории

Ведущее устройство 20 классифицирует AU 31 на две категории. Одним является AUfast (область элемента адаптивного управления). Этот AU 31 имеет скорость, достаточную для выполнения записи в реальном времени с быстродействием Pc карты. Другим является AUslow (область элемента неадаптивного управления). Этот AU 31 является непригодным для записи в реальном времени, так как область памяти слишком фрагментирована.

Ведущее устройство 20 подсчитывает количество Nu занятых RU для каждого AU 31, а после этого рассчитывает долю r занятых RU по количеству Nu занятых RU. Определяется, является ли AU AUfast или AUslow, с использованием следующего математического выражения 12.

[Математическое выражение 12]

Если Nu / Nt < r(Pc), AU является AUfast,

если Nu / Nt ≥ r(Pc), AU является AUslow.

Более точно, если (количество Nu занятых RU) / (общее количество Nt RU в AU) является меньшим, чем максимальная доля r(Pc) занятых RU, AU классифицируется как AUfast. С другой стороны, если Nu / Nt равно или больше, чем максимальная доля r(Pc) занятых RU, AU классифицируется как AUslow.

Фиг.14 показывает выделение AU 31 в пространстве 21 памяти и показывает распределение AU 31 в двух видах пространства 21 памяти. Самый верхний AU 31 включает в себя файловую систему; по этой причине он является областью, которая непригодна для записи в реальном времени. Следовательно, самый верхний AU 31 классифицируется как AUslow. Более того, элемент каталога не должен создаваться в AU 31, записывающем данные.

AU1 и AU4 не включают в себя файловую систему; однако определено, что они слишком фрагментированы, так как (количество Nu занятых RU) / (общее количество Nt RU в AU) является большим, чем максимальная доля r(Pc) занятых RU.

[4-4] Имеющееся в распоряжении время записи

Ведущее устройство 20 может рассчитывать доступное время для записи в реальном времени с использованием следующего математического выражения 13. В этом выражении Nr представляет количество Nr, имеющихся в распоряжении RU 32 из всех AU 31, определенных в качестве AUfast. Если достаточное имеющееся в распоряжении время записи не приготовлено, ведущее устройство 20 выдает пользователям инструкции, чтобы перенести данные записи в другое место, или переформатирует карту 19 памяти.

[Математическое выражение 13]

Имеющееся в распоряжении время записи:

TREC= Sc × Nr / Pa.

Ведущее устройство 20 вновь рассчитывает имеющееся в распоряжении время записи, когда оно устанавливает количество Nd RU записи между обновлениями файловой системы, то есть период TPF обновления файловой системы, большим. Это происходит потому, что большее количество Nd RU между обновлениями файловой системы улучшает быстродействие. Другими словами, максимальное значение доли r(Pc) занятых RU возрастает, а количество AUfast увеличивается; поэтому увеличивается имеющееся в распоряжении время записи.

[4-5] Требования для ведущего буфера

Ведущий буфер 27 должен обладать емкостью, достаточной для временного хранения данных. Ведущий буфер 27 должен удовлетворять следующим требованиям.

[4-5-1] Требования к размеру ведущего буфера

Ведущему буферу 27 необходимо иметь емкость, удовлетворяющую следующим запросам.

(1) Требование со стороны обновления файловой системы (FAT)

Когда ведущее устройство 20 обновляет файловую систему, ведущий буфер используется для временного хранения данных, которые предполагаются записываемыми во время записи файловой системы. По этой причине требуется большой размер буфера. Размер буфера задан как максимальное значение TFW(max) времени записи файловой системы. Например, максимальное значение TFW(max) времени записи файловой системы составляет 750 [мс], как видно из математического выражения 5. Вообще размер буфера представлен как данные времени записи, которые может хранить буфер.

(2) Требование со стороны исправления ошибок

Ведущий буфер 27 используется для дополнения задержки при исправлении ошибки данных записи. Если возникает ошибка записи, карта 19 памяти не возвращает статус CRC и не останавливает многоблочную запись или не отображает появление события ошибки. Ведущему буферу 27 необходимо сохранять данные до тех пор, пока запись не завершится, чтобы предоставить повторной записи возможность выполняться, если возникает ошибка.

Ведущий буфер 27 должен иметь надлежащий размер, например 250 [мс], с тем, чтобы ведущее устройство 20 продолжало запись в реальном времени, даже если возникает ошибка. Это происходит потому, что значение 250 [мс] задано в качестве максимального времени для завершения записи. Поэтому размер требуется в сочетании с максимальным значением TFW(max) времени записи файловой системы. Если максимальное значение TFW(max) времени записи файловой системы составляет 750 [мс], требуется буфер, допускающий хранение данных, в сумме эквивалентных 1 [с].

(3) Требование со стороны компенсации задержки записи AU

Если записанные RU 32 существуют в AU 31, включающем в себя случай, когда занятые RU 32 собираются в верхней части AU 31, данные не могут записываться, пока данные, сохраненные в занятом RU 32, не перемещены в другой RU 32. Следовательно, данные записи должны сохраняться в ведущем буфере, в то время как перемещаются записанные RU 32.

Фиг.15 показывает принцип ведущего буфера 27. Как показано на фиг.15, предполагается, что данные непрерывно входят в ведущий буфер 27 из ведущего устройства 20 с постоянной скоростью Pa, и ведущее устройство 20 считывает данные, сохраненные в ведущем буфере 27, чтобы записывать данные в AU 31.

С другой стороны, скорость передачи данных, выводимых из ведущего буфера 27, зависит от фрагментированной структуры AU 31. Более точно, если в AU 31 существует записанный RU 32, как описано выше, данные записи удерживаются ведущим буфером; следовательно, они не выводятся. Если никаких записанных RU 32 не существует в AU 31, или когда завершено перемещение RU 32, ведущий буфер 27 выводит данные со скоростью Pw.

Как видно из описания, размер, требуемый для ведущего буфера 27, определяется по тому, насколько длительное действие занимает перемещение всех занятых RU 32 в AU 31.

Если размер ведущего буфера 27 становится недостаточным, может происходить переполнение (недостаток буфера) ведущего буфера 27 в зависимости от фрагментированной структуры данных в AUfast. По этой причине может дополнительно потребоваться рассмотрение в соответствии с размером ведущего буфера 27 и фрагментированной структурой данных AUfast.

(4) Подготовка для данных записи

Подготовка данных записи отнимает определенное время у ведущего устройства 20, и, соответственно, данные записи формируются дискретно. В этом случае данные могут однократно сохраняться в буфере 27 и могут записываться ведущим контроллером 26. При таком образе действий передача может выполняться непрерывно; следовательно, может быть достигнута эффективная передача.

В частности, при записи в реальном времени данные реального времени однократно сохраняются в ведущем буфере 27, работающем как FIFO (первым вошел, первым обслужен), а после этого записываются в карту 19 памяти. При таком образе действий возможно сдерживать время, расходуемое на подготовку (расчет) данных реального времени. Другими словами, данные эффективно записываются в карту 19 памяти.

Если данные записываются прямо в карту 19 памяти после того, как рассчитывались в системной памяти, процедура является последовательной. По этой причине расчет и запись данных должны выполняться поочередно. Если выполняется поочередная работа, никакие данные не могут записываться в карту 19 памяти во время расчета, и в силу этого карта 19 памяти демонстрирует быстродействие, худшее, чем класс, который она представляет.

Требуемый размер буфера представлен в виде функции с использованием быстродействия Pa приложения, быстродействия Pw перемещения, максимальной доли r(Pc) занятых RU и размера SAU AU.

В следующем математическом выражении 14 показан требуемый размер SBUF буфера. В выражении 14 первый элемент (Pa) по правую сторону соответствует описанию столбцов (1) и (2). Второй элемент по правую сторону соответствует описанию столбца (3). Описание столбца (4) не включено в математическое выражение 14. Более того, дополнительный буфер может потребоваться в зависимости от стандартов ведущего устройства 20.

[Математическое выражение 14]

Требуемый размер буфера:

SBUF > Pa + [r(Pc) × SAU × Pa] / Pm.

Если быстродействие Pa приложения является меньшим, чем быстродействие Pm перемещения, а ведущий буфер 27 имеет большой размер, превышающий (Pa + SAU), математическое выражение 14 всегда удовлетворено.

[4-5-2] Обработка, когда размер ведущего буфера мал

Независимо от вышеприведенного обсуждения, последующее является пояснением о способе нахождения AUfast, имеющего небольшую степень фрагментации, если размер ведущего буфера 27 недостаточен. Предпочтительно, чтобы ведущий буфер 27 лучше имел достаточный размер, нежели выполнение способа, здесь описанного.

Фиг.16 показывает случай, где все занятые RU 32 собираются в верхней части AU 31. Максимальная доля r(Pc) занятых RU представляет границу, которая разделяется занятым RU 32c и свободным RU 32d. Когда ведущее устройство 20 записывает данные в первый свободный RU 32d, выводы карты 19 памяти долго заняты, до тех пор, пока полностью не перемещены все занятые RU 32c. В течение этой длительности данные записи сохраняются в ведущем буфере 27. В этом случае время, требуемое для перемещения всех занятых RU 32c в AU 31, выражается как изложено ниже.

(r(Pc) × SAU) / Pm

Поэтому размер ведущего буфера 27, требуемый в этом случае, выражается следующим математическим выражением 15.

[Математическое выражение 15]

Размер ведущего буфера: SBUF > Pa × [(r(Pc) × SAU) / Pm].

Следующее математическое выражение 16 получено из математического выражения 15.

[Математическое выражение 16]

Доля занятых RU, ограниченная размером ведущего буфера,

= r(Pc) < [(Pm × SBUF) / (Pa × SAU)].

Как видно из математического выражения 16, если размер ведущего буфера 27 мал, максимальная доля r(Pc) занятых RU ограничена размером ведущего буфера 27. В этом случае AU 31 должен классифицироваться с использованием максимальной доли r(Pc) занятых RU, ограниченной размером ведущего буфера 27, в качестве r(Pc) в математическом выражении 12.

Более того, если размер ведущего буфера 27 мал, наблюдается размер данных, сохраняемых в ведущем буфере 27, во время записи данных в реальном времени. В соответствии с наблюдаемым результатом, управление может выполняться так, чтобы битовая скорость передачи данных временно делалась меньшей, или может управляться период обновления файловой системы, чтобы предотвратить переполнение буфера. Есть проблема, что ведущий буфер 27 переполняется; как результат, теряются данные. По этой причине потеря данных должна быть предотвращена, даже если ухудшается качество данных.

Если запись производится с использованием быстродействия записи, спрогнозированной на основании информации быстродействия (параметра быстродействия) запоминающего устройства 19, ведущее устройство 20 производит изменение режима. Более точно, когда происходит переполнение буфера или часто возникает ошибка во время доступа к запоминающему устройству 19, ведущее устройство производит замену на режим более низкой скорости, чем скорость, основанная на информации быстродействия запоминающего устройства 19.

[4-6] Прочее

Ведущее устройство 20 может содержать средство для сравнения информации быстродействия (например, класса, параметра быстродействия) со своей информацией быстродействия (такой же, как вышеприведенная).

Ведущее устройство 20 может быть снабжено средством сравнения для сравнения информации быстродействия, считанной из карты 19 памяти, с его собственной информацией быстродействия. Это основано на следующих соображениях. Например, даже если одно из карты 19 памяти и ведущего устройства обладает очень высоким быстродействием, другое может не иметь быстродействия, эквивалентного вышеприведенному. В таком случае более низкое быстродействие, в итоге, ограничивает передачу данных между ведущим устройством 20 и картой 19 памяти.

Быстродействие, которого ожидают пользователи, может быть не получено, когда используется карта 19 памяти более низкого класса. Для того чтобы избежать недостатка, ведущее устройство 20 может сравнивать информацию быстродействия, считанную из карты 19 памяти, со своей информацией быстродействия и информировать пользователей о результате посредством дисплея.

Например, карта 19 памяти вставляется в ведущее устройство 20, а после этого ведущее устройство 20 отображает на экране следующее сообщение. То есть «Это устройство принадлежит классу M; однако выполняется работа на основании класса N (N < M), так как классом вставленной карты памяти является N». При таком образе действий пользователи могут понимать, почему ожидаемая скорость работы не получена, даже если используется карта памяти класса N. Отображение экрана может производиться автоматически после того, как карта 19 памяти вставлена в ведущее устройство 20, или пользователи могут производить предопределенную операцию, чтобы заставить сообщение появиться на экране.

Функция сравнения информации быстродействия, описанная выше, не является необходимой для ведущего устройства 20, чтобы использовать карту 19 памяти, хранящую информацию производительности.

(Второй вариант осуществления)

Карта памяти SDTM, к которой применим первый вариант осуществления, будет разъяснена ниже.

Фиг.17 - схематичное представление, показывающее конфигурацию карты памяти SD™ согласно второму варианту осуществления настоящего изобретения. Карта памяти SD™ (в дальнейшем указываемая ссылкой просто как карта памяти) 41 обменивается информацией с ведущим устройством 20 через шинный интерфейс 45. Карта 41 памяти включает в себя микросхему памяти NAND flash™ (в дальнейшем указываемой ссылкой просто, как флэш-память), контроллер 43 карты, управляющий микросхемой 42 флэш-памяти, и несколько сигнальных контактов (контактов с первого по девятый) 44. Номер 45 ссылки обозначает шинный интерфейс.

Контроллер 43 карты эквивалентен контроллеру 22 устройства по первому варианту осуществления (смотрите фиг.2). Флэш-память 42 эквивалентна пространству 21 памяти по фиг.2.

Сигнальные контакты 44 подключены с помощью электрического соединения к контроллеру 43 карты. Распределение сигналов по сигнальным контактам 44, то есть с первого по девятый контактам, является таким, как показано на фиг.18.

Данные с 0 по данные 3 назначены на седьмой, восьмой, девятый и первый контакты, соответственно. Первый контакт также выделен для сигнала детектирования карты. Второй контакт выделен для команды. Третий и шестой контакты выделены для нулевого потенциала Vss, а четвертый контакт выделен для потенциала Vdd источника питания. Пятый контакт выделен для сигнала тактирования.

Карта 41 памяти может быть вставлена в слот, сформированный в ведущем устройстве 20. Ведущий контроллер 26 (не показан) ведущего устройства обменивается различными сигналами и данными с контроллером 43 карты у карты 41 памяти через, с первого по девятый, контакты. Например, когда данные записываются в карту 41 памяти, ведущий контроллер 26 отправляет команду записи в контроллер 43 карты в виде последовательного сигнала через второй контакт. В этом случае контроллер 43 карты осуществляет выборку команды записи, подаваемую на второй контакт, в ответ на сигнал тактирования, подаваемый на пятый контакт.

Как описано выше, команда записи последовательно вводится в контроллер 43 карты с использованием только второго контакта. Второй контакт, выделенный для ввода команды, помещен между первым контактом для данных 3 и третьим контактом для нулевого потенциала Vss. Шинный интерфейс 45, соответствующий нескольким сигнальным контактам 44, используется для связи ведущего контроллера 26 ведущего устройства 20 с картой 41 памяти.

С другой стороны, связь флэш-памяти 42 с контроллером 43 карты выполняется через интерфейс памяти NAND flash™. Поэтому, хотя здесь и не показано, флэш-память 42 и контроллер 43 памяти соединены через 8-битную линию ввода/вывода (I/O).

Например, при записи данных во флэш-память 42 контроллер 43 карты последовательно вводит следующую информацию во флэш-память 42 через линию I/O. Информация включает в себя команду 80H ввода данных, адрес столбца, адрес страницы, данные и команду 10H программирования. «H» команды 80H обозначает шестнадцатеричное число, и, фактически, 8-битный сигнал «10000000» подается параллельно на 8-битную линию I/O. А именно многобитная команда подается параллельно через интерфейс памяти NAND flash™.

В интерфейсе памяти NAND flash™ команда и данные для флэш-памяти 42 обмениваются по одной и той же линии I/O. Таким образом, интерфейс, используемый для связи ведущего контроллера 26 ведущего устройства 20 с картой 41 памяти, отличается от такового, используемого для связи флэш-памяти с контроллером 43 карты.

Фиг.19 - структурная схема, показывающая конфигурацию аппаратных средств карты памяти согласно второму варианту осуществления.

Ведущее устройство 20 включает в себя аппаратные средства и программное обеспечение для осуществления доступа к карте 41 памяти через шинный интерфейс 45. Карта 41 памяти работает, будучи подключенной к ведущему устройству и принимающей электропитание, и в таком случае выполняет процедуры в соответствии с доступом из ведущего устройства 20.

Карта 41 памяти включает в себя флэш-память 42 и контроллер 43 памяти, как описано выше. Во флэш-памяти 42 размер блока стирания (то есть размер блока в элементе стирания) при операции стирания установлен в предопределенный размер (например, 256 кбайт). Более того, запись и чтение данных выполняются в элементе, названном страницей (например, 2 кбайта).

Контроллер 43 карты управляет физической структурой флэш-памяти 42 (например, адрес какого логического сектора включен в адрес какого физического блока, или какой блок стирается). Контроллер 43 карты имеет ведущий интерфейсный модуль 53, микропроцессор (MPU) 54, контроллер 55 флэш-памяти, постоянное запоминающее устройство (ПЗУ, ROM) 56, оперативное запоминающее устройство (ОЗУ, RAM) 57 и буфер 58.

Ведущий интерфейсный модуль 53 осуществляет интерфейс между контроллером 43 карты и ведущим устройством 20 и включает в себя регистр 59. Фиг.20 - структурная схема, показывающая конфигурацию регистра 59. Регистр 59 содержит регистр состояния карты и регистры, такие как CID, RCA, DSR, CSD, SCR и OCR.

Регистры определены, как изложено ниже. Регистр состояния карты используется при нормальной работе и, например, хранит информацию об ошибках, описанную позже. Регистры CID, RCA, DSR, CSD, SCR и OCR используются, главным образом, когда инициализируется карта памяти.

Номер идентификации карты (CID) хранит идентификационный номер карты 41 памяти. Относительный адрес карты (RCA) хранит относительный адрес карты (динамически определенный ведущим устройством при инициализации). Регистр задающего каскада (DSR) аккумулирует энергию возбуждения шины карты памяти.

Специфичные карте данные (CSD) хранят значения характеристических параметров карты 41 памяти. CSD, кроме того, удерживает информацию о версии, код идентификации быстродействия и параметр быстродействия, описанные в первом варианте осуществления.

Регистр данных конфигурации SD (SCR) хранит массив данных карты 41 памяти. Регистр условий работы (OCR) хранит рабочее напряжение карты 41 памяти, имеющей ограниченное напряжение рабочего диапазона.

MPU 54 управляет работой карты 41 памяти, взятой в целом. Когда карта 41 памяти принимает электропитание, MPU 54 считывает микропрограммное обеспечение (управляющую программу), сохраненное в ПЗУ 56, в ОЗУ 57 для выполнения предопределенных последовательностей операций. При таком образе действий MPU 54 подготавливает таблицы в ОЗУ 57.

MPU 54 также принимает команды записи, чтения и стирания для выполнения предопределенных последовательностей операций по отношению к флэш-памяти 42, или управляет передачей данных через буфер 58.

ПЗУ 56 хранит управляющие программы, управляемые MPU 54. ОЗУ 57 используется как рабочее пространство MPU 54 и хранит управляющие программы и различные таблицы. Контроллер 55 флэш-памяти осуществляет интерфейс между контроллером 43 карты и флэш-памятью 42.

Буфер 58 временно сохраняет предопределенный объем данных (например, одну страницу) при записи данных, отправленных из ведущего устройства 20 во флэш-память 42, и временно сохраняет предопределенный объем данных при отправке данных, считываемых из флэш-памяти 42 в ведущее устройство 20.

Фиг.21 показывает массив данных флэш-памяти 42 в карте 41 памяти. Каждая страница флэш-памяти 42 содержит 2112 байт (512-байтная область памяти данных × 4 + 10-байтная область резерва × 4 + 24-байтная область памяти управляющих данных). 128 страниц являются одним элементом стирания (256 кбайт + 8 кбайт (к означает 1024). В последующем описании элемент стирания флэш-памяти 42 установлен в 256 кбайт для удобства разъяснения.

Флэш-память 42 включает в себя буфер 42А страницы для ввода и вывода данных во флэш-память 42. Емкость памяти буфера 42А страницы составляет 2112 байта (2048 байт + 64 байта). При записи данных буфер 42А страницы выполняет ввод/вывод данных во флэш-память 42 при элементе в одну страницу, эквивалентную его собственной емкости памяти.

Если флэш-память имеет емкость памяти 1Гбайт, количеством блоков в 256 кбайт (элементом стирания) является 512.

Фиг.21 показывает случай, где элементом стирания является 256 кбайт; однако является особенно эффективным строить элемент стирания в 16 кбайт. В этом случае каждая страница содержит 528 байт (512-байтная область памяти данных + 16-байтная область резерва), и 32 страницы являются одним элементом стирания (16 кбайт + 0,5 кбайт).

Область (область памяти данных), в которую записываются данные флэш-памяти 42, поделена на несколько областей в соответствии с сохраненными данными, как показано на фиг.19. Флэш-память 42 содержит следующие области памяти данных, то есть область 61 управляющих данных, область 62 конфиденциальных данных, область 63 данных защиты и область 64 пользовательских данных.

Область 61 управляющих данных хранит управляющую информацию, относящуюся к карте памяти, то есть информацию защиты карты 41 памяти и информацию о карте, такую как ID носителя.

Область 62 конфиденциальных данных хранит ключевую информацию, используемую для шифрования, и конфиденциальные данные, используемые для аутентификации, и является областью, которая недоступна из ведущего устройства 20.

Область 63 данных защиты хранит значащие данные и является областью, которая доступна, только когда ведущее устройство 20 проверено на достоверность, несмотря на взаимную аутентификацию с ведущим устройством 20, присоединенным к карте 41 памяти.

Область 64 пользовательских данных хранит пользовательские данные и является областью, которая свободно доступна и имеется в распоряжении пользователей карты 41 памяти.

Пояснение по второму варианту осуществления направлено на случай, где режимом работы карты 41 памяти является 4-битный режим SD. Настоящее изобретение применимо к случаю, где режимом работы карты 41 памяти является 1-битный режим работы SD и режим SPI. Фиг.22 показывает распределение сигналов, соответствующее сигнальным контактам в 4-битном режиме SD, 1-битном режиме SD и режиме SPI.

Режим работы карты 41 памяти, в общем случае, классифицируется на режим SD и режим SPI. В режиме SD карта 41 памяти установлена в 4-битный режим SD или 1-битный режим SD согласно команде изменения разрядности шины из ведущего устройства 20.

Четыре контакта, с контакта данных 0 (DAT0) по контакт данных 3 (DAT3), все используются для передачи данных в 4-битном режиме SD, который передает данные по элементам 4-битной разрядности.

В 1-битном режиме SD, который передает передачу данных по элементам 1-битной разрядности, контакт данных 0 (DAT0) используется только для передачи данных, а контакт данных 1 (DAT1) и данных 2 (DAT2) не используется совсем. Контакт данных 3 (DAT3) используется, например, для асинхронного прерывания ведущего устройства 20 из карты 19 памяти.

В режиме SPI контакт данных 0 (DAT0) используется в качестве сигнальной линии данных (Данных на вывод) из карты 19 памяти в ведущее устройство 20. Контакт команды (CMD) используется в качестве сигнальной линии данных (Данных на ввод) из ведущего устройства 20 в карту 19 памяти. Контакт данных 1 (DAT1) и контакт данных 2 (DAT2) не используются. В режиме SPI контакт данных 3 (DAT3) используется для передачи сигнала выбора микросхемы (CS) из ведущего устройства 20 в карту 19 памяти.

Когда флэш-память 42 содержит одну микросхему, карта 19 памяти используется для не настолько высокоскоростной работы и классифицируется в качестве класса М (М является нулем или положительным целым числом).

Когда флэш-память 42 имеет класс N (N является положительным целым числом, большим, чем М), более высокоскоростной, чем карта 19 памяти с одной микросхемой, некоторые микросхемы флэш-памяти 42 могут представлять собой некоторые микросхемы в карте 19 памяти. При таком образе действий контроллер карты записывает данные в одну микросхему флэш-памяти, в то время как передает данные в другую микросхему флэш-памяти. Таким образом, внешняя скорость передачи данных между контроллером 43 карты и флэш-памятью 42 улучшается.

Более того, может применяться микросхема флэш-памяти, имеющая в распоряжении функцию копирования страницы (или резервного копирования), и тем самым данные, хранимые в странице микросхемы флэш-памяти, копируются в другую страницу той же самой микросхемы флэш-памяти. При таком образе действий улучшается быстродействие Pm перемещения.

Настоящее изобретение описано на основе первого и второго вариантов осуществления; однако настоящее изобретение не ограничено по объему. Цифровая фотокамера, цифровая видеокамера, ПК и PDA даны в качестве ведущих устройств, к которым применимо настоящее изобретение.