Системы и способы предоставления результата текущей команды процессора при выходе из виртуальной машины - RU2686552C2

Код документа: RU2686552C2

Чертежи

Описание

Родственные заявки

[0001] По настоящей заявке испрашивается приоритет по дате подачи предварительной заявки на патент США №62/038,476, поданной 18 августа 2014 года с названием "Системы и способы предоставления текущей команды процессора при выходе из виртуальной машины", полное содержание которой включено в данный документ посредством ссылки.

УРОВЕНЬ ТЕХНИКИ

[0002] Изобретение относится к компьютерной безопасности и, в частности, к выполнению операций компьютерной безопасности в конфигурациях аппаратной виртуализации.

[0003] Вредоносное программное обеспечение, также известное как вредоносные программы, воздействует на большое количество компьютерных систем по всему миру. В множестве своих форм, таких как компьютерные вирусы, вирусы-черви, руткиты и шпионские программы, вредоносные программы представляет серьезную опасность для миллионов компьютерных пользователей, подвергая их, среди прочего, опасности потери данных и конфиденциальной информации, хищения идентификационных данных и потери производительности.

[0004] Современные вычислительные приложения часто используют технологию аппаратной виртуализации для создания имитированных компьютерных сред, известных как виртуальные машины (VM), которые ведут себя во многих случаях как физические компьютерные системы. В приложениях, таких как консолидация серверов и инфраструктура как услуга, несколько виртуальных машин могут выполняться одновременно на одной и той же компьютерной системе, распределяя между собой аппаратные ресурсы, уменьшая, таким образом, инвестиционные и эксплуатационные расходы. Каждая виртуальная машина может выполнять свою собственную операционную систему и/или программное обеспечение отдельно от других виртуальных машин. Вследствие устойчивого распространения угроз компьютерной безопасности, таких как вредоносные программы и шпионские программы, каждая такая виртуальная машина потенциально нуждается в защите.

[0005] Некоторые решения по обеспечению безопасности защищают виртуальную машину путем мониторинга способа, посредством которого гостевые процессы, выполняющиеся внутри защищенной VM, осуществляют доступ к памяти, для идентификации потенциальной вредоносной активности. В одном примере программа компьютерной безопасности может конфигурировать процессор для генерации внутреннего события (например, события исключения или выхода из VM) при попытке сделать запись, или выполнить код из специальной области памяти, например области памяти, используемой гостевым процессом. Такие события процессора обычно приостанавливают выполнение текущего потока и переключают процессор на выполнение программы обработчика событий, которая может образовывать часть программы компьютерной безопасности. Программа компьютерной безопасности может, таким образом, обнаружить попытку доступа к памяти способом, который может указывать на вредоносные программы. После анализа события, программа компьютерной безопасности может эмулировать команду процессора, которая выполнялась, когда произошло это событие, и может вернуть выполнение к начальному ходу. Такие способы известны специалистам под общим названием "лови-и-эмулируй" (trap-and-emulate).

[0006] Традиционные способы "лови-и-эмулируй" могут оказывать значительную вычислительную нагрузку на хостовую компьютерную систему, что может сказываться на опыте пользователя и производительности. Таким образом, существует значительный интерес к разработке эффективных систем и способов обеспечения компьютерной безопасности, которые пригодны для сред виртуализации.

РАСКРЫТИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

[0007] Согласно одному аспекту хостовая система содержит по меньшей мере один аппаратный процессор, конфигурированный для выполнения виртуальной машины и программы компьютерной безопасности. По меньшей мере один аппаратный процессор дополнительно конфигурирован так, чтобы, в ответ на получение гостевой команды на выполнение, определять, вызывает ли выполнение гостевой команды внутри виртуальной машины нарушение разрешения на доступ к памяти. По меньшей мере один аппаратный процессор дополнительно конфигурирован так, чтобы, в ответ на определение, приводит ли выполнение гостевой команды к нарушению, когда выполнение гостевой команды приводит к нарушению, определять результат применения оператора гостевой команды к операнду гостевой команды, записывать результат в предопределенную область, доступную для программы компьютерной безопасности, и приостанавливать выполнение гостевой команды. По меньшей мере один аппаратный процессор дополнительно конфигурирован так, чтобы, в ответ на приостановку выполнения гостевой команды, переключаться на выполнение программы компьютерной безопасности, при этом программа компьютерной безопасности конфигурирована для определения, указывает ли нарушение на угрозу компьютерной безопасности.

[0008] Согласно другому аспекту способ защиты хостовой системы от угроз компьютерной безопасности содержит, в ответ на получение гостевой команды на выполнение, использование по меньшей мере одного процессора хостовой системы для определения, приводит ли выполнение гостевой команды к нарушению разрешения на доступ к памяти, при этом гостевая команда выполняется внутри гостевой виртуальной машины, предоставленной хостовой системой. Способ дополнительно содержит, в ответ на определение, приводит ли гостевая команда к нарушению, когда выполнение гостевой команды приводит к нарушению, использование по меньшей мере одного аппаратного процессора для определения результата применения оператора гостевой команды к операнду гостевой команды; использование по меньшей мере одного аппаратного процессора для записи результата в предопределенную область, доступную для программы компьютерной безопасности; и приостановку выполнения гостевой команды. Способ дополнительно содержит, в ответ на приостановку выполнения гостевой команды, переключение на выполнение программы компьютерной безопасности, причем программа компьютерной безопасности конфигурирована для определения, указывает ли нарушение на угрозу компьютерной безопасности.

[0009] Согласно другому аспекту по меньшей мере один аппаратный процессор хостовой системы выполнен конфигурируемым так, чтобы, в ответ на получение гостевой команды на выполнение, определять, приводит ли выполнение гостевой команды к нарушению разрешения на доступ к памяти, причем гостевая команда выполняется внутри гостевой виртуальной машины, предоставленной хостовой системой. По меньшей мере один аппаратный процессор дополнительно выполнен конфигурируемым так, чтобы, в ответ на определение, приводит ли гостевая команда к нарушению, когда выполнение гостевой команды приводит к нарушению, определять результат применения оператора гостевой команды к операнду гостевой команды; записывать результат в предопределенную область, доступную для программы компьютерной безопасности; приостанавливать выполнение гостевой команды. По меньшей мере один аппаратный процессор дополнительно выполнен конфигурируемым так, чтобы, в ответ на приостановку выполнения гостевой команды, переключаться на выполнение программы компьютерной безопасности, причем программа компьютерной безопасности конфигурирована для определения, указывает ли нарушение на угрозу компьютерной безопасности.

[0010] Согласно другому аспекту долговременный машиночитаемый носитель хранит команды, которые, при их выполнении по меньшей мере одним аппаратным процессором хостовой системы, побуждают хостовую систему формировать программу компьютерной безопасности, конфигурированную для определения, указывает ли нарушение разрешения на доступ к памяти на угрозу компьютерной безопасности. По меньшей мере один аппаратный процессор выполнен конфигурируемым так, чтобы, в ответ на получение гостевой команды на выполнение, определять, приводит ли выполнение гостевой команды к нарушению, при этом гостевая команда выполняется внутри гостевой виртуальной машины, предоставленной хостовой системой. По меньшей мере один аппаратный процессор дополнительно выполнен конфигурируемым так, чтобы, в ответ на определение, приводит ли гостевая команда к нарушению, когда выполнение гостевой команды приводит к нарушению, определять результат применения оператора гостевой команды к операнду гостевой команды; записывать результат в предопределенную область, доступную для программы компьютерной безопасности; приостанавливать выполнение гостевой команды. По меньшей мере один аппаратный процессор дополнительно выполнен конфигурируемым так, чтобы, в ответ на приостановку выполнения гостевой команды, переключаться на выполнение программы компьютерной безопасности.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

[0011] Упомянутые выше аспекты и преимущества настоящего изобретения станут более понятными по прочтении следующего ниже подробного описания со ссылками на чертежи, на которых показано следующее.

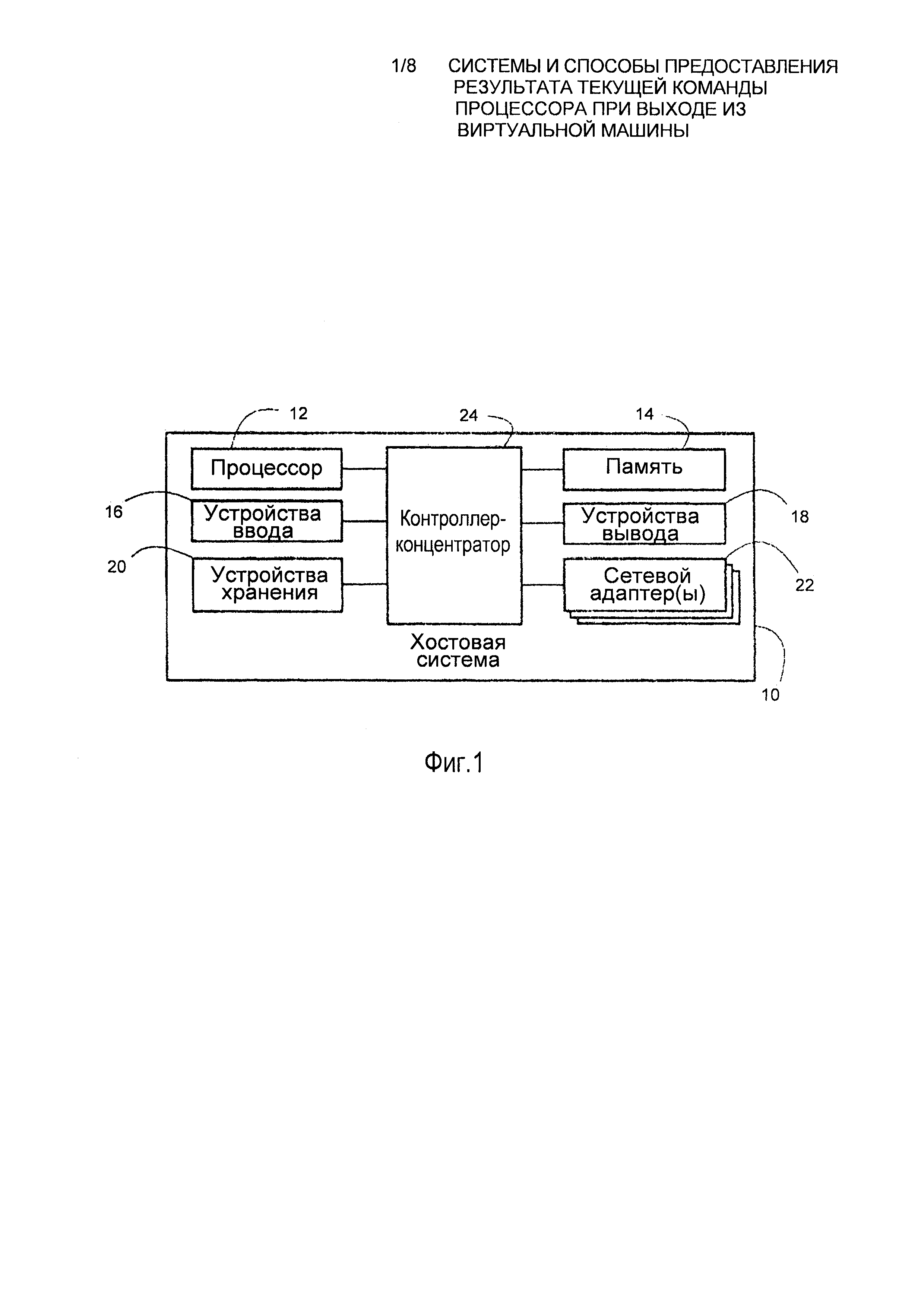

[0012] На фиг.1 показана примерная аппаратная конфигурация хостовой компьютерной системы согласно некоторым вариантам осуществления настоящего изобретения.

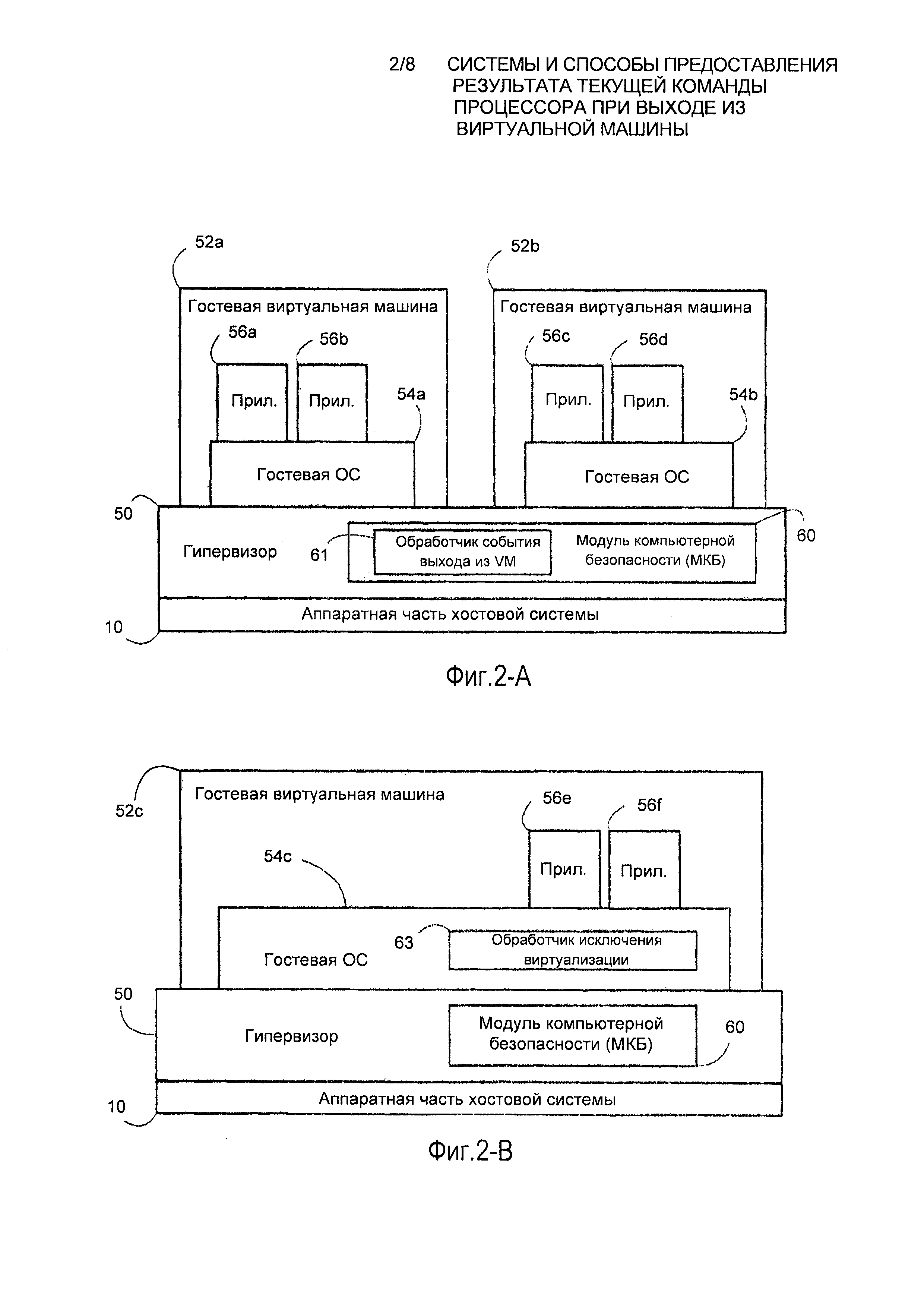

[0013] На фиг. 2-А показан примерный набор виртуальных машин, предоставленных гипервизором, выполняющимся на хостовой системе, и модуль компьютерной безопасности (МКБ), защищающий этот набор виртуальных машин, согласно некоторым вариантам осуществления настоящего изобретения.

[0014] На фиг. 2-В показан альтернативный вариант осуществления настоящего изобретения, в котором МКБ выполняется под виртуальной машиной, причем обработчик исключений выполняется внутри защищенной виртуальной машины.

[0015] На фиг. 2-С показан еще один вариант осуществления настоящего изобретения, в котором как МКБ, так и обработчик исключений выполняются внутри защищенной виртуальной машины.

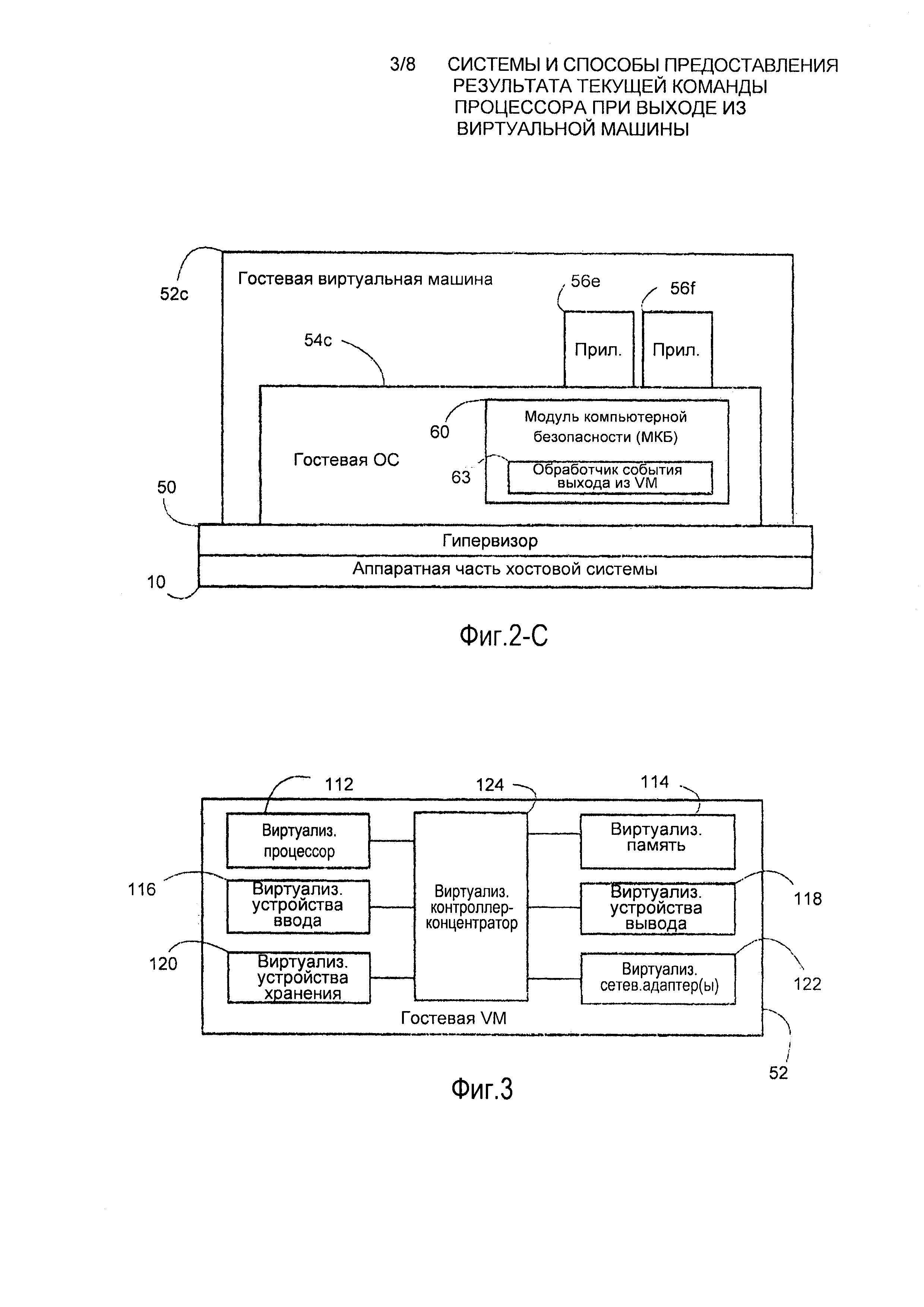

[0016] На фиг. 3 показана примерная конфигурация виртуализированных аппаратных средств, предоставленных в виде гостевой виртуальной машины согласно некоторым вариантам осуществления настоящего изобретения.

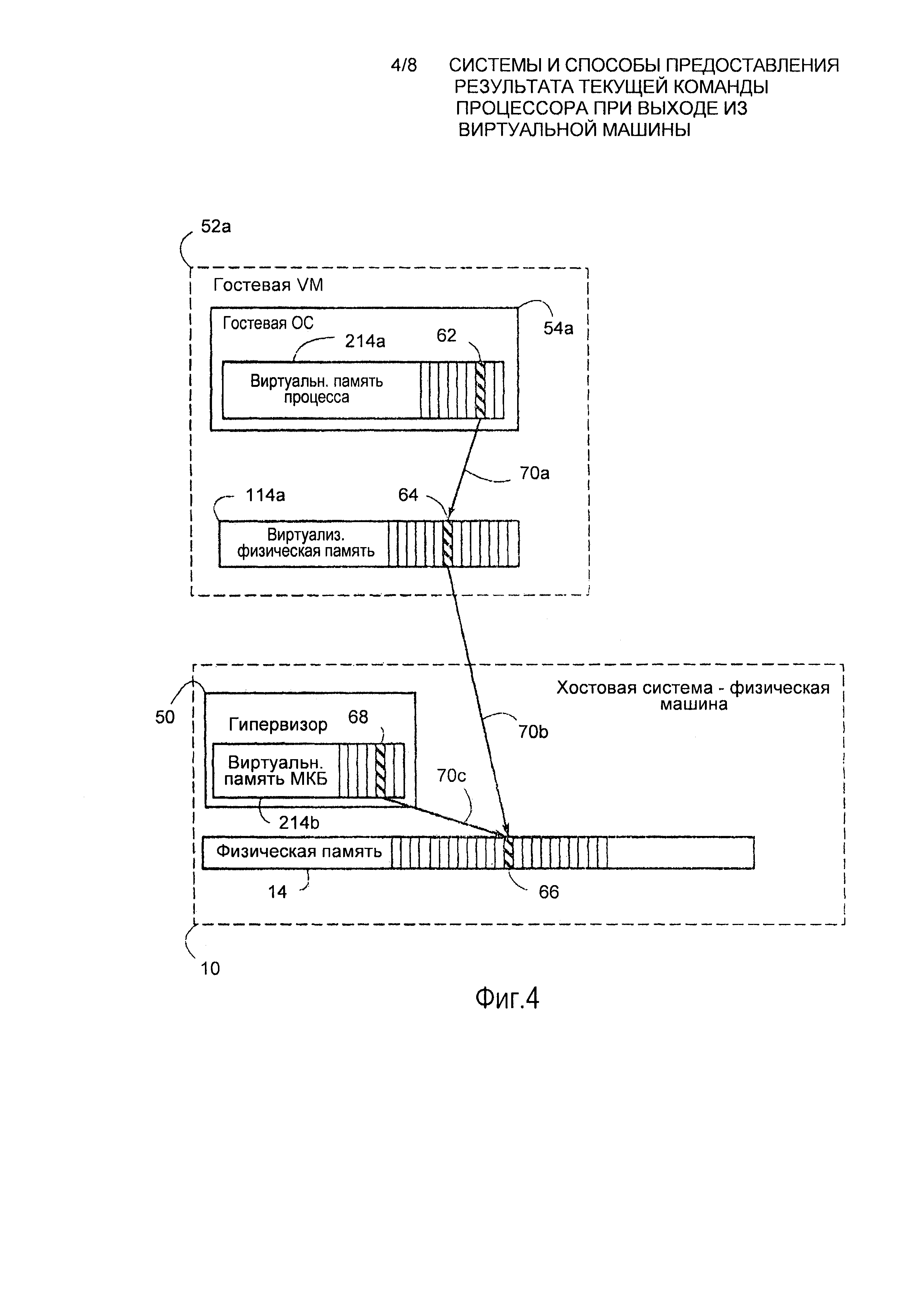

[0017] На фиг. 4 показан набор примерных трансляций адресов памяти в конфигурации аппаратной виртуализации, как показано на фиг. 2, согласно некоторым вариантам осуществления настоящего изобретения.

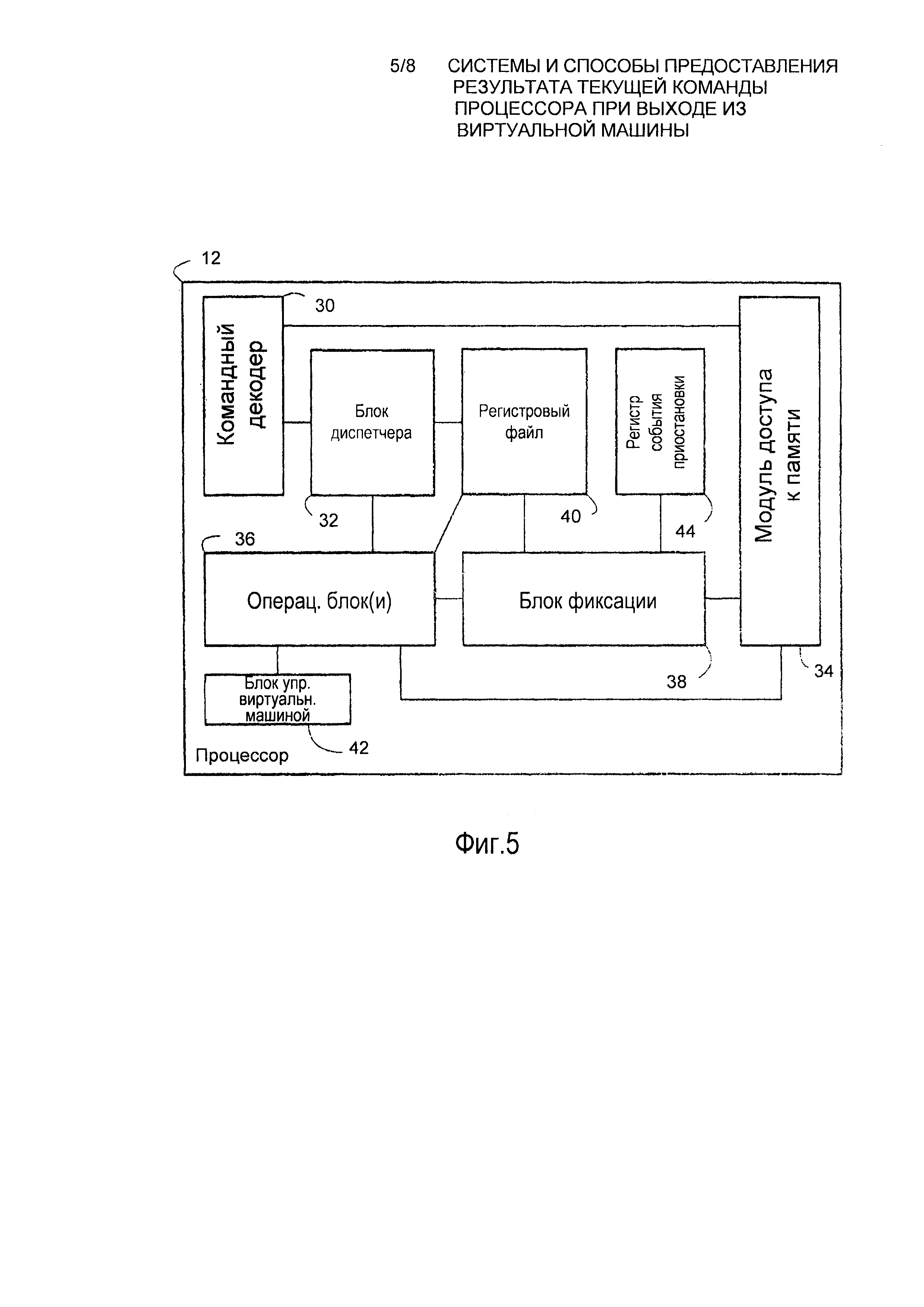

[0018] На фиг. 5 показаны примерные компоненты процессора согласно некоторым вариантам осуществления настоящего изобретения.

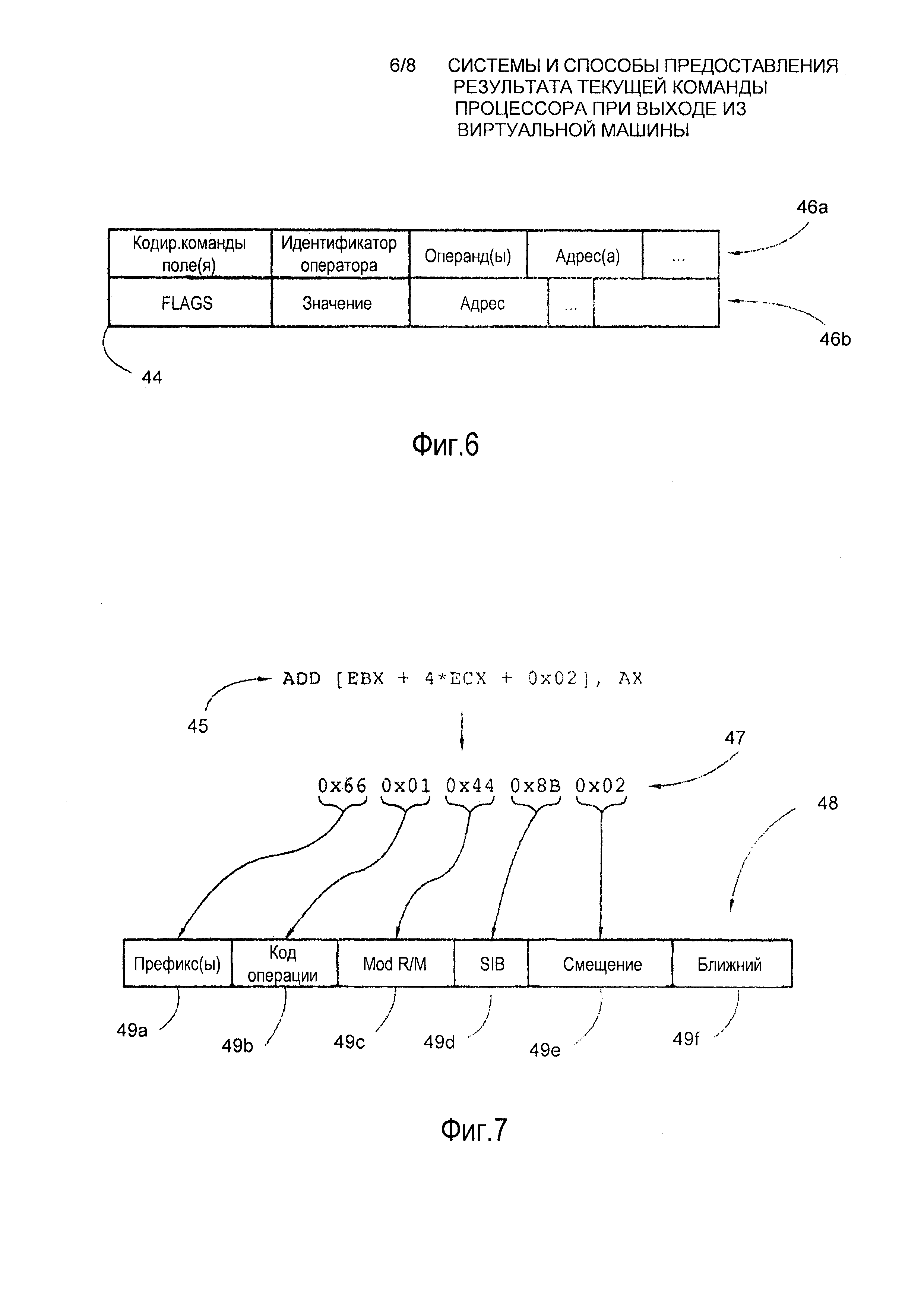

[0019] На фиг. 6 показан примерный регистр события приостановки процессора согласно некоторым вариантам осуществления настоящего изобретения.

[0020] На фиг. 7 показано представление на языке ассемблера примерной команды процессора набора команд х86 и соответствующее представление его машинного кода.

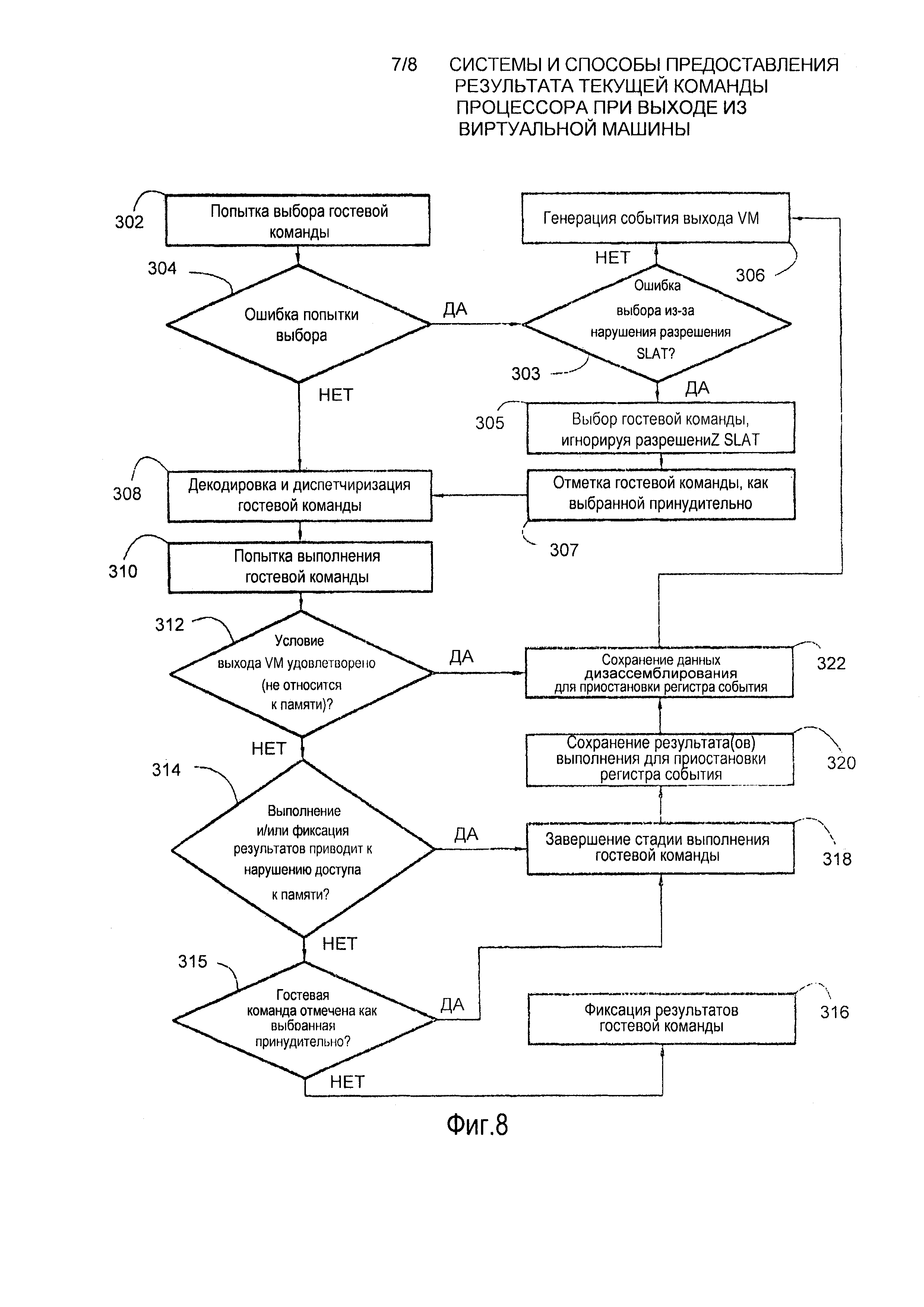

[0021] На фиг. 8 показана примерная последовательность этапов, выполняемых процессором для выполнения команды процессора согласно некоторым вариантам осуществления настоящего изобретения.

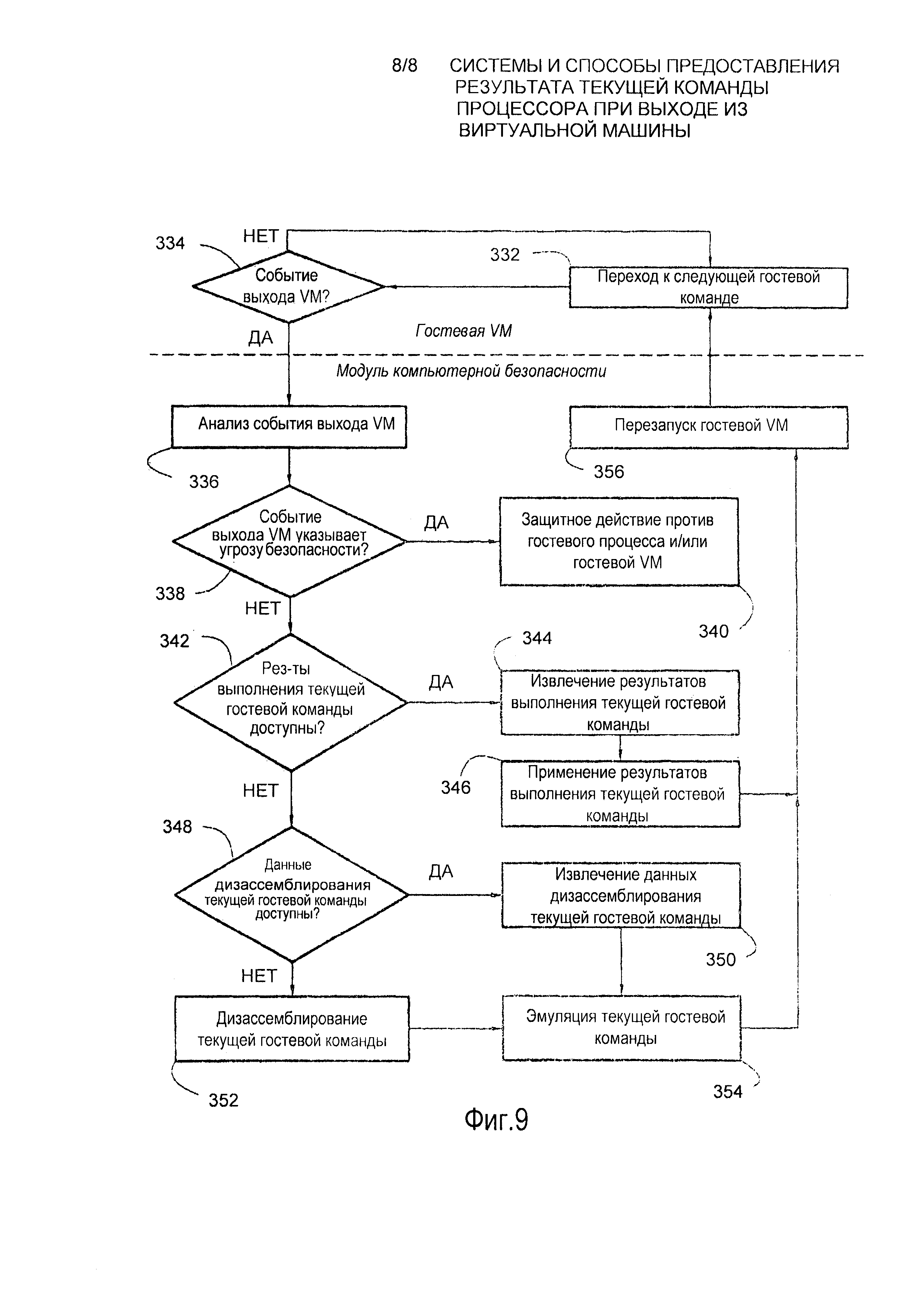

[0022] На фиг. 9 показана примерная последовательность этапов, выполняемых модулем компьютерной безопасности, для защиты гостевой виртуальной машины согласно некоторым вариантам осуществления настоящего изобретения.

ОСУЩЕСТВЛЕНИЕ ИЗОБРЕТЕНИЯ

[0023] В нижеследующем описании подразумевается, что все упоминаемые соединения между структурами могут быть непосредственными функциональными соединениями или опосредованными функциональными соединениями через промежуточные структуры. Набор элементов включает в себя один или более элементов. Любое упоминание элемента понимается как относящееся к по меньшей мере одному элементу. Множество элементов содержит, по меньшей мере, два элемента. Если не требуется иное, любые описанные этапы способа не должны обязательно выполняться в конкретном показанном порядке. Первый элемент (например, данные), полученный из второго элемента, охватывает первый элемент, эквивалентный второму элементу, а также первый элемент, генерированный посредством обработки второго элемента и, опционально, другие данные. Выполнение определения или решения в соответствии с параметром охватывает выполнение определения или решения в соответствии с этим параметром и, опционально, согласно другим данным. Если не указано иное, указатель (индикатор) некоторой величины/данных может представлять собой сами величину/данные, или указатель, отличный от самих величины/данных. Компьютерная программа представляет собой последовательность команд процессора, выполняющих задачу. Компьютерная программа, описанная в некоторых вариантах осуществления настоящего изобретения, может представлять собой автономные программные объекты или подобъекты (например, подпрограммы, библиотеки) других компьютерных программ. Если не указано иное, программа компьютерной безопасности представляет собой компьютерную программу, которая защищает оборудование и данные от ненамеренного или несанкционированного доступа, модификации или разрушения. Если не указано иное, процесс представляет собой экземпляр компьютерной программы, такой как приложение или часть операционной системы, и характеризуется наличием, по меньшей мере, ходом исполнения и пространством виртуальной памяти, назначенным ему, при этом содержание соответствующего пространства виртуальной памяти включает в себя выполняемый код. Если не указано иное, страница представляет собой наименьшую единицу виртуальной памяти, которая может быть отдельно отображена в физическую память хостовой системы. Термин "логическая часть" охватывает схемы аппаратных средств, имеющие фиксированные или реконфигурируемые функциональные возможности (например, схемы программируемых пользователем вентильных матриц), но не охватывает программное обеспечение, эмулирующее такие функциональные возможности на компьютере общего назначения. Если не указано иное, регистр представляет собой компонент хранения, интегрированный с процессором или образующий его часть и отличный от оперативного запоминающего устройства (RAM). Машиночитаемые носители включают в себя такие долговременные носители как магнитные, оптические и полупроводниковые запоминающие носители (например, жесткие диски, оптические диски, флэш-память, DRAM), а также линии связи, такие как токопроводящие кабели и волоконно-оптические линии. Согласно некоторым вариантам осуществления, настоящее изобретение относится, в частности, к компьютерным системам, содержащим аппаратные средства (например, один или более процессоров), программированные для выполнения способов, описанных в настоящем документе, и машиночитаемым носителям, кодирующим команды для выполнения способов, описанных в настоящем документе.

[0024] Следующее ниже описание иллюстрирует варианты осуществления изобретения на примерах, которые не следует считать ограничивающими притязания изобретения.

[0025] На фиг. 1 показана примерная аппаратная конфигурация хостовой системы 10 согласно некоторым вариантам осуществления настоящего изобретения. Хостовая система 10 может представлять собой вычислительное устройство профессионального применения, такое как корпоративный сервер, или устройство конечного пользователя, такое как персональный компьютер, планшетный компьютер или смартфон. Другие примеры хостовых систем включают в себя телевизоры, игровые консоли, носимые вычислительные устройства, или любое другое электронное устройство, имеющее память и процессор. Хостовая система 10 применима для выполнения набора программных приложений, таких как, среди прочего, браузер, приложение текстового редактора и приложение электронной связи (например, электронная почта, службы мгновенного обмена сообщениями). В некоторых вариантах осуществления хостовая система 10 конфигурирована для поддержки аппаратной виртуализации и для предоставления набора виртуальных машин, как показано ниже.

[0026] На фиг. 1 показана компьютерная система; аппаратная конфигурация других хостовых систем, таких как смартфоны и планшетные компьютеры, может быть отличной. Система 10 содержит набор физических устройств, включающий в себя процессор 12, блок 14 памяти, набор устройств 16 ввода, набор устройств 18 вывода, набор устройств 20 хранения и набор сетевых адаптеров 22, все соединены контроллером-концентратором 24. В некоторых вариантах осуществления процессор 12 содержит физическое устройство (например, многоядерную интегральную схему, выполненную на полупроводниковой подложке), конфигурированную для выполнения вычислительных и/или логических операций с набором сигналов и/или данных. В некоторых вариантах осуществления такие логические операции подаются в процессор 12 в виде последовательности команд процессора (например, машинный код или программное обеспечение другого типа). Некоторые варианты осуществления настоящего изобретения вносят изменения в структуру и функциональные возможности обычного процессора, при этом соответствующие изменения позволяют процессору 12 работать более эффективно в конфигурациях аппаратной виртуализации.

[0027] Блок 14 памяти может включать в себя энергонезависимый машиночитаемый носитель (например, оперативное запоминающее устройство (RAM)), хранящий данные/сигналы, к которым обращается процессор 12 или которые генерируются им в процессе выполнения команд. Устройства 16 ввода могут включать в себя компьютерные клавиатуры, мыши и микрофоны, помимо прочего, в том числе соответствующие аппаратные интерфейсы и/или адаптеры, которые позволяют пользователю вводить данные и/или команды в хостовую систему 10. Устройства 18 вывода могут включать в себя, помимо прочего, устройства отображения, такие как мониторы, громкоговорители, а также аппаратные интерфейсы/адаптеры, такие как графические карты, которые позволяют хостовой системе 10 передавать данные пользователю. В некоторых вариантах осуществления устройства 16 ввода и устройства 18 вывода могут совместно использовать общую часть аппаратных средств, как в случае устройств с сенсорным экраном. Устройства 20 хранения включают в себя машиночитаемые носители, обеспечивающие энергонезависимое хранение, чтение и запись команд процессора и/или данных. Примеры устройств 20 хранения включают в себя магнитные и оптические диски и устройства флэш-памяти, а также съемные носители, такие как CD и/или DVD-диски и дисковые накопители. Набор сетевых адаптеров 22 позволяет подключать хостовую систему 10 к компьютерной сети и/или к другим устройствам/компьютерным системам. Контроллер-концентратор 24 обычно представляет собой множество шин системы, периферийных шин и/или шин микросхем и/или все другие схемы, обеспечивающие связь между процессором 12 и устройствами 14, 16, 18, 20, 22. Например, контроллер-концентратор 24 может включать в себя, среди прочего, блок управления памятью (MMU), контроллер ввода/вывода (I/O) и контроллер прерываний. В другом примере контроллер-концентратор 24 может включать в себя северный мост, соединяющий процессор 12 с памятью 14, и/или южный мост, соединяющий процессор 12 с устройствами 16, 18, 20, 22. В некоторых вариантах осуществления части контроллера-концентратора (такие как MMU) могут быть интегрированы с процессором 12, т.е. могут иметь общую подложку с процессором 12.

[0028] На фиг. 2 показана примерная функциональная конфигурация согласно некоторым вариантам осуществления настоящего изобретения, в которой хостовая система 10 использует технологию аппаратной визуализации для управления набором гостевых виртуальных машин 52а-b, предоставленных гипервизором 50. Такие конфигурации являются обычными, среди прочего, в таких приложениях, как облачные вычисления и консолидация серверов. Виртуальная машина (VM) известна в данной области техники как абстракция, например, программная эмуляция, фактической физической машины/компьютерной системы, при этом VM выполнена с возможностью выполнения операционной системы и другого программного обеспечения. В некоторых вариантах осуществления гипервизор 50 включает в себя программное обеспечение, конфигурированное для создания или обеспечения множества виртуализированных устройств, таких как виртуальный процессор и виртуальный контроллер-концентратор, и для представления таких виртуализированных устройств программному обеспечению вместо реальных, физических устройств хостовой системы 10. Такие операции гипервизора 50 широко известны в данной области техники как предоставление виртуальной машины. В некоторых вариантах осуществления гипервизор 50 обеспечивает возможность мультиплексирования (распределения) множеством виртуальных машин аппаратных ресурсов хостовой системы 10. Гипервизор 50 может дополнительно управлять таким мультиплексированием, так чтобы каждая гостевая VM 52а-b работала независимо и «не знала» о других VM, выполняемых параллельно на хостовой системе 10. Примеры популярных гипервизоров включают в себя, среди прочего, VMware vSphere™ компании VMware Inc. и гипервизор Xen с открытым кодом.

[0029] Каждая VM 52а-b может соответственно выполнять гостевую операционную систему (ОС) 54а-b. Набор примерных приложений 56a-d в общем случае представляет собой, среди прочего, любое программное приложение, такое как обработка текстов, обработка изображений, медиаплеер, база данных, календарь, управление личными контактами, браузер, игры, речевая связь, передача данных и антивредоносные приложения. Операционные системы 54а-b могут включать в себя, среди прочего, любую широко распространенную операционную систему, такую как Microsoft Windows®, MacOS®, Linux®, iOS® или Android™. Каждая ОС 54a-b обеспечивает интерфейс между приложениями, выполняющимися в соответствующей VM, и виртуализированными аппаратными устройствами соответствующей VM. В нижеследующем описании под выражением программное обеспечение, выполняющееся внутри соответствующей виртуальной машины, понимается программное обеспечение, выполняющееся на виртуальном процессоре виртуальной машины. Например, в примере на фиг 2-А, о приложениях 56а-b говорится, что они выполняются внутри гостевой VM 52а, тогда как о приложениях 56c-d говорится, что они выполняются внутри гостевой VM 52b. Напротив, о гипервизоре 50 говорится, что он выполняется вне гостевых VM 52а-b, или под ними.

[0030] На фиг. 3 показана примерная конфигурация виртуальной машины 52, предоставленной гипервизором 50. VM 52 может представлять собой любую VM 52а-b на фиг. 2-А. VM 52 содержит виртуализированный процессор 112, виртуализированный блок 114 памяти, виртуализированные устройства 116 ввода, виртуализированные устройства 118 вывода, виртуализированное запоминающее устройство 120, виртуализированные сетевые адаптеры 122 и виртуализированный контроллер-концентратор 124. Виртуализированный процессор 112 содержит эмуляцию по меньшей мере некоторых из функциональных возможностей процессора 12 и конфигурирован для получения команд процессора на выполнение, которые образуют часть программного обеспечения, такого как операционная система и другие приложения. Считается, что программное обеспечение, использующее для выполнения процессор 112, выполняется внутри виртуальной машины 52. В некоторых вариантах осуществления виртуализированное запоминающее устройство 114 содержит адресуемые пространства для хранения и извлечения данных, используемых виртуализированным процессором 112. Другие виртуализированные устройства (например, виртуализированные ввод, вывод, хранение и т.д.) эмулируют, по меньшей мере, некоторые из функциональных возможностей соответствующих физических устройств хостовой системы 10. Виртуализированный процессор 112 может быть конфигурирован для взаимодействия с такими виртуализированными устройствами, как если бы он взаимодействовал бы с соответствующими физическими устройствами. Например, программное обеспечение, выполняющееся внутри VM 52, может отправлять и/или получать сетевой трафик через виртуализированный сетевой адаптер (адаптеры) 122. В некоторых вариантах осуществления гипервизор 50 может предоставлять только подмножество виртуализированных устройств для VM 52 (например, только виртуализированный процессор 112, виртуализированную память 114 и части концентратора 124). Гипервизор 50 также может предоставлять выбранной VM исключительное использование некоторых аппаратных устройств хостовой системы 10. В одном таком примере VM 52а (фиг. 2-А) может иметь исключительное использование устройств 16 ввода и устройств 18 вывода, но не иметь виртуализированного сетевого адаптера. При этом VM 52b могут иметь исключительное использование сетевого адаптера (адаптеров) 22. Такие конфигурации могут быть реализованы, например, с использованием технологии VT-d® от Intel®

[0031] Современные процессоры реализуют иерархию уровней привилегий процессора, также известные в данной области техники как кольца защиты. Каждое такое кольцо или уровень характеризуется набором действий и/или команд процессора, которые разрешено выполнять программному обеспечению, выполняющемуся в соответствующем кольце. Примерные уровни привилегий/кольца включают в себя режим пользователя (кольцо 3) и режим ядра (кольцо 0) Некоторые хостовые системы, конфигурированные для поддержки аппаратной виртуализации, могут включать в себя дополнительное кольцо с наивысшими привилегиями процессора (например, кольцо -1, режим суперпользователя или VMXroot на платформе Intel®). В некоторых вариантах осуществления гипервизор 50 принимает управление процессором 12 на наиболее привилегированном уровне (кольцо -1), создавая, таким образом, платформу аппаратной виртуализации, предоставленную в виде виртуальной машины для другого программного обеспечения, выполняющегося на хостовой системе 10. Операционная система, такая как гостевая ОС 54а на фиг. 2-А, выполняется внутри виртуальной среды соответствующей VM, как правило с меньшей привилегией процессора, чем гипервизор 50 (например, в кольце 0 или в режиме ядра). Обычные пользовательские приложения, такие как 56а-b, обычно выполняются с меньшей привилегией процессора, чем ОС 34а (например, в кольце 3 или в режиме пользователя) Некоторые части приложений 56а-b могут выполняться на уровне привилегий ядра, в то время как некоторые части ОС 34а могут выполняться в режиме пользователя (кольцо 3). Если программный объект пытается выполнить действие или команду, требующие привилегий процессора, превышающих допускаемые его назначенным кольцом защиты, эта попытка обычно генерирует событие процессора, такое как исключение или ошибка, которое передает управление процессором 12 объекту (например, программе обработчика), выполняющемся в кольце с достаточными привилегиями для выполнения соответствующего действия.

[0032] В частности, попытка выполнения определенных действий или выполнения некоторых команд изнутри гостевой VM может инициировать специальную категорию событий процессора, которые в данном документе обобщенно называются событиями приостановки VM. В некоторых вариантах осуществления событие приостановки VM приостанавливает выполнение текущего потока внутри гостевой VM и переключает процессор 12 на выполнение программы обработчика. Примерные события приостановки VM включают в себя, среди прочего, событие выхода из VM (например, VMExit на платформах Intel®) и исключение виртуализации (например, #VE на платформах Intel®). События выхода из VM переключают процессор 12 на выполнение программы обработчика вне соответствующей гостевой VM, обычно на уровне гипервизора 50. Исключение виртуализации может переключить процессор 12 на выполнение программы обработчика внутри соответствующей гостевой VM вместо выхода из соответствующей VM.

[0033] Примерные команды, инициирующие событие приостановки VM, включают в себя VMCALL на платформах Intel®. События приостановки VM также могут быть инициированы другими событиями, такими как нарушения доступа к памяти. В одном из таких примеров, когда программный объект, выполняющийся внутри VM, пытается выполнить запись в секцию памяти, отмеченную как незаписываемая, или выполнить код из секции памяти, отмеченной как невыполняемая, процессор 12 может генерировать событие выхода из VM. Такие механизмы переключения VM, например, позволяют программе компьютерной безопасности защитить виртуальную машину извне соответствующей VM. Программа компьютерной безопасности может перехватывать события выхода из VM, происходящие в ответ на определенные действия, выполняемые программным обеспечением, выполняющимся внутри VM, причем эти действия могут указывать на угрозу безопасности. Программа компьютерной безопасности может затем блокировать и/или дополнительно анализировать такие действия, потенциально без знания программного обеспечения в VM. Такие конфигурации могут существенно усилить компьютерную безопасность.

[0034] В некоторых вариантах осуществления (например, на фиг. 2-А) гипервизор 50 включает в себя модуль компьютерной безопасности (МКБ) 60, конфигурированный, среди прочего, для выполнения таких операций компьютерной безопасности. Модуль 60 может быть включен в гипервизор (например, в виде библиотеки) или может поставляться в виде компьютерной программы, отдельной и независимой от гипервизора 50, но выполняющейся на уровне привилегий гипервизора 50. Единичный модуль 60 может быть конфигурирован для защиты нескольких гостевых VM, выполняющихся на хостовой системе 10. Операции по обеспечению безопасности, выполняемые модулем 60, могут включать в себя обнаружение действия, выполняемого процессом, выполняющимся внутри гостевой VM (например, вызов определенных функций ОС, доступ к регистру ОС, загрузка файла из удаленного местоположения, запись данных в файл и т.д.). Другие операции безопасности модуля 60 могут включать в себя определение адреса секции памяти, которая содержит часть программного объекта, выполняющегося внутри гостевой VM, доступ к соответствующей секции памяти и анализ содержаний, хранящегося внутри соответствующей секции памяти. Другие примеры операций по обеспечению безопасности включают в себя перехват и/или ограничение доступа к таким секциям памяти, например, предотвращение перезаписи кода или данных, принадлежащих защищенному процессу, и предотвращение выполнения кода, хранящегося в определенных страницах памяти. В некоторых вариантах осуществления МКБ 60 включает в себя обработчик 61 события выхода из VM, конфигурированный для перехвата событий выхода из VM, происходящих внутри гостевых VM 52а-b. В альтернативном варианте осуществления обработчик 61 может быть отдельным модулем (например, библиотекой) гипервизора 50, отдельным от МКБ 60, который перехватывает события выхода из VM и избирательно передает управление на МКБ 60 после определения причины, и/или типа каждого произошедшего выхода из VM.

[0035] На фиг. 2-В показан альтернативный вариант осуществления, в котором модуль 60 компьютерной безопасности защищает гостевую VM 52 с извне соответствующей VM. В таких вариантах осуществления процессор 12 может быть конфигурирован для генерации исключения виртуализации (вместо события выхода из VM, как описано выше со ссылкой на фиг. 2-А), когда происходит нарушение доступа к памяти. В примерном варианте осуществления на фиг. 2-В, обработчик 63 исключения виртуализации выполняется внутри VM 52с, например, на уровне привилегий операционной системы 54с, и конфигурирован для перехвата исключений виртуализации и для взаимодействия с МКБ 60.

[0036] Связь между обработчиком 63 и МКБ 60 может происходить согласно любому способу связи между процессами, известному в данной области техники. Для передачи данных изнутри защищенной VM на уровень гипервизора 50, некоторые варианты осуществления обработчика 63 используют специализированную команду (например, VMCALL на платформах Intel®) для передачи управления процессором 12 от соответствующей VM к гипервизору 50. Передаваемые данные могут быть размещены обработчиком 63 исключений в предопределенную секцию памяти, используемую совместно с МКБ. Для передачи данных к обработчику 63 некоторые варианты осуществления МКБ 60 могут вносить прерывание внутрь VM 52с, при этом это прерывание обрабатываться обработчиком 63. Соответствующие данные могут быть переданы снова через совместно используемую секцию памяти, как описано выше.

[0037] В другом варианте осуществления, показанном на фиг. 2-С, как МКБ 60, так и обработчик 63 выполняются внутри защищенной VM, например, в режиме ядра (кольцо 0). Такие варианты осуществления могут также использовать исключения виртуализации для обнаружения нарушений доступа к памяти. Выбор между конфигурациями 2-А-В-С может включать в себя оценку компромисса между эффективностью и безопасностью. События выхода из VM являются относительно затратными с точки зрения вычислений, как правило требуя загрузки и/или выгрузки больших структур данных в/из памяти с каждым циклом выхода и повторного входа. Таким образом, конфигурации, такие как 2-А, могут потребовать больше вычислений для перехвата события, чем такие конфигурации, как 2-В-С. С другой стороны, поддержание критических компонентов безопасности, таких как МКБ 60 и обработчики 61-63, вне защищенной VM (как в примерах 2-А-В) может усилить безопасность, так как вредоносной программе, выполняющейся внутри соответствующей VM, может оказаться более затруднительно помешать работе таких компонентов.

[0038] Для обеспечения возможности защиты гостевой VM в конфигурации, изображенной на фиг. 2-А-В (т.е., извне соответствующей VM) некоторые варианты осуществления МКБ 60 используют структуры данных трансляции адресов и/или механизмы трансляции адресов процессора 12. Виртуальные машины, как правило, работают с виртуализированной физической памятью (см., например, память 114 на фиг. 3), также известной в данной области техники как гостевая физическая память. Виртуализированная физическая память содержит абстрактное представление фактической физической памяти 14, например, в виде непрерывного пространства адресов, обычно называемых гостевыми физическими адресами (GPA) Каждое такое пространство адресов уникальным образом прикреплено к гостевой VM, при этом части упомянутого пространства адресов отображены на секции физической памяти 14 и/или физических запоминающих устройств 20. В системах, конфигурированных для поддержки виртуализации, такое отображение обычно достигается с использованием аппаратно-ускоренных, выделенных структур данных и механизмов, управляемых процессором 12, известных как трансляция адресов второго уровня (SLAT). Популярные реализации SLAT включают в себя расширенные таблицы страниц (ЕРТ) на платформах Intel® и быстрая индексация виртуализации (RVI)/вложенные таблицы страниц (NPT) на платформах AMD®. В таких системах виртуализированная физическая память может быть разделена на блоки, известные в данной области техники как страницы, причем страница представляет собой наименьший блок виртуализированной физической памяти, отдельно отображенный на физическую память с помощью таких механизмов, как EPT/NPT, т.е. отображение между физической и виртуализированной физической памятью выполняется с гранулярностью страницы. Все страницы обычно имеют предопределенный размер, например, 4 килобайта, 2 мегабайта и т.д. Разбиение виртуализированной физической памяти на страницы обычно конфигурируется гипервизором 50. В некоторых вариантах осуществления гипервизор 50 также конфигурирует структуры SLAT и, таким образом, конфигурирует трансляцию адресов между физической памятью и виртуализированной физической памятью. Такие трансляции адресов известны в данной области техники как трансляции гостевых физических адресов на хостовые физические адреса (GPA-HPA).

[0039] В некоторых вариантах осуществления операционная система, выполняющаяся внутри VM, устанавливает пространство виртуальной памяти для каждого процесса, выполняющегося внутри соответствующей VM, причем упомянутое пространство виртуальной памяти представляет собой абстракцию физической памяти. Виртуальная память процесса, как правило, содержит непрерывное пространство адресов, обычно известное в данной области техники как гостевые виртуальные адреса (GVA) или гостевые линейные адреса (GLA). В некоторых вариантах осуществления, пространства виртуальной памяти процесса также разделены на страницы, причем такие страницы представляют собой наименьший блок виртуальной памяти, индивидуально отображенный посредством ОС в виртуализированную физическую память соответствующей VM, т.е. отображение виртуальной памяти в виртуализированную физическую память выполняется с гранулированностью страницы. ОС может конфигурировать выделенную структуру данных, такую как таблица страниц, используемую виртуализированным процессором соответствующей VM для выполнения трансляций гостевых виртуальных адресов в гостевые физические адреса (GVA-GPA).

[0040] На фиг. 4 показана примерная трансляция адресов памяти в варианте осуществления на фиг. 2-А. После предоставления гипервизором 50, гостевая VM 52а видит пространство 114а виртуализированной физической памяти как свое собственное пространство физической памяти. Процесс, выполняющийся внутри гостевой VM 52а, назначен пространству 214а виртуальной памяти посредством гостевой ОС 54а. Если процесс пытается осуществить доступ к памяти на гостевом виртуальном адресе 62, GVA 62 транслируется посредством (виртуализированного) MMU гостевой VM 52а в гостевой физический адрес 64 внутри пространства 114а виртуализированной физической памяти. Трансляция 70а GVA-GPA может происходить, например, в соответствии с таблицами страниц, конфигурированными и управляемыми гостевой ОС 34а. GPA 64 дополнительно отображается с помощью MMU на хостовый физический адрес (НРА) 66 внутри физической памяти 14 хостовой системы 10. Трансляция 70b GPA-HPA может происходить, например, в соответствии с структурами SLAT, конфигурированными гипервизором 50.

[0041] Каждому процессу, выполняемому под гостевыми VM 52а-b, обычно присваивается пространство виртуальной памяти, адресуемое посредством того, что известно в данной области техники как хостовые виртуальные адреса (HVA). В примере на фиг. 4 гипервизор 50 устанавливает пространство 214b виртуальной памяти для модуля 60 компьютерной безопасности. МКБ 60 затем может ссылаться на НРА 66 через HVA 68. Если модуль 60 интегрирован внутри гипервизора 50, например, в виде библиотеки, пространство 214b памяти может совпадать с пространством виртуальной памяти гипервизора 50. Для того, чтобы управлять такими пространствами, гипервизор 50 может конфигурировать выделенные структуры данных и механизмы (например, таблицы страниц), используемые MMU для выполнения трансляций HVA-HPA, таких как трансляция 70 с.

[0042] В некоторых вариантах осуществления гипервизор 50 и/или МКБ 60 может устанавливать разрешения на доступ для каждого подмножества страниц физической памяти. Такие страницы памяти могут быть использованы, например, определенными критическими гостевыми процессами, выполняющимися внутри защищенной VM, такими как процессы ОС и/или антивредоносных программ. Разрешения доступа указывают, например, на то, может ли соответствующая страница быть считана и может ли быть сделана запись в нее, и разрешено ли программному обеспечению выполнять код из соответствующей страницы. Разрешения на доступ могут быть указаны, например, в виде части записи SLAT, представляющей соответствующую страницу памяти. Некоторые хостовые системы могут позволять устанавливать разрешения доступа с гранулярностью субстраницы.

[0043] Гипервизор 50 и/или МКБ 60 могут дополнительно конфигурировать процессор 12 для генерации события приостановки VM, когда программное обеспечение, выполняющееся внутри гостевой VM, пытается осуществить доступ к памяти способом, нарушающим разрешения на доступ (например, для записи в страницу памяти, отмеченную как не записываемая). Такая попытка называется при этом нарушением доступа к памяти. Соответствующее событие приостановки VM может быть событием выхода из VM, в таких конфигурациях, как показанные на фиг. 2-А, и исключением визуализации в таких конфигурациях, как показанные на фиг. 2-В-С

[0044] Некоторые варианты осуществления настоящего изобретения вводят изменения в структуру и функциональные возможности обычного аппаратного процессора, чтобы позволить этому процессору работать более эффективно в конфигурациях аппаратной визуализации. На фиг. 5 показаны примерные аппаратные компоненты процессора 12 согласно некоторым вариантам осуществления настоящего изобретения. Под показанными компонентами имеются в виду общие устройства, выполняющие описанные функциональные возможности; конструктивные детали могут существенно изменяться в зависимости от реализаций. Например, каждый показанный компонент может содержать множество соединенных между собой подсистем, не обязательно физически вблизи друг к другу. Показанные компоненты не являются исчерпывающими; процессор 12 может включать в себя множество других компонентов (например, планировщик, контроллер прерываний, различные кэши и т.д.), которые для упрощения представления были опущены на фиг. 5.

[0045] Процессор 12 может включать в себя логическую часть/схемы, конфигурированные для выполнения различных этапов конвейера процессора. Например, командный декодер 30 выполняет операции декодирования команд, которые могут включать в себя трансляцию каждой команды процессора в набор элементарных операций процессора и/или микроопераций. Набор операционных блоков 36, соединенных с декодером 30, может осуществлять этап выполнения конвейера. Примерный операционный блок (блоки) 36 включают в себя, среди прочего, арифметико-логический блок (ALU) и блок вычислений с плавающей запятой (FPU)

[0046] В некоторых вариантах осуществления этап выполнения конвейера для команды содержит определение результата применения оператора соответствующей команды к операнду соответствующей команды. Такие результаты могут включать в себя, помимо прочего, адрес памяти, значение для фиксации в адрес памяти или в регистр процессора (например, в регистр общего назначения, такой как АХ, модельно-зависимый регистр - MSR, управляющий регистр, такой как EFLAGS, или скрытый регистр, такой как скрытая часть сегментного регистра х86, также известного как кэш дескрипторов), значение указателя команды (например, RIP), и значение указателя стека (например, RSP).

[0047] Операнд (операнды) команды может быть явным в операторе команды или может быть неявным. Примерная команда х86 с неявными операндами представляет собой команду STC, которая устанавливает флаг переноса управляющего регистра EFLAGS процессора равным 1. В некоторых вариантах осуществления регистр EFLAGS и значение 1 интерпретируются как (неявные) операнды, хотя они не появляются в явном виде в операторе команды STC.

[0048] Блок 38 фиксации может выполнять стадию фиксации конвейера, т.е., сохранять вывод операционного блока (блоков) 36 в памяти 14 и/или обновлять содержимое определенных регистров процессора для отражения изменений/результатов, полученных при этапе выполнения. Блок 38 фиксации может содержать логические модули, известные в данной области техники как блоки прекращения.

[0049] Модуль 34 доступа к памяти, соединенный с декодером 30 и операционным блоком (блоками) 36 включает в себя логическую часть, конфигурированную для взаимодействия с памятью 14, например, для выборки команд из памяти, для загрузки данных из памяти, и для сохранения результатов выполнения команд процессора в память. В некоторых вариантах осуществления модуль доступа к памяти содержит MMU, конфигурированный для выполнения трансляций виртуального адреса в физический, необходимых для доступа к памяти.

[0050] Современные процессоры обычно поддерживают нестандартное и/или спекулятивное выполнения команд процессора. В таких системах множество команд одновременно выбираются, декодируются и выполняются одним и тем же операционным блоком (блоками) 36. Результаты таких выполнений затем фиксируются надлежащим образом для сохранения требуемого потока соответствующей компьютерной программы. Такие конфигурации используются, например, в сочетании с алгоритмами прогнозирования переходов для улучшения производительности процессора 12. В некоторых вариантах осуществления, конфигурированных для нестандартного выполнения, процессор 12 может дополнительно содержать блок 32 диспетчера, соединенный с декодером 30 и с операционными модулями 36, и регистровый файл 40, соединен с операционным блоком (блоками) 36 и блоком 38 фиксации. Диспетчер 36 может планировать отдельные микрооперации для выполнения и поддерживать отображение, связывающее каждую микрооперацию со своей соответствующей командой, чтобы управлять порядком выполнения и фиксации. Регистровый файл 40 содержит массив внутренних регистров процессора, организованный, например, в виде буфера переупорядочивания. Регистровый файл 40 может дополнительно содержать логическую часть, позволяющую блоку 36 диспетчера связывать ряд регистров файла 40 с каждой запланированной микрооперацией, такая операция известна в данной области техники как переименование регистров. В таких конфигурациях каждый такой ряд регистров может содержать, например, значения регистров общего назначения и/или состояния процессора 12, причем упомянутые значения соответствуют промежуточному этапу выполнения определенной команды процессора.

[0051] Процессор 12 может дополнительно включать в себя блок 38 управления виртуальной машины, конфигурированный для управления данными состояния виртуальной машины. В некоторых вариантах осуществления объект состояния виртуальной машины (VMSO) содержит структуру данных, используемую внутри процессором 12 для представления текущего состояния каждого виртуализированного процессора, предоставленного на хостовой системе 10. Примерные VMSO включают в себя структуру управления виртуальной машины (VMCS) на платформах Intel® и блок управления виртуальной машины (VMCB) на платформах AMD®. VMSO обычно устанавливаются гипервизором 50 в виде части предоставления каждой виртуальной машины. В некоторых вариантах осуществления процессор 12 связывает область в памяти с каждым VMSO, так что программное обеспечение может ссылаться на конкретный VMSO с использованием адреса памяти или указателя (например, указатель VMCS на платформах Intel®).

[0052] Каждый VMSO может содержать гостевую область состояния и хостовую область состояния, причем гостевая область состояния хранит состояние CPU соответствующей гостевой VM и хостовая область состояния хранит текущее состояние гипервизора 50. В некоторых вариантах осуществления гостевая область состояния VMSO включает в себя, среди прочего, содержимое управляющих регистров (например, CR0, CR3 и т.д.), указатель команды (например, RIP), регистры общего назначения (например, ЕАХ, ЕСХ и т.д.), и регистры состояния (например, EFLAGS) виртуального процессора соответствующей гостевой VM. Хостовая область состояния VMSO может содержать указатель (например, указатель ЕРТ на платформах Intel®) на структуру данных SLAT, конфигурированную для трансляций адресов GPA-HPA для соответствующей гостевой VM.

[0053] В некоторых вариантах осуществления процессор 12 может сохранять часть VMSO внутри выделенных внутренних регистров/кэшей, в то время как другие части соответствующего VMSO могут находиться в памяти. В любой заданный момент времени по меньшей мере один VMSO (здесь именуемый текущим VMSO) может быть загружен в процессор, идентифицируя виртуальную машину, имеющую в текущий момент управление процессором 12. Современные процессоры обычно конфигурированы для многопотоковой обработки. В таких конфигурациях физический процессор 12 может работать с множеством ядер, при этом каждое ядро дополнительно содержит множество логических процессоров, причем каждый логический процессор может обрабатывать поток выполнения независимо и одновременно с другими логическими процессорами. Множество логических процессоров могут совместно использовать некоторые аппаратные ресурсы, например, общий MMU. В многопоточном варианте осуществления отдельный VMSO может быть загружен в каждый отдельный логический процессор.

[0054] Когда процессор 12 переключается от выполнения соответствующей VM на выполнение гипервизора 50 (например, при выходе из VM), процессор 12 может сохранять состояние соответствующей VM в гостевую область состояния текущего VMSO. Если процессор 12 переключается от выполнения первой VM на выполнение второй VM, VMSO, связанный с первой VM, выгружается, a VMSO, связанный со второй VM, загружается в процессор, при этом второй VMSO становится текущим VMSO. В некоторых вариантах осуществления такая загрузка/выгрузка данных VMSO в/из процессора 12 выполняется модулем 38 управления виртуальной машины. Модуль 38 может дополнительно выполнять извлечение и/или сохранение данных VMSO из/в памяти 14.

[0055] В некоторых вариантах осуществления процессор 12 дополнительно содержит регистр 44 события приостановки, соединенный с операционным блоком (блоками) 36 и/или с блоком 38 фиксации и конфигурированный для хранения зависящих от команд данных, связанных с гостевой командой, при этом выполнение упомянутых гостевых команд вызвало событие приостановки VM (например, выход из VM или исключение виртуализации). В некоторых вариантах осуществления регистр 44 события приостановки представляет собой предоставленный регистр, доступный для программного обеспечения, выполняющегося на хостовой системе 10, т.е. данные, хранящиеся в регистре 44, могут быть считаны программным обеспечением, таким как модуль 60 безопасности. В одном таком примере регистр 44 события приостановки включает в себя зависящий от модели регистр (MSR) процессора 12. В некоторых вариантах осуществления доступ к регистру 44 может быть ограничен подмножеством программных объектов, выбранных в соответствии с таким критерием, как привилегия процессора (например, только кольцо -1 или режим суперпользователя) или тип объекта (например, только драйверы). В некоторых вариантах осуществления программный доступ к регистру 44 может быть ограничен только подмножеством операций (например, только для чтения).

[0056] На фиг. 6 показан примерный набор полей регистра 44 события приостановки согласно некоторым вариантам осуществления настоящего изобретения. Регистр 44 может включать в себя поле 46а дизассемблирования и поле 46b результата выполнения. Поле 46а дизассемблирования может хранить данные, полученные в результате дизассемблирования соответствующей гостевой команды.

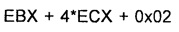

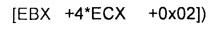

[0057] На фиг. 7 показано представление 45 на языке ассемблера примерной команды процессора Intel® х86. Показанная команда инструктирует процессор увеличить содержание, хранимое в памяти в (виртуальном) адресе

[0058] В некоторых вариантах осуществления дизассемблирование команды содержит синтаксический анализ представления машинного кода команды для идентификации и/или вычисления набора семантических элементов. Такие семантические элементы могут включать в себя, среди прочего, оператор (например, MOV, ADD и т.д.) и операнд (например, АХ,

[0059] В примере на фиг. 7 дизассемблирование команды может включать в себя определение содержания отдельных полей кодирования, как показано с помощью стрелок, указывающих на соответствие между представлением 47 машинного кода и обобщенной формой 48. В некоторых вариантах осуществления дизассемблирование показанной команды включает в себя идентификацию оператора ADD и/или определение в соответствии с машинным кодом 47 того, что соответствующая команда имеет два операнда, что один из операндов представляет собой содержание регистра АХ и что второй операнд представляет собой содержание памяти, и определение выражения (например,

[0060] В некоторых вариантах осуществления поле 46а дизассемблирования регистра 44 (фиг. 6) включает в себя содержимое полей кодирования команды соответствующей команды (см. фиг. 7). Другое примерное содержимое поля 46а включает в себя идентификатор оператора, указывающий на оператор соответствующей команды, и индикатор операнда соответствующей команды. Индикатор операнда может дополнительно включать в себя идентификатор регистра процессора (например, АХ), и флаг, указывающий, например, на то, является ли соответствующий операнд содержимым регистра или содержимым памяти. Поле 46а дизассемблирования может дополнительно содержать адрес памяти (например, GVA, GPA и/или НРА), указанный операндом. Структура поля 46а дизассемблирования может зависеть от платформы. Например, на платформах Intel®, поле 46а дизассемблирования может включать в себя содержание префикса, кода операции modR/M, SIB, смещение, и поля непосредственного кодирования текущей гостевой команды. На других платформах поле 46а может хранить другие значения в соответствии с архитектурой набора команд (ISA) соответствующей платформы.

[0061] В некоторых вариантах осуществления поле 46b результата выполнения регистра 44 события приостановки может хранить данные, указывающие на результат выполнения соответствующей команды процессора. Такие результаты могут включать в себя значение регистра состояния (например, FLAGS), значение указателя команды (например, RIP), и значение регистра общего назначения (например, ЕАХ), получаемых в результате выполнения соответствующей команды. Поле 46b может дополнительно содержать значение, подлежащее фиксации в память, в результате выполнения соответствующей команды, размер соответствующего значения (например, байт, слово и т.д.) и/или адрес памяти, куда будет внесено соответствующее значение.

[0062] В некоторых вариантах осуществления операционный блок (блоки) 36 и/или блок 38 фиксации могут быть конфигурированы для определения, вызывает ли выполнение гостевой команды событие процессора VM (такое как выход из VM исключения визуализации), и если да, для сохранения данных дизассемблирования команды для приостановки регистра 44 события перед генерацией соответствующего события. Процессор 12 может быть дополнительно конфигурирован для задержки генерации события процессора до завершения стадии выполнения соответствующей гостевой команды и для сохранения результата выполнения соответствующей команды в регистр 44 события вместо фиксации таких результатов в память и/или регистр общего назначения процессора 12. Для предотвращения фиксации результатов таких команд, процессор 12 может быть конфигурирован для генерации события процессора VM перед стадией фиксации конвейера для соответствующей команды. Такая функция описана ниже более подробно.

[0063] На фиг. 8 показана подробная, примерная последовательность этапов, выполняемых процессором 12 для выполнения гостевой команды согласно некоторым вариантам осуществления настоящего изобретения. На фиг. 8 показан вариант осуществления, в котором процессор 12 конфигурирован для генерации события выхода из VM в ответ на нарушение доступа к памяти. Специалисту в данной области понятно, что настоящее изобретение может быть легко модифицировано для включения варианта осуществления, который генерирует другие события приостановки VM (такие как исключение визуализации) вместо события выхода из VM. "Гостевая команда" - это термин, используемый в настоящем документе для обозначения команд процессора, образующих часть компьютерной программы, выполняющейся внутри гостевой VM, такой как виртуальные машины VM 52а-b на фиг. 2-А.

[0064] На этапе 302 выполняется попытка выборки гостевой команды. Если попытка выборки завершается ошибкой, на этапе 303 может быть определено, вызвана ли эта ошибка нарушением доступа к памяти (например, когда гостевая команда находится в странице памяти, отмеченной как невыполняемая в структуре SLAT гостевой VM). Если нет, то на этапе 306 процессор 12 генерирует событие выхода из VM и передает выполнение обработчику событий, такому как обработчик 61 на фиг. 2-А. Если ошибка выборки гостевой команды вызвана нарушением доступа к памяти, такая ошибка может указывать на то, что программа безопасности (например, антивредоносный модуль) пытается защитить содержимое соответствующей страницы памяти. Одна примерная секция памяти, обычно защищенная от выполнения таким способом, хранит стек выполнения гостевого процесса. Отметка стека как невыполняемый может защитить гостевой процесс, например, от экслойта стека. В таких ситуациях некоторые варианты осуществления могут повторно попытаться вызвать гостевую команду, игнорируя соответствующие разрешения доступа к памяти (этап 305). На этапе 307, выбранная гостевая команда отмечается специальным флагом для указания на то, что соответствующая команда была "выбрана принудительно", т.е. была выбрана с нарушением разрешения доступа к памяти. Процессор 12 может затем перейти к этапу 308.

[0065] После этапа выборки на этапе 308 выполняется декодировка и диспетчеризация гостевой команды. На этапе 310 гостевая команда запускается на выполнение. Если выполнение гостевой команды удовлетворяет условию выхода из VM, причем это условие не относится к доступу к памяти, процессор 12 переходит к этапу 322, который подробно описан ниже. Такие выходы из VM могут быть инициированы в различных ситуациях. Например, гостевая команда может представлять собой специализированную команду, такую как VMCALL, которая автоматически инициирует событие выхода из VM при вызове изнутри гостевой VM. Еще одной примерной причиной для выхода из VM, не относящейся к доступу к памяти, является возникновение аппаратного события (например, прерывание) во время выполнения гостевой команды.

[0066] Когда выполнение гостевой команды вызывает нарушение доступа к памяти (например, когда гостевая команда инструктирует процессор записывать результат в страницу памяти, отмеченную как не записываемая), обычный процессор как правило приостанавливает выполнение гостевой команды, останавливает конвейер (конвейеры) процессора и генерирует событие приостановки VM (например, VMExit). В отличие от этого, в некоторых вариантах осуществления настоящего изобретения выполнение гостевой команды не приостанавливается. Вместо этого на этапе 318 событие выхода из VM задерживается, пока будет закончена стадия выполнения конвейера для гостевой команды. Однако в некоторых вариантах осуществления результаты завершенной стадии выполнения не фиксируются, как это происходит в обычных системах. Вместо этого на этапе 320 процессор 12 может инструктировать блок 38 фиксации сохранить результаты завершенной стадии выполнения гостевой команды в регистре 44 события приостановки. Такие функциональные возможности могут быть достигнуты, например, при использовании сигнала активации для переключения блока 38 фиксации от фиксации результатов в памяти и/или регистрах общего назначения процессора 12 на сохранение результатов в регистре 44, когда произошло нарушение доступа к памяти. Управляющий сигнал может указывать на то, вызвало ли выполнение гостевой команды нарушение доступа к памяти. Блок 38 фиксации может получать такой сигнал, например, из MMU через модуль 34 доступа к памяти. В некоторых вариантах осуществления этап 320 содержит извлечение блоком 38 фиксации результата выполнения гостевой команды из регистрового файла 40.

[0067] В альтернативном варианте осуществления вместо сохранения результатов выполнения гостевой команды в регистр 44, на этапе 320 такие результаты могут сохраняться в выделенную область памяти, такую как гостевая область состояния VMSO соответствующей гостевой VM. В еще одном варианте осуществления процессор 12 может передавать такие результаты обработчику 61 выхода из VM после выполнения выхода из VM (этап 306).

[0068] На этапе 322 процессор 12 может сохранять результаты дизассемблирования гостевой команды в регистр 4 события приостановки (и/или в память, как описано выше). Альтернативно данные дизассемблирования команды могут быть сохранены в выделенную область VMSO выполняющейся в текущий момент гостевой VM. Данные дизассемблирования команды могут быть получены командным декодером 30 и/или операционным блоком (блоками) 36 в процессе декодирования и/или выполнения гостевой команды; этап 322 может включать в себя извлечение таких данных из соответствующего модуля процессора. После сохранения результатов выполнения и/или данных дизассемблирования для гостевой команды, процессор 12 может генерировать событие выхода из VM (этап 306).

[0069] Когда выполнение текущей гостевой команды происходит без возникновения нарушений доступа к памяти (этап 314) и в отсутствие не относящихся к памяти причин выхода из VM (этап 312), на этапе 315 может быть определено, была ли принудительно выбрана текущая гостевая команда (см. этапы 305-307 выше). Если нет, на этапе 316 результаты выполнения фиксируются в память и/или в регистры процессора общего назначения. Если текущая гостевая команда выбрана принудительно, некоторые варианты осуществления могут обращаться с соответствующей командой как с командой, вызывающей нарушение доступа к памяти, т.е., путем ожидания завершения соответствующей командой этапа выполнения конвейера, сохранения результатов и/или данных дизассемблирования команды в регистр 44 перед генерацией события выхода из VM (см. этапы 318-320-322-306 выше).

[0070] На фиг. 9 показана примерная последовательность этапов, выполняемых гостевой VM и/или модулем 60 компьютерной безопасности (фиг. 2-А-В) согласно некоторым вариантам осуществления настоящего изобретения, которые относятся к компьютерной безопасности. Гостевой процесс, такой как приложение (например, 56а на фиг. 2-А) или процесс операционной системы (например, гостевой ОС 54а на фиг. 2-А) может выполняться внутри гостевой VM с пошаговым продвижением через последовательность гостевых команд (этап 332). Выполнение гостевого процесса продолжается, пока будет генерирован выход из VM, в соответствии, например, со сценарием, описанным выше со ссылкой на фиг. 8. Специалисту в данной области техники может быть понятно, как изобретение может быть адаптировано к системе, в которой процессор 12 генерирует исключение виртуализации вместо события выхода из VM, и в которой обработчик исключений, выполняющийся внутри гостевой VM (например, обработчик 63 на фиг. 2-В) конфигурирован для перехвата соответствующего исключения.

[0071] На этапе 336 обработчик 61 перехватывает событие выхода из VM, которое анализируется на факт угрозы безопасности. Если событие указывает на угрозу безопасности (например, операция, выполняемая со злоумышленным намерением), на этапе 340, МКБ 60 может предпринять защитное действие против гостевого процесса и/или против гостевой VM. Такое действие может включать в себя, среди прочего, блокирование выполнения гостевого процесса, возвращение сообщения об ошибке или набора фиктивных результатов в гостевой процесс и предупреждение администратора хостовой системы.

[0072] Когда событие выхода из VM не указывает на угрозу безопасности, на этапе 342 определяется, доступны ли результаты выполнения гостевой команды (либо в регистре 44 событий процессора 12, либо в памяти). Если нет, то МКБ 60 переходит к этапу 348, который подробно описан ниже. Если да, то на этапе 344 извлекаются соответствующие результаты из регистра 44 и/или памяти (например, гостевой области состояния VMSO соответствующей гостевой VM). На этапе 346, МКБ 60 может применить результаты выполнения текущей гостевой команды. В некоторых вариантах осуществления этап 346 содержит набор операций, выполняемых в обычных системах на стадии фиксации. Например, этап 346 может включать в себя обновление значений регистров общего назначения, управляющих регистров и регистров состояния процессора виртуализированного процессора соответствующей гостевой VM. В некоторых вариантах осуществления такие регистры доступны внутри гостевой области состояния VMSO соответствующей гостевой VM. Этап 346 может дополнительно включать в себя сохранение некоторых результатов в адресах памяти, указанных операндом текущей гостевой команды. Этап 346 может дополнительно включать в себя увеличение значения указателя команды (например, RIP на платформах х86), чтобы показать, что выполнение текущей гостевой команды завершено.

[0073] Некоторые варианты осуществления настоящего изобретения добавляют выделенную команду к текущей архитектуре набора команд (ISA) процессора 12, причем новая команда инструктирует процессор 12 применить результат выполнения гостевой команды непосредственно из-под гостевой VM, выполняющей соответствующую гостевую команду. Эта новая команда (мнемоническим примером является VMAPPLY) может выполнять операции этапа 346 (фиг. 9), например, копировать содержимое из регистра 44 события приостановки в виртуальные регистры виртуализированного процессора соответствующей гостевой VM и/или в память.

[0074] В некоторых вариантах осуществления на этапе 346 может дополнительно проверяться, является ли текущая гостевая команда атомарной командой (например, как указано префиксом LOCK). Если да, то вместо применения результатов непосредственно к регистрам гостя и/или к памяти, этап 346 может принудительно инициировать повторное выполнение текущей гостевой команды при возвращении к гостевой VM (см. этап 356 ниже).

[0075] Если результаты выполнения текущей гостевой команды не доступны (например, если выход из текущей VM был вызван привилегированной командой, такой как VMCALL), на этапе 348 модуль 60 компьютерной безопасности определяет, доступны ли данные дизассемблирования для текущей гостевой команды. Если да, то на этапе 350, МКБ 60 может извлечь такие данные, например из поля 46а дизассемблирования регистра 44 (см. например, фиг. 6). МКБ 60 может затем перейти к эмуляции текущей гостевой команды согласно извлеченным данным дизассемблирования (этап 354).

[0076] Если данные дизассемблирования доступны, на этапе 352 может быть выполнено дизассемблирование текущей гостевой команды перед переходом к эмуляции. На этапе 356, МКБ 60 может повторно запустить соответствующую гостевую VM (например, посредством выдачи команды VMRESUME на платформах Intel®). В некоторых вариантах осуществления, в которых этап 346 включает в себя изменение указателя команды, выполнение гостевого процесса будет начинаться с команды процессора, непосредственно следующей за текущей гостевой командой, или с команды процессора, указанной текущей гостевой командой (например, в случае управляющих команд изменения потока, такой как JMP, CALL и т.д.).

[0077] Примерные системы и способы, описанные выше, позволяют хостовой системе, такой как компьютер или смартфон, эффективно выполнять задачи компьютерной безопасности при работе в конфигурации аппаратной виртуализации. Задачи безопасности могут включать в себя, среди прочего, защиту хостовой системы от вредоносных программ, таких как компьютерные вирусы и шпионские программы. В некоторых вариантах осуществления хостовая система конфигурирована для выполнения операционной системы и набора программных приложений внутри виртуальной машины. Модуль безопасности может выполняться вне соответствующей виртуальной машины, например, на уровне гипервизора, и может защищать соответствующую виртуальную машину от вредоносных программ.

[0078] В некоторых вариантах осуществления модуль безопасности идентифицирует секцию памяти (например, набор страниц памяти), содержащую код и/или данные, являющиеся критическими для безопасности защищенной VM, и конфигурирует разрешения на доступ для соответствующей секции памяти. Такие разрешения на доступ могут указывать, например, на то, что соответствующая секция памяти является не записываемой и/или не выполняемой. Модуль безопасности дополнительно может конфигурировать процессор хостовой системы для генерации события приостановки VM (такого, как выход из VM или исключение виртуализации) в ответ на нарушение доступа к памяти, например, когда программное обеспечение, выполняющееся внутри защищенной VM, пытается записать в секцию памяти, отмеченную как не записываемая, или выполнить код из секции памяти, отмеченной как невыполняемая. Модуль безопасности может при этом перехватывать такие события процессора через обработчик событий, и может определять, указывают ли эти события на угрозу компьютерной безопасности. В конфигурациях, в которых модуль безопасности выполняется вне защищенной VM, активность модуля безопасности потенциально является невидимой для программного обеспечения, выполняющегося внутри защищенной VM, включая вредоносные программы.

[0079] В обычных системах перехват событий приостановки VM протекает согласно способам, обычно известным в данной области техники как "лови-и-эмулируй". В одном примере обычной технологии, после определения, какая команда вызвала соответствующее событие (например, выход из VM) антивредоносная программа эмулирует соответствующую команду перед возвратом выполнения к защищенной VM и модифицирует указатель команды для указания на то, что соответствующая команда уже выполнялась. Без этапа эмуляции возврат выполнения к защищенной VM, как правило, мог бы повторно инициировать выход из VM, создавая, таким образом, бесконечную петлю.

[0080] Таким образом, в обычных системах и способах "лови-и-эмулируй" может потребоваться, чтобы антивредоносная программа содержала дизассемблер команд и/или эмулятор команд. Такие компоненты могут быть сложными в разработке и обслуживании и могут быть не переносимыми, например, из одного процессора в другой. Кроме того, в обычных системах этапы дизассемблирования и/или эмуляции обычно выполняются для каждого события приостановки VM, что оказывает значительную вычислительную нагрузку на хостовую систему. Напротив, некоторые варианты осуществления настоящего изобретения устраняют необходимость в дизассемблере и/или эмуляторе, существенно ускоряя операции компьютерной безопасности.

[0081] Некоторые варианты осуществления настоящего изобретения вводят изменения в конфигурацию и работу обычных процессоров, позволяя таким процессорам работать более эффективно в конфигурациях аппаратной виртуализации. В некоторых вариантах осуществления процессор конфигурирован для задержки генерации события приостановки VM, пока будет завершена фаза выполнения конвейера для текущей команды, по меньшей мере, в некоторых случаях (например, когда событие приостановки VM инициируется нарушением доступа к памяти). Процессор может быть дополнительно конфигурирован для сохранения результата стадии выполнения текущей команды в специальный регистр процессора (отличный от регистров общего назначения или управляющих регистров процессора) или в специальную область памяти (например, в гостевую область состояния VMSO соответствующей гостевой VM).

[0082] Эти усовершенствования могут быть особенно предпочтительными для приложений компьютерной безопасности, обеспечивая возможность эффективной защиты виртуальной машины извне, например, из уровня гипервизора, предоставляющего соответствующую VM. По сравнению с обычным решением компьютерной безопасности, некоторые варианты осуществления настоящего изобретения обеспечивают существенное сокращение вычислений за счет исключения стадий дизассемблирования и эмуляции из работы программного обеспечения безопасности, конфигурированного для перехвата и анализа событий приостановки VM. Вместо эмуляции команды, генерировавшей соответствующее событие, некоторые варианты осуществления позволяют программному обеспечению безопасности считывать соответствующие результаты из регистра процессора или области памяти, и непосредственно применять такие результаты.

[0083] В отличие от обычных систем, некоторые варианты осуществления настоящего изобретения генерируют событие приостановки VM только после того, как текущая гостевая команда завершит стадию выполнения конвейера. Такие изменения функциональных возможностей аппаратных компонентов может внести задержку из-за дополнительных тиков таймера, необходимых для осуществления стадии выполнения соответствующей команды. Однако такое ухудшение эффективности, по существу, компенсируется посредством исключения операций эмуляции и/или дизассемблирования команды, необходимых в обычном программном обеспечении компьютерной безопасности (потенциально доходящих до сотен дополнительных команд для каждого события приостановки VM)

[0084] Специалисту в данной области техники понятно, что приведенные выше варианты осуществления изобретения могут быть изменены различными способами без выхода за рамки объема изобретения. Соответственно, объем изобретения должен определяться согласно нижеследующей формуле изобретения и ее законных эквивалентов.

Реферат

Изобретение относится к области компьютерной безопасности. Техническим результатом является обеспечение компьютерной безопасности виртуальной машины. Процессор конфигурирован для генерации события приостановки виртуальной машины (VM) (например, выхода из VM или исключения виртуализации), когда гостевая команда, выполняющаяся внутри гостевой VM, осуществляет нарушение на доступ к памяти. В некоторых вариантах осуществления процессор дополнительно конфигурирован для задержки генерации события приостановки VM, пока будет завершена стадия выполнения конвейера для гостевой команды, и для сохранения результатов стадии выполнения в специальной области (например, в специальном регистре процессора, считываемом программным обеспечением безопасности) перед генерацией события. 4 н. и 17 з.п. ф-лы, 11 ил.

Комментарии