Микропроцессорная система - SU1172455A3

Код документа: SU1172455A3

Чертежи

Описание

рователк сигнапов Чтение-запись, о первым и вторым выходами формивыходы которых являются соответствен- рователя сигналов Чтение-запись.

1172455

Реферат

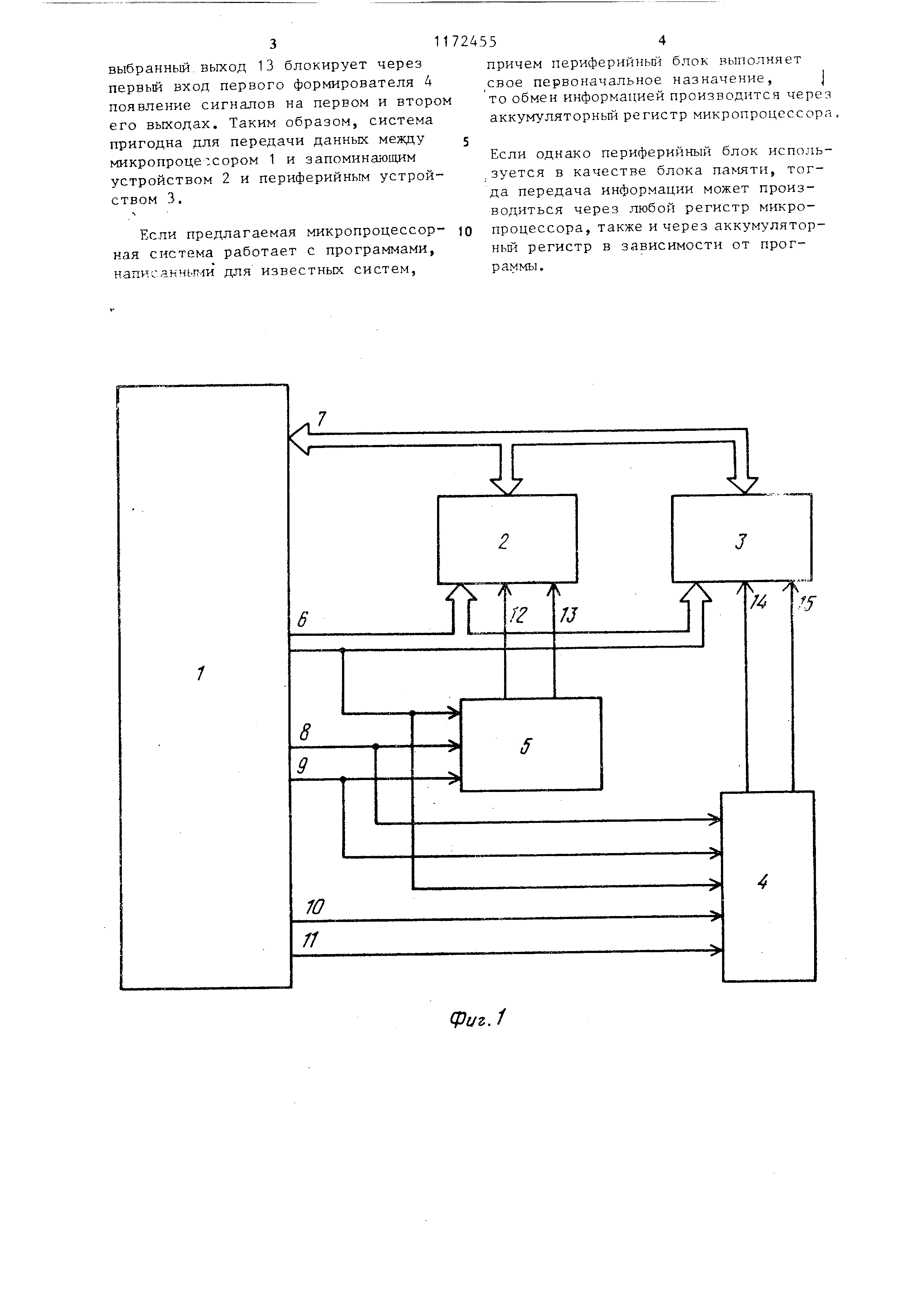

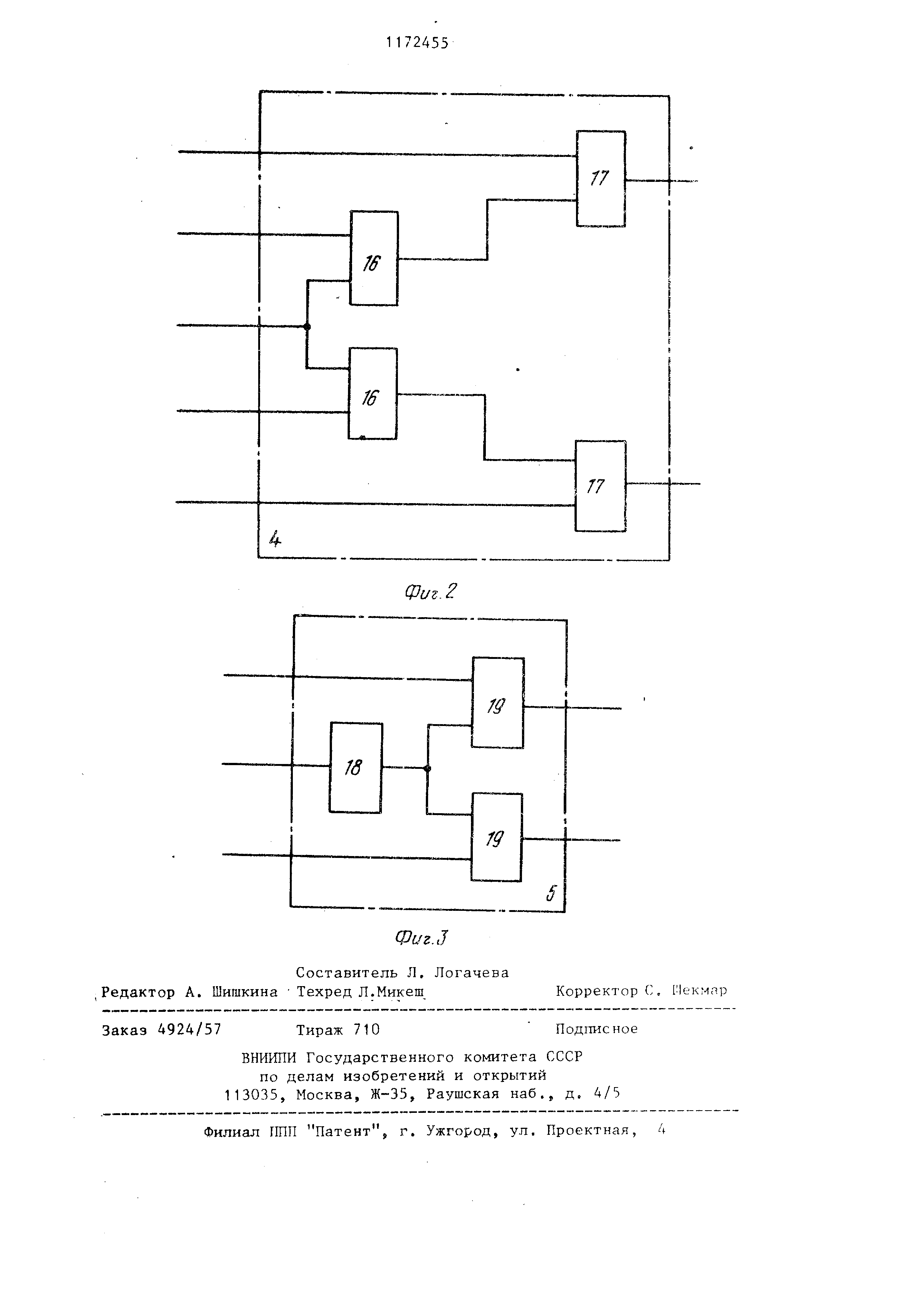

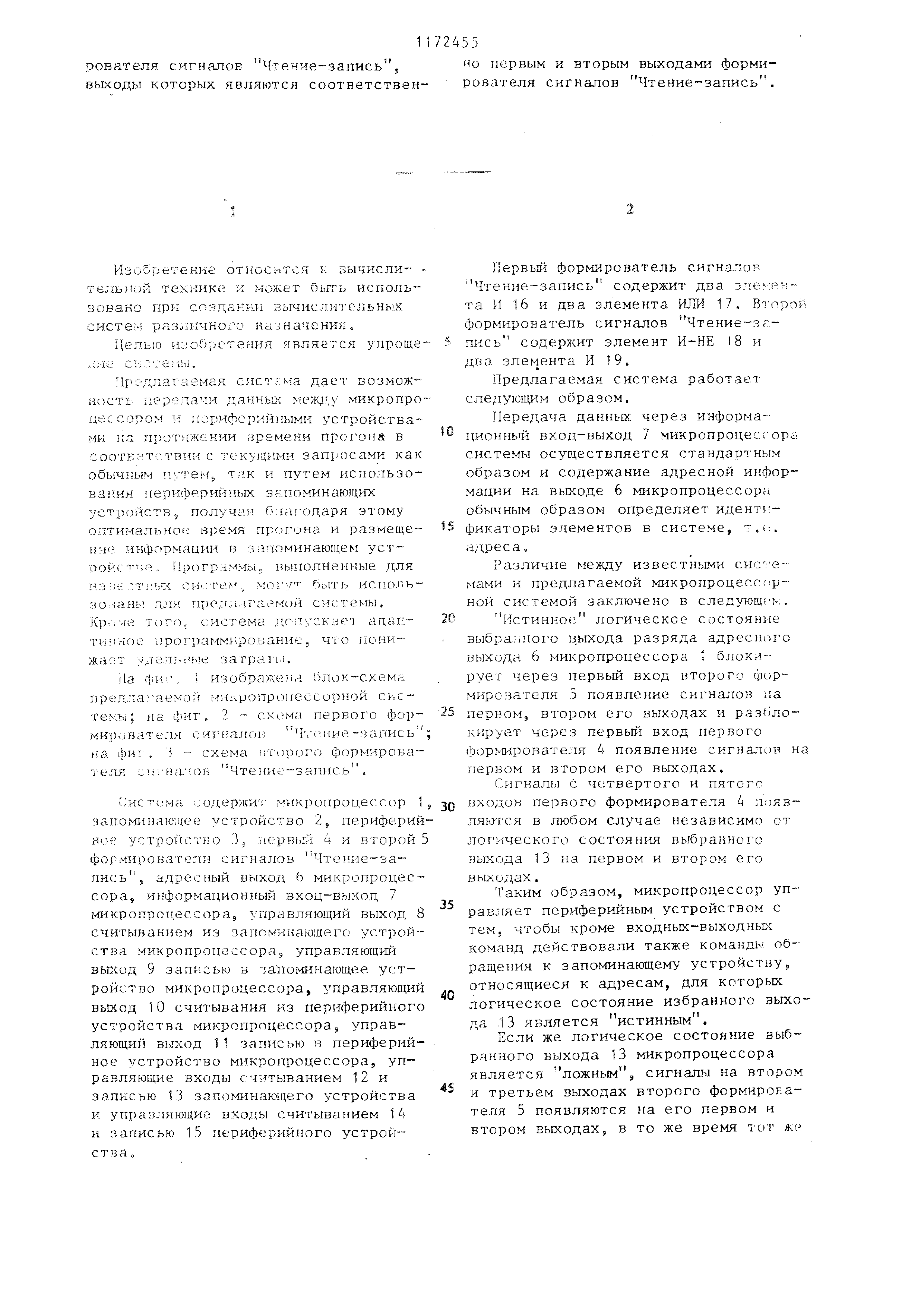

МИКРОПРОЦЕССОРНАЯ СИСТЕМА, содержащая микропроцессор, запоминающее устройство и периферийное устройство , причем информационные входы-выходы запоминающего и периферийного устройств через информационную шину соединены с информационным входом-выходом микрокомпрессора, адресный выход которого соединен через адресную .шину с адресными входами запоминающего и перифериГжого устройств, отличающаяся тем, что, с целью упрощения, она содержит первый и второй формирователи сигналов Чтениезапись , к первым входам которых поключер; в1)Гход разряда адресного выхода микр(.1Т1ро1де(.:сора, управляющие выходы считьтанием и записью периферийН (П I запоминающего устройств которого гт1.1Лк:1Юк:11Ы соответственно к BTopbw 1 тр(-|ч,и--1 входам первого и второго формирователей ст гналон Чтение-запись, управляю1иие выходы считыванием и записью тапомиткчющего устройства микропроцессора подключены соответственно к четвер-л/ч-гхи пятому вxoдa i первого формирователя сигналов Чтение-запись, первый и второй ВЫХОДЬ которого ПОДКЛЮЧ1:(М соответственно к управляющим вхолам считыванием п записью периферийН.::го устройства, первь й и второй выхгЛы второго формирователя сигналов Чтение-запись подключоны соответственно к управляюши входам считывание:-; и записью запоминающего устройства , первый формирователь ситналов Чтение-запись содержит два элемента И и два элемента iUD-l, причем первый вход первого формтфовате.ля сиг KasiEbj налов Чте;Ие-зап сь подключен к первым входам первого и второго элементов И, выходы которых подключены соответствечно к вторым входам первого и второго элементов ИЛИ, вторые входы которых н: вторые входы первого и второго элементов И подключены соответст1 енно к второму, третьему, четвертому и пятому входам первого формирователя сигналов Чте , первый и второй выходы ние-запись которого являются выходами первого и второго элементов ИЛ1-} соответственно , второй формирователь сигналов Чтение-запись содержит элемент И-НЕ и два элемента И, первьш вход второго формирователя сигналов Чтение-запись через элемент И-НЕ подключен к первым входам первого и второго элементов И, к вторым входам которых подключены соответственно второй и третий входы второгс борми

Комментарии