1

Изобретение относится к устройству

управления в цифровых системах обработки данных и, в частности,

может быть использовано в микропроцессорах ,, микроконтроллерах и т.п.

Известна система обработки данных в которой устройства управления

содержат регистры управления, в которые записываются управляющие данные , используемые при выполнении

программы для определения образа действия в конкретных ситуациях l.

Хотя управляющие регистры увеличивают возможности основной схемы управления, так как управление записью

в них может осуществляться с помощью программы, они не позволяют производить выборочную установку

или изменение состояния отдельных управляющих разрядов, так как запись информации во все 32 двоичных

разряда этих регистров производится одновременно. Это является недостатком,особенно в случае небольших

систем с ограниченными возможностями типа микропроцессора.

Наиболее близким к изобретению п технической сущности является микропроцессор , содержащий кроме обычных

функциональных блоков запоминающее устройство, регистр операции или

регистр команд, соединенный с выходом запоминающего устройства, декодирующую схему или схему управления, соединенную с выходом регистра операции , для генерирования сигналов

управления для других блоков данного

микропроцессора 2 .

Сигналы управления являются зависимыми только от настоящих содержаний

регистра операции и, таким образом , данный микропроцессор имеет

до некоторой степени ограниченную возможность управления.

Целью изобретения является получение большей гибкости управления

системой обработки данных и осуществление выборочного изменения независимых

параметров контроля за счет содержимого единственной команды. Поставленная цель достигается

тем, что устройство управления в

системе обработки данных, содержащее

блок памяти, выход которого соединен с информационным входом регистра

команд, управляющий выход которого соединен с входом дешифратора

команд, содержит группу блоков- вспомогательного управления и блок контроля

нагрузки, причем группа выходов дешифратора команд соединена с группой управляющих входов блока

контроля нагрузки, тактовьй вход

которого соединен с тактовым входом

устройства, группа информационных входов блока контроля нагрузки соединена с группой адресных выходов

регистра команд, первые входы блоко вспомогательного управления группы

соединены с соответствующими выходами данных регистра.команд,вторые входы блоков вспомогательного управ

ления группы соединены с соответствующими выходами блока контроля наг рузки, выходы блоков вспомогательного

управления группы соединены с соответствующими выходами устройства .

Причем блок контроля нагрузки содержит группу элементов И,первые входы которых соединены с соответствующими

входами группы информационных входов блока, вторые входы всех элементов И группы соединены

с соответствующими входами группы управляющих входов блока, третьи входы всех элементов И группы соеди

нены с тактовым входом блока, выходы элементов И группы соединены с соответствующими выходами блока.

Кроме того, блок контроля нагруз ки содержит элемент ИЛИ и группу элементов И, причем первые входы

элементов И группы соединены с соот ветствующими входами группы информационных

входов блока, вторые входы первого и второго элементов И группы соединены с первой половиной

входов группы управляющих входов блока и с первым входом элемента ИЛ вьсход которого соединен с вторыми

входами третьего и четвертого элементов И группы, вторые входы пятого и шестого элементов И группы сое

динены с второй половиной входов группы управляющих входов блока и с вторым входом элемента ИЛИ,выходы

элементов И группы соединены с соответствующими выходами блока. При этом блок вспомогательного

управления содержит два элемента НЕ два элемента НЕ-И, причем первый вход первого элемента НЕ-И соединен

с первым входом блока, второй вход которого соединен с первым входом второго элемента НЕ-И и через первы

элемент НЕ - с вторым входом первого элемента НЕ-И, выходы первого и второго элементов НЕ-И соединены

через второй элемент НЕ с выходом блока и с вторым входом второго элемента НЕ-И.

Блок вспомогательного управления содержит элемент НЕ, два элемента И и триггер, причем первый вход

первого элемента И соединен с первым входом блока и через элемент НЕ с

первым входом второго элемента И, второй вход которого соединен с вторыми

входами блока и первого элемента И, выход которого соединен с , входом установки триггера, вход

сброса которого соединен с выходом второго элемента И, выход триггера соединен с выходом блока.

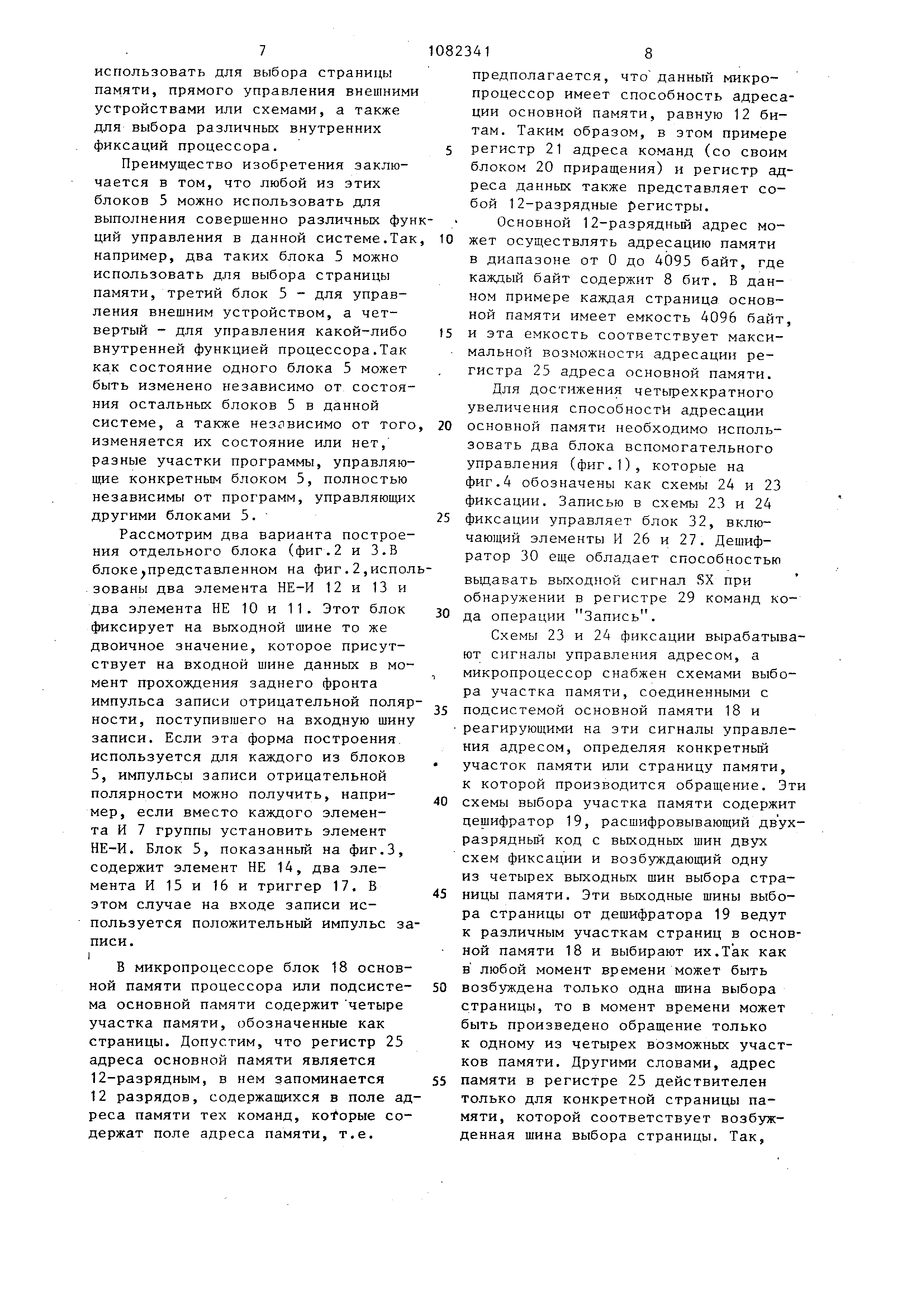

На фиг.1 представлена блок-схема устройства управления с первым вариантом выполнения блока контроля

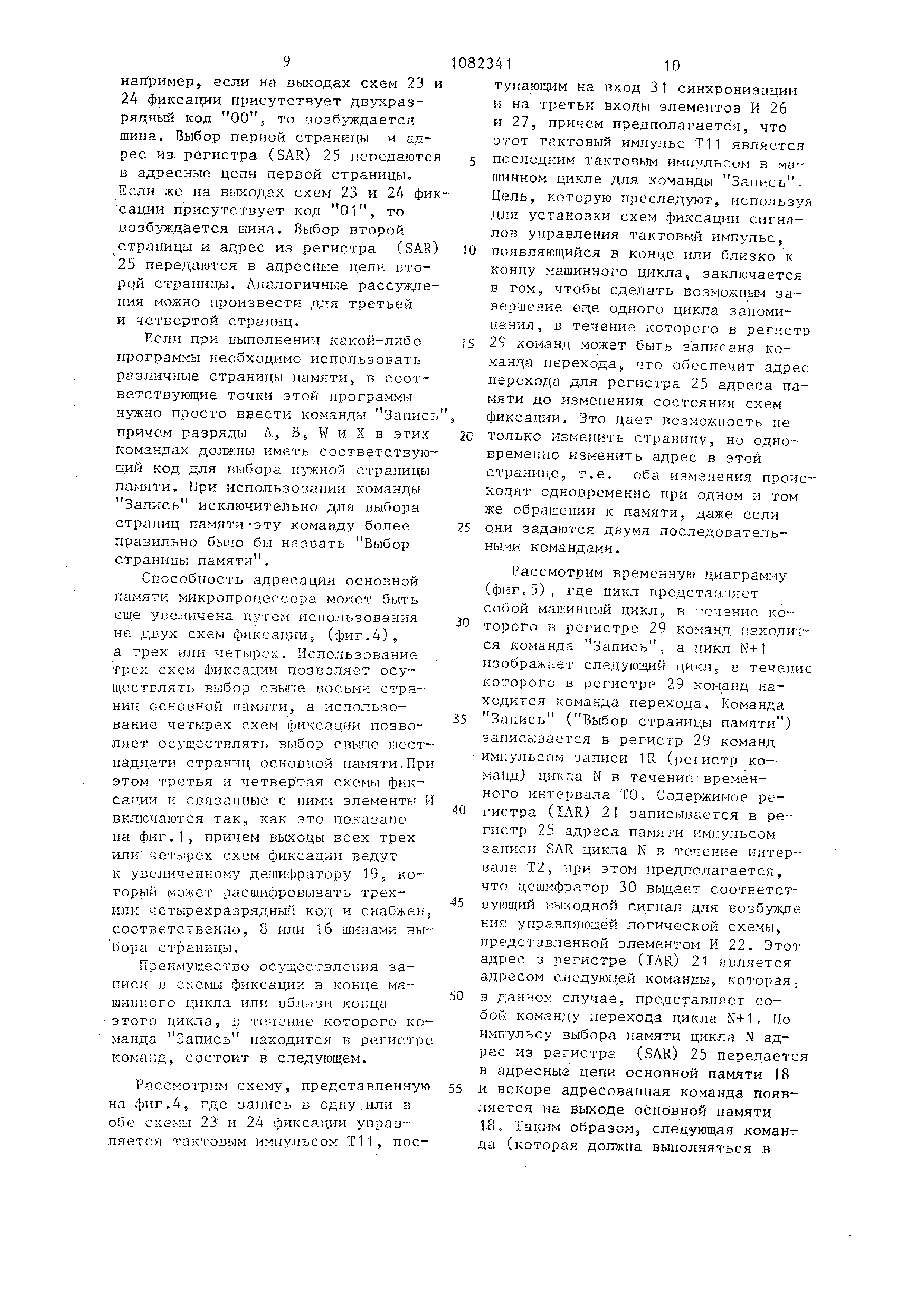

нагрузки; на фиг.2 - блок-схема блока вспомогательного управления,первый

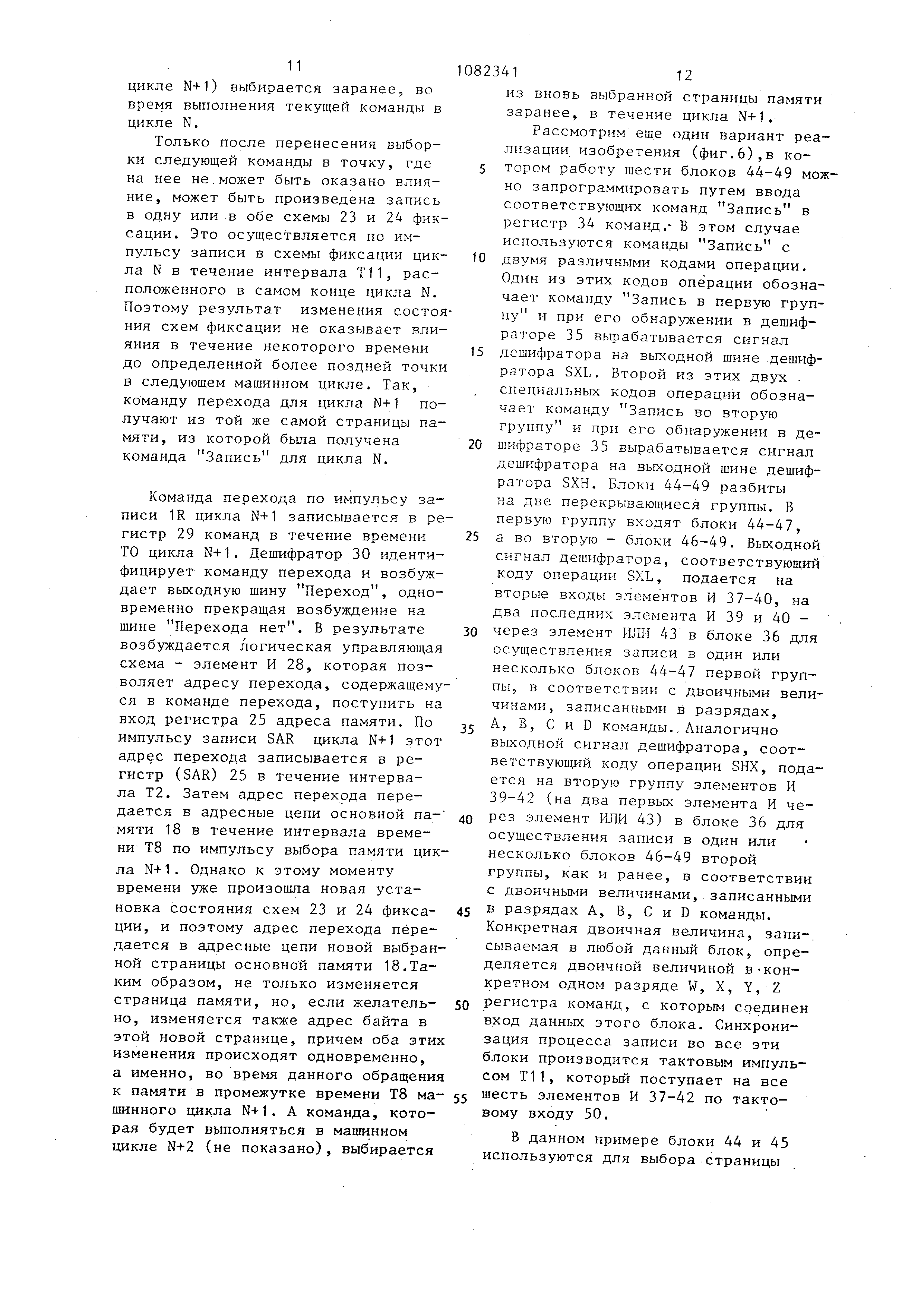

вариант; на фиг.З - то же, второй вариант;на фиг.4 - вариант применения устройства в микропроцессоре;

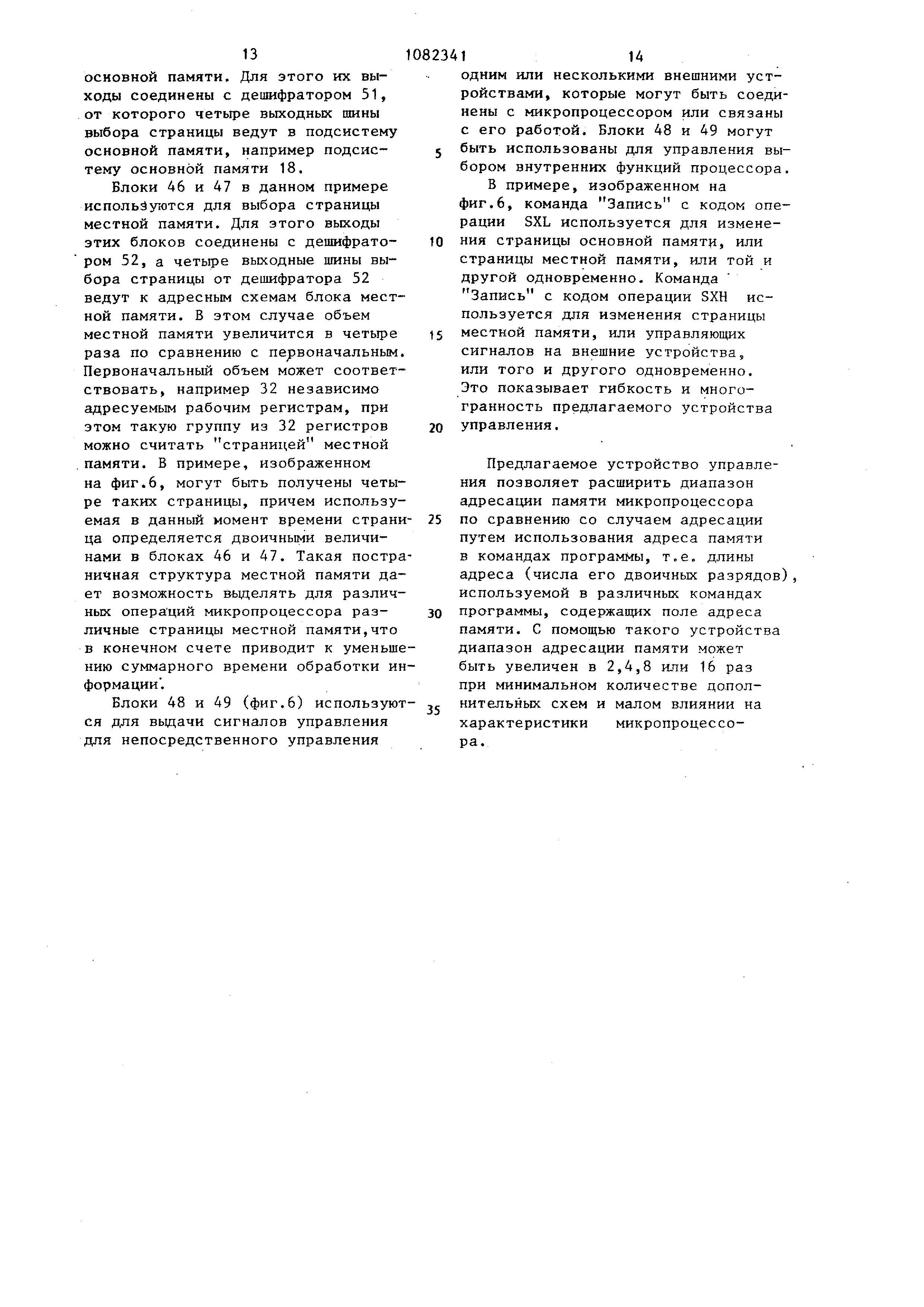

на фиг.З - временлая диаграмма работы , изображенной на фиг.4,

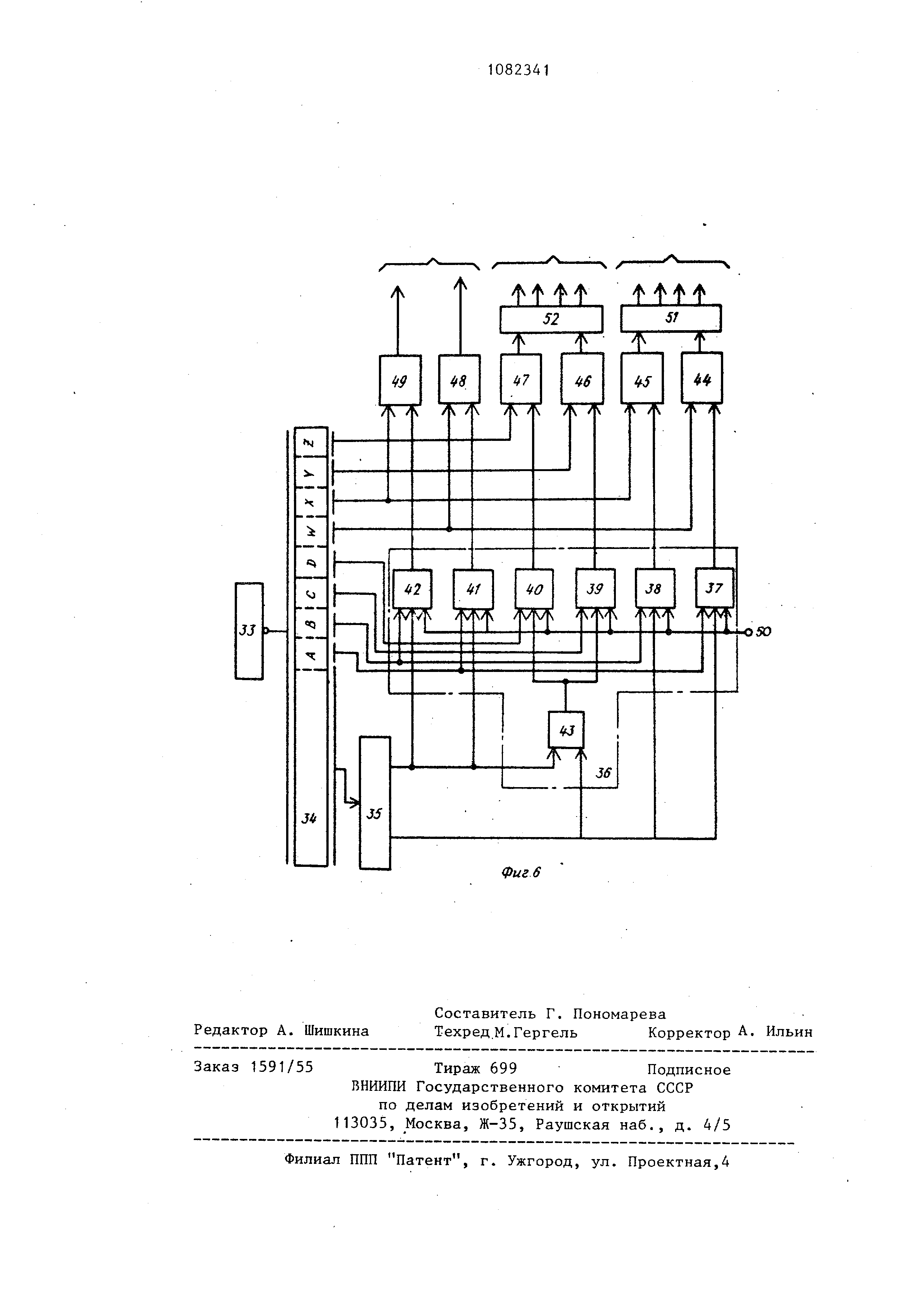

на фиг.6 - блок-схема устройства управления с вторым вариантом выполнения блока контроля нагрузки.

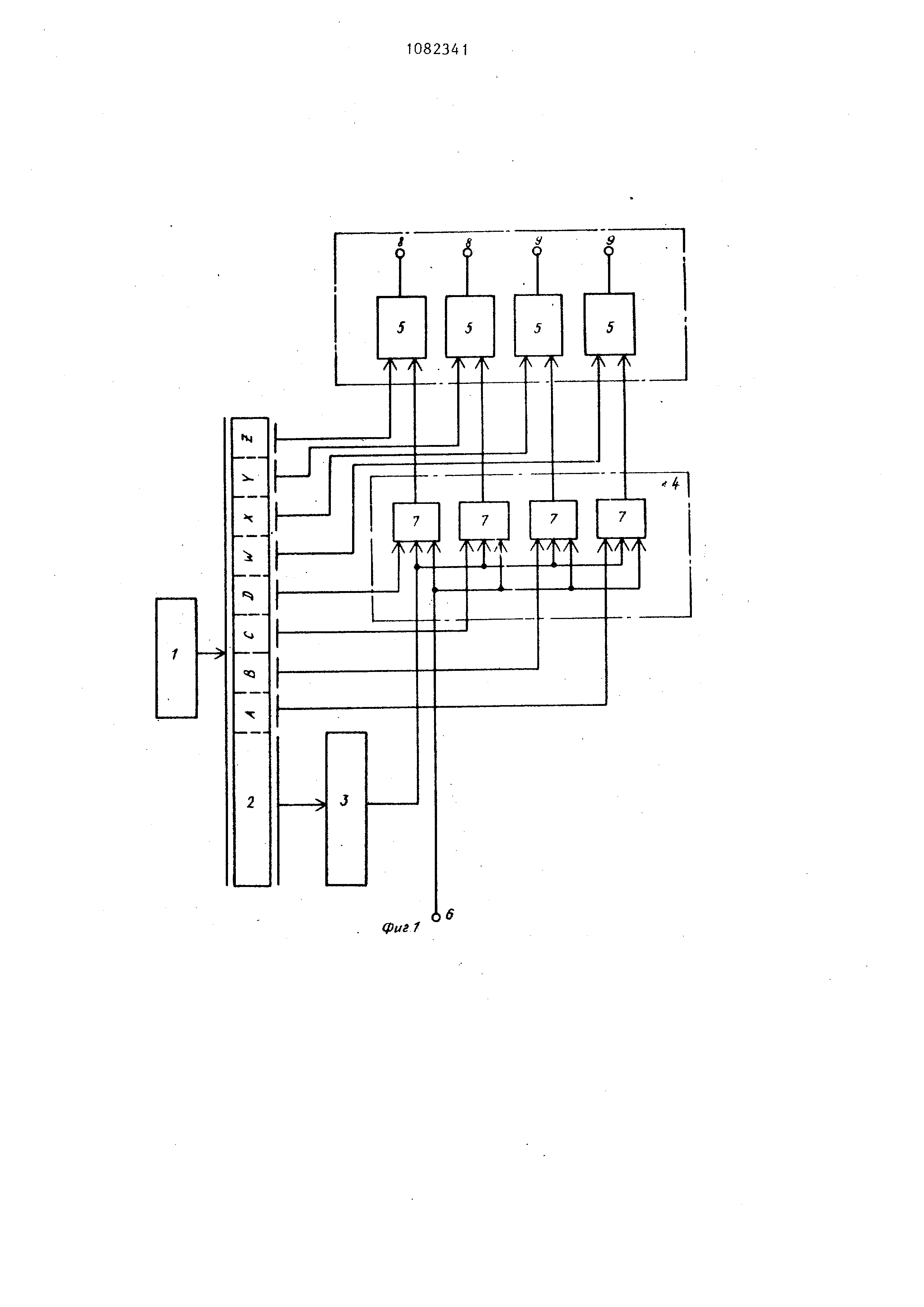

Устройство управления (фиг.1) содержит блок 1 памяти, регистр 2 команд , дешифратор 3 команд, блок 4

контроля нагрузки, блоки 5 вспомогательного управления группы, тактовьш

вход 6 устройства. Блок 4 (по первому варианту) содержит элементы И 7

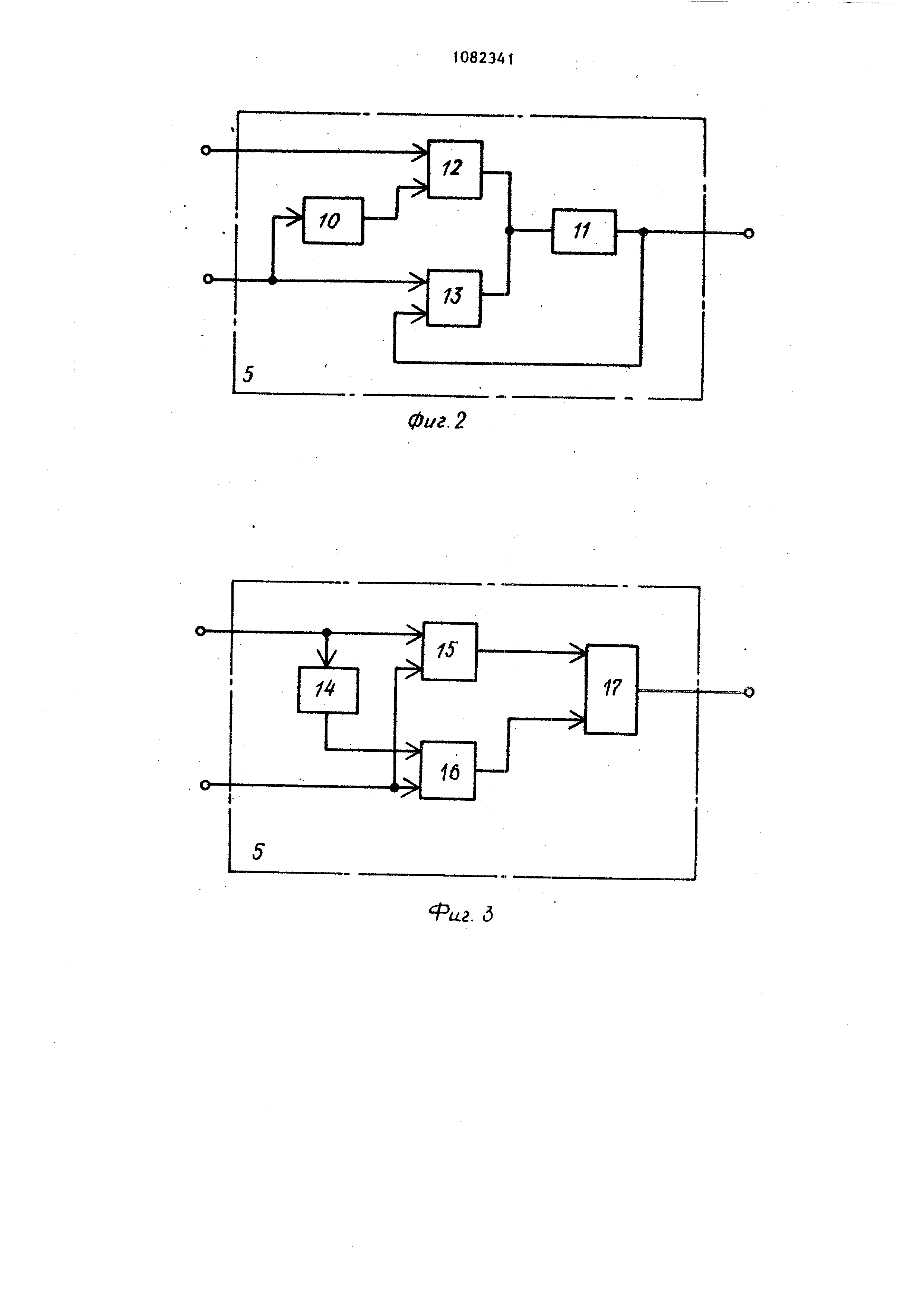

группы. Кроме того, устройство содержит выходы 8 и 9. Блок 5 по первому варианту (фиг.2)

содержит элементы НЕ 10 и 11, элементы НЕ-И 12 и 13. Блок 5 по второму варианту (фиг.З)

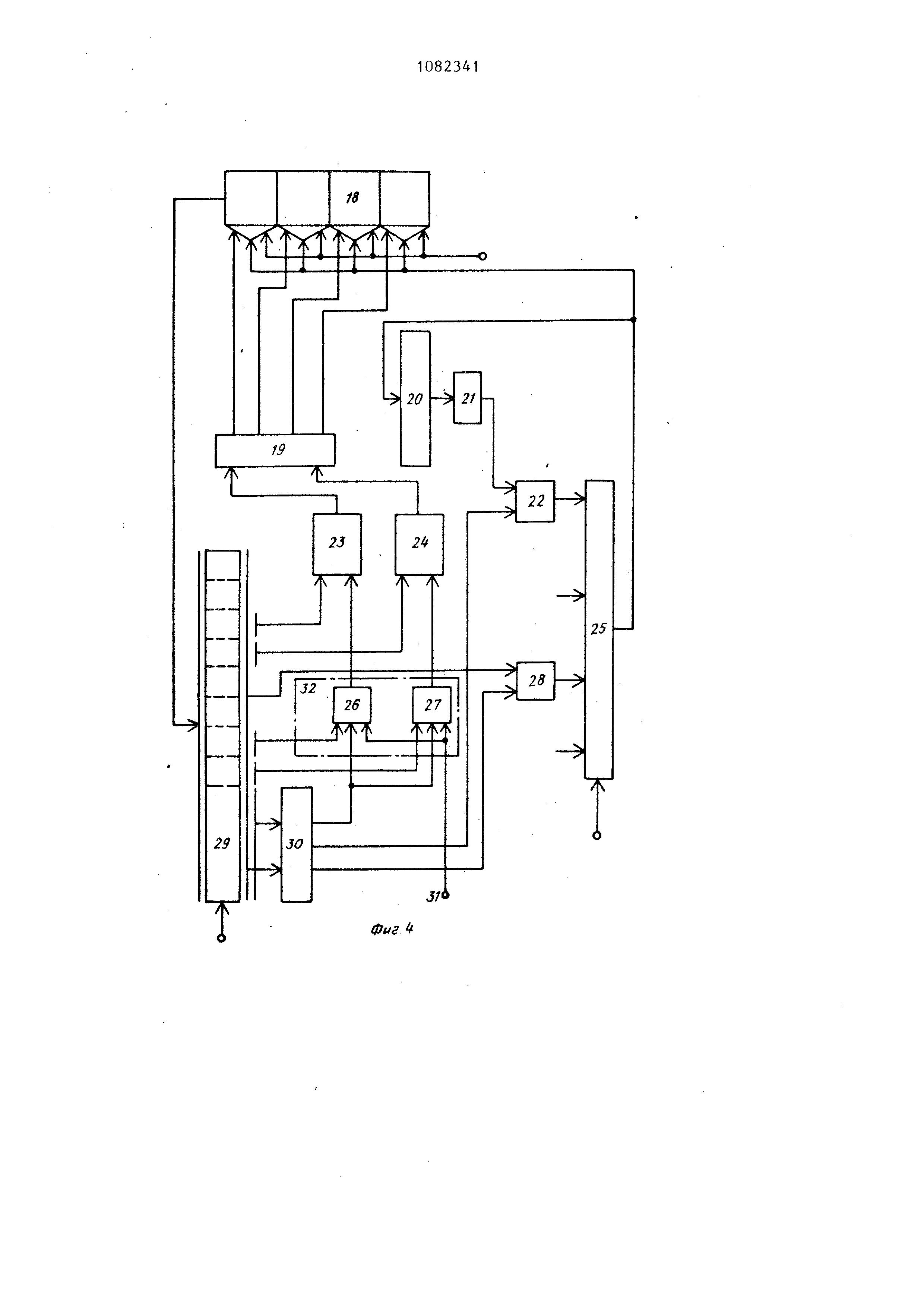

содержит элемент НЕ 14,элементы И 15 и 16 и триггер 17. Микропроцессор (фиг.4) содержит

блок 18 основной памяти, дешифратор 19, блок 20 приращения, регистр

21 адреса команды, элемент И 22, схемы 23 и 24 фиксации, регистр 25

адреса основной памяти, элементы И 26-28, регистр 29 команд, дешифратор

30, вход 31 синхронизации,блок 32 контроля нагрузки. Устройство управления с вторым

вариантом выполнения блока контроля нагрузки (фиг.6) содержит блок 33

памяти, регистр 34 команд, дешифратор 35 команд, блок 36 контроля

нагрузки, содержащий элементы И 37-42 группы и элемент ИЛИ 43, блоки 44-49

вспомогательного управления группы, тактовый вход 50,дешифраторы 51 и 52.

Регистр 2 команд принимает за один раз одну команду от блока 1 памяти . Для осуществления записи в од или несколько блоков 5 в набор команд устройства обработки данных до

бавляется новая команда. Назовем ее командой Запись. Для отличия этой команды от команд других типов в

заданном наборе команд ей придается единственньш заранее установленный код операции (ОР СООЕ). Остальные

двоичные разряды А, В, С, D, W, X, Y, Z команды Запись составляют операнд этой команды и обеспечивают

единственные конкретные значения адреса и данных устройства управления. В частности, разряды

A-D образуют поле адреса, а разряды W-Z поле данных. Как это имеет место в известных

устройствах обработки данных, процессор , в котором используется устройство управления, работает пов

торяющимися временными циклами или машинными циклами. Каждый машинный

цикл устройства обработки данных по разделяется на-последовательности

временных интервалов равной длительности , и для каждого такого интервала обеспечивается отдельный

тактовый импульс. Допустим, что машинные циклы процессора разбиты

на 12 временных интервалов, обозначенных ТО + Т11. Один из тактовых импульсов, например, импульс Т 11,

появляющийся на входе 6 в конце машинного цикла, подается на третий вход каждого элемента И 7 груп

пы-. Любой элемент И 7 группы будет вьщавать сигнал записи на соответствующий

ей блок 5 при одновременном выполнении трех условий, а именно: соответствующий двоичный ра

ряд группы ABCD регистра 2 команд имеет значение 1, дешифратор 3 обнаружил команду Запись ()

присутствует тактовый импульс Т11. Так, например, первый элемент И 7 группы вьщает сигнал записи на вход

соответствующего блока 5, когда в двоичный разряд 102 (А) записана 1, на выходе дешифратора 3 (SX)

также единичное значение, и на входе 6 появляется тактовый импульс Т1 1 с уровнем логической 1. Если

же на одном или нескольких входах элемента И 7 группы уровень сигнала не равен логической 1, на вход

16 записи блока 5 сигнал записи не поступает.

Двоичные разряды, А, В, С и D команды Запись определяют один из блоков 5, в который при появлении

такой команды будет произведена запись. В разрядах А, В, С и D соответствующих блоков 5, в которые

должна быть произведена запись, находится логическая 1. В разрядах А, В, С и D соответствующих блоков

5, запись в которые производится не должна, находится логический О, Если на блок 5 не поступает сигнала

записи, то его состояние не изменяется . Если необходимо произвести запись

в него, то значение записываемого в него сигнала определяется величиной, записанной в соответствующем

двоичном разряде W, X, Y и Z команды Запись. Так, например , если в рязряде ,W содержится

двоичная логическая 1, то сигнал записи на выходе элемента И 7 группы

запишет единичную величину в соответствующий блок 5. И наоборот, если в разряде содержится двоичный

логический О, то сигнал записи на выходе элемента И 7 группы запишет

нулевое значение в соответствующий блок 5. Формат команды Запись (фиг.1)

дает возможность изменить состояние любого одного, двух, трех или

четырех блоков 5 с программным управлением , причем состояние любого такого блока может быть изменено

либо в нулевое, либо в единичное по желанию. Это дает значительную гибкость при установке и сбросе

в исходное состояние блоков 5 с программным управлением. Всякий раз когда программисту нужно изменить

состояние одного или нескольких блоков 5, он просто вводит в программу

команду Запись с соответствующими значениями двоичных разрядов А, В, С, D, W, X, Y, Z. Когда

при выполнении данной программы эта команда поступает в регистр 2

команд, состояние одного или нескольких блоков 5 изменяется соответствующим образом.

Выходные величины XI, Х2, ХЗ и Х4 На выходах блоков 5 можно использовать

для различных целей управления в системе обработки данных, в которой размещены эти блоки 5. Их можно

использовать для выбора страницы памяти, прямого управления внешними

устройствами или схемами, а также для выбора различных внутренних фиксаций процессора.

Преимущество изобретения заключается в том, что любой из этих блоков 5 можно использовать для

выполнения совершенно различных фун ций управления в данной системе.Так например, два таких блока 5 можно

использовать для выбора страницы памяти, третий блок 5 - для управления внешним устройством, а четвертый

- для управления какой-либо внутренней функцией процессора.Так как состояние одного блока 5 может

быть изменено независимо от состояния остальных блоков 5 в данной системе, а также независимо от того

изменяется их состояние или нет, разные участки программы, управляющие конкретным блоком 5, полностью

независимы от программ, управляющих другими блоками 5. Рассмотрим два варианта построения

отдельного блока (фиг.2 и З.В блоке представленном на фиг.2,испол . зованы два элемента НЕ-И 12 и 13 и

два элемента НЕ 10 и 11. Этот блок фиксирует на выходной шине то же

двоичное значение, которое присутствует на входной шине данных в момент прохождения заднего фронта

импульса записи отрицательной поляр ности, поступившего на входную шину

записи. Если эта форма построения используется для каждого из блоков 5, импульсы записи отрицательной

полярности можно получить, например , если вместо каждого элемента И 7 группы установить элемент

НЕ-И. Блок 5, показанный на фиг.З, содержит элемент НЕ 14, два элемента И 15 и 16 и триггер 17. В

этом случае на входе записи используется положительный импульс за писи.

В микропроцессоре блок 18 основной памяти процессора или подсистема основной памяти содержит четыре

участка памяти, обозначенные как страницы. Допустим, что регистр 25 адреса основной памяти является

12-разрядным, в нем запоминается 12 разрядов, содержащихся в поле ад

реса памяти тех команд, которые содержат поле адреса памяти, т.е. предполагается, чтоданный микропроцессор имеет способность адресации основной памяти, равную 12 битам

. Таким образом, в этом примере регистр 21 адреса команд (со своим

блоком 20 приращения) и регистр адреса данных также представляет собой 12-разрядные регистры.

Основной 12-разрядный адрес может осуществлять адресацию памяти в диапазоне от О до 4095 байт, где

каждый байт содержит 8 бит. В данном примере каждая страница основной памяти имеет емкость 4096 байт,

и эта емкость соответствует максимальвой возможности адресации регистра 25 адреса основной памяти.

Для достижения четьфехкратного увеличения способности адресации

основной памяти необходимо использовать два блока вспомогательного управления (фиг.1), которые на

фиг.4 обозначены как схемы 24 и 23 фиксации. Записью в схемы 23 и 24

фиксации управляет блок 32, включающий элементы И 26 и 27. Дешифратор 30 еще обладает способностью

выдавать выходной сигнал SX при обнаружении в регистре 29 команд кода операции Запись.

Схемы 23 и 24 фиксации вырабатывают сигналы управления адресом, а

микропроцессор снабжен схемами выбора участка памяти, соединенными с подсистемой основной памяти 18 и

реагирующими на эти сигналы управления адресом, определяя конкретный

участок памяти или страницу памяти, к которой производится обращение. Эти

схемы выбора участка памяти содержит дешифратор 19, расшифровывающий двухразрядньм

код с выходных шин двух схем фиксации и возбуждающий одну из четырех выходных шин выбора стравицы

памяти. Эти выходные шины выбора страницы от дешифратора 19 ведут

к различным участкам страниц в основной памяти 18 и выбирают их.Так как

в любой момент времени может быть возбуждена только одна пшна выбора

страницы, то в момент времени может быть произведено обращение только

к одному из четырех возможных участков памяти. Другими словами, адрес

памяти в регистре 25 действителен только для конкретной страницы памяти

, которой соответствует возбужденная шина выбора страницы. Так, например, если на выходах схем 23 24фиксации присутствует двухразрядный код 00, то возбуждается

шина. Выбор первой страницы и адрес из. регистра (SAR) 25 передаютс в адресные цепи первой страницы.

Если же на выходах схем 23 и 24 фи сации присутствует код 01, то возбузсдается шина. Выбор второй

страницы и адрес из регистра (SAR 25передаются в адресные цепи второй страницы. Аналогичные рассужде

ния можно произвести для третьей и четвертой страниц. Если при выполнении какой-либо

программы необходимо использовать различные страницы памяти, в соответствующие точки этой программы

нужно просто ввести команды Запис причем разряды А, В, W и X в этих командах должны иметь соответствую

щий код для выбора н окной страницы памяти. При использовании команды Запись исключительно для выбора

страниц памяти-эту команду более правильно было бы назвать Выбор страницы памяти.

Способность адресации основной памяти микропроцессора может быть еще увелр чена путем использования

не двух схем фиксации (фиг.4), а трех или четырех. Использование

трех схем фиксации позволяет осуществлять выбор свыше восьми страниц основной памяти, а использование

четырех схем фиксации позволяет осуществлять выбор свыше шест надцати страниц основной памяти о Пр

этом третья и четвертая схемы фиксации и связанные с ними элементы включаются так, как это показано

на фиг.1, причем выходы всех трех или четырех схем фиксации ведут к увеличенному дешифратору 19, который

может расшифровывать трехили четырехразрядньй код и снабжен соответственно, 8 или 16 шинами вы

бора страницы. Преимущество осуществления записи в схемы фиксации в конце машинного

цикла или вблизи конца этого цикла, в течение которого к манда Запись находится в регистр

команд, состоит в следующем. Рассмотрим схему, представленну на фиг.45 где запись в одну.или в

обе схемы 23 и 24 фиксации управляется тактовым импульсом Т11, пос тупающим на вход 31 синхронизации и на третьи входы элементов И 26 и 27, причем предполагается, что

этот тактовьш импульс Т11 является последним тактовым импульсом в машинном цикле для команды Запись,

Цель, которую преследуют, используя для установки схем фиксации сигналов управления тактовый импульс,

появляющийся в конце или близко к концу машинного цикла, заключается

в том, чтобы сделать возможным завершение еще одного цикла запоминания , в течение которого в регистр

29 команд может быть записана команда перехода, что обеспечит адрес

перехода для регистра 25 адреса памяти до изменения состояния схем фиксации. Это дает возможность не

только изменить страницу, но одновременно изменить адрес в этой

странице, т.е. оба изменения происходят одновременно при одном и том же обращении к памяти, даже если

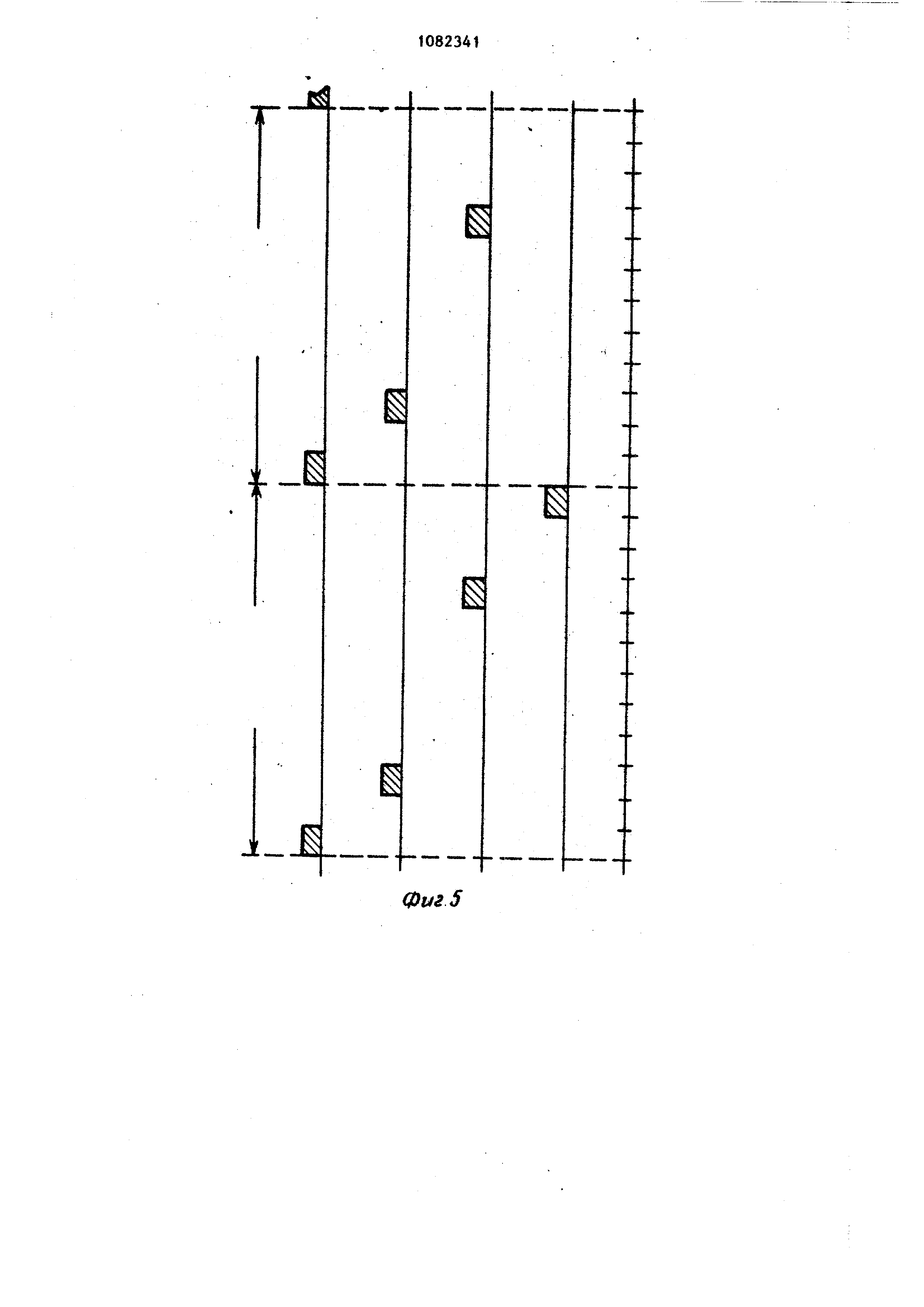

они задаются двумя последовательными командами. Рассмотрим временную диаграмму

(фиг.5)з где цикл представляет собой машинный цикл, в течение которого в регистре 29 команд находится

команда Запись, а цикл N+1 изображает следующий цикл, в течение

которого в регистре 29 команд находится команда перехода. Команда Запись (Выбор страницы памяти)

записывается в регистр 29 команд импульсом записи IR (регистр команд ) цикла N в течениевременного

интервала ТО, Содержимое регистра (IAR) 21 записывается в регистр 25 адреса памяти импульсом

записи SAR цикла N в течение интервала Т2, при этом предполагается,

что дешифратор 30 выдает соответствующий вькодной сигнал для возбуждения

управляющей логической схемы, представленной элементом И 22. Этот адрес в регистре (IAR) 21 является

адресом следующей команды, которая, в данном случае, представляет собой

команду перехода цикла N+1. По импульсу выбора памяти цикла N адрес из регистра (SAR) 25 передается

в адресные цепи основной памяти 18 и вскоре адресованная команда появляется на выходе основной памяти

18. Таким образом, следующая команда (которая должна выполняться в

цикле N+1) выбирается заранее, во время выполнения текущей команды в

цикле N.

Только после перенесения выборки следующей команды в точку, где

на нее не может быть оказано влияние , может быть произведена запись

в одну или в обе схемы 23 и 24 фиксации . Это осуществляется по импульсу записи в схемы фиксации цикла

N в течение интервала Т11, расположенного в самом конце цикла N. Поэтому результат изменения состояния

схем фиксации не оказывает влияния в течение некоторого времени до определенной более поздней точки

в следующем машинном цикле. Так, команду перехода для цикла N+1 получают из той же самой страницы памяти

, из которой бьша получена команда Запись для цикла N.

Команда перехода по импульсу записи 1R цикла N+1 записывается в регистр 29 команд в течение времени

ТО цикла N+1. Дешифратор 30 идентифицирует команду перехода и возбуждает

выходную шину Переход, одновременно прекращая возбуждение на щине Перехода нет. В результате

возбуждается логическая управляющая схема - элемент И 28, которая позволяет

адресу перехода, содержащемуся в команде перехода, поступить на вход регистра 25 адреса памяти. По

импульсу записи SAR цикла N+1 этот адрес перехода записывается в регистр (SAR) 25 в течение интервала

Т2. Затем адрес перехода передается в адресные цепи основной памяти 18 в течение интервала времени-

Т8 по импульсу выбора памяти цикла N+1. Однако к этому моменту времени уже произошла новая установка

состояния схем 23 к 24 фиксации , и поэтому адрес перехода передается в адресные цепи новой выбранной

страницы основной памяти 18.Таким образом, не только изменяется страница памяти, но, если желательно

, изменяется также адрес байта в этой новой странице, причем оба эти изменения происходят одновременно,

а именно, во время данного обращени к памяти в промежутке времени Т8 ма

шинного цикла N+1, А команда, которая будет выполняться в машинном цикле N+2 (не показано), выбирается

из вновь выбранной страницы памяти заранее, в течение цикла N+1.

Рассмотрим еще один вариант реализации изобретения (фиг.6),в котором работу шести блоков 44-49 можно

запрограммировать путем ввода соответствующих команд Запись в регистр 34 команд. В этом случае

используются команды Запись с двумя различными кодами операции. Один из этих кодов операции обозначает

команду Запись в первую группу и при его обнаружении в дешифраторе 35 вырабатывается сигнал

дешифратора на выходной шине -дешифратора SXL. Второй из этих двух .

специальных кодов операции обозначает команду Запись во вторую

группу и при его обнаружении в дешифраторе 35 вырабатывается сигнал

дешифратора на выходной шине дешифратора SXH. Блоки 44-49 разбиты на две перекрывающиеся группы. В

первую группу входят блоки 44-47, а во вторую - блоки 46-49. Выходной

сигнал дешифратора, соответствующий коду операции SXL, подается на вторые входы элементов И 37-40, на

два последних элемента И 39 и 40 через элемент ИЛИ 43 в блоке 36 для осуществления записи в один или

несколько блоков 44-47 первой группы , в соответствии с двоичными величинами

, записанными в разрядах, А, В, С и D команды.. Аналогично

выходной сигнал дешифратора, соответствующий коду операции SHX, подается на вторую группу элементов И

39-42 (на два первых элемента И через элемент ИЛИ 43) в блоке 36 для осуществления записи в один или

несколько блоков 46-49 второй группы, как и ранее, в соответствии с двоичными величинами, записанными

в разрядах А, В, С и D команды. Конкретная двоичная величина, записываемая

в любой данный блок, определяется двоичной величиной в-конкретном одном разряде W, X, Y, Z

регистра команд, с которым соединен вход данных этого блока. Синхронизация процесса записи во все эти

блоки производится тактовым импульсом Т11, который поступает на все

шесть элементов И 37-42 по тактовому входу 50.

В данном примере блоки 44 и 45 используются для выбора страницы 13 основной памяти. Для этого их выходы соединены с дешифратором 51,

от которого четыре выходных шины выбора страницы ведут в подсистему основной памяти, например подсистему

основной памяти 18. Блоки 46 и 47 в данном примере используются для выбора страницы

местной памяти. Для этого выходы этих блоков соединены с дешифратором 52, а четыре выходные шины выбора

страницы от дешифратора 52 ведут к адресным схемам блока местной памяти. В этом случае объем

местной памяти увеличится в четьфе раза по сравнению с первоначальным

Первоначальный объем может соответствовать , например 32 независимо адресуемым рабочим регистрам, при

этом такую группу из 32 регистров можно считать страницей местной памяти. В примере, изображенном

на фиг.6, могут быть получены четыре таких страницы, причем используемая в данный момент времени страни

ца определяется двоичными величинами в блоках 46 и 47. Такая постра ничная структура местной памяти дает

возможность выделять для различных операций микропроцессора различные страницы местной памяти,что

в конечном счете приводит к уменьше нию суммарного времени обработки ин формации.

Блоки 48 и 49 (фиг.6) используют ся рдя выдачи сигналов управления для непосредственного управления

114 одним или несколькими внешними устройствами

, которые могут быть соединены с 1« кропроцессором или связаны с его работой. Блоки 48 и 49 могут

быть использованы для управления выбором внутренних функций процессора. В примере, изображенном на

фиг.6, команда Запись с кодом операции SXL используется для изменения страницы основной памяти, или

страницы местной памяти, или той и другой одновременно. Команда Запись с кодом операции SXH используется

для изменения страницы местной памяти, или управляющих сигналов на внешние устройства,

или того и другого одновременно. Это показывает гибкость и многогранность предлагаемого устройства

управления. Предлагаемое устройство управления позволяет расширить диапазон

адресации памяти микропроцессора по сравнению со случаем адресации путем использования адреса памяти

в командах программы, т.е. длины адреса (числа его двоичных разрядов),

используемой в различных командах программы, содержащих поле адреса

памяти. С помощью такого устройства диапазон адресации памяти может быть увеличен в 2,4,8 или 16 раз

при минимальном количестве дололнительных схем и малом влиянии на характеристики микропроцессора

.

10

ф1/г.2

фуг 5

Комментарии