Изобретение относится к устройствам для преобразования виртуального адреса в реальный адрес.

Под виртуальным адресом подразумевается адрес, который содержится

в команде программы и который следует видоизменить для получения доступа к информации, выраженной

словом в центральной памяти, в то время как при использовании реального

адреса обеспечивается непосредственный доступ.

Под центральной памятью подразумевается запо шнающее устройство, в

котором в отличие or вспомогательной памяти содержится информаш1я, к

которой имеется непосредственный доступ от центрального блока вычислтельного

устройства.

Известно устройство для динамического

преобразования адресов, содержащее три регистра, четьфе блока памяти, три схемы сравнения, коммутатор

, генератор, блок управления, элементы И, ИЛИ 0.

Недостаток устройства - низкое

быстродействие.

Наиболее близким к изобретению является устройство преобразования

виртуального адреса в реальный адрес для системы обработки данных в реальном времени, в котором

программы распределены по пронумерованным функциональным группам,причем каждая функциональная группа

в свою очередь разделена на сегменты , определяемые таким же количеством дескрипторов 2j

Метод разделения программы на сегменты или сегментации позволяет

уменьшить габариты центральной памяти, производя загрузку в заданный момент лишь сегмента центральной

памяти, программу которого необходимо использовать в заданньй момент .

В известном устройстве преобразования используется регистр номера функциональной группы, таблица

дескрипторов сегментов, локализованная в центральной памяти системы

обработки данных, и регистры, называемые базовыми, каждый из которых предназначен дпя хранения

дескриптора сегментов, причем система названных регистров служит для хранения дескрипторов сегментов,

необходимых для функциональной группыс

Недостаток данного устройства

обусловлен относительно высоким временем вьтолнения операции.

Цель изобретения - повышение быстродействия .

Поставленная цель достигается

тем, .что устройство для преобразования виртуального адреса в реальный адрес, содержащее центральную

память, узел базовых регистров и сумматор, регистр виртугСпьного адреса , регистр номера функционального

бпока, регистр адреса информации , регистр команд,регистр данных,

два дешифратора команд и линию задержки вход которой соединен с

выходом первого деимфратора команд, группа входов которого соединена с

группой выходов регистра команд и с группой входов второго дешиф{эатора

5 команд, первая группа входов сумматора соединена с группой выходов

узла базовых регистров, вторая группа входов сумматора соединена с первой группой вь1ходов регистра вирO

туального адреса, группа адресных входов узла базовых регистров соединена

с второй группой выходов регистра виртуального адреса, содержит . блок формирования сигнала подтвержв

дения, регистр предварительного

адреса, две группы элементов И,группу

элементов НЕ и блок управления . доступом, содержащим две линии задержки

, два элемента НЕ, два триггера , два элемента ИЛИ, четыре элемента И, мультиплексор, причем группа

адресных входов блока формирования сигнала подверждения соединена с

второй группой выходов регистра вИр5 туального адреса, вход форсирования

блока формирования сигнала подтверждения соединен с выходом второго

дешифратора, управляюп91й вход блока формирования сигнала подтверждения

соединен с выходом первого элемента И блока управления доступом,вход

первого элемента НЕ которого соединен с выходом блока формирования

сигнала подтверждения, первая группа входов данных мультиплексора блока управления доступом соединена

с группой выходов сумматора, вторая группа входов данных сумматора блока

управления доступом соединена с группой выходов регистра предварительного

адреса, группа выходов данных мультиплексора блока управления доступом соединена с группой адресных

входов центральной памяти, вход первой линии задержки блока управления доступом соединен с выходом

первого дешифратора, вход второй линии задержки блока управления доступом

соединен с первым входом второго элемента И блока управления доступом

и с выходом лигши задержки, выходы третьего элемента И и первого триггера блока управления доступом

соединены соответственно с управляющими входами узла базовых регистров

и центральной памяти выход второго элемента И блока управления доступом

соединен с первыми входами элементов И первой группы и через элементы НЕ группы - с первыми входами элментов И второй группы, первая, вторая и третья группы входов регистра

предварительного адреса соединены соответственно с группами выходов регистра адреса информации, регистр

номера функционального блока и второй группой выходов регистра виртуального адреса, вторые входы элементов

И первой и второй групп соединены с соответствующими выходами центральной памяти, выходы элементов

И первой группы соединены с соответствующими входами регистра дан ньпс, выходы элементов И второй группы

соединены с соответствующими входами данных узла базовых регистров, вход логической единицы блока

формирования сигнала подтверждения соединен с входом логической единицы устройстваj а в блоке управления

доступом выход первого эле- мента НЕ соединен с 3 -входом второго триггера, тактовый вход которого

соединен с первым входом первой линии задержки, второй и третий выходы которой соединены соответственно

с первыми входами первого элемента ИЛИ и четвертого элемента И, выход второго триггера

соединен с вторым входом четвертого элемента И, первыми входами первого и третьего элементов И, второго

элемента 1-1ЛИ и через второй элемент НЕ - с вторым входом второго элемента И, первый выход второй

линии задержки соединен с вторым входом первого элемента И, второй выход второй линии задержки соединен

с входом форсирования второго триггера, вторыми входами второго элемента ИЛИ и первого элемен- ,

та И, третий вьпсод второй линии задержки соединен с вторым входом первого элемента ИЛИ, выходы первого

и второго элементов ИЛИ сое|динены соответственно с тактовым входом и входом форсирования первого

триггера, выход четвертого элемента И сс5единен с управляющим входом мультиплексора,К -вход второго

триггера и D -вход первого триггера соединены соответственно с входами логического нуля и логической

едини1№1 устройства.

Кроме того, блок формирования

сигнала подтверждения содержит дешифратор , rpyitny элементов И, группу триггеров и мультиплексор,причем группа адресных входов блока соединена с группой входов дешифратора

и группой управляющих входов мультиплексора, выход которого является выходом блока, выходы триггеров

группы соединены с соответствующими информа1щонными вxoдa м мультиплексора, выходы элементов И

группы соединены с тактовыми входами триггеров группы, входы форсирования

которых соединены с входом форсиропаиия блока, управляющий вход jcoToporo соединен с первыми

5 входами элементов И группы, вторые входы которых соединены с соответствующими

выходами дешифратора,вход логической единицы блока соединен с входом дешифратора и D -входами

O триггеров группы.

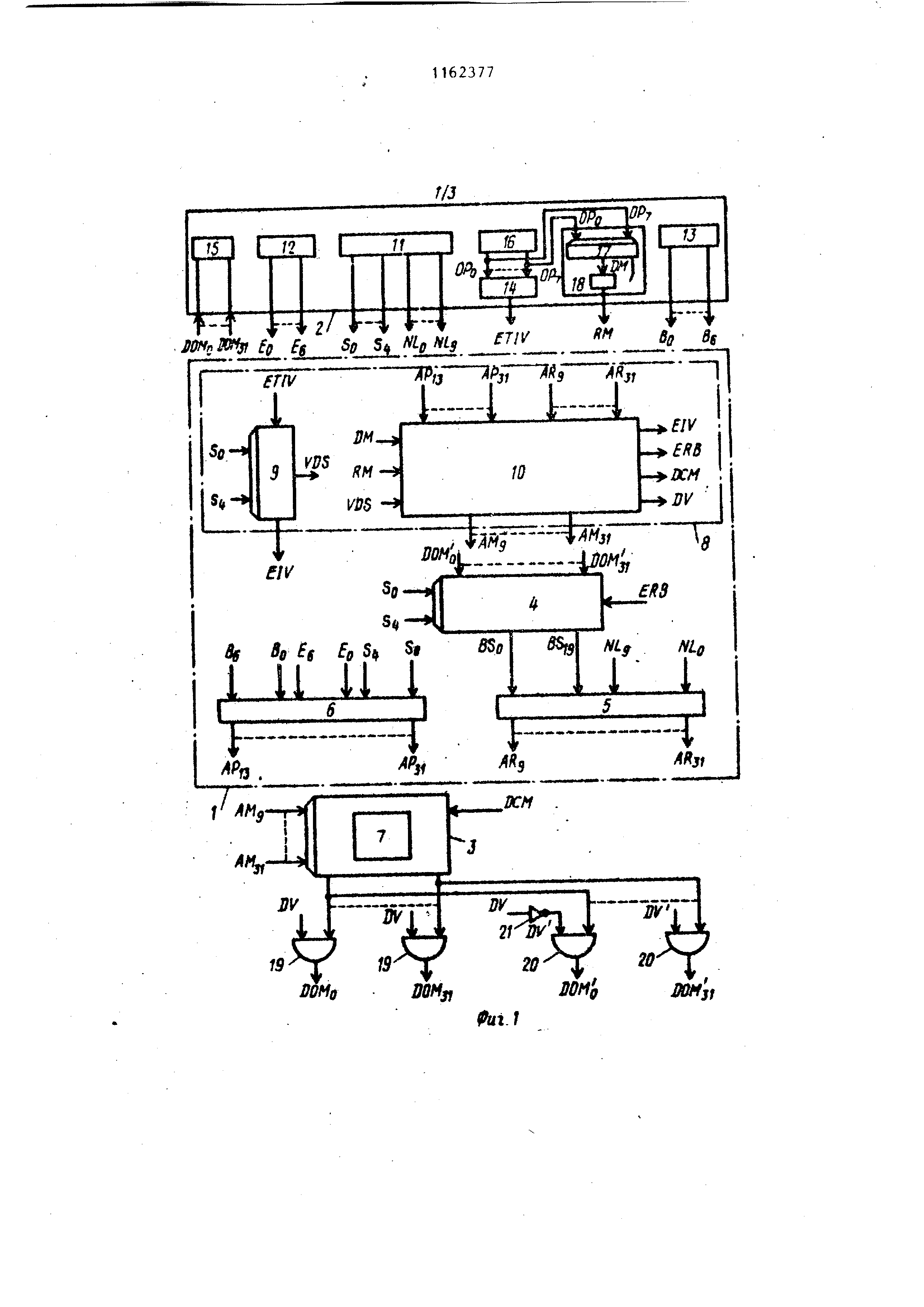

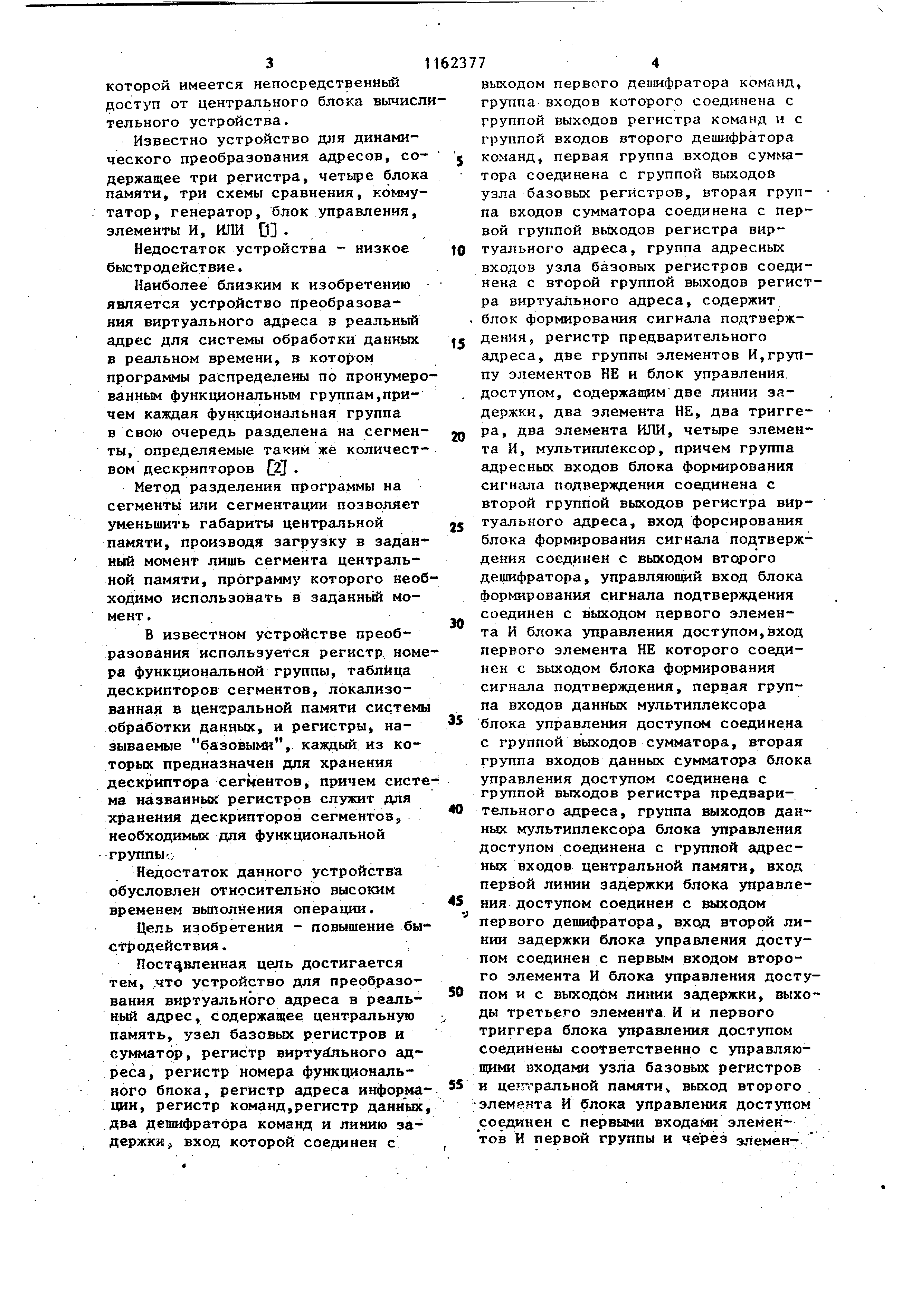

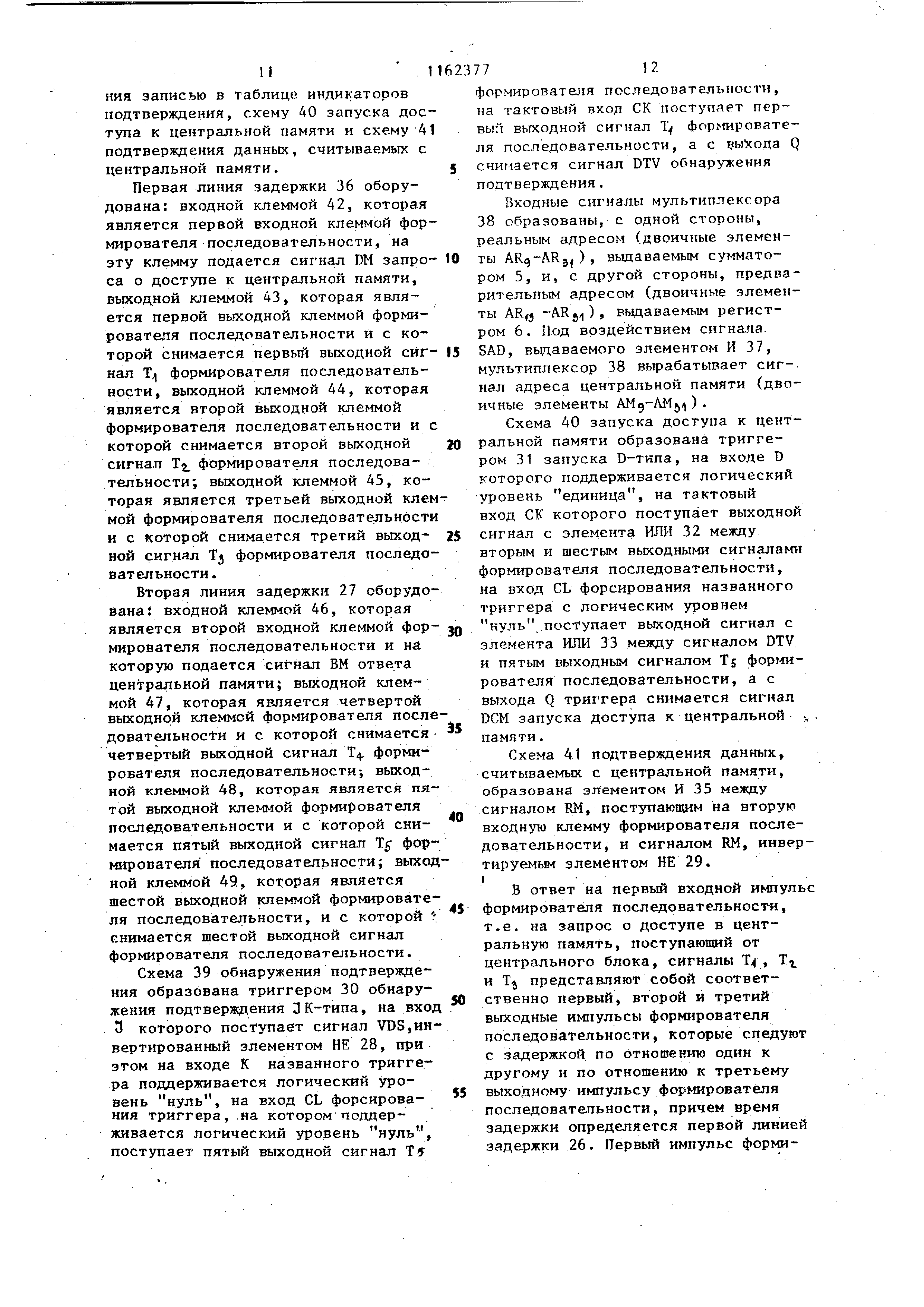

На фиг.1 представлена блок-схема

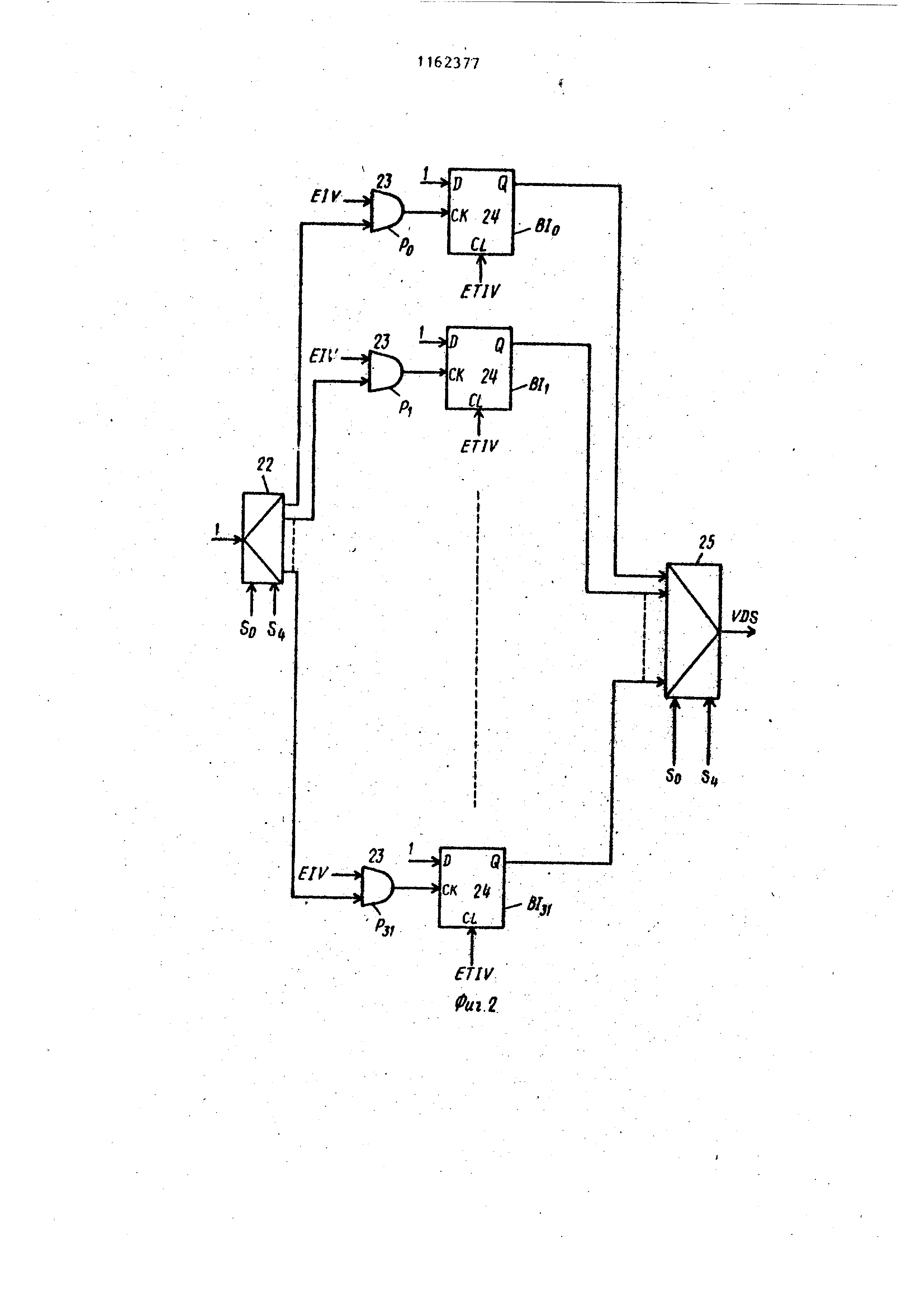

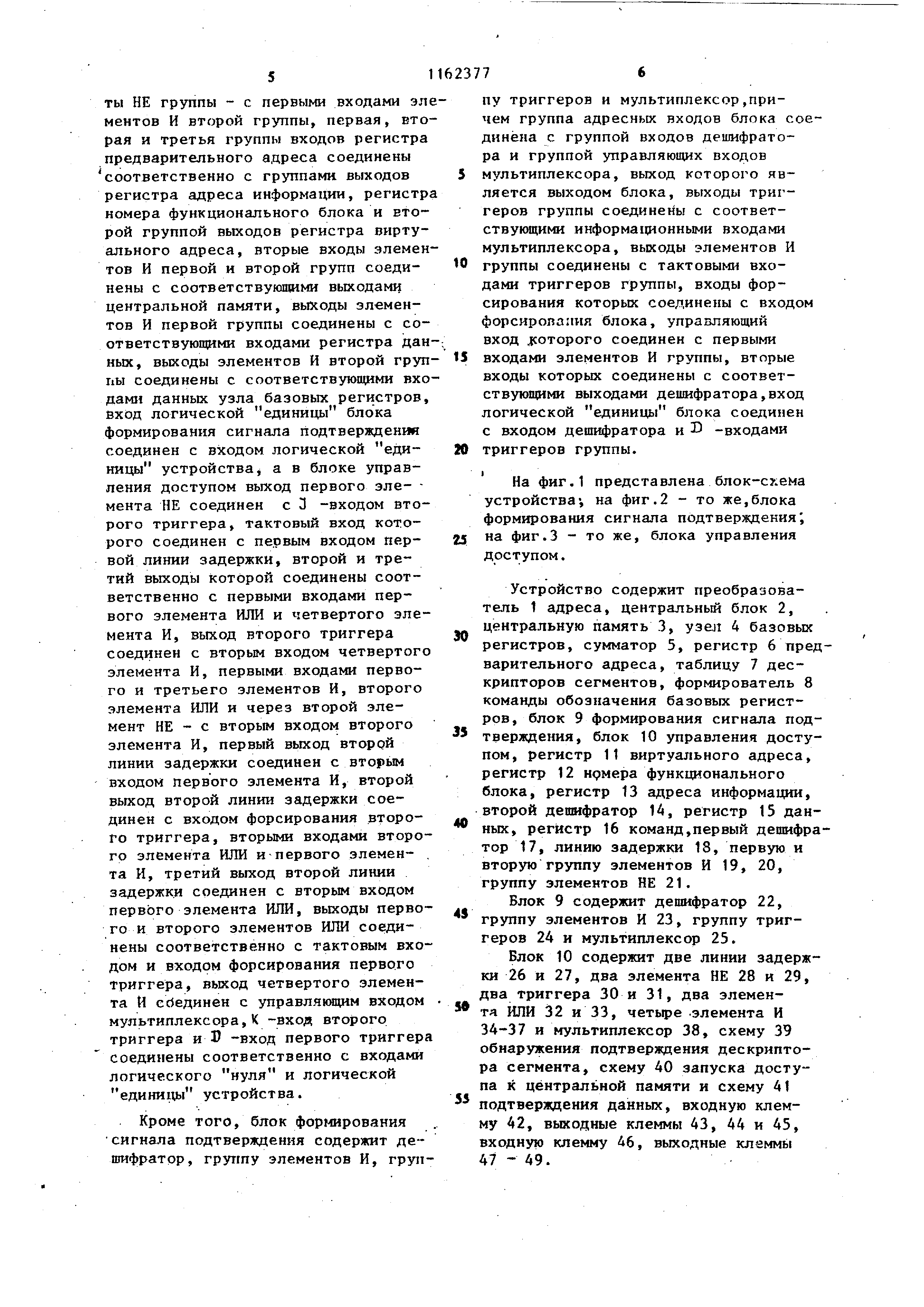

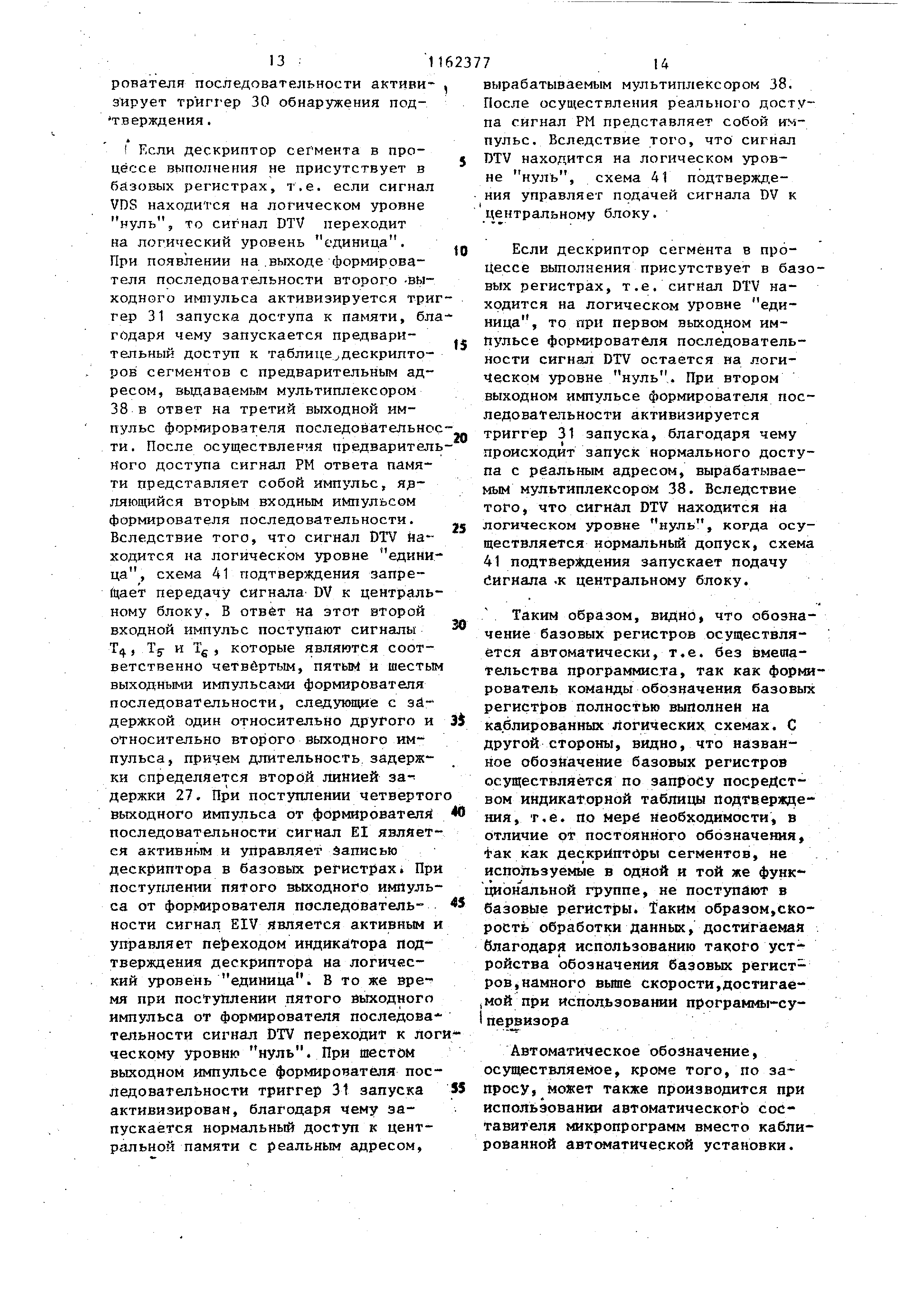

устройства-, на фиг.2 - то же,блока формирования сигнала подтверждения;

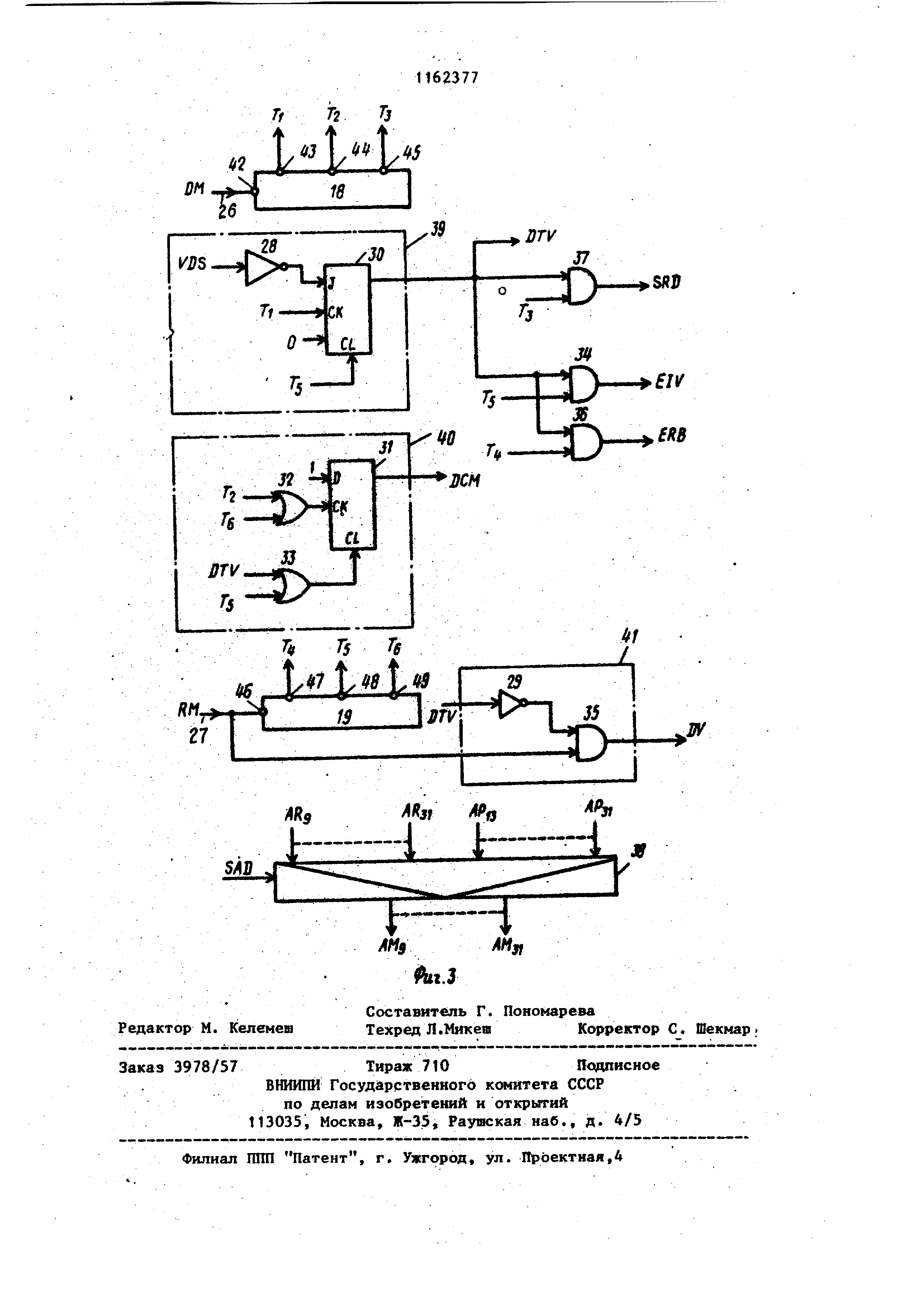

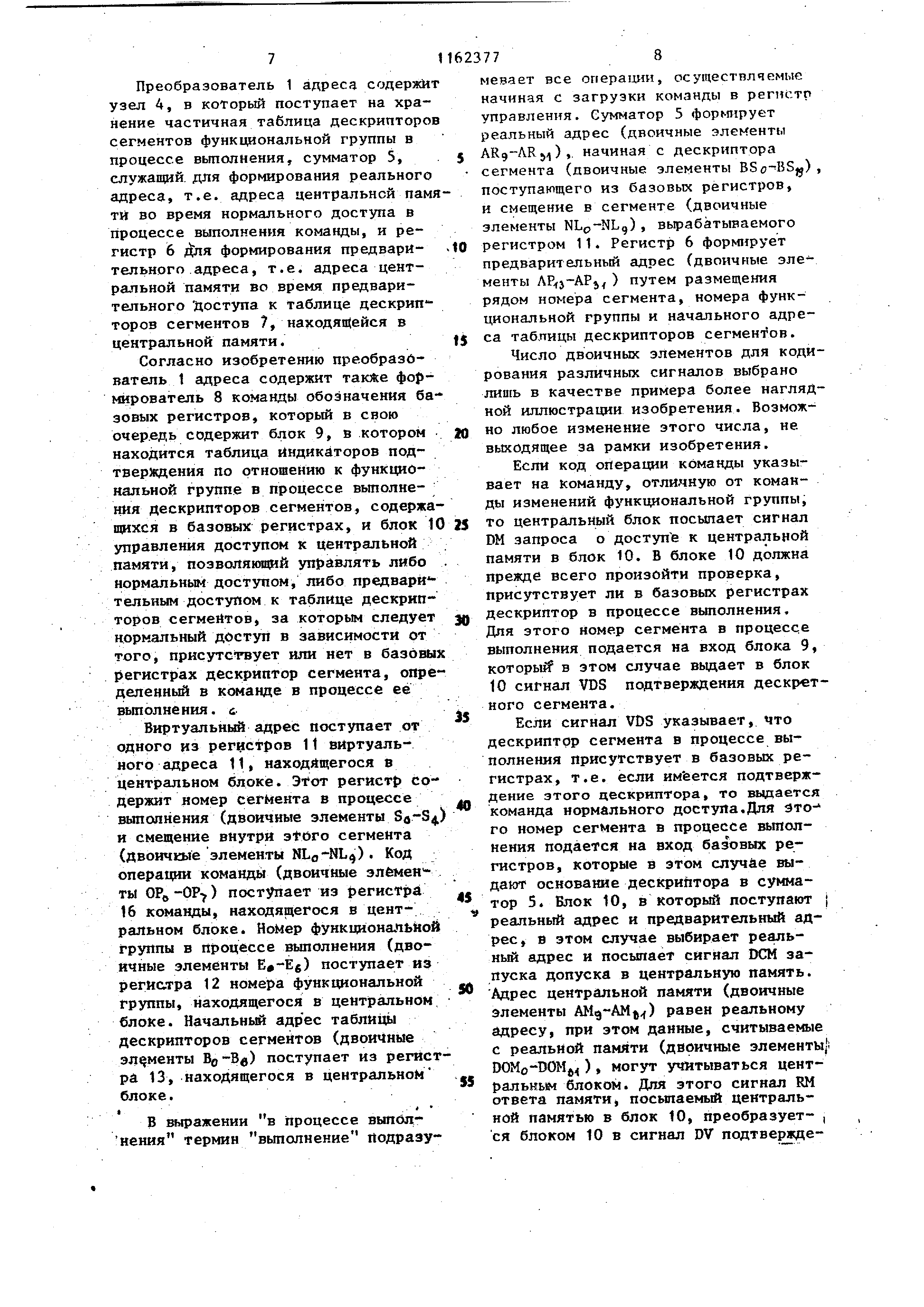

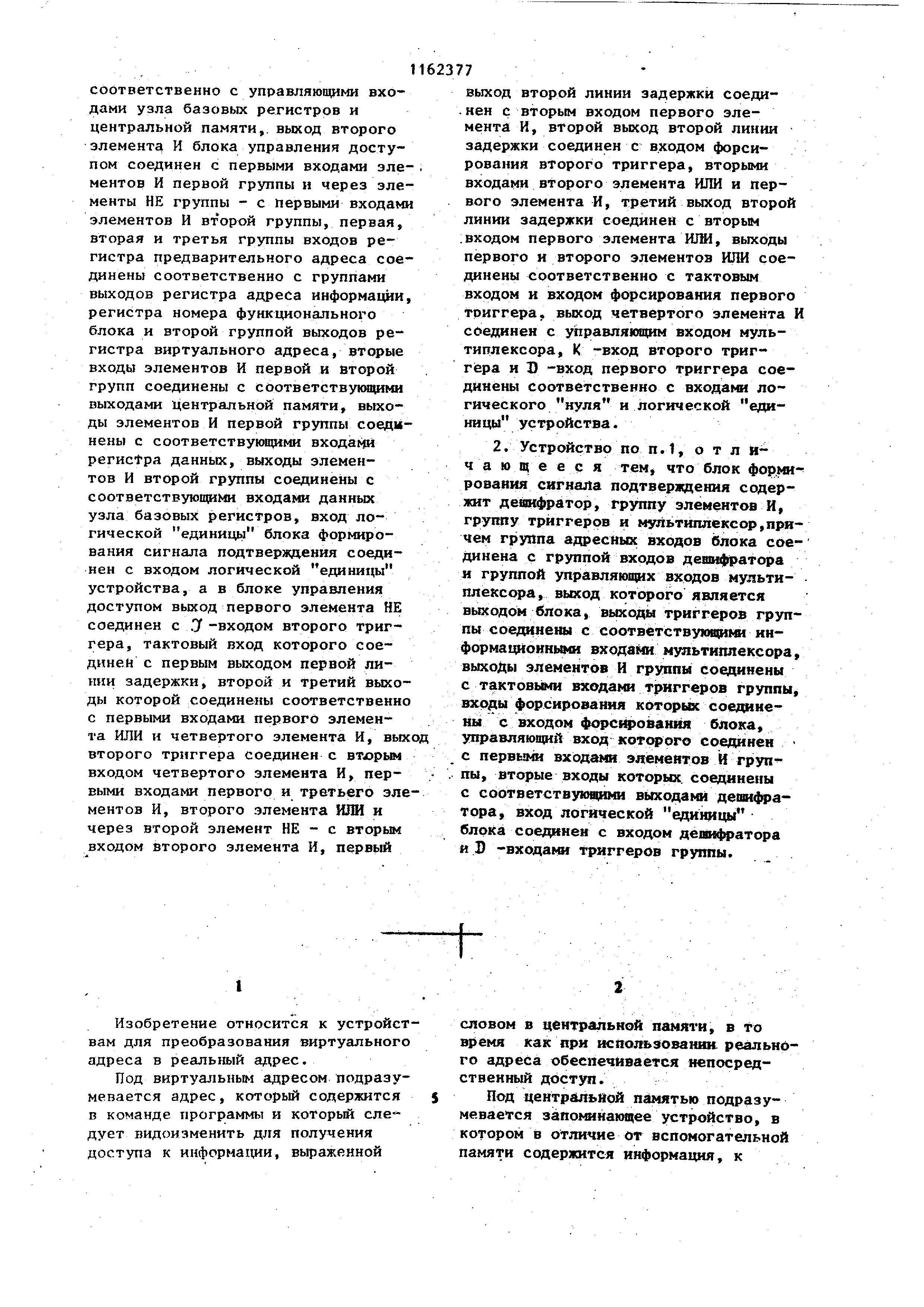

5 на фиг.З - то же, блока управления доступом.

Устройство содержит преобразователь 1 адреса, центральньй блок 2,

центральную память .3, узел 4 базовых регистров, сумматор 5, регистр 6 предварительного

адреса, таблицу 7 дескрипторов сегментов, формирователь 8 команды обозначения базовых регистров

, блок 9 формирования сигнала под тэерждения, блок 10 управления доступом

, регистр 11 виртуального адреса, регистр 12 нрмера функционального

блока, регистр 13 адреса информации, второй дешифратор 14, регистр 15 данных

, регистр 16 команд,первый дешифратор 17, линию задержки 18, первую и

вторую группу элементов И 19, 20, группу элементов НЕ 21.

Блок 9 содержит дешифратор 22, группу элементов И 23, группу триггеров 24 и мультиплексор 25.

Блок 10 содержит две линии задержки 26 и 27, два элемента НЕ 28 и 29,

два триггера 30 и 31, два элемента ИЛИ 32 и 33, четыре -элемента И 34-37 и мультиплексор 38, схему 39

обнаружения подтверждения дескриптора сегмента, схему 40 запуска доступа

к центральной памяти и схему 41

подтверждения данных, входную клемму

42, выходные клеммы 43, 44 и 45, входную клемму 46, выходные клеммы 47-49.

Преобразователь 1 адреса содержит узел 4, в который поступает на хранение

частичная таблица дескрипторов сегментов функциональной группы в процессе вьшолнения, сумматор 5,

служащий для формирования реального адреса, т.е. адреса центральной памя тй во время нормального доступа в

процессе выполнения команды, и регистр 6 Для формирования предварительного адреса, т.е. адреса центральной

памяти во время предварительного Доступа к таблице дескрипторов сегментов 7, находя11(ейся в

центральной памяти.

Согласно изобретению преобразбватель

1 адреса содержит также ормирователь 8 команды обозначения базовых регистров, который в свою

очер.едь содеряит блок 9, в котором находится таблица индикаторов подтверждения

по отношению к функциональной группе в процессе вьтолнения дескрипторов сегментов, содержащихся

в базовых регистрах, и блок 10 управления доступом к центральной памяти, позволяющий управлять либо

нормальным доступом, либо предвари тельным доступом к таблице дескрипторов сегмейтов, за которым следует

нормальный доступ в зависимости от того, присутсгвует или нет в базовых

регистрах дескриптор сегмента, определенный в команде в процессе её выполнения, с

Виртуальный адрес поступает от одного из регистров 11 виртуального адреса 11, находйщегося в

центральном блоке. Этот регист{) содержит номер сегмента в процессе выполнения (двоичные элементы Sa-S.)

и смещение внутри сегмента (двоичкыеэлементы NLo-NL) . Код операции команды (двоичные элёменты

ОР -Off ) поступает из регистра 16 команды, находящегося в центральном блоке. Номер функциональной

группы в процессе выполнения (двоичные элементы E#-Eg) поступает из регистра 12 номера функциональной

группы, находящегося в цент ральном блоке. Начальный адрес таблицы дескрипторов сегмейтов (двоичные

элементы BO-Bfl) поступает из регистра 13, находящегося в центральном блоке.

В выражении в процессе выполнения термин выполнение нодразумевает все операщш, осуществляемые начиная с загрузки команды в регистр управления. Сумматор 5 фор№1рует

реальный адрес (двоичные элементы ARg-ARj;,),. начиная с дескриптора

сегмента (двоичные элементы BSo-BSjj) поступающего из базовых регистров, и смещение в сегменте (двоичные

элементы NLp-NLg), вырабатываемого регистром 11. Регистр 6 формирует

предварительный адрес (двоичные элементы AF j-APj ) путем размещения

рядом номера сегмента, номера функциональной группы и начального адреса таблицы дескрипторов сегментов.

Число двоичных элементов для кодирования различных сигналов выбрано

лишь в качестве примера более наглядной иллюстрации изобретения. Возможно

любое изменение этого числа, не выходящее за рамки изобретения.

Если код операции команды указывает на команду, отли-чную от команды изменений функциональной группы,

то центральный блок посыпает сигнал DM запроса о доступов к центральной

памяти в блок 10. В блоке 10 должна прежде всего произойти проверка,

присутствует ли в базовых регистрах дескриптор в процессе выполнения.

Для зтого номер сегмента в процессе выполнения подается на вход блока 9,

KOTopbtff в этом случае вьщает в блок 10 сигнал VDS подтверждения дескр«тного сегмента.

Если сигнал VDS указывает, что дескриптор сегмента в процессе выполнения

присутствует в базовых регистрах , т.е. если имеется подтверждение этого дескриптора, то выдается

команда нормального доступа.Для этого номер сегмента в процессе вьшолнения

подается на вход базовых регистров , которые в этом случае выдают основание дескриптора в сумматор

5. Блок 10, в который поступают реальный адрес и предварительный адрес

, в этом случае выбирает реальный адрес и посыпает сигнал DCM запуска допуска в центральную память.

Адрес центральной памяти (двоичные элементы ) равен реальному адресу, при этом данные, считываемые

с реальной памяти (двоичные элементы DOMo-BOMj), могут учитываться центральньм

блоком. Для этого сигнал ЕМ ответа памяти посыпаемый центральной памятью в блок 10, преобразуется

блоком 10 в сигнал DV подтверждения данных, поступающих в центральный

блок,

И наоборот, если сигнал VDS указывает , что дескриптор сегмента в процессе

выполнения не присутствует в базовых регистрах, то подается команда предваритепьного доступа к

таблице дескрипторов сегментов. Для этого блок 10 выбирает предварительный адрес и посылает в центральную

память сигнал DCM запуска доступа в центральную память. Адрес центральной памяти равен предварительному

адресу, и блок 10 : апре1дает подачу сигнала DV к центральному блоку и управляет записями данных

DOMo-DOMjf в базовые регистры путем подачи в базовые регистры сигнала ERB управления записью в базовых

регистрах. Затем блок 10 посыпает в блок 9 сигнал EIV управления записью

в таблице индикаторов подтверждения . Названный сигнал предназначен для изменения состояния индикатора

подтверждения дескриптора сегмента в процессе выполнения. В этом случае может осуществляться

управление реальиым доступом, и оператдия происходит так же, как уже описано.

Если код операш-ш команды указывает на одну из команд изменения функциональной группы, то дешифратор

кода операции вызывает изменение состояния системы индикаторов подтверждения блока 9 посредством

сигнала ETIV, при этом меняете содержание регистра 12 номера функциональной группы.

Согласно фиг.1 номер сегмента кодируется при помощи пяти двоичных

элементов (So-S4). В этом случае ма ссимальное число п сегментов функциональной

группы равно 32, а таблица индикаторов подтверждения (фиг.2) содержит 32 индикаторных

триггера D-типа,

Схема считывания с таблицы индикаторов

подтверждения образована мультиплексором 25 считывания, имеющим 32 входа, соединенных с выходами

О индикаторных триггеров,причем названный мультиплексор управляется номером сегмента в процессе

.вьтолнения (двоичные элементы . ; SB-5ф). Выходной сигнал VDS мультиплексора

25 равен сигналу, выдаваемому тем индикаторным триггером,номер которого совпадает с номером сегмента.

Fia входах 1) индикаторных триггеров

30 поддерживается логический 5 уровень единица.

Схема записи индикаторных триггеров образована группой из 32-х элементов И причем один

вход каждого из этих элементов питается сигналом EIV управления записью

в таблице индикаторов подтверждения, а выход соединён с входом СК тактового

устройства одного из индикаторных триггеров. На одной входе дешиф5 . ратора 22 поддерживается логический

уровень единица, причем названный дешифратор управляется двоичными

элементами So+S.. На вход CL форсирования 32-х индикаторных триггеров

0 с логическим уровнем нуль поступает сигнал ETIV с выхода дешифратора 14.

При получении запроса о доступе сигнала DM к центральной памяти

блок 10 проверяет сигнал VDS. Если сигнал VDS имеет логический уровень

единица, это означает, что в базовых регистрах присутствует дескриптор

сегмента в процессе вьтолнения,

и этом случае может осуществляться

нормальный доступ. Если сигнал VDS имеет логический уровень нуль, то

блок 10 подает команду о предварительном доступе к таблице дескрипторов сегментов ив случае, если

дескриптор присутствует в базовых регистрах, посыпает сигнал EIV с логическим

уровнем единица в таблицу индикаторов подтверждения. В этом случае названньй сигнал EIV,

воздействуя совместно с дешифратором 22; позволяет активизировать тот

индикаторный триггер, номер которого соответствует номеру сегмента

в процессе вьтолнения, т.е. выход О

этого триггера переходит на логический

уройень единица.

Из фиг.З видно, что блок управления

доступом содержит мультиплексор 38 адресации центральной памяти, формирователь последовательности,

образованный первой линией задержки 26 и второй линией задержки 27, схему

39 обнаружения подтверждения дескриптора сегмента, элемент И 37

управления мультиплексором 38, элемент И 36 управления записью в базовых

регистрах, элемент И 34 управлеи ния записью в таблице индикаторов подтверждения, схему 40 запуска дос тупа к центральной памяти и схему 4

подтверждения данных, считываемых с центральной памяти. Первая линия задержки 36 оборудована;

входной клеммой 42, которая является первой входной клеммой фор мирователя последовательности, на

эту клемму подается сигнал DM запро са о доступе к центральной памяти,

выходной клеммой 43, которая является первой выходной клеммой формирователя последовательности и с которой

снимается первый выходной сиг нал Т,| формирователя последовательности , выходной клеммой 44, которая

является второй выходной формирователя последовательности и которой снимается второй выходной

сигнал Т2 формирователя последовательности; выходной клеммой 45, которая является третьей выходной кле

мой формирователя последовательност и с которой снимается третий выходной сигнал Т формирователя последо

вательности. Вторая линия задержки 27 оборудо вана входной клеммой 46, которая

является второй входной клеммой фор мирователя последовательности и на которую подается сигнал ВМ ответа

центральной памяти; выходной клеммой 47, которая является четвертой выходной клеммой формирователя посл

довательности и с. которой снимается четвертый выходной сигнал 14. формирователя

последовательности-, выходной клеммой 48, которая является пя той выходной клеммой формирователя

последовательности и с которой снимается пятый выходной сигнал Т формирователя последовательности; выход

ной клеммой 49., которая является шестой выходной клеммой формировате ля последовательности, и с которой

снимается шестой выходной сигнал формирователя последовательности. Схема 39 обнаружения подтверждения

образована триггером 30 обнаружения подтверждения ЗК-типа, на вход 3 которого поступает сигнал VDS,ин

вертированный элементом НЕ 28, при этом на входе К названного триггера поддерживается логический уровень

нуль, на вход CL форсирования триггера, .на котором поддерживается логический уровень нуль,

поступает пятый выходной сигнал Т 771. формирователя последовательности,

на тактовый вход СК поступает первый выходной сигнал Т фop п poвaтeля последовательности, а с выхода Q

снимается сигнал DTV обнаружения подтверждения, Входные сигналы мультиплексора

38 образованы, с одной стороны, реальным адресом (двоичные элементы ARij-ARj ) , вьщаваемым cyiwaToром

5, и, с другой стороны, предварительным адресом (двоичные элементы ARfj -ARj), выдаваемым регистром

6. Под воздействием сигнала. SAD, вьщаваемого элементом И 37, мультиплексор 38 вьфабатывает сигнал

адреса центральной памяти (двоичные элементы AMg-AM5). Схема 40 запуска доступа к центральной

памяти образована триггером 31 запуска D-типа, на входе D которого поддерживается логический

уровень единица, на тактовый вход СК которого поступает выходной сигнал с элемента ИЛИ 32 между

вторым и шестым выходными сигналами формирователя последовательности,

на вход C.L форсирования названного триггера с логическим уровнем нуль поступает выходной сигнал с

элемента ИЛИ 33 между сигналом DTV и пятым выходным сигналом Tj формирователя последовательности, а с

выхода Q триггера снимается сигнал DCM запуска доступа к центральной -, . памяти.

Схема 41 подтверждения данных, считываемых с центральной памяти, образована элементом И 35 между

сигналом RM, поступающим на вторую входную клемму формирователя последовательности

, и сигналом RM, инвертируемым элементом НЕ 29. I

В ответ на первый входной импульс формирователя последовательности,

т.е. на запрос о доступе в центральную память, поступающий от центрального блока, сигналы Т , Т.

и Т представляют собой соответственно первый, второй и третий выходные импульсы формирователя

последовательности, которые следуют с задержкой по отношению один к другому и по отношению к третьему

выходному импульсу формирователя последовательности, причем время задержки определяется первой линией

задержки 26. Первый импульс формирователя последовательности активизирует

триггер 30 обнаружения подтверждения . I Если дескриптор сегмента в процессе

выполнения не присутствует в бйзовых регистрах, т.е. если сигнал VDS находится на логическом уровне

нуль, то сигнал DTV переходит на логический уровень единица. При появлении на .вьгкоде ч1)ормирователя

последовательности второго -выходного импульса активизируется три гер 31 запуска доступа к памяти, бл

годаря чему запускается предварительный доступ к таблице,дескрипторов сегментов с предварительным адресом

, вьщаваемым мультиплексором 38 в ответ на третий выходной импульс формирователя последовательно

ти . После осуществления предварител ного доступа сигнал РМ ответа памяти

представляет собой импульс, ярляющийся BTOpbiM входным импульсом формирователя последовательности.

Вследствие того, что сигнал DTV йаходится на логическом уровне едини

ца, схема 41 подтверждения запрещает передачу сигнала DV к централь ному блоку, В ответ на этот второй

„ входной импульс поступают сигналы Т, Tg- и Tg , которые являются соответственно

четвёртым, пятым и шесты выходными импульсами формирователя последовательности, следующие с зйдержкой

один относительно другого и относительно второго выходного импульса , причем длительность, задержки

определяется второй линией задержка 27, При поступлении четверто выходного импульса от форьшрователй

последовательности сигнал EI являет ся активным и управляет Записью дескриптора в базовых регистрах. Пр

поступлении пятого выходного импуль са от формирователя последователькости сигнал EIV является активным

управляет пе реходом индикатора подтверждения дескриптора на логический уровень единица. В то же время

при поступлении пятого выходного импульса от формирователя последова тельности сигнал DTV переходит к ло

ческому уровню нуль. При шестом выходном импульсе формирователя пос ледовательности триггер 31 запуска

активизирован, благодаря чему запускается нормальный доступ к центральной памяти с реальным адресом,

вырабатываемым мультиплексором 38. После осуществления реального доступа

сигнал РМ представляет собой игмпульс . Вследствие того, что сигнал DTV находится на логическом уровне

нуль, схема 41 подтвержд,ения управляет подачей сигнала DV к центральному блоку.

Если дескриптор сегмента в процессе вьтолнения присутствует в базовых

регистрах, т.е. сигнал DTV находится на логическом уровне единица , то при первом выходном импульсе

формирователя последовательности сигнал DTV остается на логическом уровне нуль,. При втором

выходном импульсе формирователя последовательности активизируется триггер 31 запуска, благодаря чему

происходит запуск нормального доступа с реальным адресом, вырабатываемым

мультиплексором 38. Вследствие того, что сигнал DTV находится на

логическом уровне нуль, когда осуществляется нормальный допуск, схема

41 подтверждения запускает подачу Сигнала .к центральному блоку.

Таким образом, видно, что обозначение базовых регистров осуществляется

автоматически, т.е. без вмешательства программиста, так как формирователь команды обозначения базовых

регистров полностью выполнен на каблированных логических схемах. С

другой стороны, видно, что названное обозначение базовых регистров

осуществляется по запросу посредством индикаторной таблицы подтверзвдения

, т,е. по мере необходимости, в отличие от постоянного обозначения, taK как дескрипторы сегментов, не

используемь е в одной и той же функ циональной группе, не поступают в

базовые регистры. Таким образом,скорость обработки данных, достиг;аемая

благодаря использованию такого устройства обозначения базовых регистров

,намного выше скорости,достигавмой при Использовании программы-суперщизора Автоматическое обозначение, осуществляемое, кроме того, по запросу , может также производится при

использовании автоматического составителя микропрограмм вместо каблированной

автоматической установки.

ES So S NLp Щ BO Bf

EQ

..

Ii--l iI

SM

SoVV3

t: VDS

t

fH

Sf

1

j

sijMjjjtoMff

eiv

KB I

Ш

DV

„nuM d

v

° --JDOM

V

nnuf«.

-awj,

i. 1

23

f/K

23

eiV

PI

22 Л

Д Q C/f V

Bio

a

Г

fnv

D Q CK 2if

-Bit

25

TT

S0 5

23

P

31

VD

5o S

D Q

CK 2if

a

eriv

Фиг.г

Комментарии