Установка, способ и система кэширования - RU2483347C2

Код документа: RU2483347C2

Чертежи

Описание

ПРЕДПОСЫЛКИ СОЗДАНИЯ ИЗОБРЕТЕНИЯ

Настоящее раскрытие в целом относится к области электроники. Более конкретно пример воплощения изобретения относится к улучшенному кэшированию трансляции адресов и/или характеристик ввода-вывода кэш-памяти в виртуализированных средах.

Виртуализация ввода/вывода - технология, разрабатываемая для обеспечения эффективной работы устройств ввода/вывода в виртуализированной среде. В целом, виртуализированная среда может быть средой, в которой одновременно могут работать несколько операционных систем (OS). В некоторых вариантах выполнения для повышения эффективности виртуализации ввода/вывода могут быть использованы аппаратные средства. Однако такое выполнение может потребовать реализации относительно большого количества транзисторных переключателей, что, в свою очередь, делает устройство более дорогостоящим и/или более сложным для осуществления.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Подробное описание имеет ссылки на сопроводительные чертежи. На чертежах крайняя левая цифра позиции обозначает фигуру, на которой впервые появилась эта позиция. Использование тех же самых позиций на различных фигурах указывает на аналогичные или идентичные компоненты.

Фигуры 1-3 иллюстрируют блок-схемы примеров воплощения вычислительных систем, которые могут быть использованы, чтобы реализовать различные обсуждаемые здесь варианты изобретения.

Фигура 4 иллюстрирует схему выполнения способа согласно одному примеру воплощения изобретения.

ПОДРОБНОЕ ОПИСАНИЕ

В последующем описании приведены многочисленные подробности, чтобы обеспечить полное понимание различных примеров воплощения изобретения. Однако некоторые примеры воплощения могут быть приведены без конкретных деталей. В других примерах известные способы, процедуры, компоненты и микросхемы подробно не описываются, чтобы не затенять сущность изобретения. Различные аспекты примеров воплощения изобретения могут быть выполнены, используя различные средства, такие как интегральные полупроводниковые микросхемы (аппаратные средства), считываемые компьютером команды, организованные в виде одной или нескольких программ (программное обеспечение), или определенную комбинацию аппаратных средств и программного обеспечения. При этом ссылки на "логику" должны означать аппаратные средства, программное обеспечение или некоторые их комбинации.

Некоторые из обсуждаемых здесь примеров воплощения могут улучшить кэширование трансляции адресов (при виртуализации для направленного ввода/вывода (VTd)) и/или работу кэш-памяти ввода/вывода в виртуализированных средах. Более конкретно, некоторые услуги виртуализации могут быть осуществлены в структурах аппаратных средств, которые используются для перевода физического адреса гостя (GPA) в физический адрес хозяина (НРА). Соответственно, такие структуры могут оказать поддержку кэширования, например, в виде буфера опережающей выборки ввода/вывода (IOTLB) при трансляциях из GPA в НРА. В некоторых примерах воплощения эти кэш-структуры могут обеспечить более низкую латентность для запросов, которые имеют целью ту же самую трансляцию адреса. Кроме того, некоторые из методик могут быть использованы в различных типах вычислительных сред, например, обсужденных со ссылками на фигуры 1-4.

На фигуре 1 показана блок-схема вычислительной системы 100 согласно одному примеру воплощения изобретения. Система 100 может включать одно или несколько средств 102-1 - 102-М (все вместе называемые здесь как "агенты 102" или в общем смысле "агент 102"). В примере воплощения агенты 102 могут быть компонентами вычислительной системы, например системы, обсужденные со ссылками на фигуры 2-4.

Как показано на фигуре 1, агенты 102 могут общаться через сетевую матрицу 104. В одном примере воплощения сетевая матрица 104 может включать компьютерную сеть, которая позволяет различным агентам (таким как вычислительные устройства) передавать данные. В одном примере воплощения сетевая матрица 104 может включать одно или несколько соединений (или соединительных сетей), которые общаются через последовательную линию связи (например, от точки к точке) и/или через сеть связи общего доступа. В частности, некоторые примеры воплощения могут облегчить отладку компонентов или проверку линий связи, которые обеспечивают связь с полностью буферизованными совместно работающими двойными модулями памяти (FBD), например, там, где линия FBD является последовательной линией связи, используемой для соединения модулей памяти с хост-контроллером (такими как процессор или ядро памяти). Информация отладки может быть передана от хост-линии FBD таким образом, чтобы информация отладки могла бы контролироваться вдоль линии приборами проверки трафика (например, одним или несколькими логическими анализаторами).

В одном примере воплощения система 100 может поддерживать схему многослойного протокола, которая может включать физический слой, слой связи, слой маршрутизации, транспортный слой и/или слой протокола. Матрица 104 может также облегчить передачу данных (например, в виде пакетов) из одного протокола (например, кэширующего процессора или кэширующего процессора памяти) к другому протоколу для двухточечной или общедоступной сети. Кроме того, в некоторых примерах воплощения сетевая матрица 104 может обеспечить связь для одного или нескольких устройств буферной памяти по соответствующим протоколам.

Кроме того, как показано стрелками на фигуре 1, агенты 102 могут передавать и/или получать данные через сетевую матрицу 104. Следовательно, некоторые агенты могут использовать однонаправленную линию связи, в то время как другие могут использовать двунаправленную линию связи. Например, один или несколько агентов (таких как агент 102-М) могут передавать данные (например, через однонаправленную линию связи 106), другие агенты (такие как агент 102-2) могут получать данные (например, через однонаправленную линию связи 108), в то время как некоторое агенты (такие как агент 102-1) могут и передавать и получать данные (например, через двунаправленную линию связи 110).

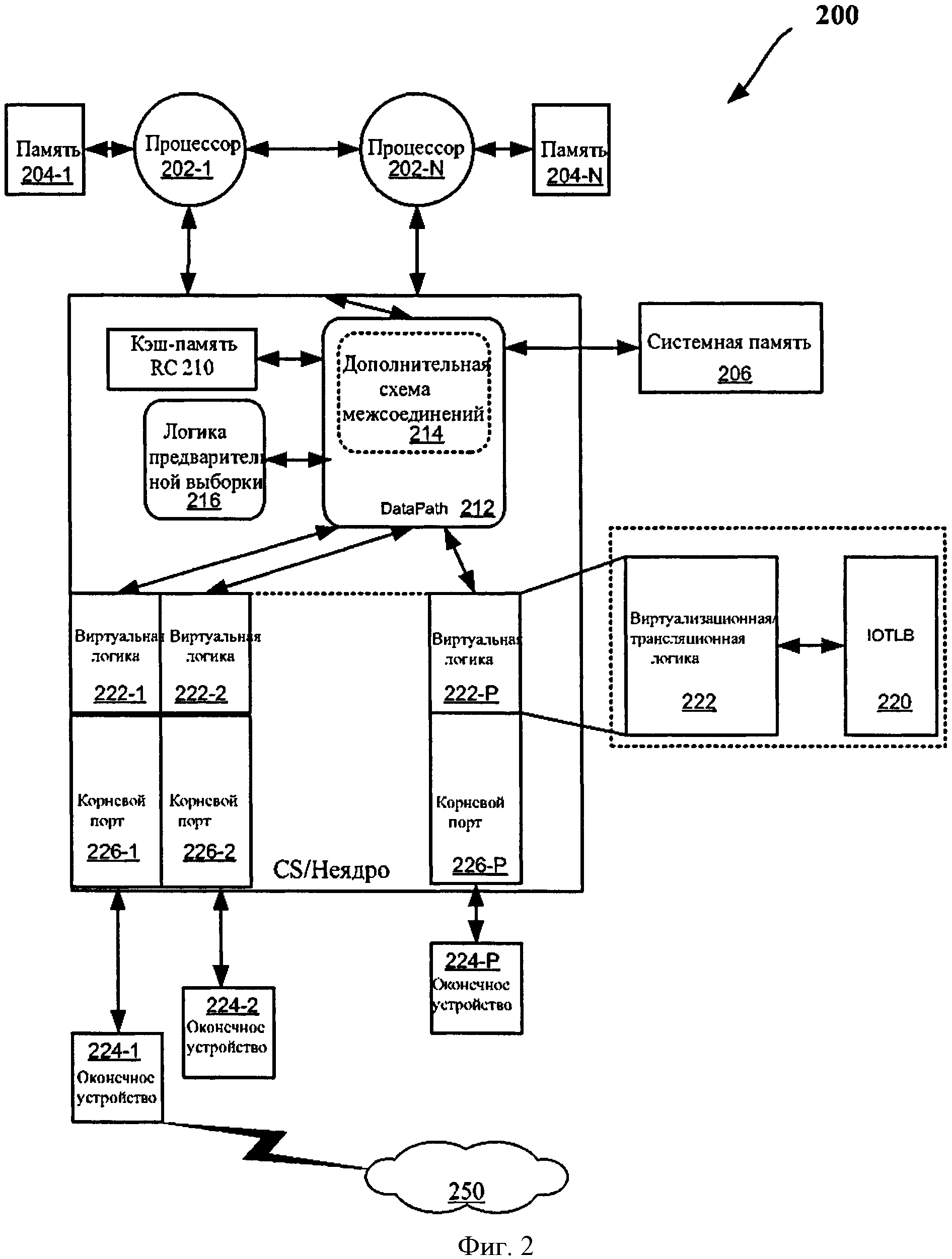

На фигуре 2 представлена блок-схема частей вычислительной системы 200 согласно одному примеру воплощения изобретения. В таком примере воплощения могут быть выполнены различные компоненты системы 200 в виде агентов 102-1 и/или 102-М, обсужденные со ссылкой на фигуру 1. Дальнейшие детали некоторых операций вычислительной системы 200 будут обсуждены со ссылкой на фигуру 4.

Система 200 может включать один или несколько процессоров 202-1 - 202-N (все вместе называемые здесь как "процессоры 202" или в общем смысле "процессор 202"). Каждый из процессоров 202-1 - 202-N может включать различные компоненты, такие как собственная или общедоступная кэш-память, исполнительные модули, одно или несколько ядер и т.д. Кроме того, каждый из процессоров 202 может иметь доступ к памяти 204 (например, к модулям памяти 204-1 - 204-N). Кроме того, система 200 может включать дополнительную системную память 206, которая может быть разделена между различными компонентами системы 200, включая, например, один или несколько процессоров 202, неядерную часть процессора или наборы микросхем (CS) 208 или компоненты, соединенные с набором микросхем 208, и т.д. Один или несколько модулей памяти 204 и/или 206 могут быть использованы для хранения одной или нескольких операционных систем. Следовательно, система 200 в некоторых примерах воплощения может выполнять множество операционных программ (в частности, одновременно).

Как показано на фигуре 2, неядерная часть 208 может включать различные компоненты, такие как основная кэш-память RC 210 (которая может быть разделена среди различных компонентов вычислительной системы, такой как система 200). В некоторых примерах воплощения кэш-память RC 210 может присутствовать в хабе управления памятью (МСН) и/или в графической части МСН (GMCH) набора микросхем или части неядра (например, CS/неядро 208). Кэш-память RC 210 может общаться с другими компонентами по линии данных 212 (которая может включать дополнительную схему межсоединений 214, например, для того, чтобы облегчить связь между одним или несколькими ядрами процессоров 202 и другими компонентами системы 200). Система 200 может дополнительно включать логику предварительной выборки 216, например предварительной выборки данных (включая команды или микрокоманды) от различных местоположений (таких как один или несколько модулей памяти 204, системная память 206, другие устройства памяти, включая, например, энергозависимые или энергонезависимые запоминающие устройства и т.д.) в блок IOTLB 220 (например, через виртуализированную или трансляционную логику 222-1 - 222-Р (называемую здесь как "логические схемы 222" или в общем смысле "логика 222")).

Как показано на фигуре 2, по меньшей мере, в одном примере воплощения путь данных 212 может быть связан с одним или несколькими устройствами ввода/вывода. Может быть использован любой тип устройства ввода/вывода. В иллюстративных целях в примере воплощения, показанном на фигуре 2, устройства ввода/вывода могут включать одно или несколько устройств 224-1 - 224-Р (все вместе называемые здесь "оконечными устройствами 224" или в общем смысле "оконечное устройство 224"). Оконечные устройства 224 могут быть периферическим соединительным устройством (например, шиной PCI) в одном примере воплощения.

Например, оконечные устройства 224 могут общаться с CS/неядром 208 по протоколу соединения через местную шину PCI, с дополнением от 3.0 от 9 марта 2004 года, опубликованную Специальной группой PCI, Портленд, Орегон, США (в дальнейшем именуемая "шиной PCI"). Альтернативно, может быть использована Спецификация PCI-X с дополнением 3.0а, в дальнейшем называемая "шина PCI-X" (2 октября 2006 года), опубликованная вышеуказанной Специальной группой PCI, Портленд, Орегон, США. Кроме того, другие периферийные устройства, связанные с CS/неядром 208, могут включать в различных примерах воплощения изобретения дисковод со встроенным контроллером (IDE) или жесткий диск интерфейса малых вычислительных систем (SCSI), устройство универсальной последовательной шины (USB), клавиатуру, мышь, параллельные порты, последовательные порты, дисководы, поддержку цифрового вывода (например, в виде интерактивное цифровое видео (DVI)) и т.д.

Как показано на фигуре 2, оконечные устройства 224 могут общаться через корневые порты 226-1 - 226-Р (все вместе именуемые здесь как "порты 226" или в общем смысле "порт 226") с другими компонентами системы 200, такими как логические схемы 222. В примере воплощения логика 222 может выполнять трансляцию адреса для виртуализированных сред, в частности трансляцию виртуальных адресов в физические адреса, например, типа IOTLB 220. Физические адреса могут соответствовать местоположениям (например, записям) в системной памяти 206. Логика 222 может дополнительно выполнять другие действия, такие как обсужденные со ссылками на фигуры 3 и 4, которые могут включить трансляцию записей GPA и НРА в устройстве памяти, соединенном с системой 200 и/или 300 (такой как системная память 206). Кроме того, логика 222 может быть корневым каталогом в соответствии со спецификацией PCI.

Кроме того, процессоры 202 могут быть процессором любого типа, таким как универсальный процессор, сетевой процессор (который может обработать данные из компьютерной сети 250) и т.д. (включая процессор компьютера с сокращенным набором команд (RISC) или процессор с полным набором команд (CISC)). Кроме того, процессоры 202 могут иметь одноядерную или многоядерную конструкцию. Процессоры 202 с многоядерной конструкцией могут включать различные типы ядер процессора на одной и той же интегральной схеме (IC). Кроме того, процессоры 202 многоядерного типа могут быть осуществлены как симметричные или асимметричные мультипроцессоры. Также, как показано на фигуре 2, по меньшей мере, одно или несколько оконечных устройств 224 в одном примере воплощения могут быть соединены с сетью 250.

Далее, процессоры 202 могут включать одно или несколько устройств кэш-памяти (не показаны), которые могут быть скрытыми и/или общедоступным в различных примерах воплощения. В целом, кэш-память хранит данные, соответствующие оригинальным данным, хранившимся в другом месте или полученным ранее. Чтобы уменьшить латентность доступа к памяти, когда данные хранятся в кэш-памяти, будущее использование может быть основано на получении доступа к кэшированной копии вместо повторного доступа или повторного вычисления оригинальных данных. Обсуждаемая здесь кэш-память (включая, например, кэш-память RC 210, IOTLB 220, их комбинации и т.д.) может быть любым типом кэш-памяти, такой как кэш-память уровня 1 (L1), кэш-память уровня 2 (L2), уровня 3 (L3), кэш-память среднего уровня, кэш-память последнего уровня (LLC), их комбинации и т.д., чтобы хранить электронные данные (например, команды), которые используется одним или несколькими компонентами системы 200.

Пример воплощения системы 200 и/или 300 может также включать другие устройства, например один или несколько дисплеев (например, подключенных к CS/неядру 208 и используемых для отображения изображений), звуковое устройство (например, подключенное к CS/неядру 208, чтобы обрабатывать звуковые сигналы) и т.д. В некоторых примерах воплощения такие устройства могут быть выполнены как оконечные устройства 224 (которые могут общаться с CS/неядром 208 через корневые порты 226).

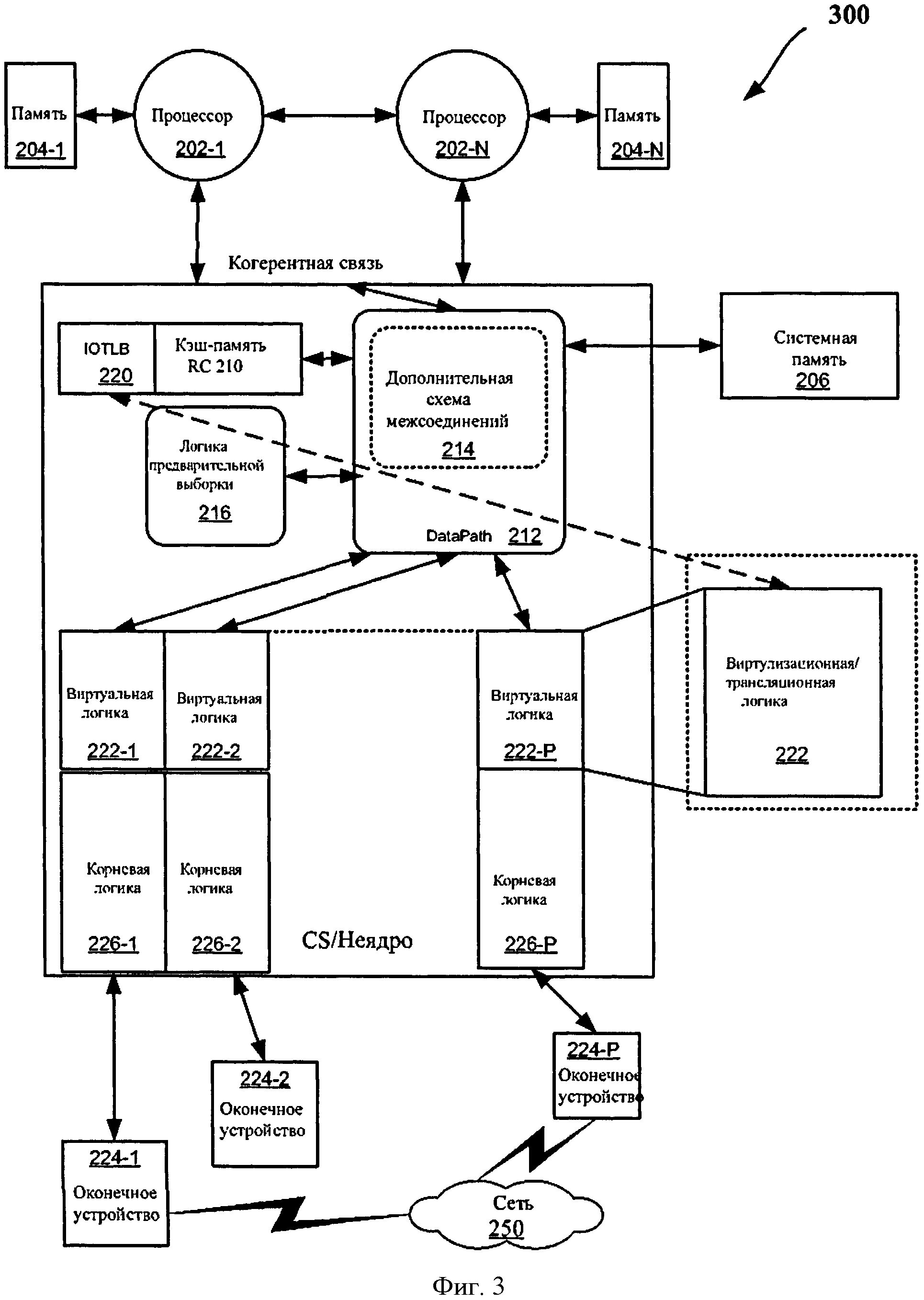

На фигуре 3 показана блок-схема частей вычислительной системы 300 согласно другому примеру воплощения изобретения. В этом примере воплощения различные компоненты системы 300 могут быть интегрированы в одном из агентов 102-1 и/или 102-М, обсужденных со ссылкой на фигуру 1. Подробное описание некоторых действий вычислительной системы 300 будет приведено здесь со ссылкой на фигуру 4.

Как показано на фигуре 3, система 300 может включать один или несколько процессоров 202, блоки памяти 204, системную память 206, кэш-память RC 210, путь данных 212, дополнительную схему межсоединений 214, логику предварительной выборки 216, IOTLB 220, логику 222, оконечные устройства 224 и корневые порты 226. Кроме того, как показано на чертеже, в одном примере воплощения кэш-память RC 210 и IOTLB 220 могут быть объединены в один модуль кэш-памяти.

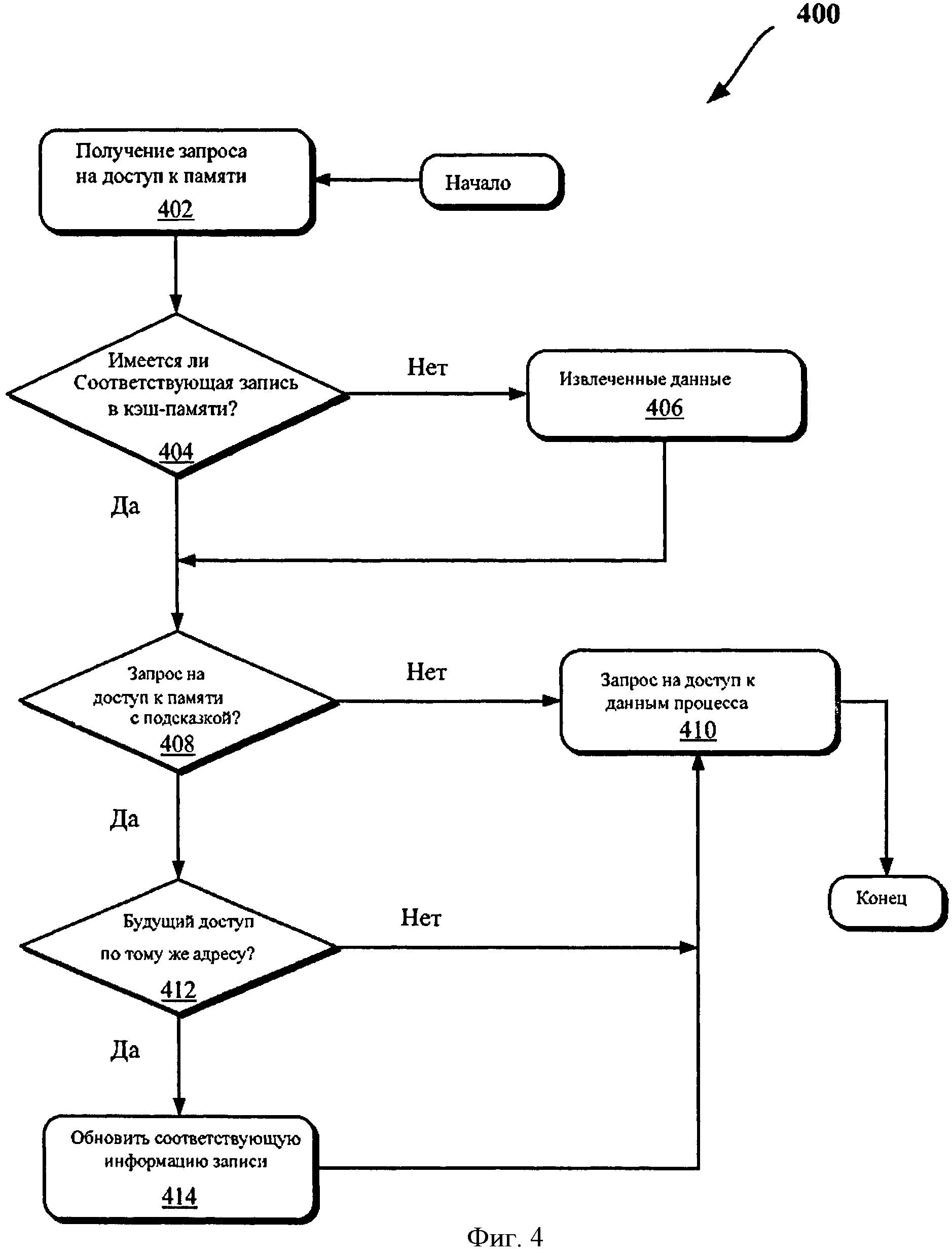

На фигуре 4 показана схема последовательности операций выполнения способа 400, чтобы обновить информацию, хранившуюся в кэш-памяти ввода/вывода, и улучшить кэширование трансляции адресов и/или работу кэш-памяти ввода/вывода в виртуализированных средах, согласно одному примеру воплощения. В одном примере воплощения обсуждены различные компоненты со ссылками на фигуры 1-3 и 5 для пояснения одной или нескольких стадий выполнения, обсужденных со ссылкой на фигуру 4.

На фигурах 1-4 стадия 402 способа 400 начинается с получения запроса на доступ к памяти. Например, запрос на доступ к памяти (например, доступ к чтению или записи) может быть сформирован одним из оконечных устройств 224 и получен соответствующей логикой виртуализации 222 через один из портов 226 на стадии 402. На стадии 404 может быть определено, существует ли запись, соответствующая запросу на доступ к кэш-памяти. В примере воплощения логика виртуализации 222 может получать доступ к IOTLB 220, кэш-памяти RC 210 и/или их комбинации (такой, как показана на фигуре 3) на стадии 404. Если соответствующая запись отсутствует, данные могут быть занесены в кэш-память на стадии 406 (например, логикой виртуализации 222 и/или логикой предварительной выборки 216).

В примере воплощения соответствующие данные могут быть предварительно внесены в кэш-память логикой 216 до стадии 402. В одном примере воплощения запрос на предварительную выборку выдается одним из оконечных устройств 224, которое выполняет упреждающую выборку и поддерживает когерентные копии целевого местоположения адреса. Эти запросы на предварительную выборку также позволяют обновить IOTLB 220, кэш-память RC 210 и/или их комбинации; входы распределяются и кэшируются до тех пор, пока запрос не будет передан устройству. Будут определены параметры настройки АСН, если вход в IOTLB 220, кэш-памяти RC 210 и/или их комбинацию должен быть поддержан или тегирован для замены.

На стадии 408 может быть определено (например, логикой виртуализации 222), включает ли запрос на доступ к памяти подсказку (в виде одной или нескольких подсказок в запросе на доступ к памяти). Если нет никакой подсказки, запрос на доступ к памяти может быть обработан на стадии 410, например, трансляцией адреса НРА и GPA и/или физического/виртуального адреса на вход IOTLB 220, кэш-память RC 210 и/или их комбинацию. В одном примере воплощения кэширование трансляции адресов и/или работа кэш-памяти ввода/вывода в виртуализированных средах могут быть улучшены на основе подсказок трафика устройства ввода/вывода (которые здесь также могут быть упомянуты как подсказки блока управления доступом (АСН)). Блок (или блоки) АСН может быть снабжен устройством ввода/вывода (например, одним из оконечных устройств 224) в запросе памяти (например, по шине PCI), чтобы определить, получило ли бы устройство доступ к одному и тому же адресу снова. Соответственно, на стадии 412 можно определить, указывает ли подсказка на будущий доступ к тому же самому адресу. Эта информация может храниться в виде одного или нескольких битов, соответствующих записи в кэш-памяти (например, запись в IOTLB 220, кэш-памяти RC 210 и/или их комбинации), что было бы полезно для алгоритма замены линии кэш-памяти, например, там, где кэшированные трансляции без намеченного повторного использования набора битов (или очищенные в зависимости от выполнения) могли бы быть кандидатами на замену. В одном примере воплощения логика 222 может выполнить операцию 412. Если не указано никакого будущего доступа, способ 400 возобновляется со стадии 410. В противном случае соответствующая информация записи может быть обновлена на стадии 414 (например, один или несколько битов для соответствующей записи в IOTLB 220, кэш-памяти RC 210 и/или их комбинации могут быть обновлены соответствующей логикой 222). После стадии 414 способ 400 возвращается на стадию 410.

В некоторых примерах воплощения консолидирование структуры IOTLB 220 и кэш-памяти RC 210 в комбинированную структуру кэш-памяти IOTLB и кэш-памяти RC (которая также называется здесь кэш-памятью ввода/вывода) может улучшить рабочие характеристики (например, уменьшить латентность для трансляций ввода/вывода) и/или обеспечить более эффективное использование полезной площади кристалла или пластины кремния (например, уменьшить общее количество затворов). В одном примере прикладные программы, формируемые процессором (например, одним или несколькими процессорами 202), будут просматривать содержимое кэш-памяти RC 210 (или комбинированной кэш-памяти ввода/вывода), используя физический адрес, а доступы ввода/вывода будут искать адрес в кэш-памяти RC 210 (или комбинированной кэш-памяти ввода/вывода) на основе GPA.

В некоторых примерах воплощения различные алгоритмы замены кэш-памяти могут быть применены к кэш-памяти RC 210, IOTLB 220 и/или их комбинации. Например, алгоритм замены может быть алгоритмом случайной замены, тогда как в другом случае может осуществляться последний использованный алгоритм (LRU).

Соответственно, в некоторых примерах воплощения латентность трансляции адреса и/или латентность, связанная с обслуживанием запросов ввода/вывода, могут быть восстановлены. Кроме того, консолидация структур хранения (например, адреса или данных), используемых для кэш-памяти RC 210 и IOTLB 220 (например, в один модуль кэш-памяти ввода/вывода), может привести к повышению эффективности кремния и лучшей работе кремниевой подложки (например, путем снижения количества транзисторных переключателей).

В различных примерах воплощения изобретения обсужденные здесь операции, например со ссылками на фигуры 1-4, могут быть осуществлены с помощью аппаратных средств (например, схем), программного обеспечения, программируемого оборудования, набора набор микрокоманд или их комбинации, которые могут быть обеспечены как продукт в виде компьютерной программы, например, включая машиночитаемую среду, сохраняющую команды (или программные продукты), используемые для программирования компьютера, чтобы выполнить обсужденный здесь процесс. Кроме того, термин "логика" может включать, например, программное обеспечение, аппаратные средства или комбинацию программного обеспечения и аппаратных средств. Машиночитаемая среда может включать устройство хранения данных, подобное устройству, обсужденному здесь.

Например, обсужденное здесь устройство хранения данных может включать энергозависимую и/или энергонезависимую память (или хранилище). Энергонезависимая память может включать одно из следующих: постоянную память (ROM), программируемую память ROM (PROM), стираемую память PROM (EPROM), электрически стираемую постоянную память (EEPROM), дисковод, дискету, ROM компакт-диска (CD-ROM), цифровой универсальный диск (DVD), флеш-память, оптический магнитный диск или другие типы энергонезависимой машиночитаемой среды, способной хранить электронные данные (например, команды). Энергозависимое хранилище (или память) может включать такие устройства, как память с произвольным доступом (RAM), динамическую RAM (DRAM), синхронную динамическую DRAM (SDRAM), статическую RAM (SRAM) и т.д.

Дополнительно, такая машиночитаемая среда может быть загружена как компонент компьютерной программы, в которой программа может быть передана от удаленного компьютера (например, сервера) на запрашиваемый компьютер (например, клиент) путем передачи сигналов данных, внедренных в несущую или другую передающую среду через линию связи (например, шину, модем или сетевое соединение).

Ссылка в описании на "один пример воплощения" или "пример воплощения" означает, что конкретный признак, структура или характеристика, описанная в связи с примером воплощения, могут быть включены, по меньшей мере, в выполнение операции. Появления фразы "в одном примере воплощения" в различных местах в описании могут или, возможно, не могут быть отнесены к одному и тому же примеру воплощения.

Кроме того, в описании и формуле изобретения могут использоваться термины "соединены" и "связаны" вместе с их производными. В некоторых примерах воплощения изобретения термин "связаны" может обозначать, что два или несколько элементов находятся в прямом физическом или электрическом контакте друг с другом. Термин "соединены" может означать, что два или несколько элементов находятся в прямом физическом или электрическом контакте. Однако "соединенный" может также означать, что два или несколько элементов, возможно, не находятся в прямом контакте друг с другом, но могут быть во взаимодействии друг с другом.

Таким образом, хотя примеры воплощения изобретения были описаны на языке, определенном для структурных признаков и/или методологических действий, следует понимать, что заявленный объект не может быть ограничен определенными признаками или описанными действиями. Скорее, определенные признаки и действия раскрыты как типичные формы осуществления заявленного объекта.

Реферат

Изобретение относится к вычислительной технике. Технический результат заключается в улучшении кэширования трансляции адресов при виртуализации для направленного ввода/вывода (VTd). Устройство кэширования содержит: кэш-память для хранения одной или нескольких записей, в которой каждая запись соответствует запросу на доступ к памяти ввода-вывода и каждая запись должна содержать физический адрес гостя (GPA), соответствующий запросу на доступ к памяти ввода/вывода, и соответствующий физический адрес хозяина (НРА); и первую логику, которая получает первый запрос на доступ к памяти ввода/вывода от оконечного устройства и определяет, включает ли первый запрос на доступ к памяти ввода/вывода подсказку будущего доступа, связанную с адресом, причем подсказка будущего доступа должна указывать хозяину, может ли выполняться доступ к адресу в будущем, и записи в кэш-памяти, которые не содержат подсказку, соответствующую предыдущим запросам на доступ к памяти ввода/вывода, содержащим подсказки на будущий доступ, должны быть заменены раньше записей, которые содержат подсказку; и первая логика должна обеспечить обновление одного или нескольких битов, соответствующее адресу, как записи в кэш-памяти, так и в записи в буфере опережающей выборки трансляции ввода/вывода (IOTLB), в ответ на определение, что первый запрос на доступ к памяти ввода/вывода включает подсказку будущего доступа. 3 н. и 16 з.п. ф-лы, 4 ил.

Формула

кэш-память для хранения одной или нескольких записей, в котором каждая запись соответствует запросу на доступ к памяти ввода-вывода, и каждая запись должна содержать физический адрес гостя (GPA), соответствующий запросу на доступ к памяти ввода/вывода, и соответствующий физический адрес хозяина (НРА); и

первую логику, которая получает первый запрос на доступ к памяти ввода/вывода от оконечного устройства и определяет, включает ли первый запрос на доступ к памяти ввода/вывода подсказку будущего доступа, связанную с адресом, причем подсказка будущего доступа должна указывать хозяину, может ли выполняться доступ к адресу в будущем, и записи в кэш-памяти, которые не содержат подсказку, соответствующую предыдущим запросам на доступ к памяти ввода/вывода, содержащим подсказки на будущий доступ, должны быть заменены раньше записей, которые содержат подсказку;

и первая логика должна обеспечить обновление одного или нескольких битов, соответствующее адресу, как записи в кэш-памяти, так и в записи в буфере опережающей выборки трансляции ввода/вывода (IOTLB), в ответ на определение, что первый запрос на доступ к памяти ввода/вывода включает подсказку будущего доступа.

получение первого запроса на доступ к памяти ввода-вывода от оконечного устройства;

сохранение одного или нескольких записей в кэш-памяти, в котором каждая запись соответствует запросу на доступ к памяти ввода-вывода между физическим адресом гостя (GPA) и физическим адресом хозяина (НРА); и

определение, включает ли первый запрос на доступ к памяти ввода/вывода подсказку будущего доступа, связанную с адресом, причем подсказка будущего доступа должна указывать хозяину, может ли выполняться доступ к адресу в будущем, и записи в кэш-памяти, которые не содержат подсказку, соответствующую предыдущим запросам на доступ к памяти ввода/вывода, содержащим подсказки на будущий доступ, должны быть заменены раньше записей, которые содержат подсказку; и

обновление одного или нескольких битов, соответствующее адресу, как записи в кэш-памяти, так и в записи в буфере опережающей выборки трансляции ввода/вывода (IOTLB), в ответ на определение, что первый запрос на доступ к памяти ввода/вывода включает подсказку будущего доступа.

память для хранения одной или нескольких записей;

кэш-память для хранения одной или нескольких записей, соответствующих одной или нескольким записям, хранящихся в памяти, в которой каждая запись в кэш-памяти должна соответствовать запросу на доступ к памяти ввода-вывода между физическим адресом гостя (GPA) и физическим адресом хозяина (НРА); и

первую логику, которая получает первый запрос на доступ к памяти ввода-вывода от оконечного устройства и определяет, включает ли первый запрос на доступ к памяти ввода/вывода подсказку будущего доступа, связанную с адресом, причем подсказка будущего доступа должна указывать хозяину, может ли выполняться доступ к адресу в будущем, и записи в кэш-памяти, которые не содержат подсказку, соответствующую предыдущим запросам на доступ к памяти ввода/вывода, содержащим подсказки на будущий доступ, должны быть заменены раньше записей, которые содержат подсказку;

и первая логика должна вызвать обновление одного или несколько битов, соответствующее адресу, как записи в кэш-памяти, так и в записи в буфере опережающей выборки трансляции ввода/вывода (IOTLB), в ответ на определение, что первый запрос на доступ к памяти ввода/вывода включает подсказку будущего доступа.

Документы, цитированные в отчёте о поиске

Разреженное кэширование для потоковой аудиовизуальной информации

Патенты аналоги

Разреженное кэширование для потоковой аудиовизуальной информации

Комментарии