Система памяти - RU2628124C2

Код документа: RU2628124C2

Чертежи

Описание

Область техники, к которой относится изобретение

Варианты осуществления, описанные здесь, в общем, относятся к системам памяти, в которой хост-контроллер памяти поддерживает связь по единственному каналу или шине с помощью многочисленных модулей памяти, которые имеют расположение выводов, совместимое со слотами, соединенными с каналом и хост-контроллером памяти. Хост-контроллер памяти поддерживает протокол, используемый многочисленными модулями памяти, соединенными с каналом, таким как протокол удвоенной скорости передачи данных третьего поколения (DDR3). Если модули памяти, такие как модули памяти с двухрядным расположением выводов (DIMM), имеют различное таймирование для вывода данных по шине, например в случае с различными типами DIMM, то хост-контроллер памяти должен регулировать эти различия при таймировании среди различных соединенных DIMM. Хост-контроллер памяти может передавать одноактные команды.

Перед использованием шины хост-контроллер памяти должен конфигурировать модули памяти для операций. В протоколе DDR3 хост-контроллер памяти можно использовать команду установки регистра режима работы (MRS) для программирования вплоть до восьми регистров режима работы в микросхемах памяти, таких как микросхемы динамической памяти произвольного доступа (DRAM), по отношению к одному корпусу модуля памяти. Команда MRS идентифицирует регистр режима работы в микросхеме памяти и включает в себя разряд инверсии, показывающий, инвертированы ли данные. После того, как шина обучена, хост-контроллер памяти может затем использовать шину для считывания и записи команд и передачи данных.

Команды могут отправлять один разряд в канале в команде. Во время нормального режима таймирования, например, таймирования IN, сигнал выбора чипа размещается на шине в течение цикла команды, чтобы побудить выбранный модуль памяти получать команду. Во время высокоскоростных операций, например, во время таймирования 2N, хост-контроллер памяти размещает сигнал выбора чипа на шине - один тактовый цикл перед командой, чтобы обеспечить дополнительное время установки.

Сигнал разрешения подачи тактовых импульсов, можно использовать для управления внутренними тактовыми сигналами в модуле памяти. Сигнал высокого уровня, разрешающий подачу тактовых импульсов (СКЕ), активирует внутренние тактовые сигналы и поддерживает права доступа на считывание и запись во время действия сигнала высокого уровня. Сигнал СКЕ низкого уровня в модуле памяти деактивирует внутренние тактовые сигналы, буферы на входе устройства и выходные драйверы. При получении сигналов СКЕ низкого уровня отключается электропитание и обновляются операции.

При передаче записей из хост-контроллера памяти в модуль памяти, записи в модуле памяти можно непосредственно записывать в микросхемы памяти. Однако в модулях памяти, имеющих буфер записи, можно реализовать систему кредита в тех случаях, когда хост-контроллер памяти выделяет максимальное количество кредитов записи и не может отправить команду записи, если отсутствуют доступные кредиты записи. Кредиты записи уменьшаются после отправки команды записи. Модуль памяти будет отправлять сообщение по шине после того, как каждая запись завершит возвращение кредита в хост-контроллер памяти, который увеличивает значение счетчика кредита записи после получения сообщения.

Во избежание передачи досадной комбинации при отправке запросов на считывание и запись, текущие хост-контроллеры памяти могут дескремблировать данные, чтобы уменьшить вероятность повторения досадной комбинации, которая может вызвать ошибку на шине. После получения дескремблированных данных записи с адресом записи, модуль памяти сохраняет дескремблированные данные записи под адресом записи. В ответ на запрос считывания зашифрованные данные сохраняются и отправляются по шине в хост-контроллер памяти для дескремблирования и дальнейшего использования.

Подробное описание изобретения

Варианты осуществления описаны посредством примера со ссылкой на сопроводительные чертежи, которые изображены не в масштабе и на которых одинаковые ссылочные позиции относятся к аналогичным элементам.

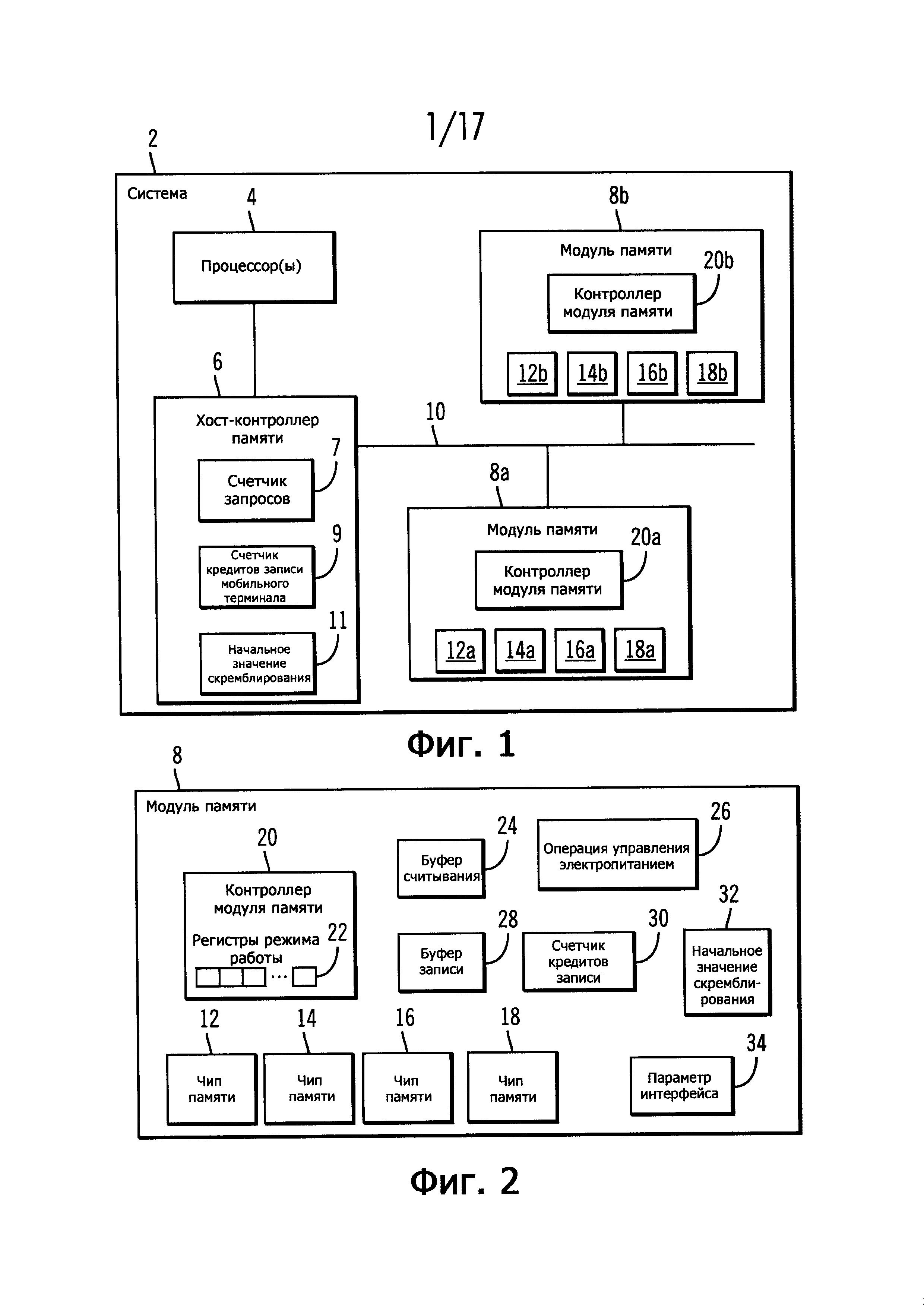

Фиг. 1 иллюстрирует вариант осуществления системы, имеющей систему памяти.

Фиг. 2 иллюстрирует вариант осуществления модуля памяти.

Фиг. 3 иллюстрирует вариант осуществления схемы разводки выводов системы памяти.

Фиг. 4 - вариант осуществления операций для выработки и обработки сигнала запроса, используемого для кодирования функции.

Фиг. 5 - иллюстрирует вариант осуществления операций для определения регулировки таймирования для выходного сигнала в модуле памяти.

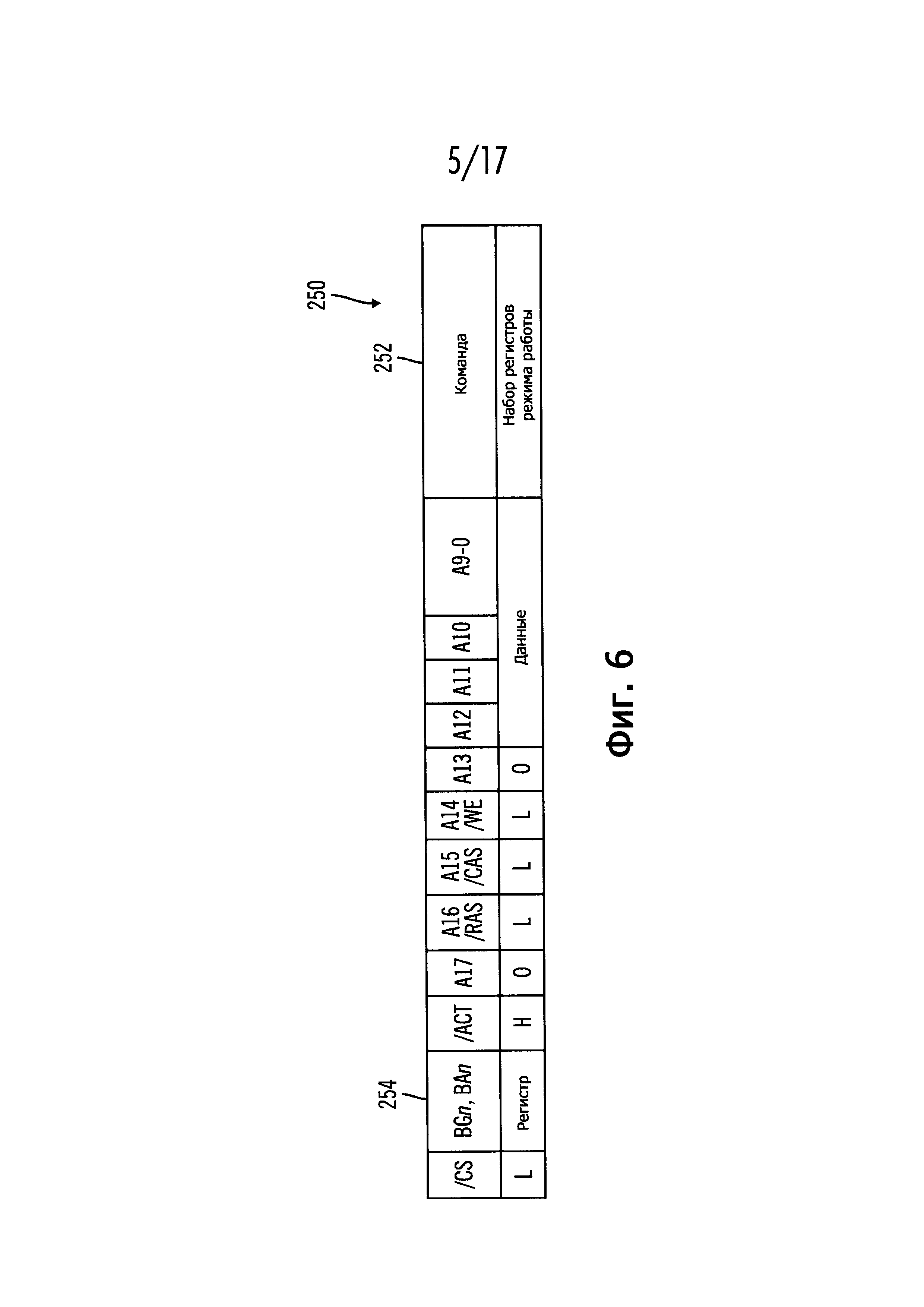

Фиг. 6 иллюстрирует вариант осуществления команды установки регистра режима работы (MRS).

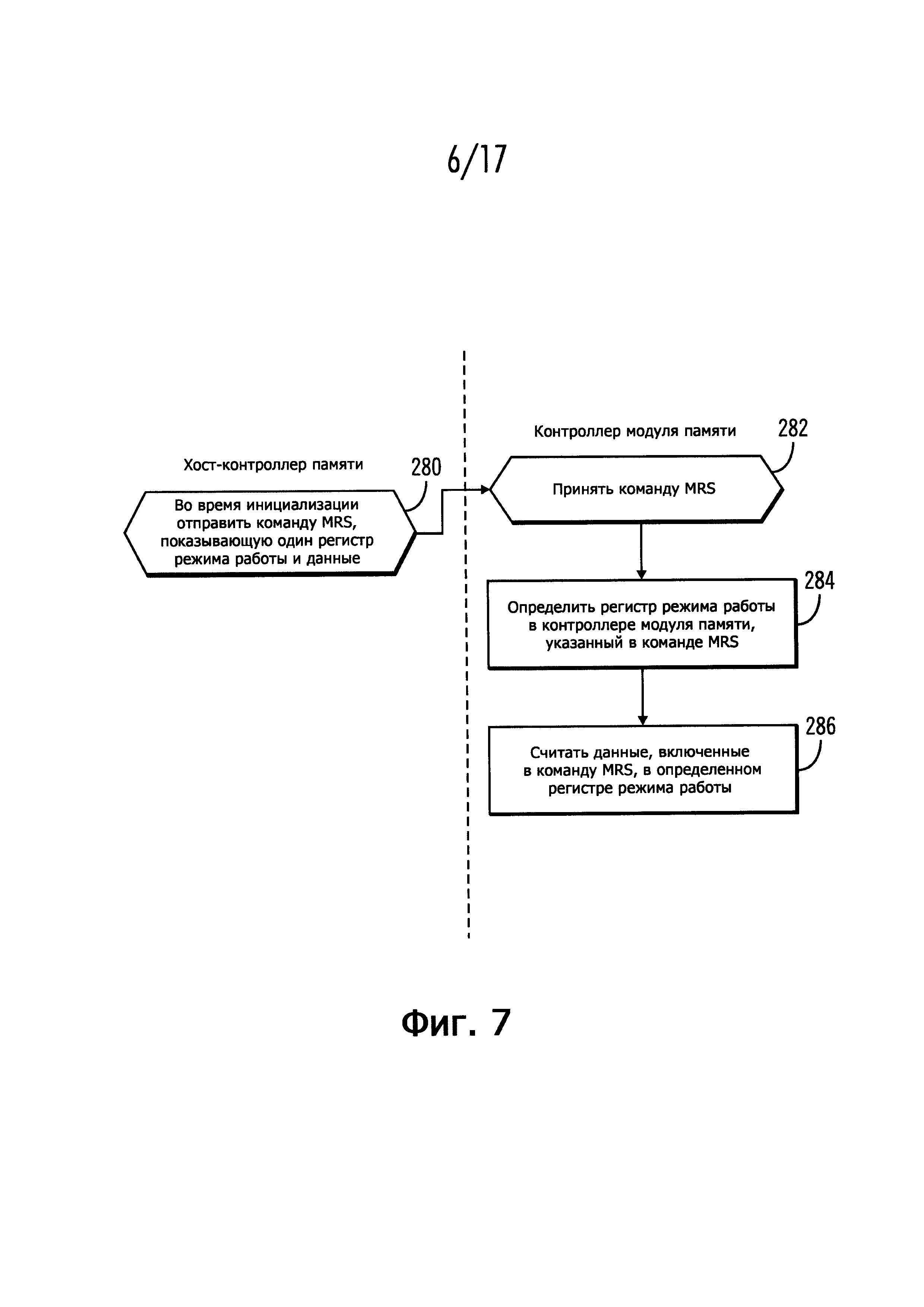

Фиг. 7 иллюстрирует вариант осуществления операций для выработки и обработки команды MRS.

Фиг. 8 и 9 предоставляют временные диаграммы для вывода команды в виде двух частей.

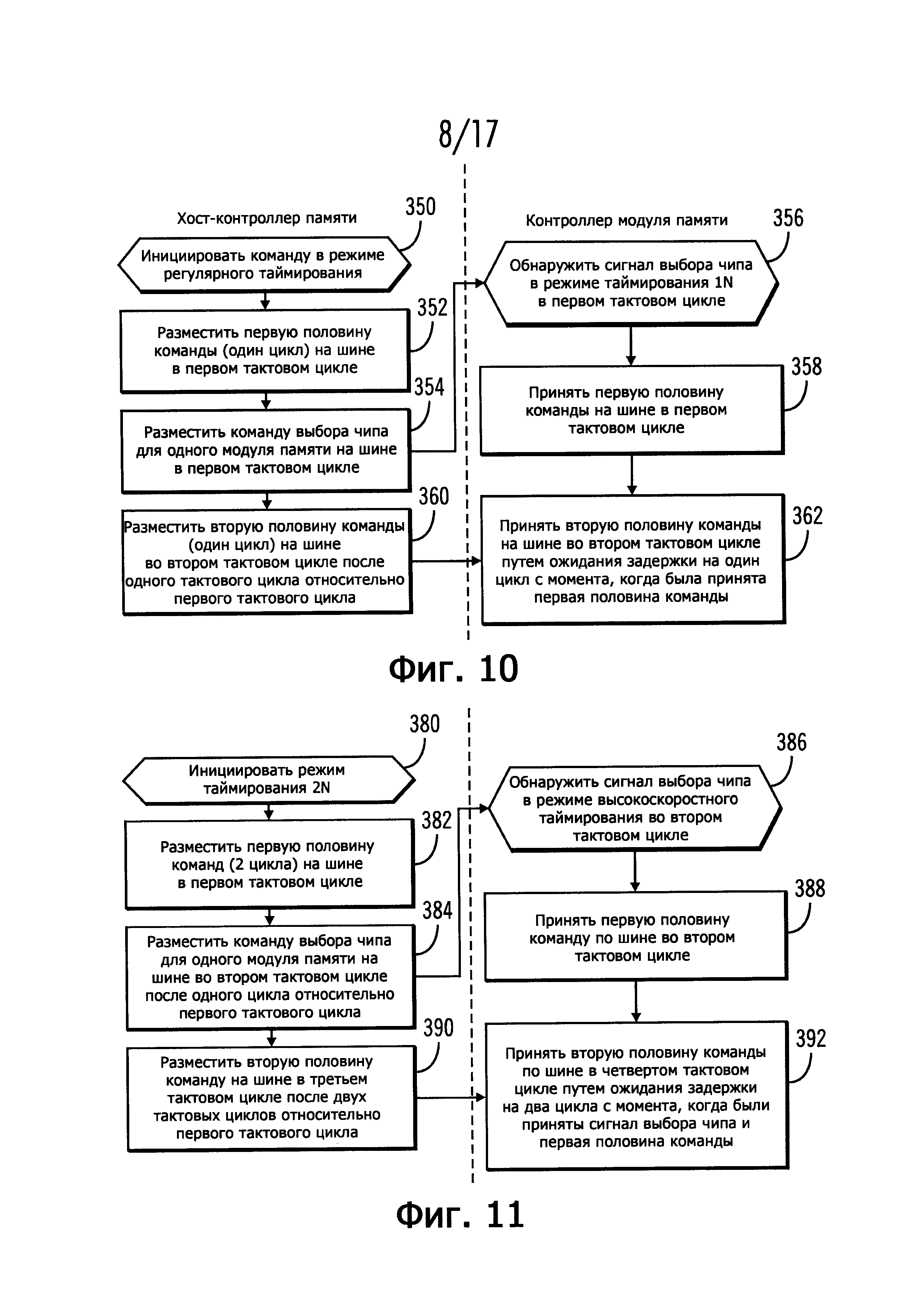

Фиг. 10 и 11 иллюстрируют варианты осуществления операций для выработки и приема команды, отправленной в многочисленных тактовых циклах.

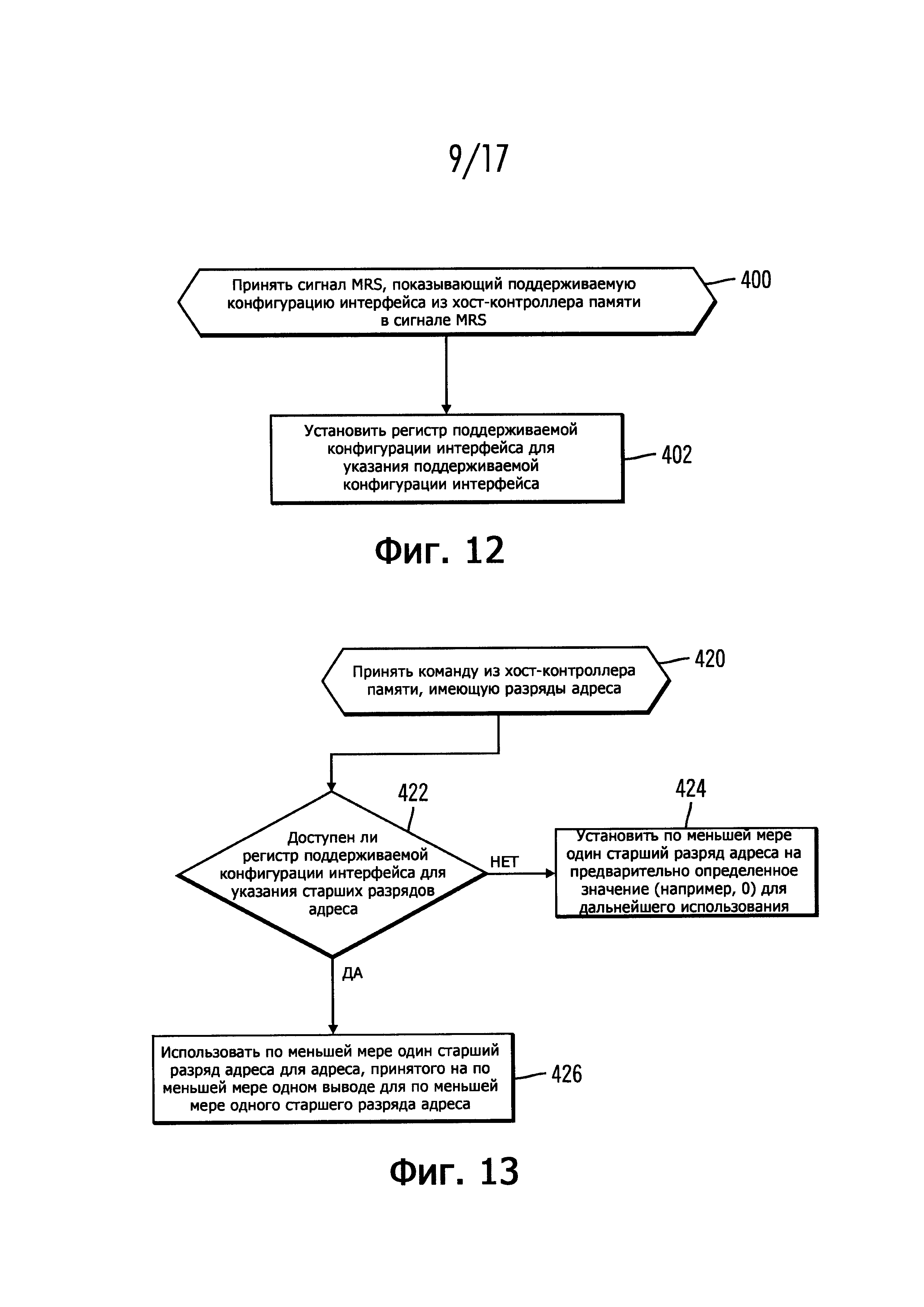

Фиг. 12 иллюстрирует вариант осуществления операций для указания поддерживаемой конфигурации интерфейса в контроллере модуля памяти.

Фиг. 13 иллюстрирует вариант осуществления операций для контроллера модуля памяти для использования разрядов адреса, основанных на поддерживаемой конфигурации интерфейса.

Фиг. 14 иллюстрирует вариант осуществления операций для использования команд для указания операций управления электропитанием.

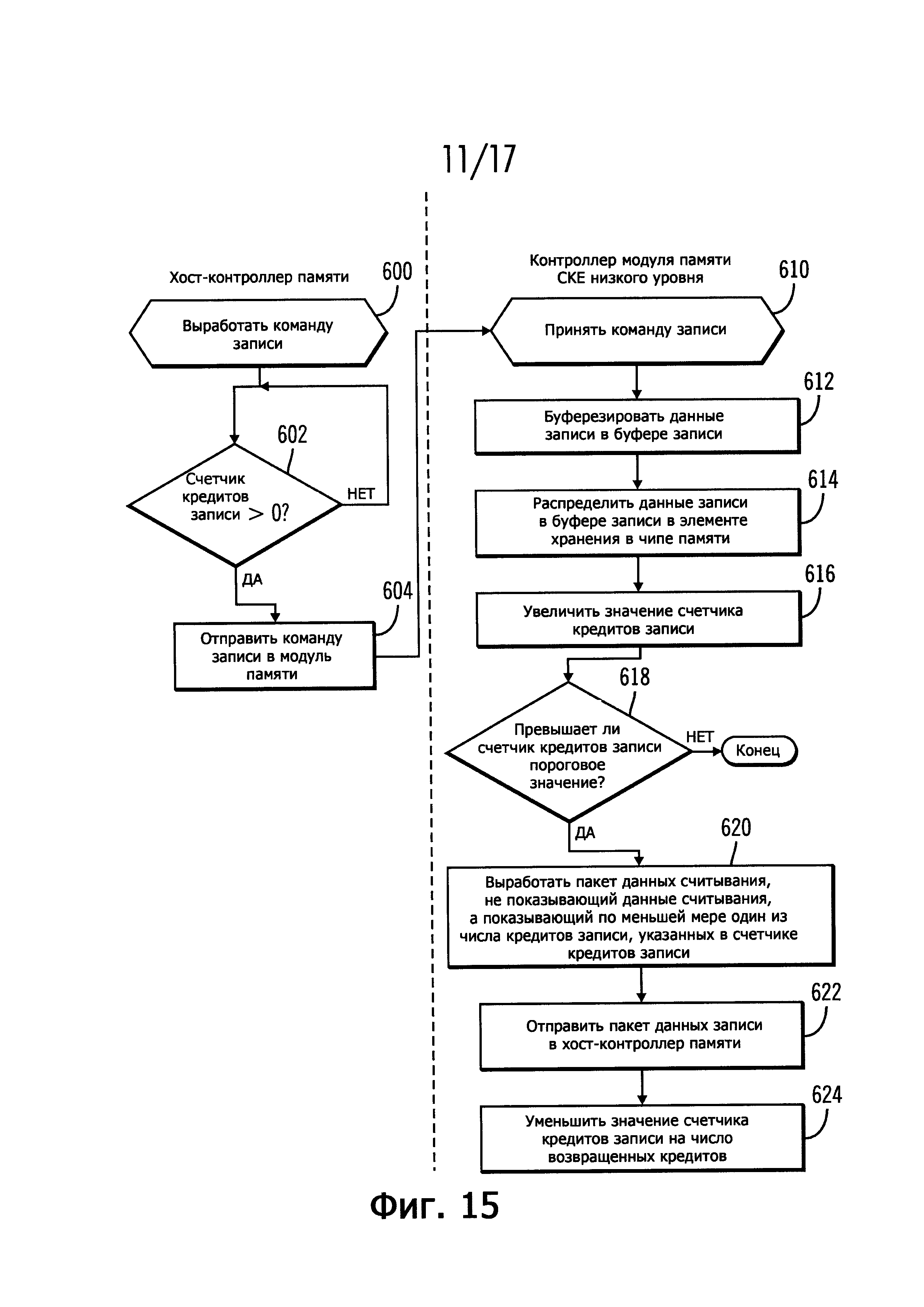

Фиг. 15 иллюстрирует вариант осуществления операций для использования кредитов записи для отправки команд записи и возврата кредитов записи в хост-контроллер памяти.

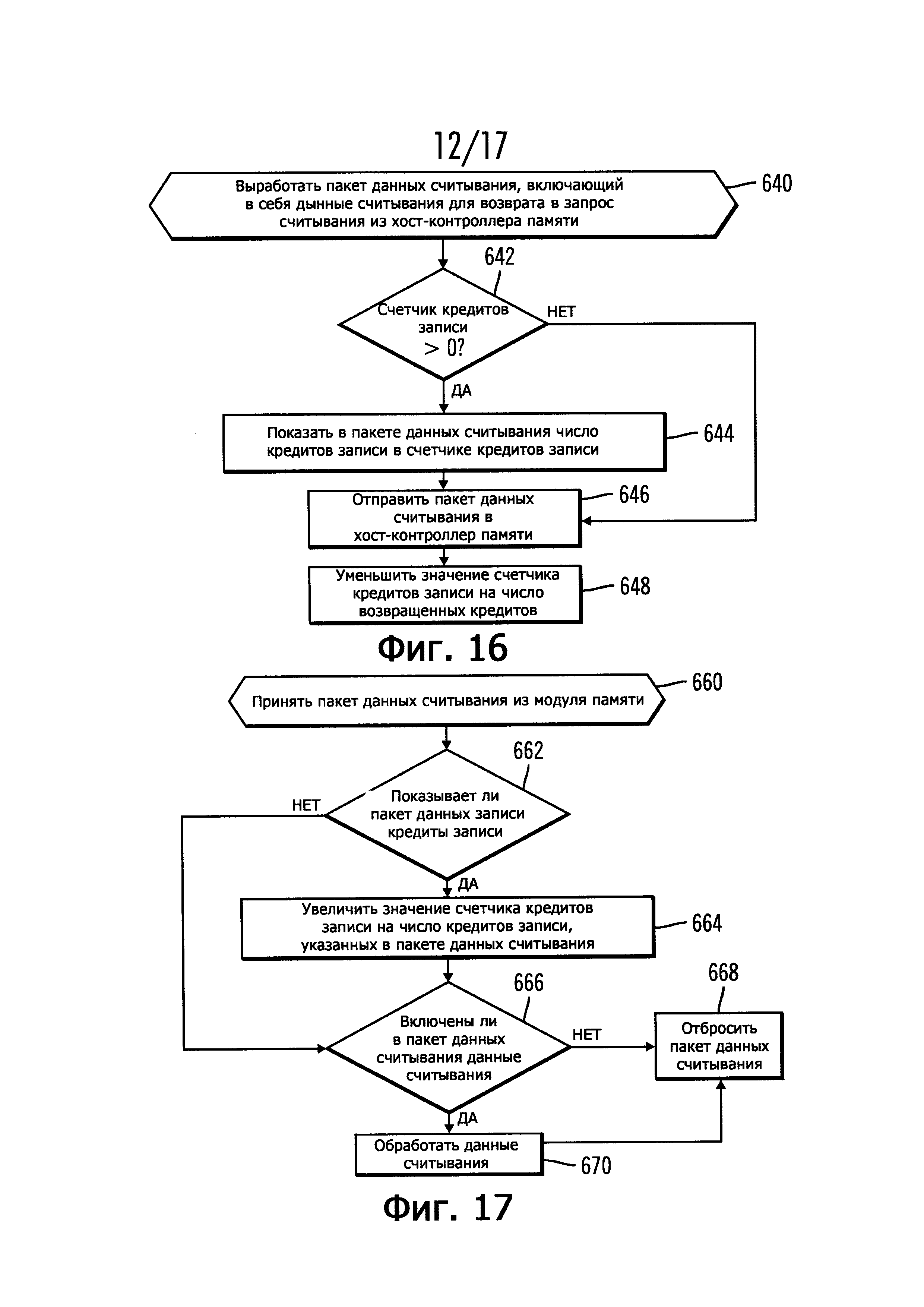

Фиг. 16 иллюстрирует вариант осуществления операций для выработки пакета данных считывания со счетчиком кредита записи.

Фиг. 17 иллюстрирует вариант осуществления операций для обработки пакета данных считывания.

Фиг. 18 иллюстрирует вариант осуществления операций для обработки потока ошибочных операций с использованием сигнала ошибки.

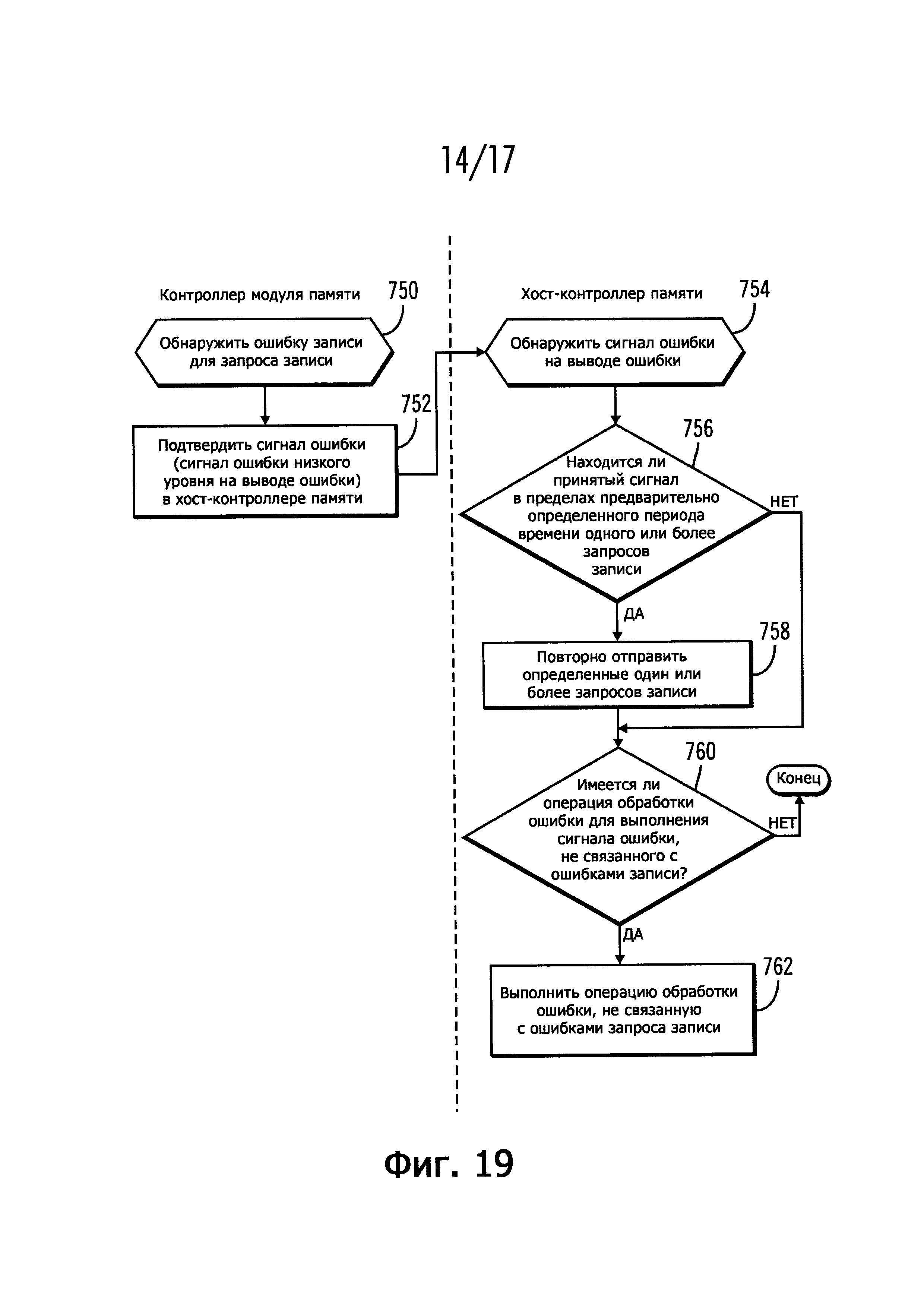

Фиг. 19 иллюстрирует вариант осуществления операций для обработки ошибки записи.

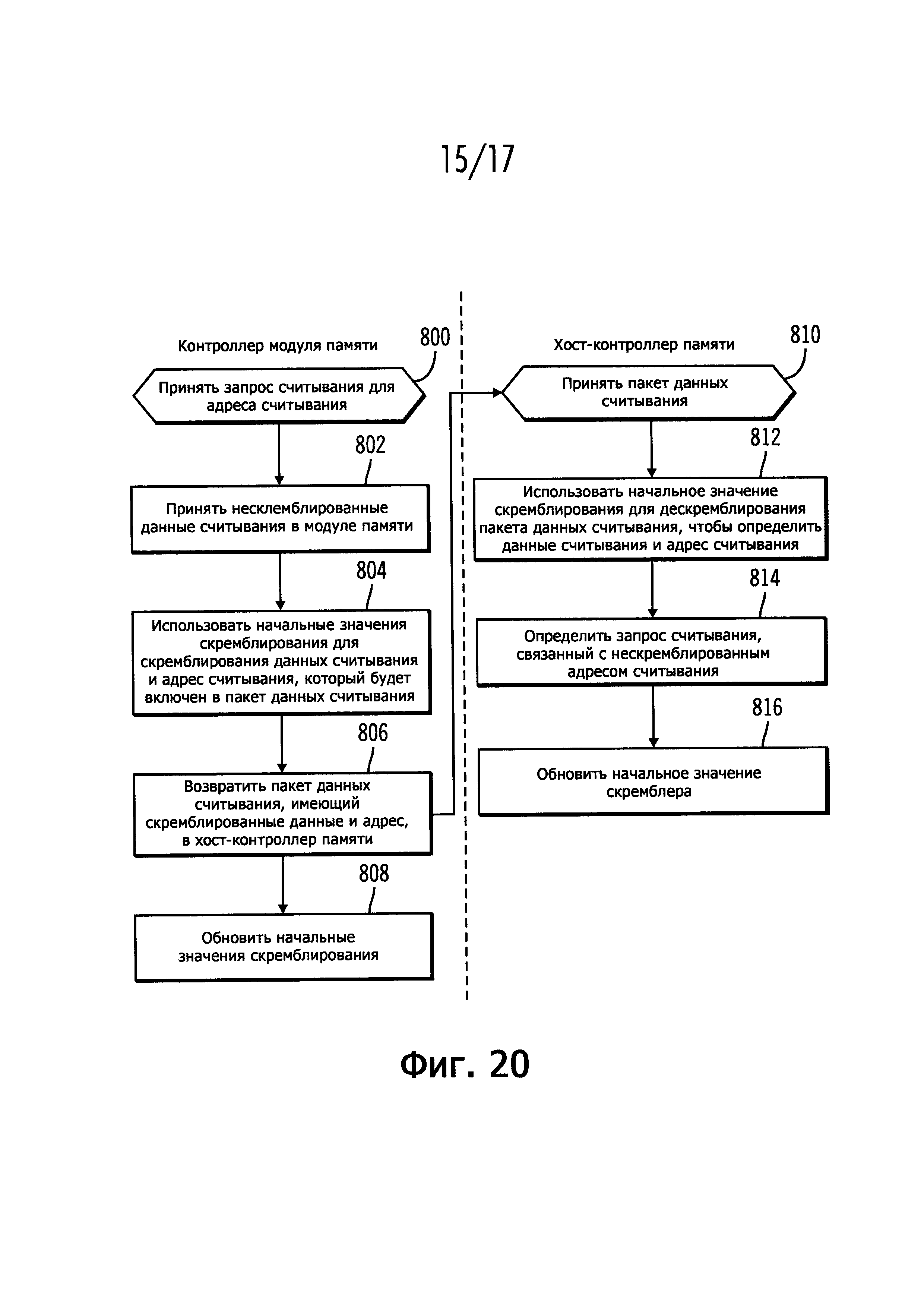

Фиг. 20 иллюстрирует вариант осуществления операций для скремблирования и дескремблирования данных, переданных по шине.

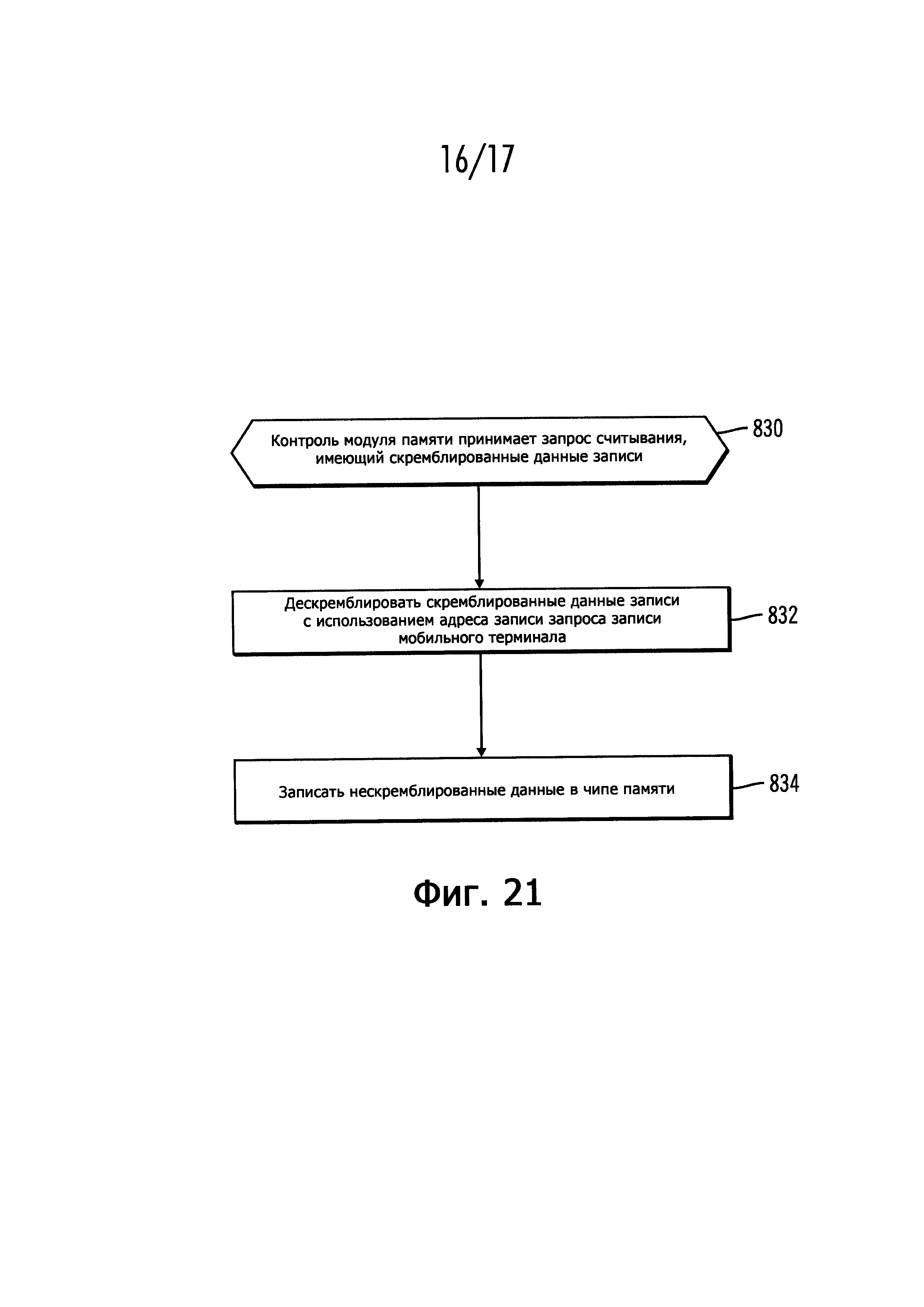

Фиг. 21 иллюстрирует вариант осуществления операций для дескремблирования данных записи в модуле памяти.

Фиг. 22 иллюстрирует вариант осуществления операций для установки параметра, показывающей конфигурацию интерфейса шины.

Фиг. 23 иллюстрирует вариант осуществления операции для выбора конфигурации интерфейса шины для обработки запроса передачи.

Описание вариантов осуществления

В последующем описании многочисленные специфические детали, такие как логические реализации, коды операций, средства для точного определения операндов, реализации разделения/совместного использования/дублирования ресурсов, типы и взаимосвязи компонентов системы и выбор разделения/интеграции логических схем изложены для того, чтобы обеспечить более полное понимание настоящего изобретение. Однако специалистам в данной области техники следует иметь в виду, что изобретение можно осуществить на практике без таких специфических подробностей. В других случаях, управляющие структуры, схемы уровней логических элементов и полные последовательности программных инструкций не описываются подробно, чтобы не загромождать описание изобретения. Специалисты в данной области техники, с помощью включенных описаний, смогут осуществить соответствующие функциональные возможности без излишнего экспериментирования.

Ссылки в описании на "один вариант осуществления", "вариант осуществления", "примерный вариант осуществления" и т.д. показывают, что вариант описанный осуществления может включать в себя конкретный признак, структуру или характеристику, но каждый вариант осуществления не обязательно должен включать в себя конкретный признак, структуру или характеристику. Более того, такие фразы не обязательно относятся к одному и тому же варианту осуществления.

В нижеследующем описании и формуле изобретения могут быть использованы термины "соединенный" и "связанный" вместе с их производными. Следует понимать, что эти термины не предназначены для использования в качестве синонимов друг для друга. Термин "соединенный" используется для обозначения того, что два или более элементов, которые могут или не могут находиться в непосредственном физическом или электрическом контакте друг с другом, действуют совместно или взаимодействуют друг с другом. Термин "связанный" используется, чтобы обозначения установления связи между двумя или более элементами, которые соединены друг с другом. Некоторые варианты осуществления относятся к электронным блокам устройств памяти. Варианты осуществления включают как устройства, так и способы для формирования электронных схем.

Фиг. 1 иллюстрирует вариант осуществления вычислительной системы 2, включающей в себя один или более процессоров 4, хост-контроллер 6 памяти и многочисленные модули 8а, 8b памяти, которые, как правило, устанавливаются на материнской плате. Процессоры 4 могут содержать центральное процессорное устройство, многоядерный процессор. Хост-контроллер 6 памяти, в ответ на запросы доступа к памяти от процессоров 4, устанавливает связь с многочисленными модулями 8а, 8b памяти по шине 10, которая также упоминается как канал, интерфейс шины и т.д., где оба модуля 8а, 8b памяти отдельно и независимо подсоединены к одной и той же шине 10. Хост-контроллер6 памяти может включать в себя счетчик 7 запросов, который увеличивает свое значение после приема сигнала запроса для гранта, чтобы использовать после последней выдачи грантов на основании на числа запросов, указанных в счетчике 7 запросов, счетчик 9 кредита записи, показывающий число или кредиты, разрешающие запросы записи, которые будут отправляться в один из модулей 8а, 8b памяти, и начальное значение 11 скремблирования, которое используется для дескремблирования запрошенных данных, считанных из одного из модулей 8а, 8b памяти.

В варианте осуществления, показанном на фиг. 1, модули 8а, 8b памяти установлены в слотах или гнездах памяти на материнской плате системы 2. Модули 8а, 8b памяти могут содержать одинаковые или различные типы модулей памяти, имеющих расположение выводов, совместимое с расположением выводов в слотах памяти на материнской плате. Кроме того, модули памяти могут поддерживать одинаковые или различные протоколы памяти, такие как протокол удвоенной скорости передачи данных четвертого поколения (DDR4), и дополнительные протоколы. Хотя показано только два модуля 8а, 8b памяти, можно предусмотреть многочисленные модули памяти.

Каждый из модулей 8а, 8b памяти включает в себя чипы 12а, 14а, 16а, 18а и 12b, 14b, 16b, 18b памяти, соответственно, на одной или обеих сторонах модуля памяти, для хранения данных. Чипы памяти, например, чипы DRAM, расположенные на одной или обеих сторонах корпуса модуля 8а, 8b памяти, содержат элементы хранения, которые хранят данные, используемые процессором 4.

Каждый модуль 8а, 8b памяти может включать в себя контроллер 20а, 20b модуля памяти для координации управления памяти и операцией доступа с помощью хост-контроллер 6 памяти. Хост-контроллер 6 памяти включает в себя логическую схему для управления операциями считывания и записи и операциями управления памятью по отношению к модулям 8а, 8b памяти, которые подсоединены к шине 10, и взаимодействуют с процессором 4 в модулях 8а, 8b памяти. Хост-контроллер 6 памяти можно выполнить как единое целое с процессором 4 или реализовать в виде логической схемы, отдельной от процессора 4 на материнской плате системы 2.

Материнская плата системы 2 может включать в себя гнездо памяти, совместимое с различными типами чипов памяти, обеспечивая различные типы модулей 8а, 8b памяти, поддерживающих различные типы устройств памяти, поддерживающих различные протоколы памяти до тех пор, пока различные типы модулей 8а, 8b памяти не будут совместимы с архитектурой выводов в гнездах памяти.

В одном варианте осуществления модули 8а, 8b памяти могут содержать один и тот же или другой тип динамических запоминающих устройств с произвольной выборкой (DRAM). В одном варианте осуществления модули 8а, 8b памяти могут содержать модули памяти с двухрядным расположением выводов (DIMM), такие как небуферные DIMM (UDIMM), модуль памяти с двухрядным расположением выводов с пониженной нагрузкой (LRDIMM), малогабаритный модуль памяти с двухрядным расположением выводов (SODIMM) и т.д. Модули 8а, 8b памяти можно реализовать в виде различных типов памяти, включающих в себя, но не ограниченных этим, NAND (флэш) память, ферроэлектрическое оперативное запоминающее устройство (FeTRAM), энергонезависимую память на основе нанопроволок, трехмерную (3D) память на основе точек пересечения, такую как память на фазовых переходах (РСМ), память, включающую в себя технологию мемристора, магниторезистивную память с произвольным доступом (MRAM), перенос спинового момента (STT)-MRAM и т.д.

В некоторых вариантах осуществления, так как различные типы модулей 8а, 8b памяти можно установить и подсоединить к шине 10, модули 8а, 8b памяти могут поддерживать различные протоколы. Например, модуль 8а памяти может содержать тип DIMM, соответствующий протоколу удвоенной скорости передачи данных четвертого поколения (DDR4) для статической DRAM (SDRAM), и модуль 8b памяти может использовать другой протокол, но несовместимый на одной и той же шине 10 с модулем 8а памяти, использующим протокол DDR4. Альтернативные и различные протоколы могут быть также использованы и реализованы в модулях 8а, 8b памяти.

Если модули 8а, 8b памяти поддерживают различные протоколы DRAM, то хост-контроллер 6 памяти выполнен с возможностью поддержания связи с использованием различных протоколов по шине 10, первого протокола, специфического для модуля 8а памяти, например, DDR4, и второго протокола памяти, специфического для модуля 8b памяти. Запросы на считывание и управление для модуля 8а памяти осуществляются с помощью первого протокола памяти и для второго модуля 8b памяти с использованием второго протокола памяти.

На фиг. 2 показаны дополнительные подробности варианта осуществления модуля 8 памяти, такого как модули 8а, 8b памяти, который включает в себя контроллер 20 модуля памяти, выполняющий операции модуля памяти и инструкции с помощью хост-контроллера 6 памяти. В некоторых реализациях, один из модулей памяти, например, 8b, может включать в себя модуль памяти, показанный на фиг. 2, и другой модуль памяти, например, 8а, может не включить в себя контроллер 20 модуля памяти, такой как модуль 8а памяти, соответствующий стандарту DDR4. В таких вариантах осуществления модуль 8а памяти может включать в себя регистр, такой как в случае RDIMM, или буфер, такой как в случае LRDIMM.

Модуль 8 памяти может включать в себя регистры 22 режима работы в контроллере модуля памяти, имеющем данные, которые можно сконфигурировать, используя команду установки регистра режима (MRS), буфер 24 считывания для буферизации данных считывания, возвращенных в хост-контроллер 6 памяти в ответ на команду считывания, регистр 26 операций управления электропитанием, показывающий операции управления электропитанием, которые будут выполняться, буфер 28 записи для буферизации данных записи перед записью в чипы 12, 14, 16, 18 памяти, счетчик 30 кредитов записи, показывающий число кредитов записи, которые необходимо возвратить в хост-контроллер 6 памяти, начальное значение 32 скремблирования, которое используется для рандомизации данных считывания, передаваемых по шине 10 в хост-контроллер 6 памяти, и параметр 34 интерфейса, идентифицирующий поддерживаемую конфигурацию интерфейса шины 10. Буферы и параметры 24, 26, 28, 30, 32 и 34 можно реализовать в контроллере 20 модуля памяти, или в схеме, внешней к контроллеру 20 модуля памяти в модуле 8 памяти. Некоторые из параметров 26, 30, 32 и 34 можно реализовать в регистрах 22 режима.

В некоторых вариантах осуществления модуль 8а памяти может содержать ближнюю память, которая сконфигурирована как уровень кэширования для дальней памяти, содержащей модуль 8b памяти. В такой конфигурации модуль 8а ближней памяти должен иметь эффект уменьшения времени доступа адресов памяти системы, к которым наиболее часто осуществляется доступ, причем специфический модуль 8b дальней памяти предназначен для кэширования. Устройства ближней памяти можно сконфигурировать как кэш с прямым отображением для их прототипов дальней памяти.

Описанные варианты осуществления контроллера 20 модуля памяти и хост-контроллера 6 памяти могут кодировать в логической схеме аппаратных средств, например, в специализированной интегральной микросхеме (ASIC), программируемой логической матрице типа FPGA (FPGA) и т.д.

Элементы вариантов осуществления настоящего изобретения можно также выполнить в виде машиночитаемого носителя информации для хранения машиноисполняемых инструкций. Машиночитаемый носитель информации может включать в себя, но не ограничиваться этим, флэш-память, оптические диски, постоянное запоминающее устройство на основе компакт-дисков (CDROM), ROM на основе цифровых универсальных/видеодисков (DVD), оперативное запоминающее устройство (RAM), стираемая программируемая постоянная память (EPROM), электрически стираемая программируемая постоянная память (EEPROM), магнитные или оптические карты, среды распространения или другой тип машиночитаемых носителей информации, подходящих для хранения электронных инструкций. Например, варианты осуществления изобретения могут быть загружены в виде компьютерной программы, которая может передаваться из удаленного компьютера (например, сервера) в запрашивающий компьютер (например, клиент) посредством сетевой передачи.

Фиг. 3 иллюстрирует расположение выводов в модуле 8а, 8b памяти с помощью хост-контроллера 6 памяти, линии шины 10 и модулей 8а, 8b памяти, где такие обозначения выводов описаны ниже или известны в технике.

Функции кодирования в сигнале запроса

В некоторых вариантах осуществления контроллер 20 модуля памяти может отправить сигнал запроса, например, REQ# 50, в хост-контроллер 6 памяти, чтобы показать, что существуют данные в буфере 24 считывания для хост-контроллера 6 памяти для возврата в виде части команды считывания. Сигнал запроса может содержать сигнал 50 разрешения подачи тактовых импульсов (СКЕ) REQ#, показанный на схеме расположения выводов, показанной на фиг. 3. Контроллер 18 модуля памяти может передавать сигнал запроса с минимальной длительностью импульса, чтобы гарантировать обнаружение хост-контроллером 6 памяти, который в определенных реализациях может содержать два тактовых цикла. Контроллер 20 модуля памяти может дополнительно кодировать дополнительную функцию в сигнале запроса, которую должен выполнять хост-контроллер 6 памяти. Путем кодирования дополнительных функций в сигнале запроса многочисленные функции можно показать в виде одного сигнала для того, чтобы максимизировать число операций и информацию, передаваемую в одиночном сигнале.

Фиг. 4 иллюстрирует вариант осуществления операций, выполняемых хост-контроллером 6 памяти и контроллером 20 модуля памяти, чтобы использовать сигнал запроса для передачи дополнительных функций в хост-контроллер 6 памяти. После инициирования (на этапе 100) операции для выработки сигнала запроса, который может быть частью команды считывания для передачи данных из буфера 24 считывания обратно в хост-контроллер 6 памяти, контроллер 20 модуля памяти определяет (на этапе 102) функцию, которую будет включать в себя сигнал запроса, причем функцию может показывать дополнительные операции, которые должен выполнить хост-контроллер 6 памяти, такие как специфическое условие ошибки или прерывание или другие функции. Контроллер 20 модуля памяти затем определяет (на этапе 104) длительность импульса, которая используется для того, чтобы показать или закодировать определенную функцию. Например, длительность импульса, равная минимальной длительности импульса, которая должна гарантировать обнаружение с помощью хост-контроллера 6 памяти сигнал запроса, можно использовать для того, чтобы показать или закодировать первую функцию, дополнительные длительности импульса, которые больше, чем минимальная длительность импульса, можно использовать для того, чтобы показать дополнительные функции. Например, если минимальная длительность импульса, которая должна гарантировать обнаружение, равна двум тактовым импульсам, то эта минимальная длительность импульса для сигнала запроса может показывать одну функцию, и длительности импульсов 6, 10 и 14 могут показывать еще одни дополнительные различные функции. Длительность импульса 14 может показывать катастрофический отказ. Кроме того, различные длительности импульсов для сигнала запроса, связанного с различными функциями, можно разделить на минимальное число тактовых импульсов, таких как 3 тактовых импульса в некоторых вариантах осуществления, чтобы гарантировать правильное обнаружение длительности импульса с помощью хост-контроллера 6 памяти. Контроллер 20 модуля памяти вырабатывает (на этапе 106) сигнал запроса, имеющий определенную длительность импульса для отправки в хост-контроллер 6 памяти.

После обнаружения (на этапе 108) сигнала запроса REQ0# на выводе 50, имеющего минимальную или первую длительность импульса, например, 2 тактовых импульса, хост-контроллер 6 памяти увеличивает значение (на этапе 110) счетчика 7 запросов, показывающего число сигналов гранта, которые необходимо отправить в модуль 8b памяти, отправляющий сигнал запроса. После увеличения значения счетчика 7 запросов хост-контроллер 6 памяти может ожидать до тех пор, пока слот на шине 10, то есть, на шине данных, не станет доступным для выдачи многочисленных запросов гранта, чтобы запросы, показанные в счетчике 7 запросов, обрабатывались в пакете в различные случайные периоды времени. После приема сигнала гранта контроллер 20 модуля памяти отправляет (на этапе 112) данные в буфере 24 считывания в хост-контроллер 6 памяти, чтобы обеспечить сбор и буферизацию данных в ответ на запрос считывания из хост-контроллера 6 памяти.

После определения минимальной или первой длительности импульса сигнала 50 запроса, если сигнал 50 запроса (на этапе 114) не продолжаться дольше измеренной минимальной длительности импульса, то управление заканчивается. В противном случае, если (на этапе 116) измеренный сигнал запроса не превышает вторую длительность импульса, например, 6 тактовых импульсов, то хост-контроллер 6 памяти может исполнить (на этапе 118) вторую функцию, связанную со второй длительностью импульса. В противном случае, если (на этапе 120) сигнал 50 запроса не превышает измеренной третьей длительности импульса, например, 10 тактовых импульсов, то хост-контроллер 6 памяти может исполнить (на этапе 122) третью функцию, связанную с третьей длительностью импульса. Если длительность импульса остается прежней, и измерена (на этапе 124) четвертая длительность импульса, например, 14 тактовых импульсов, то хост-контроллер 6 памяти может исполнить (на этапе 126) для хост-контроллера 6 памяти обработку катастрофического отказа, которая должна быть выполнена.

Хотя описанные варианты осуществления касаются четырех функций для четырех различных длительностей импульсов сигнала запроса, в некоторых реализациях может быть больше или меньше четырех функций, представленных с помощью более или менее четырех длительностей импульсов. Кроме того, одна длительность импульса может показывать ряд многочисленных функций, которые необходимо выполнить.

В операциях, показанных на фиг. 4, функции, непредусмотренные начальной функцией гранта запроса, обрабатываются только после определения того, что длительность импульса не превышает длительность импульса, связанную с этими дополнительными функциями. В альтернативном варианте осуществления каждую дополнительную функцию можно исполнить после измерения длительности импульса, связанной с этой функцией даже в том случае, если длительность импульса превышает измеренную длительность импульса, поэтому каждая функция исполняется в виде измерений длительности импульса, которая продолжается за пределы длительности импульса запуска.

С помощью описанного варианта осуществления, показанного на фиг. 4, различные функции можно закодировать в виде сигнала запроса с помощью контроллера 20 модуля памяти с использованием различных длительностей импульсов для контроллера модуля памяти, которые можно быть разделить на минимальное число тактовых импульсов, которое гарантируют обнаружение длительности импульса с помощью хост-контроллера 6 памяти. Таким образом, в единственном сигнале запроса контроллер 20 модуля памяти может сигнализировать о сигнале запроса, таком как запрос на возврат данных из буфера 24 считывания, и об одной из множества различных функций.

Регулировка таймирования сигнала на выходе первого модуля памяти на основании различий компонентов с помощью второго модуля памяти для согласования таймирования из второго модуля памяти

В некоторых реализациях, модули 8а и 8b памяти могут содержать различные типы модулей памяти, которые имеют различные компоненты. Например, модуль 8а памяти может или не может включать в себя регистры и буферы данных, не включенные в модуль 8b памяти, и наоборот, и модули 8а, 8b памяти могут поддерживать различные протоколы памяти. Описанные варианты осуществления обеспечивают технологии для одного модуля памяти, такого как 8b, для регулировки его таймирования, чтобы согласовать его с другим модулем памяти, например, 8а, таким образом, чтобы хост-контроллер 6 памяти нельзя было отрегулировать на различные таймирования из различных модулей памяти, таких как различные типы DIMM. При наличии контроллера 20а, 20b модуля памяти, который производит регулировки таймирования, предотвращаются чрезмерные циклы безостановочной работы и потеря производительности в хост-контроллере памяти.

Фиг. 5 иллюстрирует вариант осуществления операций, выполняемых контроллером 20 модуля памяти, таким как контроллер 20b модуля памяти, для регулировки таймирования выходного сигнала на основании различий компонентов с другими модулями 8а, 8b памяти на шине 10. После инициирования (на этапе 200) операция для вывода данных из буфера 24 данных, контроллер 20b модуля памяти определяет (на этапе 202) регулировку таймирования на основании по меньшей мере одного компонента в по меньшей мере одном из модулей 8а, 8b памяти на канале. Этапы 204-208 обеспечивают вариант осуществления операций определения регулировки таймирования. Контроллер 20b модуля памяти может ускорить (на этапе 204) таймирование в ответ на первый модуль 8b памяти, имеющий по меньшей мере один компонент, приводящий в действие таймирование выходного сигнала, который не включен в другой второй модуль 8а памяти. Кроме того, можно добавить (на этапе 206) задержку в таймирование в ответ на другой второй модуль 8а памяти на шине 10, имеющей по меньшей мере один компонент, приводящий в действие таймирование выходного сигнала второго модуля 8b памяти, который не включен в первый модуль 8b памяти.

Контроллер 20b модуля памяти может затем определить (на этапе 208) регулировку чистого таймирования с любой добавленной задержкой или ускорением таймирования. Контроллер 20b модуля памяти регулирует (на этапе 210) таймирование выходного сигнала, поступающего из буфера 24 данных в хост-контроллер 6 памяти, на основании определенной регулировки таймирования для согласования таймирования выходного сигнала во втором модуле 8а памяти.

Например, если модуль 8b памяти, включающий в себя контроллер 8b, выполняющий вычисления, включает в себя буфер 24 данных, необнаруженный в другом модуле 8а памяти, то регулировка таймирования может содержать ускорение таймирования выходного сигнала, когда другой второй модуль 8а памяти не включает в себя буфер данных, такой как включенный в первый модуль 8b памяти. В другой реализации, если другой модуль 8а памяти имеет регистр, не включенный в модуль 8b памяти, выполняющий вычисления, например, в случае RDIMM, то регулировка таймирования содержит задержку таймирования выходного сигнала, предназначенного для регистра в другом модуле 8а памяти, не включенном в модуль 8b памяти, который производит вычисления. Если бы ускорение таймирования для буфера 24 данных было бы больше, чем задержка, добавленная для регистра в другом модуле 8а памяти, то регулировка чистого таймирования содержала бы ускорение таймирования. Аналогично, если бы добавленная задержка была бы больше, чем ускорение, то чистая регулировка содержала бы добавление задержки к таймированию. Если модуль 8b памяти, производящий вычисления, не включает в себя регистры или буферы 24 данных, включенные в другой модуль памяти, например, если другой модуль 8а памяти представляет собой RDIMM и LRDIMM, то контроллер 20b модуля памяти может задержать таймирование с учетом задержек, вызванных дополнительными компонентами в другом модуле 8а памяти.

Модули 8а, 8b памяти могут иметь различные типы компонентов по своей команде, адрес и шины управления в шине 10, если они содержат различные типы DIMM, такие как UDIMM, RDIMM и LRDIMM.

В некоторых описанных вариантах осуществления выход, для которого регулируется таймирование, содержит выход данных на шине данных в шине 10 из буфера 24 данных. В альтернативных вариантах осуществления отрегулированные выходные сигналы могут содержать выходной сигнал, который отличается от выходного сигнала передачи данных.

Хотя операции, описаны по отношению к одному модулю памяти, выполняющему регулировки таймирования, один или несколько модулей 8а, 8b памяти на шине 10 могут выполнять регулировки таймирования, показанные на фиг. 5.

С помощью описанных регулировок таймирования контроллер 20b модуля памяти может регулировать таймирование на своем выходе, например, на выходе буфера 24 данных, чтобы согласовать сигнал таймирования, подаваемый из другого модуля 8а памяти с аналогичными типами выходных сигналов с тем, чтобы хост-контроллеру 6 памяти не нужно было выполнять какие-либо регулировки таймирования, чтобы приспособиться к различным конфигурациям различных модулей 8а, 8b памяти на шине 10.

Использование кодирования регистров в команде установки регистра режима работы (MRS)

Контроллер 20 модуля памяти может включать в себя регистры 22 режима работы. В некоторых вариантах осуществления контроллер 20b модуля памяти может реализовать первый протокол, который отличается от второго протокола памяти, используемого в другом контроллере 8а, таком как DDR 4. Однако контроллер 20b модуля памяти может поддержать некоторые команды из второго протокола другого модуля 8а памяти, такого как DDR4, например, команду установки регистра режима работы (MRS), и еще использовать команду для различных целей, которая отличается от той, которая используется контроллером 20а модуля памяти, реализующим первый протокол памяти.

Фиг. 6 иллюстрирует вариант осуществления команды 250 MRS, которая может или не может включать в себя поля MRS из другого протокола памяти, такого как DDR4. Команда 250 точно определяет код 252 операции, показывающий операцию MRS. Регистры А0-А13 адреса можно использовать для предоставления данных для одного из регистров 22 режима работы в контроллере 20 модуля памяти, и разряды 254 регистра показывают регистр 22 режима работы, в который необходимо записать данные с адресами А0-А13. Например, если имеется 16 регистров 22 режима работы, то четыре разряда 254 регистров, такие как BA0, ВА1, BG0, BG1, могут показывать один из 16 регистров 22 режима работы в контроллере 20 модуля памяти для дальнейшего использования.

В одном варианте осуществления команда 250 MRS может содержать однотактную команду, которую можно использовать для обеспечения параметров конфигурации в модуле 8 памяти перед подготовкой шины 10 к операциям, производимым на шине, таким как операции считывания и записи, которые могут содержать двухтактные команды. Таким образом, команда 250 MRS использует адресные входные сигналы А0-А17, показанные на схеме разводки выводов (фиг. 3) в виде линии 52, и командные входные сигналы BG1:0 и ВА1:0, которые показаны в виде линий 54 и 56, соответственно, на схеме разводки выводов (фиг. 3). В некоторых вариантах осуществления адресные входные сигналы А14-16 содержат код операции команды MRS.

Фиг. 7 иллюстрирует вариант осуществления операций, выполняемых хост-контроллером 6 памяти и контроллером 20 модуля памяти для программирования регистров 22 режима работы в контроллере 20 модуля памяти. Во время инициализации, например, перед подготовкой шины 10 к считыванию и операциям, которые могут содержать команды, отправленные в двух тактовых импульсах, хост-контроллер 6 памяти может выработать (на этапе 280) и отправлять команду 250 MRS, чтобы показать регистр 22 режима работы в контроллере 20 модуля памяти для конфигурирования с данными, включенными в поля А13:0 адреса, которые может отправить команда 250 MRS в одном тактовом цикле.

Контроллер 20 модуля памяти принимает (на этапе 282) команду 250 MRS и определяет (на этапе 284) регистр 22 режима работы, показанный в разрядах 254 регистра на линиях 34 и 35 (фиг. 3). Контроллер 20 модуля памяти затем считывает (на этапе 286) данные, представленные в разрядах А0:А13 адреса в определенном регистре 22 режима работы.

Хост-контроллер 6 памяти может дополнительно использовать команду 250 MRS согласно протоколу DDR4, которая отправляется в модуль памяти, например, модуль 8а памяти, реализующий протокол DDR4, для программирования один из восьми регистров режима работы на одном из чипов 12а, 14а, 16а, 18а памяти, где разряды ВА0, ВА1, BG0 регистра идентифицируют регистр режима работы в чипе памяти, и разряд BG1 показывает, инвертированы ли разряды. Таким образом, хост-контроллер 6 памяти может использовать тот же самый формат команды MRS для контроллеров 20а, 20b памяти, реализующих различные протоколы памяти для того, чтобы вызвать различные операции согласно различным протоколам. Например, когда команда 250 MRS используется для модуля 8а памяти, поддерживающего DDR4, команда 250 MRS записывает данные в регистр режима работы в одном из чипов 12а, 14а, 16а, 18а памяти. После использования для модуля памяти 8b регистров 22 режима работы в контроллере 20 модуля памяти, команда 250 MRS записывает данные в регистры 22 режима работы в контроллере 20 модуля памяти, а не в чипы 12, 14, 16, 18 DRAM. Таким образом, хост-контроллер 6 памяти может использовать тот же самый формат команды MRS с модулями памяти, поддерживающими различные протоколы памяти, например, DDR4 и некоторый другой протокол.

Прием модулем памяти второй половины команды в случае, когда сигнал выбора чипа принимается только для первой половины команды

Описанные варианты осуществления обеспечивают технологии для модуля памяти для приема команды в многочисленных частях, например, в двух половинах, при наличии только приема одного сигнала выбора чипа для модуля 8 памяти таким образом, чтобы модуль 8 памяти автоматически принимал вторую половину команды в интервале задержки с момента, когда была отправлена первая половина команды. Дополнительные варианты осуществления обеспечивают технологии для слияния задержки для того, чтобы автоматически принимать вторую половину команды в высокоскоростном режиме таймирования, например, таймирования 2N, когда модуль 8а, 8b памяти работает на более высоких скоростях в отличие от режима регулярного таймирования, например таймирования 1N.

В некоторых вариантах осуществления команды занимают два разряда в канале и отправляются с тактовыми импульсами, следующими друг за другом. Это позволяет отправить весь адрес в одной команде вместо двух, например, отправить информации о строках и столбцах в одной команде. Контроллер 20 модуля памяти выполнен с возможностью узнавать о высокоскоростном режиме таймирования (2N) через хост-контроллер 6 памяти, который программирует регистры 22 режима работы в контроллере 20 модуля памяти.

На фиг. 8 представлен вариант осуществления временной диаграммы для режима регулярного таймирования, например таймирования 1N, для команд, таких как команды считывания, которые отправляются в двух частях, показанных как CMD0a, CMD0b, CMD1a, CMD1b, CMD2a, CMD2b. Хост-контроллер 6 памяти может поместить первую половину команды CMD0a и сигнала S0# 302 выбора чипа, также показанного в виде линии 58 S0# на фиг. 3, на шине на тактовом цикле 300 для первого модуля 8а памяти. Первый модуль 8а памяти может принять первую половину команды CMD0a на цикле 300 после приема сигнала 302 выбора чипа и может дополнительно автоматически принять вторую половину команды CMD0b в интервале задержки от первой половины команды CMD0a, такой как один тактовый цикл, позже в тактовом цикле 304.

Хост-контроллер 6 памяти может поместить первую половину команды CMD1a и сигнал S2# 306 выбора чипа, также показанный как линия 60 S2# на фиг. 3, на шине на тактовом цикле 308, чтобы выбрать второй модуль памяти 8b. Второй модуль памяти 8b может принять первую половину команды CMD1a в цикле 308 после приема сигнала 306 выбора чипа и может дополнительно автоматически принять вторую половину команды CMD1b на один тактовый цикл позже в цикле 310.

На фиг. 9 представлен вариант осуществления временной диаграммы для высокоскоростного режима таймирования для более высоких скоростей, чем регулярное таймирование, например, таймирование 2N, где обе части каждой команды, показаны как CMD0a, CMD0b, CMD1a, CMD1b, CMD2a, CMD2b, остаются на шине 10 для двух тактовых циклов. Хост-контроллер 6 памяти может поместить первую половину команды CMD0a на шине на тактовом цикле 320 для двух циклов и разместить сигнал S0# 322 выбора чипа, также показанный как линия 38 S0# на фиг. 3, на шине на тактовом цикле 324 для первого модуля 8а памяти, таком как один цикл с момента, когда, первая половина команды CMD0a была размещена на шине 10, таким образом осуществляя задержку сигнала выбора чипа в высокоскоростном режиме таймирования. Хост-контроллер 6 памяти может поместить первую половину команды CMD0a на шине на тактовом цикле 320 для двух циклов и разместить сигнал S0# 322 выбора чипа, также показанный как линия 38 SO# на фиг. 3, на шине на тактовом цикле 324 для первого модуля 8а памяти, таком как один цикл с момента, когда первая половина команды CMD0a была размещена на шине 10, таким образом осуществляя задержку сигнала выбора чипа в высокоскоростном режиме таймирования. Первый модуль 8а памяти может принять первую половину команды CMD0a в тактовом цикле 324 при приеме сигнала 322 выбора чипа и может дополнительно автоматически принять вторую половину команды CMD0b с интервалом задержки, показанном в виде двух тактовых циклов сигнала 322 выбора чипа, в начале тактового цикла 328.

Хост-контроллер 6 памяти может поместить первую половину команды CMD1a на цикле 330 и сигнал S2# 332 выбора чипа, также показанный как линия 60 S2# на фиг. 3, на один цикл позже цикла 332 для второго модуля памяти 8b. Второй модуль памяти 8b может принять первую половину команды CMD1a на тактовом цикле 336 из сигнала выбора чипа 332 и может дополнительно автоматически считать вторую половину команды CMD1b на два тактовых цикла позже в цикле 338. Таким образом, хост-контроллер 6 памяти задерживает на половину тактовый цикл сигнал чипа на протяжении первой половины команды, и контроллера 20 модуля памяти задерживает считывание второй половины двух циклов команды после считывания первой половины команды.

Фиг. 10 иллюстрирует вариант осуществления операций, выполняемых хост-контроллером 6 памяти и контроллером 20 модуля памяти для режима таймирования 1N для команд, занимающих два разряда на смежных циклах. Хост-контроллер 6 памяти может запрограммировать контроллер 20 модуля памяти по разрядам в регистрах 22 режима во время инициирования работы в режиме таймирования 1N. После инициирования (на этапе 350) двухцикловая команда в режиме регулярного таймирования 1N хост-контроллер 6 памяти размещает (на этапе 352) первую половину команды (один цикл) на шине 10 в первом тактовом цикле. Команда выбора чипа также размещается (на этапе 354) на шине 10 в первом тактовом цикле. После того, как контроллер 20 модуля памяти обнаруживает (на этапе 356) сигнал выбора чипа, направленный в конкретный модуль 8 памяти, включающий в себя контроллер 20 модуля памяти при программировании в режиме регулярного таймирования, контроллер 20 модуля памяти принимает (на этапе 358) первую половину команды на шине 10 в первом тактовом цикле.

Кроме того, хост-контроллер 6 памяти размещает (на этапе 360) вторую половину команды (в смежном цикле относительно первой половины) на шине 10 во втором тактовом цикле - один тактовый цикл относительно первого тактового цикла. Модуль 8 памяти, выбранный с помощью сигнала выбора чипа, принимает (на этапе 362) вторую половину команды на шине 10 во втором тактовом цикле за счет ожидания задержки на один цикл с момента, когда был принят сигнал выбора чипа и была получена первая половина команды. Контроллер 20 модуля памяти автоматически принимает вторую половину команды на шине 10, не требуя доступа сигнала выбора чипа к шине 10.

Фиг. 11 иллюстрирует вариант осуществления операций, выполняемых хост-контроллером6 памяти и контроллером 20 модуля памяти для режима высокоскоростного таймирования, например, 2N, для команд, занимающих два разряда на смежных циклах. Контроллер 20 модуля памяти можно программировать по разрядам в регистрах 22 режима работы во время инициирования работы в режиме высокоскоростного таймирования. После инициирования (на этапе 380) двухцикловая команда в режиме высокоскоростного таймирования, хост-контроллер 6 памяти размещает (на этапе 382) первую половину команды (один цикл) на шине 10 в первом тактовом цикле. Затем размещается (на этапе 384) сигнал выбора чипа на шине 10 во втором тактовом цикле, который может представлять собой один тактовый цикл относительно первого тактового цикла. Таким образом, сигнал выбора чипа размещается на шине с задержкой, такой как один тактовый цикл, относительно размещения первой половины команды. После того как контроллер 20 модуля памяти обнаруживает (на этапе 386) сигнал выбора чипа, направленный в конкретный модуль 8, при программировании в режиме высокоскоростного таймирования контроллер 20 модуля памяти принимает (на этапе 388) первую половину команды на шине 10 во втором тактовом цикле с задержкой.

Кроме того, хост-контроллер 6 памяти размещает (на этапе 390) вторую половину команды (два цикла относительно первой половины) на шине 10 в третьем тактовом цикле - два цикла относительно первого тактового цикла. Контроллер 20 модуля памяти в модуле 8 памяти, выбранном с помощью сигнала выбора чипа, принимает (на этапе 392) вторую половину команды на шине 10 в четвертом тактовом цикле путем ожидания задержки на два цикла с момента, когда был принят сигнал выбора чипа, и была получена первая половина команды. Контроллер 20 модуля памяти может автоматически принимать вторую половину команды, без ожидания сигнала выбора чипа на шине 10.

Описанные варианты осуществления предусматривают задержку сигнала выбора чипа на один тактовый сигналом в режиме высокоскоростного таймирования, например, таймирования 2N, относительно отправки первой половины команды. Кроме того, модуль памяти может автоматически принимать вторую половину двух тактовых сигналов команды после сигнала выбора чипа. Эта задержка сигнала выбора чипа позволяет обеспечить дополнительное время установки в высокоскоростном режиме. Задержка для приема второй половины команды позволяет обеспечить автоматический прием команды, не требуя сигнала выбора чипа.

В альтернативных вариантах осуществления сигнал выбора чипа можно разместить на шине, и вторую половину команды может получить в интервалах, которые отличаются от описанного одного тактового сигнала. Кроме того, в альтернативных вариантах осуществления команды могут состоять из более чем двух частей (например, разрядов) и использовать более двух тактовых циклов, и модуль 8а, 8b памяти может автоматически принимать более одной дополнительной части команды в интервалах с задержкой тактового сигнала относительно сигнала выбора чипа, не требуя при этом приема дополнительных сигналов выбора чипа.

Определение того, как установить старшие разряды адреса в модуле памяти

Контроллер 20 модуля памяти может конфигурировать для работы в модулях 8 памяти, имеющих различные конфигурации выводов и интерфейса, например, в одном модуле памяти, имеющем больше выводов для адресации, чем другой модуль памяти, имеющий меньше выводов, такой как SO-DIMM. Модуль памяти с меньшим количеством выводов адресации может обеспечить меньшее адресное пространство, чем модуль памяти, имеющий больше выводов, доступных для адресации. Поддерживаемая конфигурация интерфейса может изменяться из-за возможностей хост-контроллера 6 памяти и шины 10 или может изменяться из-за возможностей конфигурации выводов и интерфейса модуля 8 памяти, например, SO-DIMM или UDIMM.

Для таких вариантов осуществления контроллер 20 модуля памяти может использовать один из регистров 22 режима работы для указания поддерживаемых конфигураций интерфейса, например, для указаний того, имеет или нет модуль памяти выводы, доступные для старших разрядов адреса. В таком случае, если контроллер 20 модуля памяти работает в модуле 8, не имеющем одного или более выводов для старших разрядов адреса, доступных другим модулям памяти, то контроллер 20 модуля памяти будет использовать предварительно определенное значение, такое как ноль, для этих старших разрядов адреса, недоступных в модуле. Таким образом, контроллер 20 модуля памяти присваивает значение, равное нулю, для старших разрядов адреса тогда, когда отсутствуют выводы для приема значений этих старших разрядов адреса. В одном варианте осуществления старшие разряды адреса могут содержать разряд А17 52 адреса и разряд С2:0 62 адреса, показанные на схеме расположения выводов на фиг. 3. Некоторые модули памяти, такие как SO-DIMM, могут не включать в себя выводы 52 и 62.

Фиг. 12 иллюстрирует вариант осуществления операций, выполняемых контроллером 20 модуля памяти для конфигурирования настроек для адресации. Хост-контроллер 6 памяти может отправить сигнал MRS в модуль 8 памяти, показывающий поддерживаемую конфигурацию интерфейса. После приема (на этапе 400) сигнала MRS, показывающего поддерживаемую конфигурацию интерфейса, контроллер 20 модуля памяти может обновить регистр 22 режима работы, адресуемый сигналом MRS, чтобы показать поддерживаемую конфигурацию интерфейса, которая может показывать тип DIMM, например, SO-DIMM, UDIMM и т.д., или показывать то, что поддерживает интерфейс, например, поддерживаются или нет старшие разряды адреса. В ответ контроллер 20 модуля памяти устанавливает (на этапе 402) адресный регистр 22 режима работы, показывающий конфигурацию интерфейса для указания переданной конфигурации интерфейса, например, поддерживаются или нет старшие разряды адреса.

Фиг. 13 иллюстрирует вариант осуществления операций, выполняемых контроллером 20 модуля памяти для обработки адресации с использованием разрядов адреса более высокого уровня. После приема (на этапе 420) команды из хост-контроллера 6 памяти, имеющей разряды адреса, контроллер 20 модуля памяти определяет поддерживаемую конфигурацию интерфейса из регистра 22 режима работы, информация которого показывает, поддерживает ли текущий модуль 8 памяти адресацию в старших разрядов адреса. Если (на этапе 422) поддерживаемая конфигурация интерфейса не поддерживает старшие разряды адреса, например, модуль 8 памяти не имеет выводов 52 и 62, то по меньшей мере один из старших разрядов адреса для принятого адреса устанавливается на предварительно определенное значение, то есть предполагается, что старшие разряды адреса равны нулю тогда, когда отсутствуют выводы для старших разрядов адреса. Если (на этапе 422) поддерживаемая конфигурация интерфейса, показанная в регистре 22 режима работы, показывает, что старшие разряды адреса доступны, то контроллер 20 модуля памяти использует (на этапе 426) по меньшей мере один старший разряд адреса для адреса, имеющего по меньшей мере один вывод 52, 62 старшего разряда адреса.

В альтернативных вариантах осуществления контроллер 20 модуля памяти может подавать предварительно определенные значения для разрядов адреса, отличных от старших разрядов адреса, не имеющих выводов в модуле памяти.

Описанные варианты осуществления позволяют обеспечить работу контроллера модуля памяти в модулях памяти, имеющих различные конфигурации выводов, доступных для адресации, чтобы обеспечить разряды адреса высокого порядка для конфигурации модуля памяти, не имеющей выводы для обеспечения старших разрядов адреса. Таким образом, контроллер модуля памяти может применяться и работать в модулях памяти, таких как SO-DIMM и UDIMM, и обеспечивать полные возможности адресации для обеих конфигураций интерфейса.

Выполнение расширенных операций для сигнала СКЕ низкого уровня

Описанные варианты осуществления обеспечивают технологии, позволяющие выполнить предварительное конфигурирование операций управления электропитанием в модуле 8 памяти, которые должны выполняться в более позднее время, когда контроллер модуль памяти обнаружит сигнал низкого уровня, разрешающий подачу тактовых импульсов (СКЕ), на выводе СКЕ, таком как выводы 64 или 66, показанных на схеме расположения выводов на фиг. 3. Это позволяет обеспечить расширенный ряд операций управления электропитанием, которые будут выполняться после активации сигнала СКЕ низкого уровня, например, для перехода в предварительно определенное состояние пониженного энергопотребления.

Различные возможные состояния пониженного энергопотребления могут быть активированы после приема сигнала СКЕ низкого уровня в зависимости от ранее отправленной команды предварительного СКЕ. Такие показанные режимы могут содержать режимы, точно определенные в спецификации Усовершенствованного интерфейса управления конфигурацией и энергопотреблением ("ACPI"), например, состояние S3 ожидания, пониженного энергопотребления или приостановки в модуле 8 памяти, электропитание которого остается на более низком уровне, состояние S4 бездействия, где содержимое модуля 8 памяти сохраняется в энергонезависимой памяти, и модуль 8 памяти снижает электропотребление, и состояние S5, где модуль 8 памяти снижает электропотребление, хотя минимальное количество электроэнергии подается в блок питания. Энергонезависимая память, в которой хранится содержимое, может иметь различные виды, включающие в себя, но неограниченные этим, (флэш) память NAND, ферроэлектрическую память с произвольным доступом (FeTRAM), энергонезависимую память на основе нанопроволок, трехмерную (3D) память на основе точек пересечения, такая как память на фазовых переходах (РСМ), память, включающую в себя технологию мемристора, магниторезистивную память с произвольным доступом (MRAM), память на основе переноса спинового момента (STT)-MRAM.

Фиг. 14 иллюстрирует вариант осуществления операций, выполняемых хост-контроллером 6 памяти и контроллером 20 модуля памяти для облегчения операций управления электропитанием, использующих сигнал СКЕ низкого уровня. Для инициирования операций изменения режима управления электропитанием, таких как переход в один из различных распознанных режимов пониженного электропотребления, хост-контроллер 6 памяти отправляет (на этапе 500) команду предварительного СКЕ в контроллер 20 модуля памяти по шине 10, показывающую одну или более операций управления электропитанием. В одном варианте осуществления команда предварительного СКЕ может показывать одну или более специфических операций или обеспечить код, представляющий собой ряд операций. Например, команда предварительного СКЕ может показывать состояние управления электропитанием, такое как состояние системы или режим пониженного энергопотребления, например, состояния режимов пониженного энергопотребления S3, S4 и S5 ACPI, которые контроллер 20 модуля памяти может интерпретировать как ряд операций, которые необходимо выполнить для реализации этого состояния.

После приема (на этапе 502) команды предварительного СКЕ контроллер 20 модуля памяти устанавливает регистр 26 операций управления электропитанием, чтобы показать по меньшей мере одну операцию управления электропитанием, показанную в команде предварительного СКЕ. В последующий момент времени, когда хост-контроллеру 6 памяти требуется, чтобы модуль 8а, 8b памяти изменил состояния показанных операций управления электропитанием, хост-контроллер 6 памяти обеспечивает подачу (на этапе 506) сигнала 56 СКЕ низкого уровня, например, низкий уровень на выводах 64 или 66 (на фиг. 2). После обнаружения (на этапе 508) сигнала СКЕ низкого уровня, контроллер 20 модуля памяти определяет (на этапе 510), показывает ли регистр 56 операций управления электропитанием операции, которые необходимо выполнить, например, показывает ли состояние режима пониженного электропотребления или специфические операции. Если операции не показаны, такие как нуль или значение по умолчанию, контроллер 20 модуля памяти может выполнить (на этапе 512) операцию по умолчанию для обработки сигнала СКЕ низкого уровня, такую как операция деактивации внутренних тактовых сигналов, операция выключения питания перед зарядкой или операция автогенерации. Если операции или режим электропитания показаны в регистре 26, то контроллер 20 модуля памяти выполняет (на этапе 514) операции управления электропитанием, показанные в регистре 26, например, состояние пониженного энергопотребления.

Описанные варианты осуществления обеспечивают технологии для конфигурирования контроллера модуля памяти, чтобы выполнить ряд операций управления электропитанием в последующий момент времени с использованием сигнала СКЕ низкого уровня. После отправки команды предварительного СКЕ хост-контроллер 6 памяти будет подтверждать сигнал СКЕ низкого уровня для запуска более сложной операции управления электропитанием, чтобы изменить режима электропитания, который будет обычно запускаться в ответ на сигнал СКЕ низкого уровня. При использовании описанных вариантов осуществления требуется меньше сигналов для управления электропитанием, так как можно инициировать более сложную операцию управления электропитанием, такую как переход в режим пониженного электропотребления, с помощью сигнала СКЕ низкого уровня.

Предоставление кредитов записи для хоста-контроллера памяти для команд записи

Описанные варианты осуществления обеспечивают технологии для предоставления кредитов записи для хост-контроллера 6 памяти, которые будут использоваться для отправки команд записи путем включения кредитов записи в возвращенные пакеты данных считывания с целью уменьшения использования пропускной способности шины на шине 10.

Как показано на фиг. 1, хост-контроллер 6 памяти включает в себя счетчик 9 кредитов записи и будет только отправлять команды записи, когда счетчик 9 кредитов записи имеет положительные кредиты. Счетчик 9 кредитов записи уменьшать свое значение при отправке команды записи. Для каждого модуля 8а, 8b памяти можно предусмотреть по одному счетчику 9 кредитов записи. Модуль 8 памяти включает в себя буфер 28 записи для буферизации принимаемых данных записи, которые в дальнейшем разделяются на элементы хранения в чипах 12, 14, 16, 18 памяти. Контроллер 20 модуля памяти имеет счетчик 30 кредитов записи, показывающий накопленные кредиты записи для возврата в хост-контроллер 6 памяти. Кредиты записи используются для регулирования использования буфера 28 записи таким образом, чтобы хост-контроллер 6 памяти не отправлял данные записи, чтобы не переполнить буфер 28 записи.

Фиг. 15 иллюстрирует вариант осуществления операций для хост-контроллера 6 памяти и контроллера 20 модуля памяти для обработки команды записи. После выработки команды записи, хост-контроллер 6 памяти определяет (на этапе 602), больше ли нуля, не пустой ли, счетчик 30 кредитов записи. Если это так, то команда записи отправляется (на этапе 604) в модуль 8 памяти. Если (на этапе 602) счетчик 9 кредитов записи хоста является пустым, то хост-контроллер 6 памяти ожидает до тех пор, пока кредиты не станут доступными для отправки команды записи.

После приема (на этапе 610) команды записи, контроллер 20 модуля памяти буферизует (на этапе 612) данные записи в буфере 30 записи. После распределения (на этапе 614) данных записи из буфера 30 записи в элементы хранения в чипах 12, 14, 16, 18 памяти, контроллер 20 модуля памяти увеличивает значение (на этапе 616) счетчика 30 кредитов записи, показывая, что кредит необходимо возвратить в хост-контроллер 6 памяти, чтобы разрешить другую команду записи. Если (на этапе 618) счетчик 30 кредитов записи превышает пороговое значение, то контроллер 20 модуля памяти вырабатывает (на этапе 620) пакет данных считывания, показывающий данные считывания и показывающий по меньшей мере один из кредитов записи, указанных в счетчике 30 кредитов записи. Пакет данных считывания отправляется (на этапе 622) в хост-контроллер 6 памяти, и значение счетчика 30 кредитов записи уменьшается (на этапе 624) на число возвращенных кредитов. В некоторых вариантах осуществления число возвращенных кредитов может быть ограниченным, поэтому счетчик 30 кредитов записи может или не может уменьшить свое значение до нуля. Таким образом, если пакет считывания не отправляется в течение продолжительного периода времени, то контроллер 20 модуля памяти отправляет пакет данных считывания, не обеспечивая данные кредитами записи, поэтому хост-контроллер 8 памяти не прекращает свою работу из-за недостатка кредитов записи и не блокирует отправку команд записи. В альтернативном варианте, кредиты записи могут возвращаться в виде пакетов, которые отличаются от пакета данных считывания.

Фиг. 16 иллюстрирует вариант осуществления операций, выполняемых контроллером 20 модуля памяти для выработки пакета данных считывания с целью возврата в хост-контроллер 4 памяти. После выработки (на этапе 640) пакета данных считывания, включающего в себя данные считывания, которые необходимо возвратить в запросе считывания из хост-контроллера 6 памяти, если (на этапе 642) счетчик 30 кредитов записи больше нуля, то контроллер 20 модуля памяти показывает (на этапе 644) в пакете данных считывания некоторые или все кредиты записи в счетчике 30 и отправляет (на этапе 646) пакет данных считывания в хост-контроллер 6 памяти. Счетчик 30 кредитов записи уменьшается (на этапе 648) на число возвращенных кредитов записи, которые могут или не могут представлять собой все кредиты в счетчике 30 кредитов. Таким образом, кредиты записи группируются в пакет данных считывания для возврата в хост-контроллер 6 памяти, тем самым оптимизируя использование сообщения для передачи информации. Контроллер 20 модуля памяти может не указывать все кредиты в одном пакете, так как существует фиксированный набор откликов. Например, контроллер 20 модуля памяти может показать 0, 1, или 4 в пакете считывания для числа кредитов записи, которые необходимо вернуть, или 0, 1, 4, или 8 для пакета без данных, если кредиты записи возвращаются (на этапе 620 на фиг. 15) без данных считывания.

Фиг. 17 иллюстрирует вариант осуществления операций, выполняемых хост-контроллером 6 памяти для обработки пакета данных считывания из модуля 8 памяти. После приема (на этапе 660) пакета данных считывания, если (на этапе 662) пакет данных считывания показывает кредиты записи, то хост-контроллер 6 памяти увеличивает значение (на этапе 664) счетчика 9 кредитов записи на число кредитов записи, указанных в пакете данных считывания. После увеличения значения счетчика 9 кредитов записи (после этапа 664), или если не предоставлены кредиты записи (ни из какого ответвления на этапе 662), если (на этапе 666) пакет данных считывания включает в себя данные считывания, то данные считывания обрабатываются (на этапе 670). Пакет данных считывания отбрасывается (на этапе 668) после считывания данных или в случае, если пакет не включает в себя данные (ни из одного ответвления на этапе 666).

Описанные варианты осуществления обеспечивают технологии для модуля 8 памяти для передачи кредитов записи в хост-контроллер 6 памяти способом, который уменьшает полосу пропускания шины 10 за счет группирования кредитов записи в пакеты считывания или в другие, уже используемые сообщения.

Выполнение операций обработки ошибок с использованием сигналов ошибок

Описанные варианты осуществления обеспечивают технологии для упрощенного потока ошибок в модуле 8 памяти для координации обработки ошибок с помощью хост-контроллера 6 памяти. В описанных вариантах осуществления контроллер 20 модуля памяти может сигнализировать об ошибке на выводе 68 ERR0# ошибки, показанном на схеме расположения выводов на фиг. 2. Контроллер 20 модуля памяти может подтвердить сигнал ошибки (ERR) низкого уровня на выводе 68 ошибки для сигнализации о начале операций обработки ошибки и может подтвердить сигнал ошибки (ERR) высокого уровня на выводе 68 ошибки для сигнализации того, что режим закончился, и шина 10 вернулась в исходное состояние, готовое для работы. Таким образом, связь, для координации обработки ошибок между контроллером 20 модуля памяти и хост-контроллером 6 памяти на шине 10, содержит ограниченное число сигналов во избежание излишнего использования полосы пропускания при более обширной координации обработки ошибок.

Фиг. 18 иллюстрирует вариант осуществления выполняемых операций между контроллером 20 модуля памяти и хост-контроллером 6 памяти для управления операциями обработки ошибок после обнаружения ошибки в модуле 8 памяти. После обнаружения (на этапе 700) ошибки, контроллер 20 модуля памяти подтверждает (на этапе 702) первый сигнал ошибки, например, сигнал низкого уровня ERR на выводе 68 (на фиг. 2), на шине 10 для сигнализации для оповещения хост-контроллера 6 памяти о том, что начались операции обработки ошибок. После обнаружения (на этапе 704) первый сигнал ошибки, например, сигнал низкого уровня ERR на выводе 68, хост-контроллер 6 памяти отправляет (на этапе 706) подтверждение того, что первый сигнал ошибки был принят, и затем производится приостановка (на этапе 708) операций считывания и записи в модуле 8 памяти, имеющем ошибку в ответ на первый сигнал ошибки. Хост-контроллер 6 памяти может выполнять дополнительные операции обработки ошибок, такие как установка (на этапе 710) счетчика 9 кредитов записи на максимальное значение. Таким образом, предполагается, что хост-контроллер 6 памяти будет сбрасывать в виде части обработки ошибок все записи из буфера 28 записи на элементах хранения в чипах 12, 14, 16, 18 памяти.

После приема (на этапе 712) подтверждения из хост-контроллера 6 памяти о приеме первого сигнала ошибки, контроллер 20 модуля памяти выполняет операции обработки ошибок, чтобы вернуть шину 10 в исходное состояние. Такие операции могут включать в себя отбрасывание (на этапе 716) всех ожидающих запросов считывания, распределение (на этапе 718) записей в буфере 28 записи в элементах хранения в чипах 12, 14, 16, 18 памяти и сброс (на этапе 722) счетчика 30 кредитов записи с кредитами записи для возвращения в исходное состояние. После завершения операций обработки ошибок, контроллер 20 модуля памяти подтверждает (на этапе 724) второй сигнал ошибки, такой как сигнал высокого уровня ERR выводе 68 ошибки, чтобы сигнализировать о завершении обработки ошибки. После обнаружения (на этапе 726) этого второго сигнала ошибки, хост-контроллер 6 памяти возобновляет (на этапе 728) операции считывания и записи в модуле памяти в ответ на обнаружение второго сигнала ошибки.

При использовании описанных вариантов осуществления модуль 8 памяти и хост-контроллер 6 памяти координируют с ограниченным числом сигналов и выполняют операции полной обработки ошибок без обмена многочисленными передачами в отношении ошибках и транзакций, выполняемых по шине. Каждый компонент 8 и 20 предполагает, что другие компоненты выполняют полное повторное инициирование шины 10 в ответ на ошибку в модуле 8 памяти.

Использование сигнала ошибки для указания ошибки запроса записи и принятие запроса записи

Описанные варианты осуществления обеспечивают технологии для контроллера 20 модуля памяти, чтобы показать в хост-контроллере 6 памяти, что запрос записи успешно завершился без подтверждения сигнала ошибки, такого как сигнал ошибки низкого уровня, в течение предварительно определенного периода времени отправленного запроса записи, и указания неудачного запроса записи при подтверждении сигнала ошибки. После обнаружения сигнала ошибки хост-контроллер 6 памяти повторно отправляет запрос записи, если сигнал ошибки принят в течение предварительно определенного периода времени отправки запроса записи. Таким образом, полоса пропускания шины 10 сохраняется без отправки подтверждений о завершении записи в хост-контроллер 6 памяти после завершения каждого запроса записи.

Фиг. 19 иллюстрирует вариант осуществления операций, выполняемых контроллером 20 модуля памяти и хост-контроллером 6 памяти, чтобы указать принятие запроса записи и ошибки в запросе записи. После того как контроллер 20 модуля памяти обнаруживает (на этапе 750) ошибку записи с помощью одного из обработанных запросов записи, контроллер 20 модуля памяти подтверждает сигнал ошибки, такой сигнал ERR0# ошибки низкого уровня на выводе 68 (на фиг. 3). Контроллер 20 модуля памяти поддерживает сигнал ошибки высокого уровня активным, чтобы показать отсутствие возникновения ошибки. Контроллер 20 модуля памяти может дополнительно использовать сигнал ERR0# на выводе 68 для того, чтобы показать ошибки, несвязанные с ошибками запроса записи. Кроме того, контроллер 20 модуля памяти подразумеваемым образом показывает на успешное завершение запроса записи без отправки сигнала ошибки низкого уровня в течение предварительно определенного периода времени запроса записи, например, когда был отправлен или принят запрос записи.

После того как хост-контроллер 6 памяти обнаруживает (на этапе 754) сигнал ошибки низкого уровня, если (на этапе 756) сигнал ошибки низкого уровня принят в течение предварительно определенного периода времени одного или более запросов записи, то хост-контроллер 20 памяти повторно отправляет (на этапе 758) определенные один или более запросов, отправленных в течение предварительно определенного периода времени приема сигнала ошибки низкого уровня. В некоторых вариантах осуществления хост-контроллер 20 памяти повторно отправляет запросы записи даже в тех случаях, если сигнал ошибки не связан с ошибками записи. Таким образом, хост-контроллер 20 памяти обрабатывает запросы записи как полностью завершенные, если сигнал ошибки низкого уровня не принят в течение предварительно определенного периода времени, и обрабатывает запрос записи, как неудачный, если сигнал ошибки низкого уровня принят в течение предварительно определенного периода времени даже в том случае, если сигнал ошибки низкого уровня сигнализировал об ошибке, несвязанной с ошибками запросов записи.

После повторной отправки запросов записи (на этапе 758) или если существуют запросы записи, отправленные в течение предварительно определенного периода времени (ни с одного из ответвлений на этапе 756), хост-контроллер 6 памяти определяет (на этапе 760), существует ли операция обработки ошибки, связанная с сигналом ошибки низкого уровня, который будет выполняться как несвязанный с ошибками записи. Если это так, то хост-контроллер 6 памяти выполняет (на этапе 762) операцию обработки ошибки, несвязанную с ошибками записи.

При использовании описанных вариантов осуществления модуль 8 памяти не отправляет подтверждения о завершении записи после завершения каждой записи. Вместо этого, хост-контроллер 6 памяти предполагает, что запись завершена, если сигнал ошибки не принят в течение предварительно определенного периода времени после запроса записи. Кроме того, хост-контроллер 6 памяти повторно отправляет запрос записи, если сигнал ошибки принят в течение предварительно определенного периода времени отправки запроса записи даже в том случае, если контроллер 20 модуля памяти сигнализировал об ошибке, несвязанной с ошибкой записи.

Скремблирование данных считывания в модуле памяти

Описанные варианты осуществления обеспечивают технологии для контроллера 20 модуля памяти, чтобы дескремблировать данные записи и хранить нескремблированные данные записи и затем скремблировать сохраненные данные для возврата запроса считывания, включая скремблирование адреса считывания. Скремблирование данных, передаваемых по шине 10 как для считывания, так и для записей, выполняется во избежание вероятности возникновения досадной последовательности, возникающей при передаче, которая будет приводить к ошибка на шине 10.

Чтобы обеспечить скремблирование данных считывания, хост-контроллер 6 памяти и контроллер 20 модуля памяти поддерживают начальные значения 11 и 32 скремблирования (показанные на фиг. 1 и 2), соответственно. Оба этих начальных значения инициализируются с общим значение, и затем увеличиваются после обработки пакета данных считывания таким образом, чтобы увеличенные начальные значения 11 и 32 устанавливались независимым образом на одинаковое значение для одинакового пакета данных считывания и использовались для скремблирования и дескремблирования запрошенных данных считывания в пакете данных считывания, возвращенном в хост-контроллер 6 памяти в ответ на запрос считывания. Кроме того, контроллер 20 модуля памяти и хост-контроллер 6 памяти реализует логическую схему для того же самого алгоритма скремблирования данных с использованием начальных значений 11 и 32 для скремблирования и дескремблирования данных, чтобы устранить вероятность досадной последовательности на шине 10. В альтернативных вариантах осуществления хост-контроллер 6 памяти и контроллер 20 модуля памяти могут обновлять начальные значения 11 и 32 с помощью дополнительных операций, известных в предшествующем уровне техники.

Фиг. 20 иллюстрирует вариант осуществления операций, выполняемых контроллером 20 модуля памяти и хост-контроллером 6 памяти для скремблирования данных считывания, переданных через шину 10. После приема (на этапе 800) запроса считывания из хост-контроллера 6 памяти для адреса считывания, контроллер 20 модуля памяти осуществляет выборку (на этапе 802) нескремблированных данных считывания из элемента хранения, например, чипа 12, 14, 16, 18 DRAM, в модуле 8 памяти. Контроллер 20 модуля памяти использует (на этапе 804) начальное значение 32 скремблирования для скремблирования запрошенных данных считывания и адреса считывания, который будет включен в пакет данных считывания для возвращения (на этапе 806) в запрос считывания из хост-контроллера 6 памяти. Затем начальное значение 32 скремблера обновляется (на этапе 808). В одном варианте осуществления начальные значения 11, 32 скремблера обновляются псевдослучайным образом с использованием схемы линейного сдвигового регистра с обратной связью (LFSR).

После приема пакета считывания, хост-контроллер 6 памяти использует (на этапе 812) начальное значение 11 скремблера для дескремблирования пакета данных считывания, чтобы определить данные считывания и адрес считывания. Запрос считывания, связанный с нескремблированным адресом, затем определяется (на этапе 814) таким образом, чтобы данные считывания можно было вернуть в этот запрос считывания. Начальное значение 11 скремблера обновляется (на этапе 816). В альтернативном варианте осуществления начальные значения 11 и 32 скремблирования можно обновлять перед применением скремблирования и дескремблирования.

Фиг. 21 иллюстрирует вариант осуществления операций, выполняемых контроллером 20 модуля памяти для управления скремблированными данными записи. После приема (на этапе 830) запроса записи, имеющего скремблированные данные записи из хост-контроллера 6 памяти, контроллер 20 модуля памяти дескремблирует (на этапе 832) скремблированные данные записи с использованием адреса записи запроса записи и затем записывает (на этапе 834) нескремблированные данные в чип 12, 14, 16, 18 памяти в модуле 8 памяти.

Описанные варианты осуществления позволяют контроллеру 20 модуля памяти сохранять нескремблированные данные считывания и затем скремблировать как данные считывания, так и адрес для возврата на шину 10 путем использования начальных значений 11 и 32 с тем, чтобы каждый компонент 8 и 20 обновлялся во время операций скремблирования и дескремблирования.

Выбор одной из множества конфигураций интерфейса шины для использования

Описанные варианты осуществления обеспечивают параметр 34 интерфейса для конфигурирования в модуле 8 памяти, который используется контроллером 20 модуля памяти для определения конфигурации интерфейса шины, используемой модулем 8 памяти. Таким образом, контроллер 20 модуля памяти может работать с различными интерфейсами 10 шины, такими как интерфейсы шины, имеющие различную ширину шины, например, ширину данных шины, такую как 9-разрядный интерфейс, 18-разрядный интерфейс, 72-разрядный интерфейс и т.д. Например, различные типы DIMM, в которых можно реализовать контроллер 20 модуля памяти, может иметь различные конфигурации ширины шины, такие как различное число выводов, например, 72, 168, 184, 240 и т.д. для реализации различной ширины шины.

Фиг. 22 иллюстрирует вариант осуществления операций, выполняемых контроллером 20 модуля памяти для определения (на этапе 900) параметра 34 интерфейса. Контроллер 20 модуля памяти может определить конфигурацию интерфейса шины 10 во время инициализации путем сканирования шины 10 или путем опроса хост-контроллера 6 памяти. В качестве альтернативы, хост-контроллер 6 памяти или другой компонент может передавать информацию по шине 10 с такой конфигураций интерфейса, как ширина шины, конфигурация выводов и т.д., по шине 10 во время инициализации. В еще одном варианте осуществления модуль 8 памяти может иметь один или более связывающих выводов, внешних к шине 10, которые соединены с модулем 8 памяти, который поддерживает конфигурацию интерфейса шины 10. Хост-контроллер 6 памяти или другой компонент могут подтвердить конфигурацию интерфейса шины на по меньшей мере одном связывающем выводе. Один связывающий вывод можно использовать в случае, если существует только две поддерживаемых конфигурации интерфейса шины, которые будут поддерживать связь. Если существует более двух поддерживаемых конфигураций интерфейса шины, которые поддерживает контроллер 20 модуля памяти, то могут существовать дополнительные выводы, чтобы показывать более двух конфигураций интерфейса шины. После определения (на этапе 900) конфигурации интерфейса шины, параметр 32 интерфейса устанавливается таким образом, чтобы показывать определенный параметр интерфейса.

Фиг. 23 иллюстрирует вариант осуществления операций, выполняемых контроллером 20 модуля памяти для обработки запроса передачи на основании конфигурации интерфейса шины. После инициализации операции для обработки запроса передачи (на этапе 930), контроллер 20 модуля памяти выбирает (на этапе 932) конфигурацию интерфейса шины, соответствующую параметру 32 интерфейса, где выбранная конфигурация шины может содержать одну из первой, второй, третьей или дальнейших конфигураций шин, каждая из которых имеет различную ширину шины и конфигурацию выводов. Например, конфигурации шин могут содержать 9-разрядную, 18-разрядную и 72-разрядную шину данных, где каждая из этих конфигураций шин может иметь различное число выводов. Эта выбранная конфигурация шины используется при обработке запросов передачи и других операций.

Контроллер 20 модуля памяти вырабатывает (на этапе 934) ряд передач для обработки запроса передачи на основании на ширине шины выбранной конфигурации интерфейса шины. Например, если выбранная конфигурация шины имеет ширину шины меньше, чем в других возможных конфигурациях, поддерживаемых контроллером 20 модуля памяти, то эта конфигурация шины будет требовать большего количества передач для размещения их на меньшей ширине шины, чем требуется для поддерживаемой конфигурации интерфейса шины, имеющей большую ширину шины и большее количество выводов. Таким образом, контроллер 20 модуля памяти может разделить запрос передачи на различное число шинных транзакций на основании ширины шины из выбранной конфигурации интерфейса шины. Выработанные передачи передаются (на этапе 936) с выбранной конфигурации интерфейса шины.

Описанные варианты осуществления обеспечивают контроллер 20 модуля памяти, который находится в рабочем состоянии в модулях 8 памяти, имеющих различные конфигурации интерфейсов шин, позволяя контроллеру 20 модуля памяти поддерживать конфигурацию шины модуля 8 памяти, в котором она реализована.

Следует иметь в виду, что ссылка на всем протяжении данного описания на "один вариант осуществления" или "вариант осуществления" означает, что этот конкретный признак, конструкция или характеристика, описанная в связи с вариантом осуществления, включено по меньшей мере в один вариант осуществления настоящего изобретения. Поэтому следует подчеркнуть и иметь в виду, что две или более ссылки на "вариант осуществления", или "один вариант осуществления" или "альтернативный вариант осуществления" в различных частях данного описания необязательно относятся к одному и тому же варианту осуществления. Кроме того, конкретные признаки, структуры или характеристики можно объединить подходящим образом в одном или более вариантах осуществления изобретения.

Аналогично, следует иметь в виду, что в вышеизложенном описании вариантов осуществления изобретения различные признаки иногда сгруппированы вместе в одном варианте осуществления, фигуре или их описании с целью упрощения раскрытия, облегчающего понимание одного или более различных аспектов изобретения. Однако данный способ раскрытия не должен интерпретироваться как отражающий намерения того, что заявленный предмет изобретения требует больше признаков, которые однозначно изложены в каждом пункте формулы изобретения. В значительной степени, как это отражено в нижеследующей формуле изобретения, аспекты изобретения находятся в менее чем во всех признаках единственного вышеизложенного раскрытого варианта осуществления. Таким образом, формула изобретения, следующая за подробным описанием изобретения, включена тем самым в явной форме в данное подробное описание.

Реферат

Изобретение относится к вычислительной технике. Технический результат заключается в обеспечении возможности в единственном сигнале запроса сигнализировать о по меньшей мере одной из множества различных функций. Устройство для использования в модуле памяти, который соединен с хост-контроллером памяти по шине, содержит контроллер модуля памяти, содержащий аппаратное средство для выработки сигнала запроса в хост-контроллер памяти, показывающего, что хост-контроллер памяти может осуществить доступ к модулю памяти, при этом хост-контроллер отправляет запросы на считывание и запись по шине в модуль памяти для сохранения данных в чипах памяти модуля памяти, а сигнал запроса имеет длительность импульса больше или равную минимальной длительности импульса, где минимальная длительность импульса содержит ряд тактовых циклов, необходимых для гарантии того, что хост-контроллер памяти обнаруживает сигнал запроса, и где длительность импульса сигнала запроса показывает по меньшей мере одну функцию в дополнение к сигналу запроса в хост-контроллере памяти. 4 н. и 21 з.п. ф-лы, 23 ил.

Комментарии