Контроллер высокоскоростного канала обмена - RU177629U1

Код документа: RU177629U1

Чертежи

Описание

Полезная модель относится к области вычислительной техники и может быть использована в качестве канала ввода-вывода в процессорах и в качестве системного интерфейса.

Известно «Устройство для управления обменом информацией между ЭВМ и группой периферийных устройств» [SU №2411651 А2, G06F 13/00, опубл. 07.02.1992], содержащее счетчик, стек регистров адреса, блок адресации памяти микрокоманд, блок памяти микрокоманд, блоки сопряжения, стек регистров уровня приоритета, тактовый генератор, блок приоритета, блок регистров данных, мультиплексор управления, дешифратор, блок управления, блок обработки очередей, блок регистров адреса, мультиплексор признаков результата, стек регистров признаков результата, блок оперативной памяти, мультиплексор адреса, регистр признаков результата, мультиплексор данных с соответствующими связями.

Недостатком этого устройства являются ограниченные функциональные возможности.

Наиболее близким к заявляемому является «Устройство для сопряжения периферийных устройств с эвм-персональным компьютером» [РФ №2183851 C1, G06F 13/24, 27.09.2007], содержащее блок приемопередатчиков, устройство управления, транслятор прерывания и мультиплексор, отличающееся тем, что в него введены генератор тактов, таймер ожидания и блок управления общей шиной, причем входы Сброс, магистраль Адреса, Строб Адреса, Ввод и Вывод устройства управления являются одноименными входами устройства для подключения к соответствующим выходам шины персонального компьютера, выходы Готов и Укороченный Цикл устройства управления являются одноименными выходами устройства для подключения к соответствующим входам шины персонального компьютера, выходы Управление 1 - Управление 8 устройства управления соединены с соответствующими входами мультиплексора, выход Сброс Программный которого подключен к одноименному входу устройства управления, которое соединено с мультиплексором также магистралью Слова Состояния, выходы Управляющий Сигнал 1 - Управляющий Сигнал 6, Рабочий Такт 1 - Рабочий Такт 12 и Сброс устройства управления подключены к одноименным входам блока управления общей шиной, выходы Синхронизация Активного, Вывод, Ввод, Внешнее Устройство, Байт и Сброс которого являются соответствующими выходами устройства для подключения к одноименным входам общей шины периферийных устройств, вход Синхронизация Пассивного устройства управления является соответствующим входом устройства для подключения к одноименному выходу общей шины периферийных устройств, выход Чтение/Запись устройства управления соединен с соответствующим входом блока приемопередатчиков, один вход-выход которого магистралью Адреса-Данных подключен к мультиплексору, а другой является входом-выходом магистрали Адреса-Данных устройства для подключения к общей шине периферийных устройств, вход-выход магистрали Данных мультиплексора является соответствующим входом-выходом устройства для подключения к шине персонального компьютера, вход Стоп Таймер устройства управления соединен с выходом таймера ожидания, вход которого подключен к выходу Старт Таймер генератора тактов, вход Тактовые Импульсы которого является одноименным входом устройства для подключения к соответствующему выходу шины персонального компьютера, выходы Такт 1 - Такт 12 генератора тактов соединены с соответствующими входами устройства управления, выходы Старт Начала, Старт Конца и Сброс которого подключены к одноименным входам генератора тактов, выходы Окончание Прерывания и Прерывание по Таймеру устройства управления соединены с одноименными входами транслятора прерывания, выход Предоставление Прерывания и вход Требование Прерывания которого являются одноименными соответственно выходом и входом устройства для подключения к общей шине периферийных устройств, выход Прерывание Аппаратное транслятора прерываний является выходом Прерывание Аппаратное устройства для подключения к соответствующему входу шины персонального компьютера, при этом мультиплексор состоит из регистра адреса, регистра слова состояния и регистра данных, причем магистральный вход регистра адреса, первые магистральные входы и выходы регистра слова состояния и регистра данных объединены и являются входом-выходом магистрали Данных мультиплексора, магистральный выход регистра адреса и вторые магистральные вход и выход регистра данных объединены и являются входом-выходом магистрали Адреса-Данных мультиплексора, вторые магистральные вход и выход регистра слова состояния объединены и являются входом-выходом магистрали Слова Состояния мультиплексора, вход управления записью и вход управления считыванием регистра адреса являются входами соответственно Управление 1 и Управление 2 мультиплексора, входы управления записью, считыванием и выбором первого/второго направления регистра слова состояния и регистра данных являются соответственно входами Управление 3 - Управление 5 и Управление 6 - Управление 8 мультиплексора, причем выход выделенного для программного сброса разряда регистра слова состояния первого направления является выходом Сброс Программный мультиплексора.

Недостатком данного устройства является отсутствие возможности использования его в качестве канала ввода-вывода в процессорах и в качестве системного интерфейса.

Техническим результатом является расширение функциональных возможностей контроллера за счет использования его в качестве канала ввода-вывода в процессорах и в качестве системного интерфейса.

Технический результат достигается тем, что в «Контроллер высокоскоростного канала обмена», содержащий мультиплексор, дополнительно введены блок очереди приема пакетов, блок проверки пакетов, принимаемых от физического уровня, блок очереди приема пакетов от системы, блок формирования пакетов, блок пересинхронизации и разбора пакетов, блок операционных регистров, блок управления физическим уровнем и блок выбора пакетов, первый двухсторонний вход-выход которого соединен с первым двухсторонним входом-выходом блока формирования пакетов, второй двухсторонний вход-выход которого соединен с вторым двухсторонним входом-выходом блока 8 выбора пакетов, выход которого соединен с выходом контроллера высокоскоростного канала обмена, вход которого соединен с входом блока пересинхронизации и разбора пакетов, первый, второй, третий и четвертый выходы которого соединены соответственно с первым, вторым, третьим и четвертым входами блока проверки пакетов, принимаемых от физического уровня, первый и второй выходы которого соединены соответственно с первым и вторым входами блока очереди приема пакетов, первый двухсторонний вход-выход которого соединен с первым двухсторонним входом-выходом контроллера высокоскоростного канала обмена, второй двухсторонний вход-выход которого соединен с вторым двухсторонним входом-выходом блока операционных регистров, первый двухсторонний вход-выход которого соединен с объединенными первыми двухсторонними входами выходами блока очереди приема пакетов и блока очереди приема пакетов от системы, двухсторонним входом-выходом блока проверки пакетов, принимаемых от физического уровня, вторым двухсторонним входом-выходом блока управления физическим уровнем и четвертым двухсторонним входом-выходом блока формирования пакетов, третий двухсторонний вход-выход которого соединен с вторым двухсторонним входом-выходом блока очереди приема пакетов от системы, третий двухсторонний вход-выход которого соединен с третьим двухсторонним входом-выходом контроллера высокоскоростного канала обмена, четвертый двухсторонний вход-выход которого соединен с первым двухсторонним входом-выходом блока управления физическим уровнем, причем блок очереди приема пакетов содержит блок приема и формирования пакетов уровня транзакций, n блоков приема и формирования пакетов уровня транзакций, где n=1, 2, 3, …, N, блоков управления потоком соответствующего виртуального канала и блок «глобального» управления потоком, первый двухсторонний вход-выход которого соединен с первым двухсторонним входом-выходом блока очереди приема пакетов, второй двухсторонний вход-выход которого соединен с первым двухсторонним входом-выходом блока приема и формирования пакетов уровня транзакций, второй двухсторонний вход-выход которого соединен с вторым двухсторонним входом-выходом блока «глобального» управления потоком, с третьего по (n+3)-й двухсторонние входы-выходы которого соединены с соответственно с одноименными двухсторонними входами выходами блока приема и формирования пакетов уровня транзакций, первый и второй входы которого соединены соответственно с первым и вторым входами блока очереди приема пакетов, причем блок проверки пакетов, принимаемых от физического уровня содержит буфер приема пакетов, блок проверки пакетов уровня транзакций от физического уровня и блок проверки пакетов канального уровня, третий двухсторонний вход-выход которого соединен с третьим двухсторонним входом-выходом блока проверки пакетов уровня транзакций от физического уровня, первый двухсторонний вход-выход которого соединен с первым двухсторонним входом-выходом блока приема пакетов, второй двухсторонний вход-выход которого соединен с вторым двухсторонним входом-выходом блока проверки пакетов канального уровня, первый двухсторонний вход-выход которого соединен с двухсторонним входом-выходом блока проверки пакетов, принимаемых от физического уровня, первый и второй выходы которого соединены соответственно с первым и вторым выходами блока приема пакетов, первый и второй входы блока проверки пакетов уровня транзакций от физического уровня соединены соответственно с первым и вторым входами блока проверки пакетов, принимаемых от физического уровня, третий и четвертый входы которого соединены соответственно с первым и вторым входами блока проверки пакетов канального уровня, причем блок очереди приема пакетов от системы содержит блок «глобального» управления потоком, блок декодирования пакетов, m буферов для передачи пакетов, где m=1, 2, 3, …, М, буфер для передачи ответов и арбитр второй первый двухсторонний вход-выход которого соединен с вторым двухсторонним входом-выходом блока «глобального» управления потоком, третий двухсторонний вход-выход которого соединен с первым двухсторонним входом-выходом блока декодирования пакетов, второй двухсторонний вход-выход которого соединен с третьим двухсторонним входом-выходом блока очереди приема пакетов, первый двухсторонний вход-выход которого соединен с первым двухсторонним входом-выходом арбитра, с первого по m-й входы которого соединены с соответственно с одноименными выходами соответственно буферов для передачи пакетов, с первого по m-й входы которых соединены с соответственно с одноименными выходами соответственно выходами блока декодирования пакетов, (m+1)-й выход которого соединен с входом буфер для передачи ответов, выход которого соединен с (m+1)-м входом арбитра, первый двухсторонний вход-выход блока «глобального» управления потоком соединен с вторым двухсторонним входом-выходом блока очереди приема пакетов, причем блок формирования пакетов содержит блок формирования пакетов уровня транзакций, блок формирования пакетов канального уровня и блок повторов пакетов, двухсторонний вход-выход мультиплексора соединен с вторым двухсторонним входом-выходом блока очереди приема пакетов, третий двухсторонний вход-выход которого соединен с первым двухсторонним входом-выходом блока формирования пакетов канального уровня, второй двухсторонний вход-выход которого соединен с четвертым двухсторонним входом-выходом блока очереди приема пакетов, первый двухсторонний вход-выход которого соединен с первым двухсторонним входом-выходом блока формирования пакетов уровня транзакций, второй двухсторонний вход-выход которого соединен с третьим двухсторонним входом-выходом блока формирования пакетов канального уровня, выход блока формирования пакетов уровня транзакций соединен с объединенными первым входом мультиплексора и входом блока повторов пакетов, выход которого соединен с вторым входом мультиплексора, причем блок пересинхронизации и разбора пакетов содержит блок разбора пакетов принятых от физического уровня и пересинхронизационный буфер, двухсторонний вход-выход которого соединен с первым двухсторонним входом-выходом блока разбора пакетов принятых от физического уровня, второй и третий двухсторонние входы-выходы которого соединены соответственно с первым и вторым двухсторонними входами выходами блока очереди приема пакетов, вход которого соединен с входом пересинхронизационного буфера.

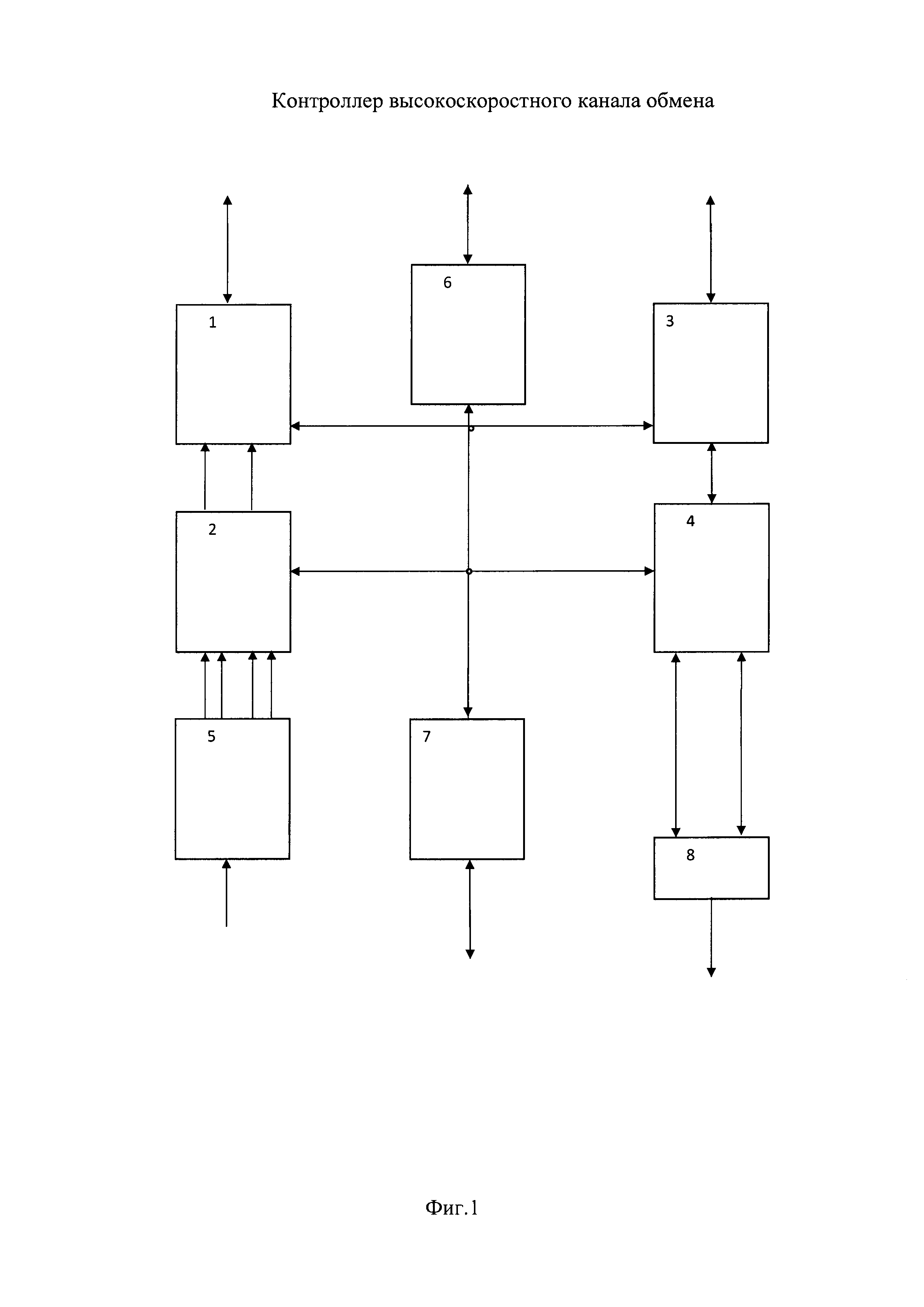

На фиг. 1 представлена схема контроллера высокоскоростного канала обмена.

На фиг. 2 представлена схема блока очереди приема пакетов.

На фиг. 3 представлена схема блока проверки пакетов, принимаемых от физического уровня.

На фиг. 4 представлена схема блока очереди приема пакетов от системы.

На фиг. 5 представлена схема блока формирования пакетов.

На фиг. 6 представлена схема блока пересинхронизации и разбора пакетов.

Контроллер высокоскоростного канала обмена (фиг. 1) содержит блок 1 очереди приема пакетов, блок 2 проверки пакетов, принимаемых от физического уровня, блок 3 очереди приема пакетов от системы, блок 4 формирования пакетов, блок 5 пересинхронизации и разбора пакетов, блок 6 операционных регистров, блок 7 управления физическим уровнем и блок 8 выбора пакетов.

Блок 1 очереди приема пакетов (фиг. 2) содержит блок 9 приема и формирования пакетов уровня транзакций, n блоков 10.1, 10.2, 10.3, …, 10.n приема и формирования пакетов уровня транзакций, где n=1, 2, 3, …, N, блоков управления потоком соответствующего виртуального канала и блок 11 «глобального» управления потоком.

Блок 2 проверки пакетов, принимаемых от физического уровня (фиг. 3) содержит буфер 12 приема пакетов, блок 13 проверки пакетов уровня транзакций от физического уровня и блок 14 проверки пакетов канального уровня.

Блок 3 очереди приема пакетов от системы (фиг. 4) содержит блок 15 «глобального» управления потоком, блок 16 декодирования пакетов, m буферов для передачи пакетов 17.1, 17.2, 17.3, …, m, где m=1, 2, 3, …, М, буфер 18 для передачи ответов и арбитр 19.

Блок 4 формирования пакетов (фиг. 5) содержит блок 20 формирования пакетов уровня транзакций, блок 21 формирования пакетов канального уровня, блок 22 повторов пакетов, и мультиплексор 23.

Блок 5 пересинхронизации и разбора пакетов (фиг. 6) содержит блок 24 разбора пакетов принятых от физического уровня и Пересинхронизационный буфер 25.

Контроллер высокоскоростного канала обмена (фиг. 1 - фиг. 6) содержит блок 1 очереди приема пакетов, блок 2 проверки пакетов, принимаемых от физического уровня, блок 3 очереди приема пакетов от системы, блок 4 формирования пакетов, блок 5 пересинхронизации и разбора пакетов, блок 6 операционных регистров, блок 7 управления физическим уровнем и блок 8 выбора пакетов, первый двухсторонний вход-выход которого соединен с первым двухсторонним входом-выходом блока 4 формирования пакетов, второй двухсторонний вход-выход которого соединен с вторым двухсторонним входом-выходом блока 8 выбора пакетов, выход которого соединен с выходом контроллера высокоскоростного канала обмена, вход которого соединен с входом блока 5 пересинхронизации и разбора пакетов, первый, второй, третий и четвертый выходы которого соединены соответственно с первым, вторым, третьим и четвертым входами блока 2 проверки пакетов, принимаемых от физического уровня, первый и второй выходы которого соединены соответственно с первым и вторым входами блока 1 очереди приема пакетов, первый двухсторонний вход-выход которого соединен с первым двухсторонним входом-выходом контроллера высокоскоростного канала обмена, второй двухсторонний вход-выход которого соединен с вторым двухсторонним входом-выходом блока 6 операционных регистров, первый двухсторонний вход-выход которого соединен с объединенными первыми двухсторонними входами выходами блока 1 очереди приема пакетов и блока 3 очереди приема пакетов от системы, двухсторонним входом-выходом блока 2 проверки пакетов, принимаемых от физического уровня, вторым двухсторонним входом-выходом блока 7 управления физическим уровнем и четвертым двухсторонним входом-выходом блока 4 формирования пакетов, третий двухсторонний вход-выход которого соединен с вторым двухсторонним входом-выходом блока 3 очереди приема пакетов от системы, третий двухсторонний вход-выход которого соединен с третьим двухсторонним входом-выходом контроллера высокоскоростного канала обмена, четвертый двухсторонний вход-выход которого соединен с первым двухсторонним входом-выходом блока 7 управления физическим уровнем, причем блок 1 очереди приема пакетов содержит блок 9 приема и формирования пакетов уровня транзакций, n блоков 10.1, 10.2, 10.3, …, n приема и формирования пакетов уровня транзакций, где n=1, 2, 3, …, N, блоков управления потоком соответствующего виртуального канала и блок 11 «глобального» управления потоком, первый двухсторонний вход-выход которого соединен с первым двухсторонним входом-выходом блока 1 очереди приема пакетов, второй двухсторонний вход-выход которого соединен с первым двухсторонним входом-выходом блока 9 приема и формирования пакетов уровня транзакций, второй двухсторонний вход-выход которого соединен с вторым двухсторонним входом-выходом блока 11 «глобального» управления потоком, с третьего по (n+3)-й двухсторонние входы-выходы которого соединены с соответственно с одноименными двухсторонними входами выходами блока 9 приема и формирования пакетов уровня транзакций, первый и второй входы которого соединены соответственно с первым и вторым входами блока 1 очереди приема пакетов, причем блок 2 проверки пакетов, принимаемых от физического уровня содержит буфер 12 приема пакетов, блок 13 проверки пакетов уровня транзакций от физического уровня и блок 14 проверки пакетов канального уровня, третий двухсторонний вход-выход которого соединен с третьим двухсторонним входом-выходом блока 13 проверки пакетов уровня транзакций от физического уровня, первый двухсторонний вход-выход которого соединен с первым двухсторонним входом-выходом блока 12 приема пакетов, второй двухсторонний вход-выход которого соединен с вторым двухсторонним входом-выходом блока 14 проверки пакетов канального уровня, первый двухсторонний вход-выход которого соединен с двухсторонним входом-выходом блока 2 проверки пакетов, принимаемых от физического уровня, первый и второй выходы которого соединены соответственно с первым и вторым выходами блока 12 приема пакетов, первый и второй входы блока 13 проверки пакетов уровня транзакций от физического уровня соединены соответственно с первым и вторым входами блока 2 проверки пакетов, принимаемых от физического уровня, третий и четвертый входы которого соединены соответственно с первым и вторым входами блока 14 проверки пакетов канального уровня, причем блок 3 очереди приема пакетов от системы содержит блок 15 «глобального» управления потоком, блок 16 декодирования пакетов, m буферов для передачи пакетов 17.1, 17.2, 17.3, …, m, где m=1, 2, 3, …, М, буфер 18 для передачи ответов и арбитр 19 второй первый двухсторонний вход-выход которого соединен с вторым двухсторонним входом-выходом блока 15 «глобального» управления потоком, третий двухсторонний вход-выход которого соединен с первым двухсторонним входом-выходом блока 16 декодирования пакетов, второй двухсторонний вход-выход которого соединен с третьим двухсторонним входом-выходом блока 3 очереди приема пакетов, первый двухсторонний вход-выход которого соединен с первым двухсторонним входом-выходом арбитра 19, с первого по m-й входы которого соединены с соответственно с одноименными выходами соответственно с 17.1 по 17.m буферов для передачи пакетов, с первого по m-й входы которых соединены с соответственно с одноименными выходами соответственно с 17.1 по 17.m выходами блока 16 декодирования пакетов, (m+1)-й выход которого соединен с входом буфер 18 для передачи ответов, выход которого соединен с (m+1)-м входом арбитра 19, первый двухсторонний вход-выход блока 15 «глобального» управления потоком соединен с вторым двухсторонним входом-выходом блока 3 очереди приема пакетов, причем блок 4 формирования пакетов содержит блок 20 формирования пакетов уровня транзакций, блок 21 формирования пакетов канального уровня и блок 22 повторов пакетов, двухсторонний вход-выход мультиплексора 23 соединен с вторым двухсторонним входом-выходом блока 4 очереди приема пакетов, третий двухсторонний вход-выход которого соединен с первым двухсторонним входом-выходом блока 21 формирования пакетов канального уровня, второй двухсторонний вход-выход которого соединен с четвертым двухсторонним входом-выходом блока 4 очереди приема пакетов, первый двухсторонний вход-выход которого соединен с первым двухсторонним входом-выходом блока 20 формирования пакетов уровня транзакций, второй двухсторонний вход-выход которого соединен с третьим двухсторонним входом-выходом блока 21 формирования пакетов канального уровня, выход блока 20 формирования пакетов уровня транзакций соединен с объединенными первым входом мультиплексора 23 и входом блока 22 повторов пакетов, выход которого соединен с вторым входом мультиплексора 23, причем блок 5 пересинхронизации и разбора пакетов содержит блок 24 разбора пакетов принятых от физического уровня и пересинхронизационный буфер 25, двухсторонний вход-выход которого соединен с первым двухсторонним входом-выходом блока 24 разбора пакетов принятых от физического уровня, второй и третий двухсторонние входы-выходы которого соединены соответственно с первым и вторым двухсторонними входами выходами блока 5 очереди приема пакетов, вход которого соединен с входом пересинхронизационного буфера 25.

Работа контроллера высокоскоростного канала обмена (фиг. 1 - фиг. 6) заключается в следующем.

Функции контроллера логически разделены на два уровня: канальный уровень с некоторыми функциями уровня транзакций и физический уровень.

Контроллер взаимодействует с системным уровнем посредством квантов информации, далее называемых транзакциями, обеспечивая сервис по надежному высокоскоростному обмену с системным уровнем внешнего абонента. Транзакции являются составляющими элементами системных операций, таких как чтение и запись, и передаются пакетами. Прием/передача пакетов транзакций по линку осуществляется в автоматическом режиме: то есть, для организации обмена не требуются обращения к внутренним регистрам. Доступ к внутренним регистрам контроллера используется только для задания режима работы, обработки прерываний и контроля состояния линка.

При выполнении обмена пакетами блоки контроллера выполняют следующие функции.

Блок 1 очереди приема пакетов от канального уровня и передачи их в систему осуществляет прием пакетов, их буферизация, реализация виртуальных каналов по приему и “глобальное” управление потоком.

Блок 2 проверки пакетов, принимаемых от физического уровня осуществляет прием, буферизацию и проверку пакетов от физического уровня.

Блок 3 очереди приема пакетов от системы предназначен для реализации очереди приема пакетов от системы, формирования пакетов уровня транзакций и передачи их в канальный уровень.

Блок 4 формирования пакетов осуществляет формирование пакетов для передачи в физический уровень и повтор передачи в случае ошибки.

Блок 5 пересинхронизации и разбора пакетов осуществляет пересинхронизацию и разбор пакетов принятых от физического уровня.

Блок 6 операционных регистров предназначен для реализации операционных регистров и доступа к ним.

Блок 7 управления физическим уровнем осуществляет управление физическим уровнем и включает в себя процедуру тренировки линка и преобразование данных в примитивы для передачи в канале.

Блок 8 выбора пакетов осуществляет выбор пакетов для передачи их в физический уровень.

Блок 9 приема и формирования пакетов уровня транзакций осуществляет прием и формирование пакетов уровня транзакций.

Блоки 10 приема и формирования пакетов уровня транзакций осуществляют управление потоком соответствующего виртуального канала.

Блок 11 «глобального» управления потоком реализует глобальное управление потоком на приемной стороне.

Буфер 12 приема пакетов предназначен для буферизации пакетов уровня транзакций полученных от физического уровня.

Блок 13 проверки пакетов уровня транзакций от физического уровня проверяет пакеты уровня транзакций, полученных от физического уровня (Transaction Layer Packet, пакет данных в на уровне транзакций - TLP).

Блок 14 проверки пакетов канального уровня проверяет пакеты канального уровня (Data Link Layer Packet - DLLP), полученных от физического уровня

Блок 15 «глобального» управления потоком реализует глобальное управление потоком на передающей стороне.

Блок 16 декодирования пакетов предназначен для декодирования пакетов.

Буферы 17 для передачи пакетов осуществляют буферизацию пакетов от системы соответствующего виртуального канала.

Буфер 18 для передачи ответов предназначен для буферизации ответов от системы.

Арбитр 19 осуществляют арбитраж между буферами для передачи пакетов от системы соответствующего виртуального канала (Тх VC* Queue).

Блок 20 формирования пакетов уровня транзакций предназначен для формирования пакетов уровня транзакций.

Блок 21 формирования пакетов канального уровня предназначен для формирования пакетов канального уровня.

Блок 22 повторов пакетов реализует повтор недоставленных пакетов в случае ошибок в канале.

Мультиплексор 23 осуществляет мультиплексирование потока данных от блока 20 формирования пакетов уровня транзакций и от блока 22 повторов пакетов.

Блок 24 разбора пакетов принятых от физического уровня предназначен для разбора пакетов от физического уровня.

Пересинхронизационный буфер 25 осуществляет пересинхронизацию пакетов.

Таким образом, контроллер высокоскоростного канала обмена позволяет использовать его в качестве канала ввода-вывода в процессорах и в качестве системного интерфейса.

Реферат

Полезная модель относится к области вычислительной техники и может быть использована в качестве канала ввода-вывода в процессорах и в качестве системного интерфейса.Техническим результатом является расширение функциональных возможностей контроллера за счет использования его в качестве канала ввода-вывода в процессорах и в качестве системного интерфейса.Контроллер высокоскоростного канала обмена содержит блок очереди приема пакетов, блок проверки пакетов, принимаемых от физического уровня, блок очереди приема пакетов от системы, блок формирования пакетов, блок пересинхронизации и разбора пакетов, блок операционных регистров, блок управления физическим уровнем и блок выбора пакетов. 6 ил.

Комментарии