Сумматор натуральных чисел - RU2724802C1

Код документа: RU2724802C1

Чертежи

Описание

Изобретение относится к области вычислительной техники и может использоваться в качестве логического элемента в электрических схемах арифметико-логических устройств и электронно-вычислительных машин, а именно выполняет суммирование и вычитание двух натуральных чисел с получением результата в виде целого неотрицательного числа.

Известны устройства для суммирования и вычитания чисел.

Арифметико-логическое устройство для сложения чисел по модулю (см. патент RU №2628180, МПК G06F 7/52, опубл. 15.08.2017), содержащее три n-разрядных регистра, два электронных ключа, входную и выходную n-разрядные шины, один n-разрядный сумматор, схему дизъюнкторов ИЛИ, модуль управляющего блока, причем информационные входы первого и второго n-разрядных регистров соединены с входной n-разрядной шиной, управляющий вход первого n-разрядного регистра соединен с первым выходом модуля управляющего блока, управляющий вход второго n-разрядного регистра соединен с вторым выходом модуля управляющего блока, выход первого n-разрядного регистра соединен с информационным входом первого электронного ключа, выход второго n-разрядного регистра соединен с информационным входом второго электронного ключа, управляющие входы первого и второго электронный ключей соединены с четвертым выходом модуля управляющего блока, выход первого электронного ключа соединен с первым информационным входом первого n-разрядного сумматора, второй информационный вход которого соединен с выходом второго электронного ключа, выход третьего n-разрядного регистра соединен с выходной n-разрядной шиной, а его первый управляющий вход соединен с седьмым выходом модуля управляющего блока, а второй управляющий вход соединен с восьмым выходом модуля управляющего блока, на первый вход модуля управляющего блока подается одноразрядный код команды сложения, на второй вход модуля управляющего блока подаются тактовые импульсы, отличающееся тем, что в него введены четвертый n-разрядный регистр, инвертор, три электронных ключа, второй n-разрядный сумматор, причем информационный вход четвертого n-разрядного регистра соединен с входной n-разрядной шиной, управляющий вход соединен с третьим выходом модуля управляющего блока, а выход соединен с информационным входом инвертора, выход которого соединен с информационным входом третьего электронного ключа, управляющий вход которого соединен с четвертым выходом модуля управляющего блока, а выход соединен с вторым информационным входом второго n-разрядного сумматора, на вход переноса которого постоянно подается сигнал логической 1, выход переноса которого соединен с третьим входом модуля управляющего блока, информационный выход первого n-разрядного сумматора соединен с информационным входом четвертого электронного ключа, а также с первым информационным входом второго n-разрядного сумматора, информационный выход которого соединен с информационным входом пятого электронного ключа, управляющий вход которого соединен с шестым выходом модуля управляющего блока, а выход соединен с вторым информационным входом схемы дизъюнкторов ИЛИ, первый информационный вход которого соединен с выходом четвертого электронного ключа, управляющий вход которого соединен с пятым выходом модуля управляющего блока, выход схемы дизъюнкторов ИЛИ соединен с информационным входом третьего n-разрядного регистра, причем модуль управляющего блока арифметико-логического устройства для сложения чисел по модулю, содержит три двухвходовых элемента И, один трехразрядный счетчик, один трехвходовой дешифратор, два RS-триггера и один инвертор, при этом первый вход первого двухвходового элемента И является первым входом модуля управляющего блока, второй вход является вторым входом модуля управляющего блока, а выход соединен со счетным входом трехразрядного счетчика, выходы которого соединены с соответствующими информационными входами трехвходового дешифратора, первый выход которого является первым выходом модуля управляющего блока, второй выход является вторым выходом модуля управляющего блока, третий выход является третьим выходом модуля управляющего блока, шестой выход является седьмым выходом модуля управляющего блока, четвертый выход соединен с S-входом первого RS-триггера, пятый выход соединен с S-входом второго RS-триггера, седьмой выход соединен с R-входами первого и второго RS-триггеров и является восьмым выходом модуля управляющего блока, выход первого RS-триггера является четвертым выходом модуля управляющего блока, выход второго RS-триггера соединен с первыми входами второго и третьего двухвходовых элементов И, третий вход модуля управляющего блока соединен со входом инвертора и вторым входом третьего двухвходового элемента И, выход которого является шестым выходом модуля управляющего блока, выход инвертора соединен со вторым входом второго двухвходового элемента И, выход которого является пятым выходом модуля управляющего блока.

Известно также арифметико-логическое устройство для вычитания чисел по модулю (см. патент RU №2628175, МПК G06F 7/52, опубл. 15.08.2017), содержащее три n-разрядных регистра, два электронных ключа, входную и выходную n-разрядные шины, один n-разрядный сумматор, инвертор, модуль управляющего блока, причем информационные входы первого и второго n-разрядных регистров соединены со входной n-разрядной шиной, управляющий вход первого n-разрядного регистра соединен с первым выходом модуля управляющего блока, управляющий вход второго n-разрядного регистра соединен со вторым выходом модуля управляющего блока, выход первого n-разрядного регистра соединен с информационным входом первого электронного ключа, выход второго n-разрядного регистра соединен с информационным входом инвертора, выход которого соединен с информационным входом второго электронного ключа, управляющие входы первого и второго электронных ключей соединены с четвертым выходом модуля управляющего блока, выход первого электронного ключа соединен с первым информационным входом первого n-разрядного сумматора, на вход переноса которого подается сигнал логической 1, а его второй информационный вход соединен с выходом второго электронного ключа, выход третьего n-разрядного регистра соединен с выходной шиной, его первый управляющий вход соединен с седьмым выходом модуля управляющего блока, а второй управляющий вход соединен с восьмым выходом модуля управляющего блока, на первый вход модуля управляющего блока подается одноразрядный код команды вычитания, на второй вход модуля управляющего блока подаются тактовые импульсы, отличающееся тем, что в него введены четвертый n-разрядный регистр, три электронных ключа, второй n-разрядный сумматор, схема дизъюнкторов ИЛИ, причем информационный вход четвертого n-разрядного регистра соединен с входной n-разрядной шиной, управляющий вход соединен с третьим выходом модуля управляющего блока, а выход соединен с информационным входом третьего электронного ключа, управляющий вход которого соединен с четвертым выходом модуля управляющего блока, а выход соединен со вторым информационным входом второго n-разрядного сумматора, выход переноса первого n-разрядного сумматора соединен с третьим входом модуля управляющего блока, информационный выход первого n-разрядного сумматора соединен с информационным входом четвертого электронного ключа, а также с первым информационным входом второго n-разрядного сумматора, информационный выход которого соединен с информационным входом пятого электронного ключа, управляющий вход которого соединен с шестым выходом модуля управляющего блока, а выход соединен со вторым информационным входом схемы дизъюнкторов ИЛИ, первый информационный вход которой соединен с выходом четвертого электронного ключа, управляющий вход которого соединен с пятым выходом модуля управляющего блока, выход схемы дизъюнкторов ИЛИ соединен с информационным входом третьего n-разрядного регистра, причем модуль управляющего блока арифметико-логического устройства для вычитания чисел по модулю содержит три двухвходовых элемента И, трехразрядный счетчик, трехвходовый дешифратор, два RS-триггера и инвертор, при этом первый вход первого двухвходового элемента И является первым входом модуля управляющего блока, второй вход является вторым входом модуля управляющего блока, а выход соединен со счетным входом трехразрядного счетчика, выходы которого соединены с соответствующими информационными входами трехвходового дешифратора, первый выход которого является первым выходом модуля управляющего блока, второй выход является вторым выходом модуля управляющего блока, третий выход является третьим выходом модуля управляющего блока, шестой выход является седьмым выходом модуля управляющего блока, четвертый выход соединен с S-входом первого RS-триггера, пятый выход соединен с S-входом второго RS-триггера, седьмой выход соединен с R-входами первого и второго RS-триггеров и является восьмым выходом модуля управляющего блока, выход первого RS-триггера является четвертым выходом модуля управляющего блока, выход второго RS-триггера соединен с первыми входами второго и третьего двухвходовых элементов И, третий вход модуля управляющего блока соединен со входом инвертора и вторым входом третьего двухвходового элемента И, выход которого является пятым выходом модуля управляющего блока, выход инвертора соединен со вторым входом второго двухвходового элемента И, выход которого является шестым выходом модуля управляющего блока.

Данные способы имеют недостаток, заключающийся в преобразовании десятичного числа в двоичный код, что ограничивает быстродействие вычисления, а также есть вероятность возникновения случайной ошибки в виде пропуска прямоугольных импульсов в процессе обработки двоичного кода триггерами.

Техническим результатом предлагаемого решения является выполнение быстродействующего сложения или вычитания натуральных чисел N и М без промежуточного преобразования их в двоичный код, а также полное исключение случайной ошибки в процессе вычисления.

Технический результат достигается тем, что сумматор натуральных чисел, характеризуется тем, что он выполнен в виде кольца из полупроводящего материала, с зубчатыми наружным и внутренними периметрами, и снабжен электродами, установленными в зубцах наружного периметра кольца, образующими первую двухфазную систему входных электродов, и электродами, установленными в зубцах внутреннего периметра кольца, образующими вторую двухфазную систему входных электродов, при этом выводы обеих двухфазных систем входных электродов соединены параллельно и подключены к источнику двухфазной системы синусоидальных напряжений с гальванической развязкой между двумя фазами, сумматор также снабжен системой выходных электродов, установленных по окружности кольца между двумя двухфазными системами входных электродов, и выполненной в виде множества тонких электродов круглой формы в поперечном сечении, к которым подключено устройство, регистрирующее количество пучностей результирующего тока.

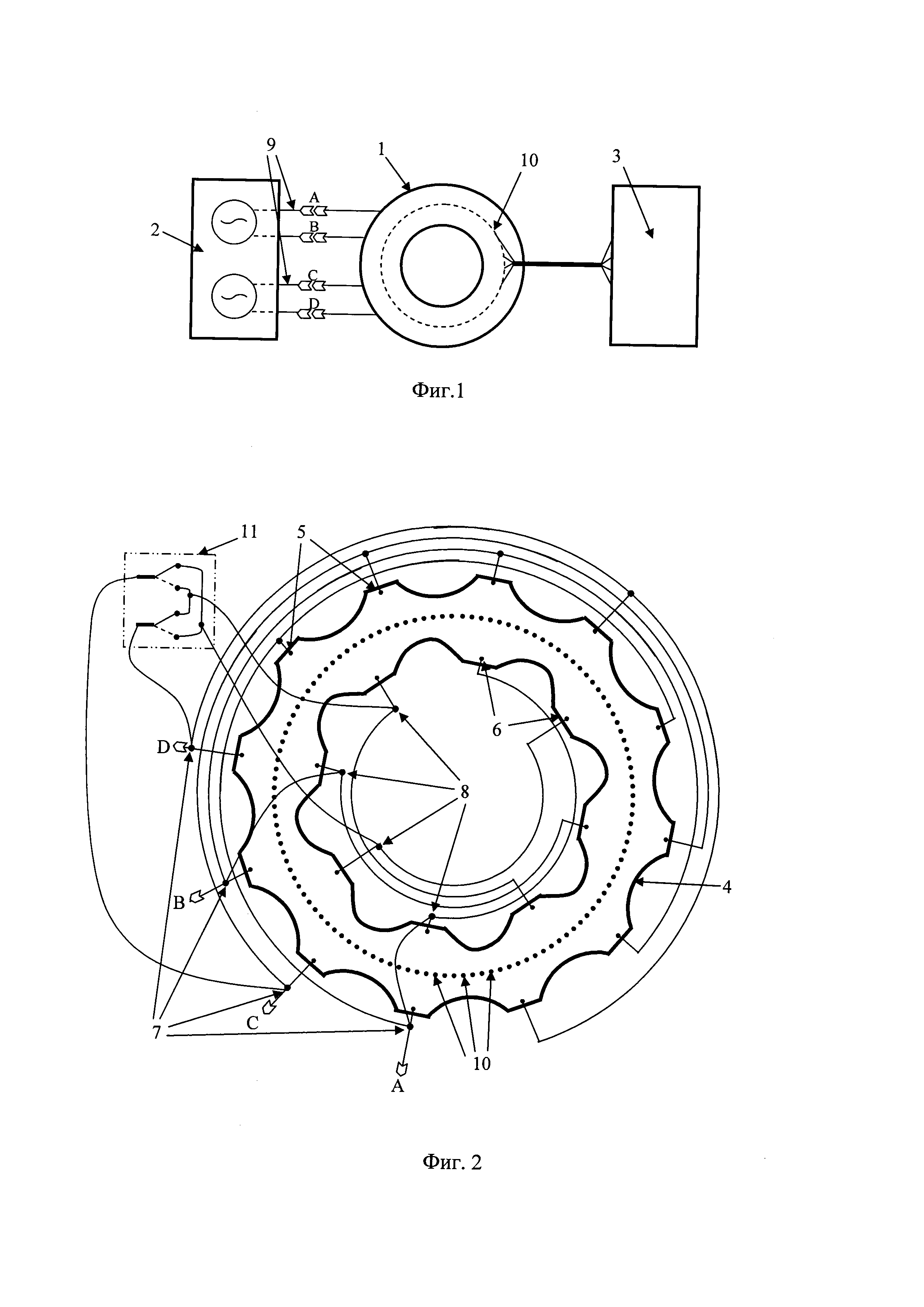

На фиг. 1 изображен общий вид схемы подключения сумматора натуральных чисел 1 к источнику двухфазной системы синусоидальных напряжений 2 с фазовым углом между двумя напряжениями равным 90° и регистрирующим устройством 3, которое регистрирует результат вычисления.

На фиг. 2 изображен сумматор натуральных чисел, состоящий из плоского кольца 4, выполненного из полупроводящего материала, с зубчатыми внутренним и наружным периметрами. В зубцы обоих периметров кольца установлены входные электроды, образуя на каждом периметре двухфазную систему входных электродов 5 и 6, которые, через параллельно соединенные выводы 7 и 8, соединяются с выводами 9 источника двухфазной системы синусоидальных напряжений. Значения суммируемых (вычитаемых) натуральных чисел N и М определяется количеством входных электродов, а именно, количество входных электродов на наружном периметре кольца равно 2N, а на внутреннем периметре равно 2М. Между наружным и внутренним периметром, на торце кольца, установлена система выходных электродов 10, состоящая из множества распределенных по окружности кольца и соединенных с кольцом тонких электродов, подключаемых к регистрирующему устройству для регистрации результата вычисления.

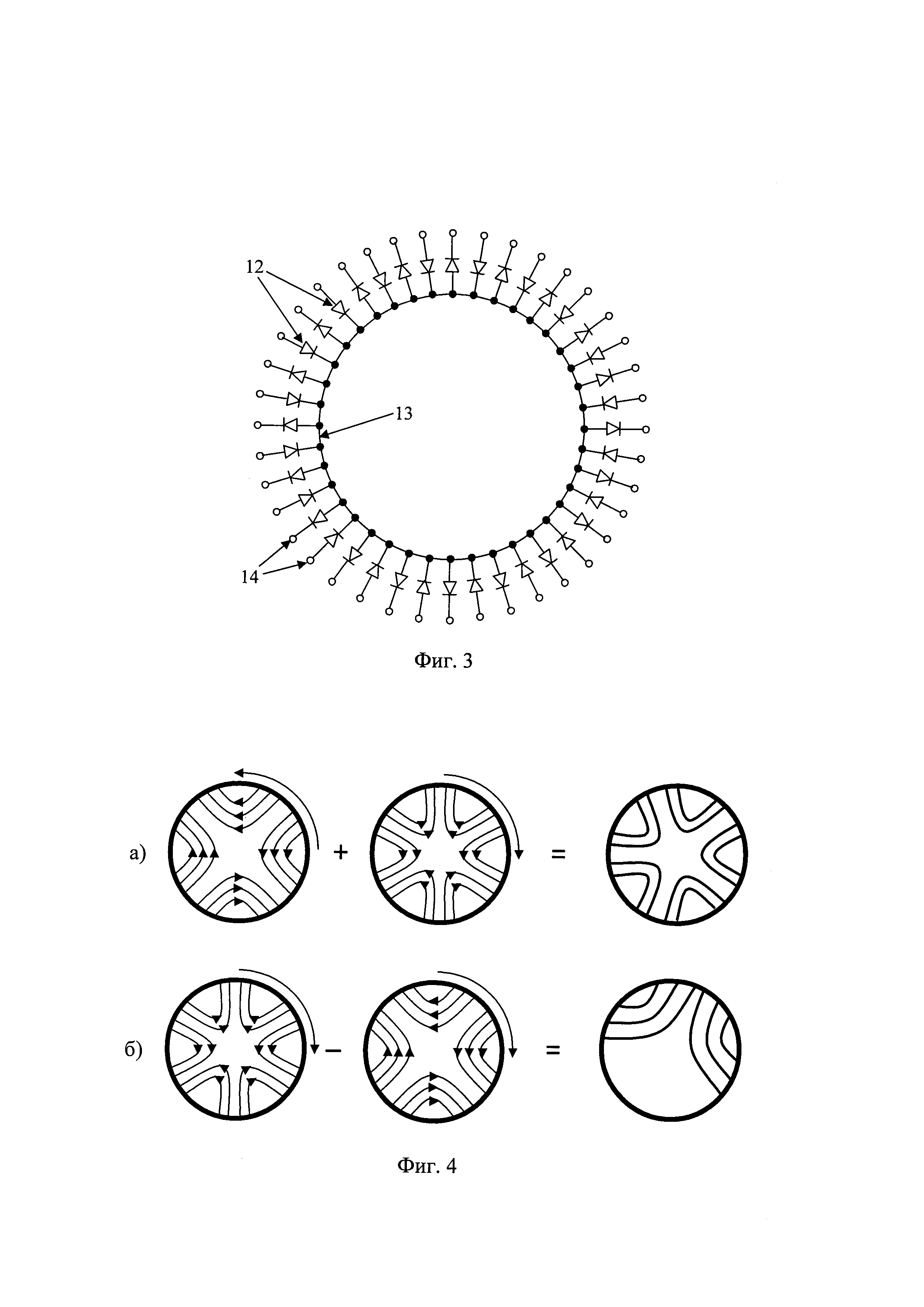

На фиг. 3 изображен светодиодный визуальный регистратор количества пучностей результирующего тока; на фиг. 4 показаны примеры суперпозиции вращающихся токов в полупроводниковом кольце: а) сложение вращающихся токов; б) вычитание вращающихся токов.

Устройство работает следующим образом (см. фиг. 1 и фиг. 2).

От источника двухфазной системы синусоидальных напряжений оба напряжения подаются на сумматор натуральных чисел. При подаче двухфазного напряжения на параллельно соединенные двухфазные системы входных электродов, в кольце возникают два вращающихся электрических тока, первый из которых создается двухфазной системой входных электродов, установленной на наружном зубчатом периметре кольца, а второй вращающийся ток создается второй двухфазной системой входных электродов, установленной на внутреннем периметре кольца. Каждый вращающийся ток имеет целое количество пар входа и выхода тока, чередующихся по окружности. Первый вращающийся ток имеет количество пар входа и выхода тока, равное первому натуральному числу «N», а второй ток имеет количество пар входа и выхода тока, равное второму натуральному числу «М». В кольце осуществляется суперпозиция обоих вращающихся токов с образованием результирующего тока, который имеет неподвижные и равномерно распределенные по окружности кольца пучности, количество которых равно сумме пар входа и выхода исходных токов «N+М» при их вращении в противоположные стороны. При вращении исходных токов в одну сторону, количество пучностей результирующего тока равно разности количества пар входа и выхода исходных токов «N-М». Таким образом, происходит суммирование или вычитание натуральных чисел «N» и «М». Информация о количестве пучностей результирующего тока снимается большим количеством распределенных по окружности кольца тонких электродов, выводы которых соединяются с регистрирующим устройством, которое регистрирует количество пучностей. Чем больше количество выходных электродов, тем больше разрешающая способность при регистрации количества пучностей.

Для создания одного вращающегося тока с определенным количеством пар входа и выхода тока, используется одна двухфазная система входных электродов, установленная на одном из зубчатых периметров кольца и состоящая из двух одинаковых однофазных систем входных электродов АВ и CD. Каждая из однофазных систем входных электродов (АВ или CD) состоит из пар входных электродов. Количество пар входных электродов одной однофазной системы равно количеству пар входа и выхода вращающегося тока. Однофазная система входных электродов присоединяется к отдельной фазе двухфазного напряжения. Между двумя однофазными системами входных электродов существует пространственный сдвиг по окружности кольца на угол равный 90 электрических градусов. Изменение направления вращения вращающегося тока осуществляется реверсивным переключателем 11 путем перемены местами двух выводов одной из однофазной системы входных электродов.

Примеры.

Для проверки возможности работы сумматора натуральных чисел было изготовлено углеродное полупроводящее кольцо с двенадцатью входными электродами, установленными на зубцах наружного периметра кольца, и восьми входными электродами, установленными на зубцах внутреннего периметра кольца (см. фиг. 2). Двенадцать входных электродов на наружном периметре кольца образуют двухфазную систему входных электродов, которая создает первый вращающийся ток с тремя парами входа и выхода тока, а восемь входных электродов на внутреннем периметре кольца образуют двухфазную систему электродов, которая создает второй вращающийся ток с двумя парами входа и выхода тока. Три пары входа и выхода первого вращающегося тока соответствуют натуральному числу «3», а две пары входа и выхода второго вращающегося тока соответствуют натуральному числу «2» (см. фиг. 4). Обе двухфазные системы входных электродов параллельно подключены к источнику двухфазной системы напряжений амплитудой 9 В и частотой 1000 Гц. Выходные электроды выполнены в виде отрезков тонких медных проводов в количестве 40 штук, утопленных в торец кольца между двумя его периметрами. К выходным электродам подключается регистратор 3 для визуального наблюдения количества пучностей, выполненный из сорока светодиодов 12, из которых двадцать светодиодов подключены к общей шине 13 анодом, а другие двадцать - катодом по схеме, изображенной на фиг. 3. Сорок свободных выводов 14 всех светодиодов подключены к выходным электродам сумматора. Светодиодный регистратор распознает переменную разность потенциалов между пучностями результирующего тока и визуально показывает количество пучностей в виде чередующихся ярких и тусклых участков по окружности этого регистратора. При вращении вращающихся токов в противоположные стороны, что соответствует суммированию натуральных чисел «2» и «3», светодиодный регистратор показывает пять неподвижных ярких пятен, равномерно распределенных по окружности регистратора, и каждое яркое пятно охватывает примерно одну десятую часть окружности. При вращении вращающихся токов в одну сторону, светодиодный регистратор показывает одно яркое пятно, охватывающее примерно половину окружности, что соответствует вычитанию натуральных чисел «3» и «2».

На фиг. 4 схематично изображены примеры физической реализации суперпозиции в одном полупроводниковом кольце двух вращающихся электрических токов, один из которых имеет количество пар входа и выхода тока равное трем, а у второго - двум, что соответствует натуральным числам «3» и «2». В результате суперпозиции противоположно вращающихся токов образуется результирующий ток, имеющий пять неподвижных по окружности кольца пучностей, что соответствует сложению натуральных чисел «2+3=5» (см. фиг. 4а). На фиг. 4б показана суперпозиция вращающихся в одну сторону токов с образованием результирующего тока с одной неподвижной пучностью, что соответствует вычитанию натуральных чисел «3-2=1».

Также изготовлен и проверен аналогичный сумматор, выполняющий суммирование и вычитание натуральных чисел «2» и «4», у которого на наружном периметре кольца установлена первая двухфазная система из шестнадцати входных электродов, создающая вращающийся ток с четырьмя парами входа и выхода тока, а на внутреннем периметре кольца установлена вторая двухфазная система из восьми электродов, создающая вращающийся ток с двумя парами входа и выхода тока. При сложении вращающихся токов, светодиодный регистратор показывает шесть неподвижных ярких пятен, каждое из которых охватывает примерно одну двенадцатую часть окружности, что соответствует суммированию натуральных чисел «2» и «4». При вычитании вращающихся токов, светодиодный регистратор показывает два ярких пятна, расположенных диаметрально противоположно, и каждое из них охватывает примерно четверть окружности, что соответствует вычитанию натуральных чисел «4» и «2».

Реферат

Изобретение относится к области вычислительной техники и может использоваться в качестве логического элемента в электрических схемах арифметико-логических устройств и электронно-вычислительных машин, а именно выполняет суммирование и вычитание двух натуральных чисел с получением результата в виде целого неотрицательного числа. Техническим результатом является выполнение быстродействующего сложения или вычитания натуральных чисел N и М без промежуточного преобразования их в двоичный код, а также полное исключение случайной ошибки в процессе вычисления. Сумматор содержит кольцо из полупроводящего материала, имеющее зубчатые наружный и внутренний периметры, в зубцах которых установлены входные электроды, а также снабжен выходными электродами, закрепленными между двумя периметрами. 4 ил.

Формула

Документы, цитированные в отчёте о поиске

Универсальный мостовой инвертирующий сумматор

Комментарии