Устройство программирования длительностей временных интервалов - SU1377822A1

Код документа: SU1377822A1

Чертежи

Описание

1

Изобретение относится к приборам времени и может быть использовано в устройствах с управлением по заданной программе параллельно с работающими объектами.

Целью изобретения является формирование временной информации для нескольких объектов.

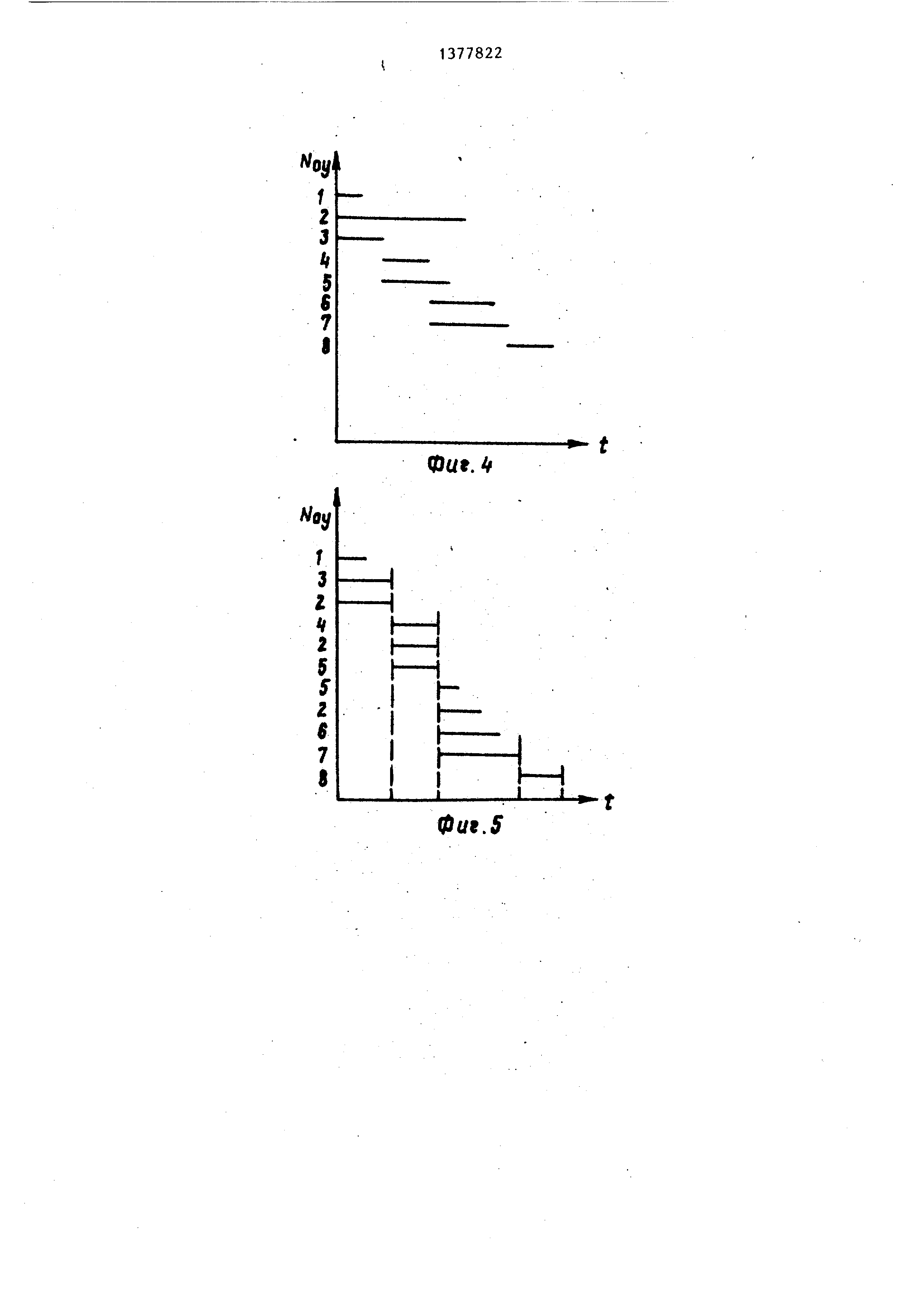

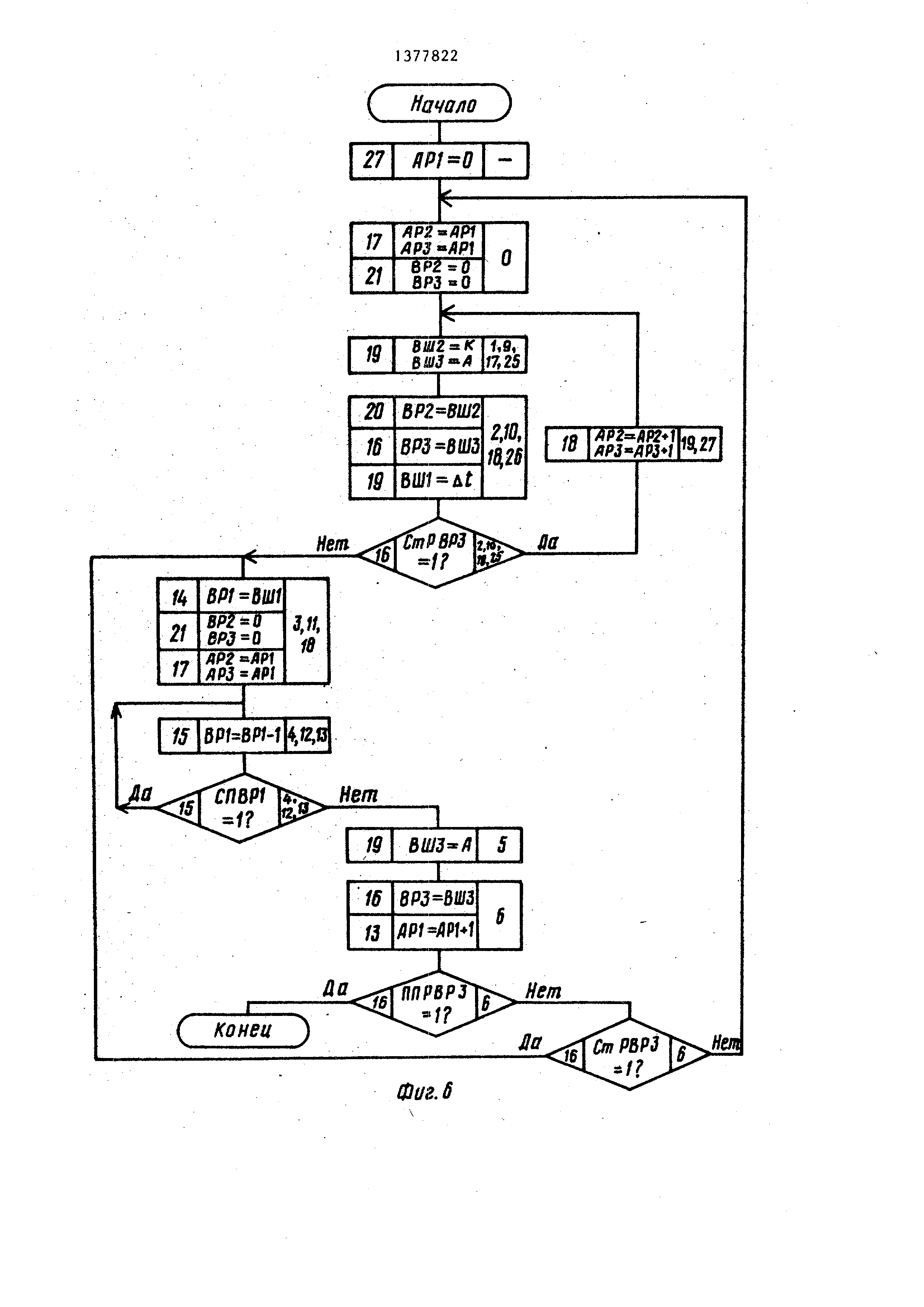

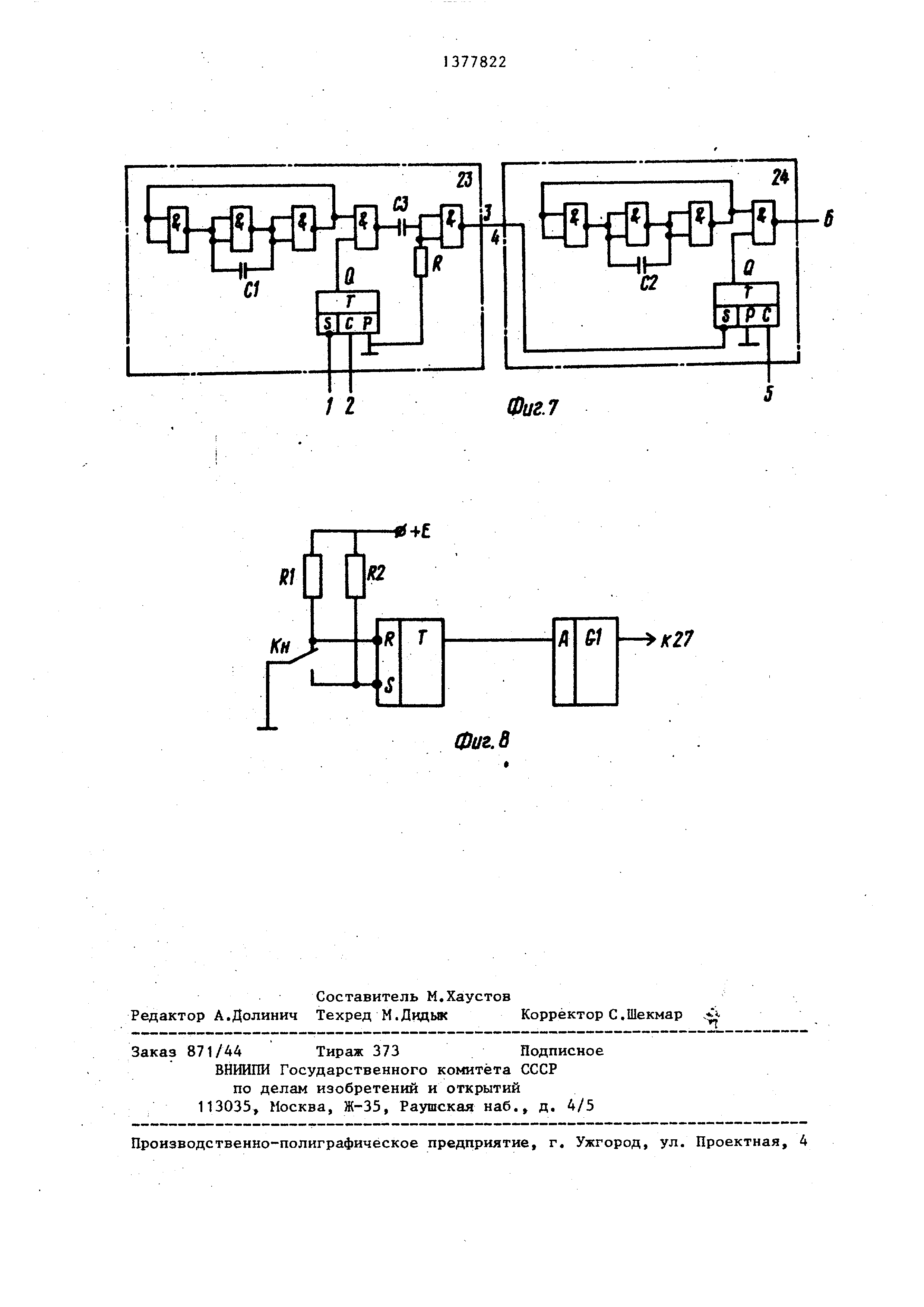

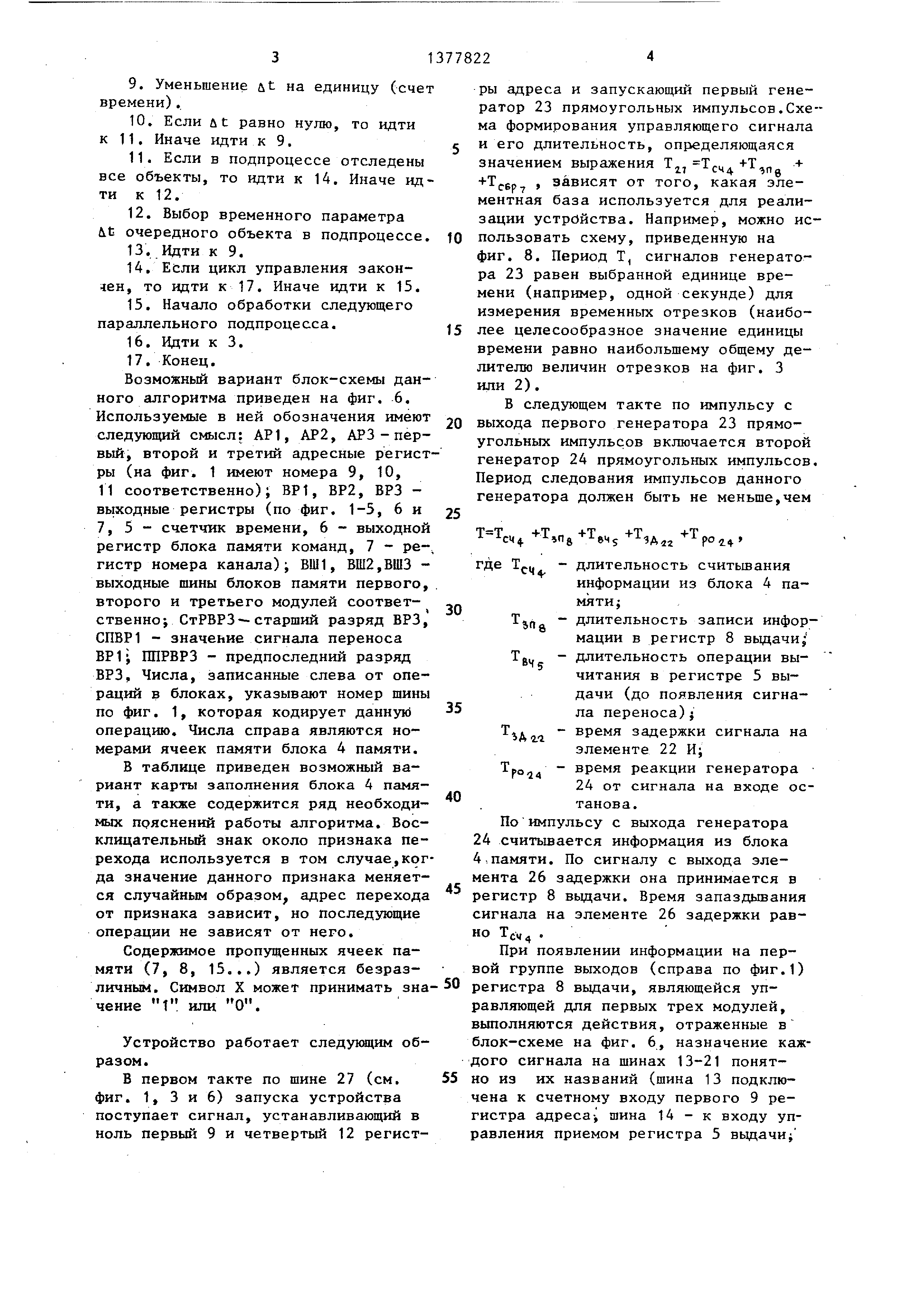

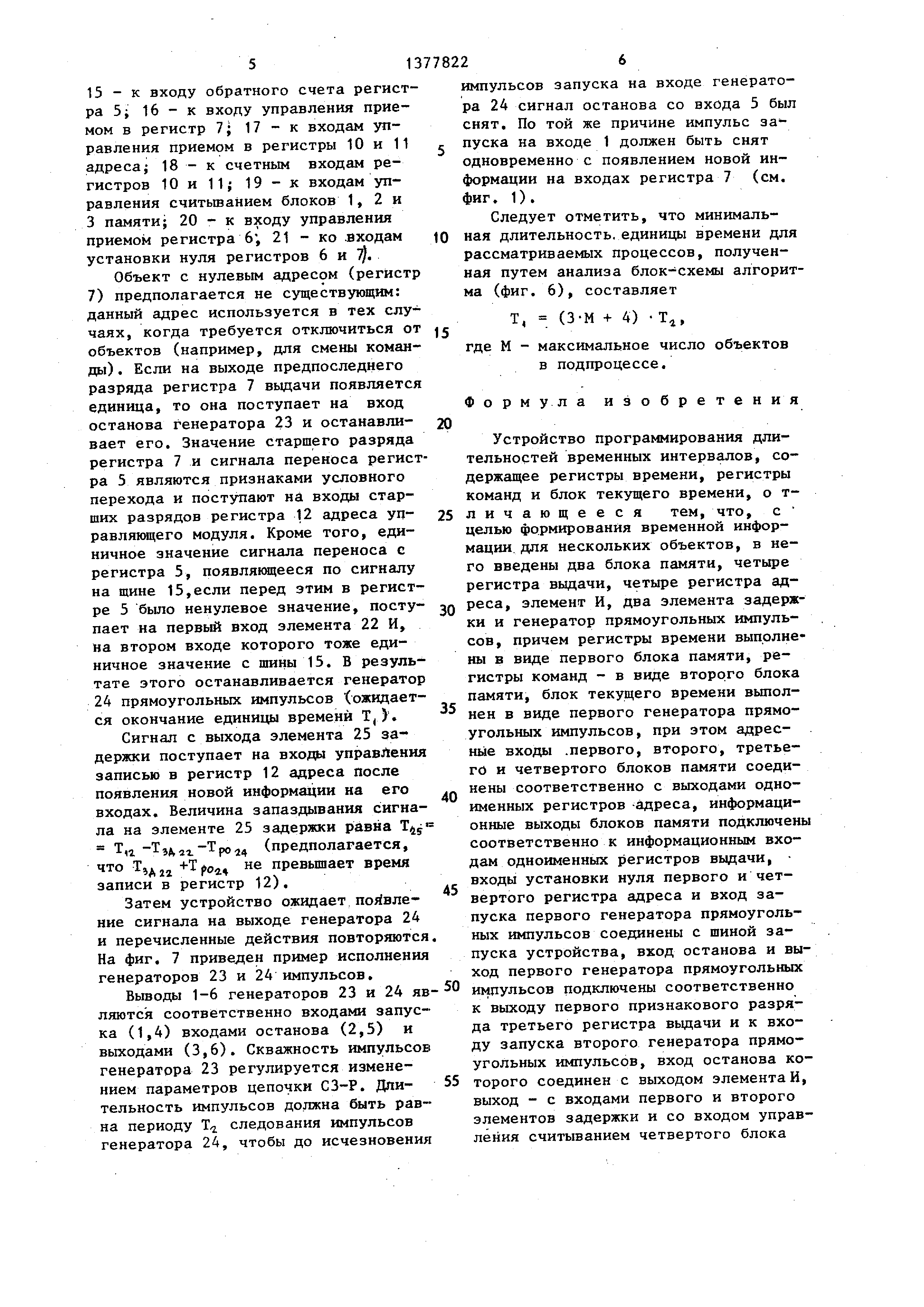

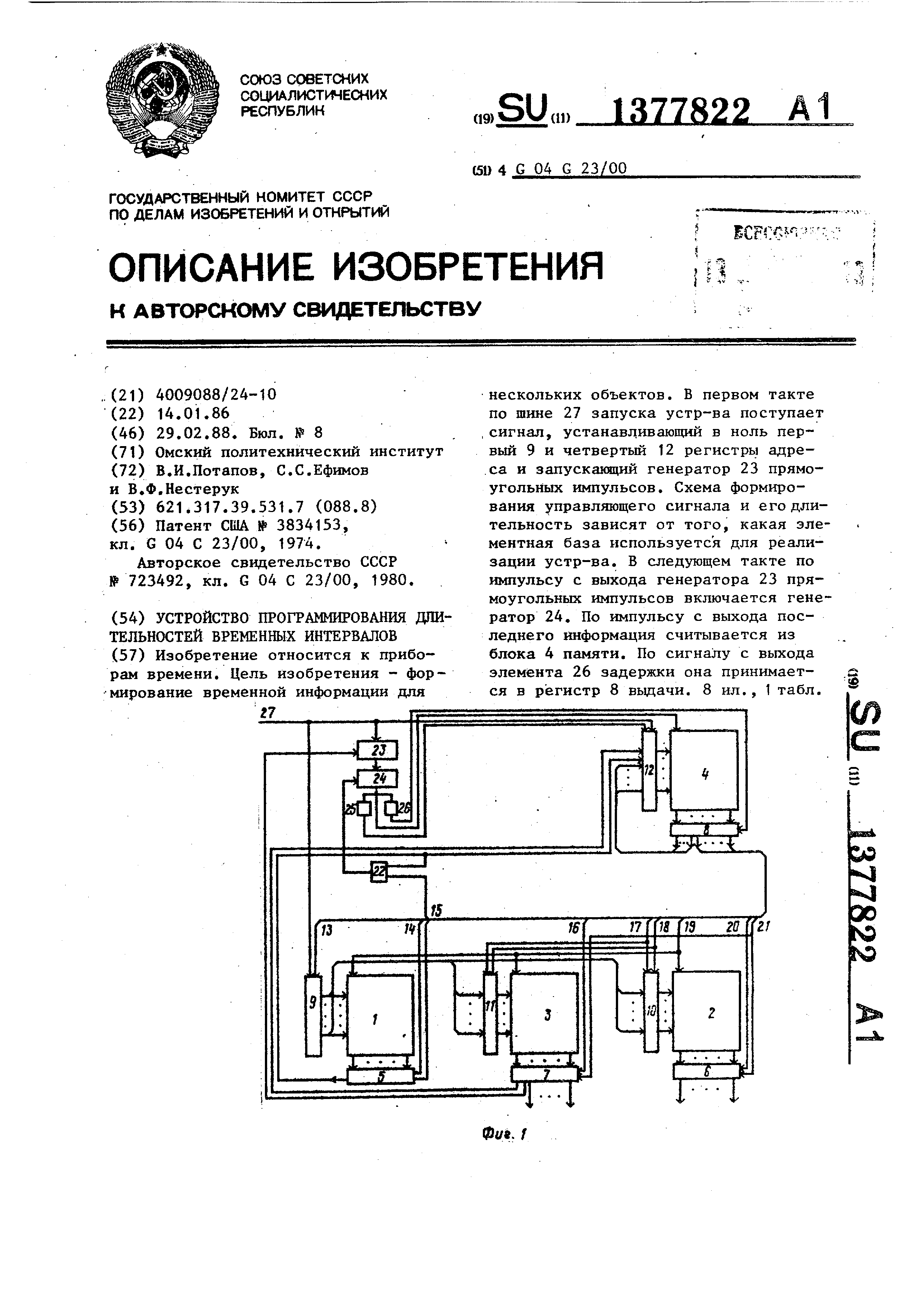

На фиг. 1 изображена схема устройства; на фиг. 2 - пример ступенчатой временной диаграммы, для реализации которых предназначено устройство; на фиг. 3 - окончательный вид, к которому приводится диаграмма; на фиг. 4 и 5 - процесс сведения диаграмм произвольного вида (фиг. 4) к параллельному (фиг. 5)J на фиг. 6 - алгоритм работы устрой- ства на фиг. 7 - пример исполнения генератора импульсов; на фиг. 8 - пример схемы, формирующей сигнал запуска устройства.

Устройство выполнено на основе четырех однотипных модулей, в соста каждого из которых входят блоки 1-4

памяти, регистры 5-8. выдачи и регистры 9-12 адреса. Четвертый модуль, включающий элементы 4, 8 и 12, выполняет функцию управляющей части и pea- JQ нем левом (старшем) разряде нули зализует программу работы трех оставшихся модулей посредством выдачи сигналов через младшую группу выходов регистра 8 выдачи на шины 13-21.

Синхронизация работы устройства осу-

щбствляется частью, состоящей из эле-35 соответствующей концу цикла управ- мента И 22, генераторов 23 и 24 пря- ления (в остальных нули).

В управдяющем модуле (правый верхписаны только в тех ячейках, которые соответствуют последним объектам в подпроцессе, (в остальных - единицы ) , а в соседних разрядах единица записана только в последней ячейке,

моугольных. импульсов и элементов 25 и 26 задержки. Схема включает шину 27 запуска устройства.

На фиг. 2 обозначены: N - номер объекта управления, t - время pia6oTbi объекта. Весь временный цикл состоит из ряда подпрессов, параллельных один другому, внутри калщого из которых длительности работы объектов расположены в порядке возрастания их величин. Окончательный вид, к которому приводится временная диаграмма , приведен на фиг. 3 (каяздый отрезок внутри параллельного подпроцесса представляется в виде приращения к предыдущему). Те алгоритмы управления , для которых невозможно однозначно вьщелить параллельные подпроцессы , т.е. которые-содержат горизонтальные отрезки, относящиеся к нескольким подпроцессам, можно свести к необходимому виду путем разре40

45

НИИ по фиг. 1), который тоже выпол--- няется на основе постоянного запоминающего устройства, хранится алгоритм работы устройства. Данный алгоритм ориентирован на процессы представленные на фиг. 3 и в общем виде ниже.

1.Начало цикла.

2.Начало обработки первого параллельного подпроцесса.

3.Выбор первого объекта в подпроцессе .

.4. Выдача команды к объекту.

5.Если все объекты подпроцесса включены в работу, идти к 8, иначе идти к 6.

6.Выбор очередного объекта в под- 55 процессе.

7.Идти к 4.

8.Выбор временного параметра а t первого объекта в подпроцессе.

50

зания данных отрезков в точках пересечения с границами подпроцессов. При этом номера получившихся отрезков, отнесенных к разным подпроцессам, остаются одинаковыми. Описанные действия иллюстрируются на фиг. 4 и 5.

Процессы рассмотренного типа широко распространены во многих отраслях народного хозяйства: нефтепереработке , нефтехимии, машиностроении и др.

Для подготовки устройства к работе требуется настройка его на определенный процесс. Для этого из имеющегося набора модулей выбирается соответствующий модуль временных задержек (крайний левый по фиг. 1): модуль требуемых команд (крайний справа снизу) и модуль адресов объектов

(посередине), В модуле временных задержек в последовательных ячейках памяти, начиная с нулевой, хранятся значения длин отрезков (фиг. 3 слева - направо), в модуле команд - соответствующие команды (включить, вы- ключить)., в модуле адресов - двоичные коды адресов объектов в порядке, соответствующем фиг. 3 (сверху-вниз). Кроме того, в модуле адресов в край

соответствующей концу цикла управ- ления (в остальных нули).

писаны только в тех ячейках, которые соответствуют последним объектам в подпроцессе, (в остальных - единицы ) , а в соседних разрядах единица записана только в последней ячейке,

НИИ по фиг. 1), который тоже выпол--- няется на основе постоянного запоминающего устройства, хранится алгоритм работы устройства. Данный алгоритм ориентирован на процессы представленные на фиг. 3 и в общем виде ниже.

1.Начало цикла.

2.Начало обработки первого параллельного подпроцесса.

3.Выбор первого объекта в подпроцессе .

.4. Выдача команды к объекту.

5.Если все объекты подпроцесса включены в работу, идти к 8, иначе идти к 6.

6.Выбор очередного объекта в под- процессе.

7.Идти к 4.

8.Выбор временного параметра а t первого объекта в подпроцессе.

9.Уменьшение &t на единицу (счет времени),

10.Если it равно нулю, то идти к 11. Иначе идти к 9.

11.Если в подпроцессе отследены все объекты, то идти к 14. Иначе идти к 12.

12.Выбор временного параметра

it очередного объекта в подпроцессе.

13.Идти к 9.

14.Если цикл управления закончен , то идти к 17. Иначе идти к 15.

15.Начало обработки следующего параллельного подпроцесса.

16.Идти к 3.

17.Конец.

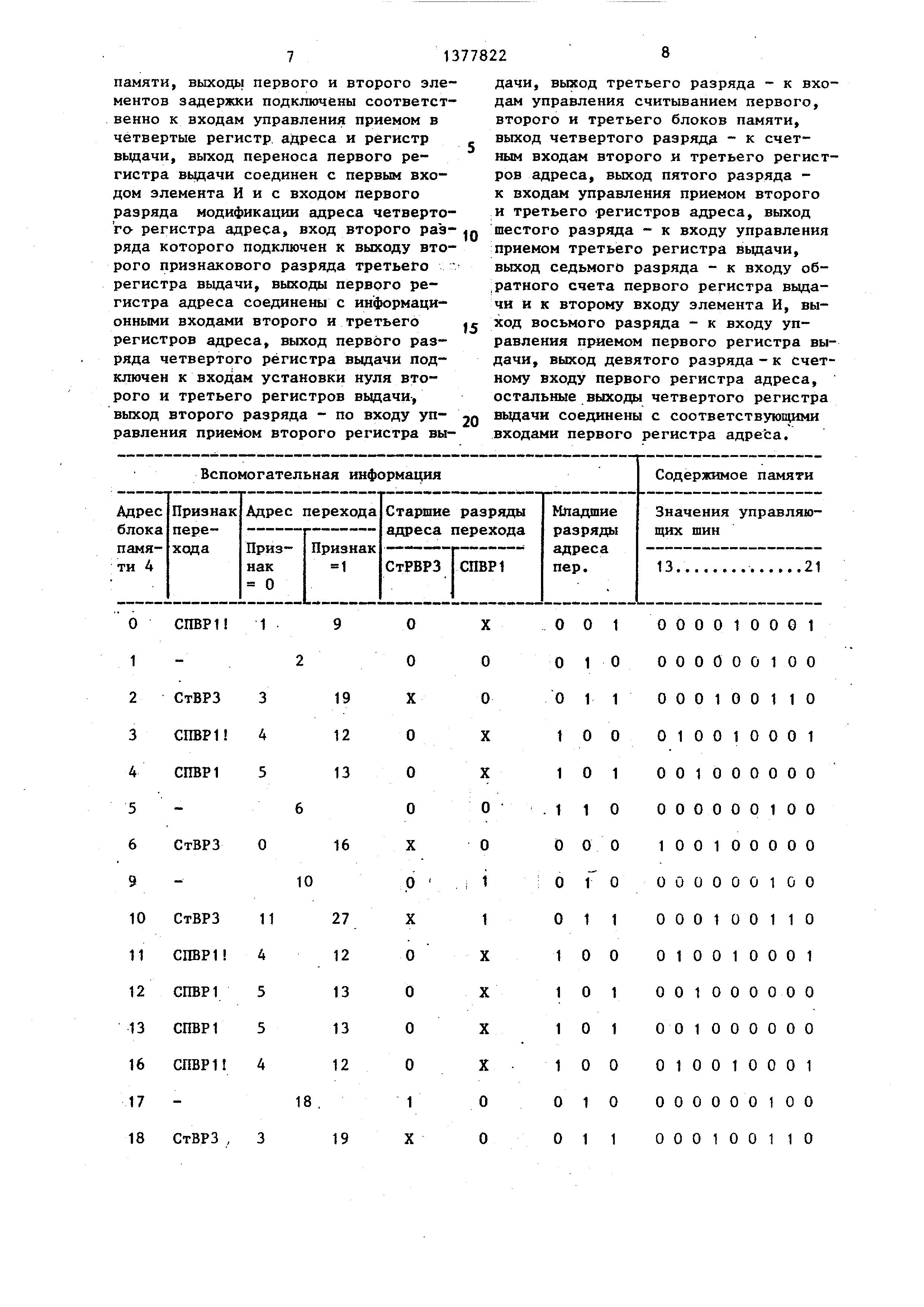

Возможный вариант блок-схемы данного алгоритма приведен на фиг. 6. Используемые в ней обозначения имеют следующий смысл: API, АР2, АРЗ - первый , второй и третий адресные регистры (на фиг. 1 имеют номера 9, 10, 11 соответственно); ВР1, ВР2, ВРЗ - выходные регистры (по фиг. 1-5, 6 и 7,5- счетчик времени, 6 - выходной регистр блока памяти команд, 7 - ре-, гистр номера канала); ВШ1, ВШ2,ВШЗ - выходные шины блоков памяти первого, второго и третьего модулей соответственно; СтРВРЗ- старший разряд ВРЗ, СПВР1 - значение сигнала переноса ВР1; ППРВРЗ - предпоследний разряд ВРЗ, Числа, записанные слева от операций в блоках, указывают номер шины по фиг. 1, которая кодирует данную операцию. Числа справа являются номерами ячеек памяти блока 4 памяти.

В таблице приведен возможный вариант карты заполнения блока 4 памяти , а также содержится ряд необходимых пояснений работы алгоритма. Восклицательный знак около признака перехода используется в том случае,когда значение данного признака меняется случайным образом, адрес перехода от признака зависит, но последующие операции не зависят от него.

Содержимое пропущенных ячеек памяти (7, 8, 15...) является безразличным . Символ X может принимать значение t или О.

Устройство работает следукицим образом .

В первом такте по шине 27 (см. фиг. 1, 3 и 6) запуска устройства поступает сигнал, устанавливающий в ноль первый 9 и четвертый 12 регист0

5

0

5

ры адреса и запускающий первый генератор 23 прямоугольных импульсов.Схема формирования управляющего сигнала и его длительность, определяющаяся значением выражения Т, +1 + +Tj.gp , зависят от того, какая элементная база используется для реализации устройства. Например, можно использовать схему, приведенную на фиг. 8. Период Т, сигналов генератора 23 равен выбранной единице времени (например, одной секунде) для измерения временных отрезков (наиболее целесообразное значение единицы времени равно наибольшему общему делителю величин отрезков на фиг. 3 или 2).

В следующем такте по импульсу с выхода первого генератора 23 прямоугольных импульсов включается второй генератор 24 прямоугольных импульсов. Период следования импульсов данного генератора должен быть не меньше,чем

,, -ьТ,п,+Т,,+Т,,,

0

5

0

5

счц.

an 8

ВЧ5

Ua-i

РО 24

0

5

где Трц - длительность считьшания

информации из блока 4 памяти;

-длительность записи информации в регистр 8 вьщачи;

- длительность операции вычитания в регистре 5 выдачи (до появления сигнала переноса)}

-время задержки сигнала на элементе 22 И;

-время реакции генератора 24 от сигнала на входе останова .

По импульсу с выхода генератора 24 считьшается информация из блока 4.памяти. По сигналу с выхода элемента 26 задержки она принимается в регистр 8 выдачи. Время запаздывания сигнала на элементе 26 задержки равно Тсч4 .

При появлении информации на первой группе выходов (справа по фиг.1) регистра 8 выдачи, являющейся управляющей для первых трех модулей, выполняются действия, отраженные в блок-схеме на фиг. 6, назначение каждого сигнала на шинах 13-21 понятно из их названий (шина 13 подключена к счетному входу первого 9 регистра адреса-, шина 14 - к входу управления приемом регистра 5 вьщачи;

15 - к входу обратного счета регистра 5; 16 - к входу управления приемом в регистр 7; 17 - к входам управления приемом в регистры 10 и 11 адреса; 18 - к счетным входам регистров 10и 11; 19-к входам управления считьшанием блоков 1, 2 и 3 памяти; 20 - к входу управления приемом регистра 6; 21 - ко .входам установки нуля регистров 6 и 7|.

Объект с нулевым адресом (регистр 7) предполагается не существующим: данный адрес используется в тех случаях , когда требуется отключиться от объектов (например, для смены команды ) , Если на выходе предпоследнего разряда регистра 7 вьщачи появляется единица, то она поступает на вход останова генератора 23 и останавли- вает его. Значение старшего разряда регистра 7 и сигнала переноса регистра 5 являются признаками условного перехода и поступают на входы старших разрядов регистра 12 адреса уп- равляющего модуля. Кроме того, единичное значение сигнала переноса с регистра 5, появлякнцееся по сигналу на щине 15,если перед этим в регистре 5 было ненулевое значение, посту- пает на первый вход элемента 22 И, на втором входе которого тоже единичное значение с шины 15. В результате этого останавливается генератор 24 прямоугольных импульсов (ожидается окончание единицы времени Т,).

Сигнал с выхода элемента 25 задержки поступает на входы управления записью в регистр 12 адреса после появления новой информации на его входах. Величина запаздывания сигнала на элементе 25 задержки равна T4j Т,г -Тэл2-1.Тро14 (предполагается, что fo не превьш1ает время записи в регистр 12).

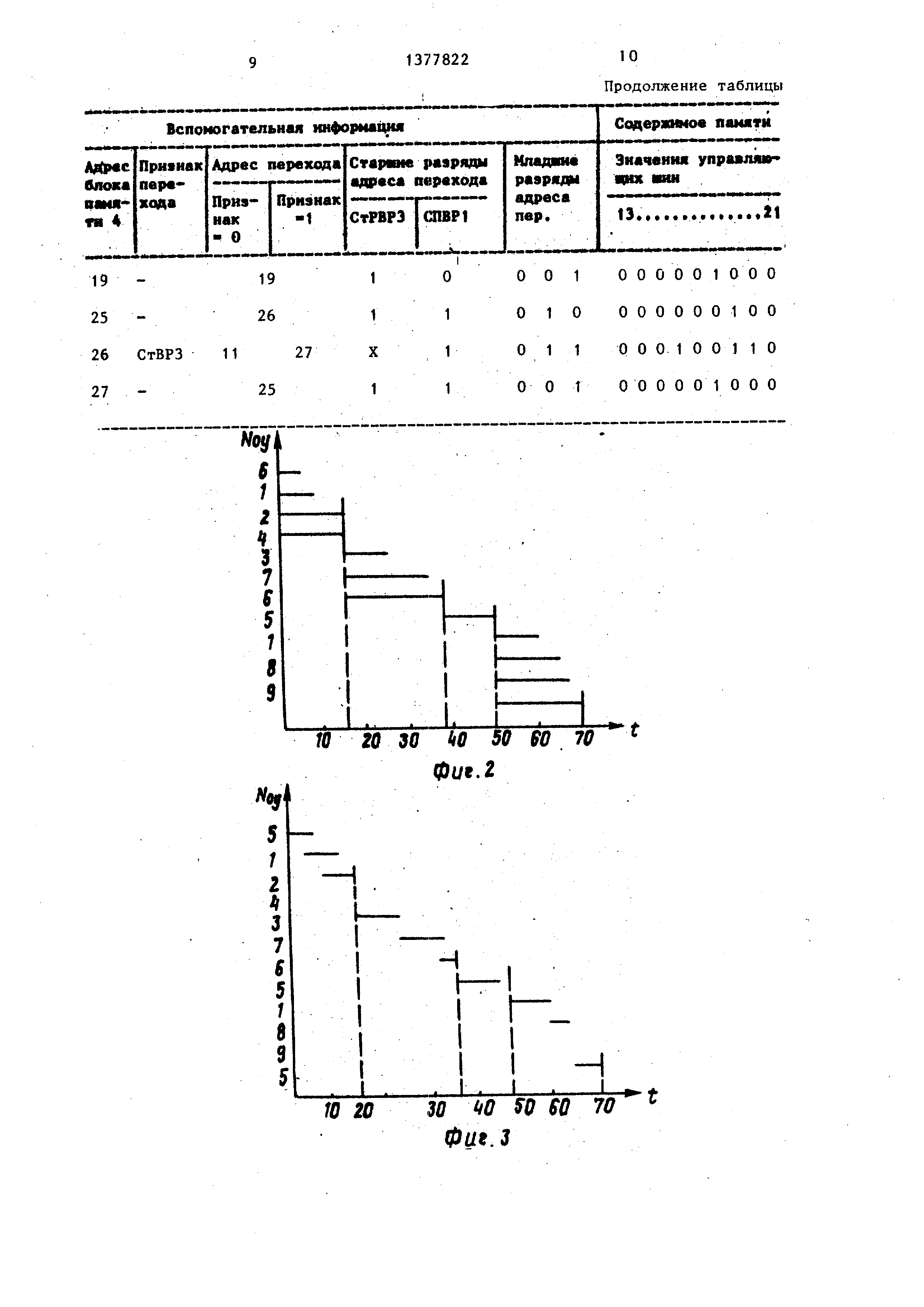

Затем устройство ожидает пойвле- ние сигнала на выходе генератора 24 и перечисленные действия повторяются На фиг. 7 приведен пример исполнения генераторов 23 и 24 импульсов.

Вьюоды 1-6 генераторов 23 и 24 являются соответственно входами запуска (1,4) входами останова (2,5) и выходами (3,6). Скважность импульсов генератора 23 регулируется изменением параметров цепочки СЗ-Р. Дли- тельность импульсов должна быть равна периоду Т следования импульсов генератора 24, чтобы до исчезновения

0 5 д

5

5

0

5

0

импульсов запуска на входе генератора 24 сигнал останова со входа 5 был снят. По той же причине импульс запуска на входе 1 должен быть снят одновременно с появлением новой информации на входах регистра 7 (см. фиг. 1).

Следует отметить, что минимальная длительность, единицы времени для рассматриваемых процессов, полученная путем анализа блок-схемы алгоритма (фиг. 6), составляет

Т, (3-М + 4) -Т,,,

где М - максимальное число объектов в подпроцессе.

Форм у л а изобретен и я

Устройство программирования длительностей временных интервалов, содержащее регистры времени, регистры команд и блок текущего времени, о т- личающееся тем, что, с целью формирования временной информации для нескольких объектов, в него введены два блока памяти, четыре регистра выдачи, четыре регистра адреса , элемент И, два элемента задержки и генератор прямоугольных импульсов , причем регистры времени выполнены в виде первого блока памяти, регистры команд - в виде второго блока памяти, блок текущего времени выполнен в виде первого генератора прямоугольных импульсов, при этом адресные входы .первого, второго, третьего и четвертого блоков памяти соединены соответственно с выходами одноименных регистров адреса, информационные выходы блоков памяти подключены соответственно к информационным входам одноименных регистров выдачи, входы установки нуля первого и четвертого регистра адреса и вход запуска первого генератора прямоугольных импульсов соединены с шиной запуска устройства, вход останова и выход первого генератора прямоугольных импульсов подключены соответственно к выходу первого признакового разряда третьего регистра вьщачи и к входу запуска второго генератора прямоугольных импульсов, вход останова которого соединен с выходом элемента И, выход - с входами первого и второго элементов задержки и со входом управления считыванием четвертого блока

памяти, выходь первого и второго элементов задержки подключены соответственно к входам управления приемом в четвертые регистр, адреса и регистр вьщачи, выход переноса первого регистра выдачи соединен с первым входом элемента И и с входом первого разряда модификации адреса четвертого- регистра адреса, вход второго разряда которого подключен к выходу второго признакового разряда третьего регистра выдачи, выходы первого регистра адреса соединены с информационными входами второго и третьего регистров адреса, выход первого разряда четвертого регистра выдачи подключен к входам установки нуля второго и третьего регистров ввдачи, выход второго разряда - по входу уп- равления приемом второго регистра вы

дачи, выход третьего разряда - к входам управления считыванием первого, второго и третьего блоков памяти, выход четвертого разрядд - к счетным входам второго и третьего регистров адреса, выход пятого разряда - к входам управления приемом второго и третьего регистров адреса, выход шестого разряда - к входу управления приемом третьего регистра выдачи, выход седьмого разряда - к входу обратного счета первого регистра выдачи и к второму входу элемента И, выход восьмого разряда - к входу управления приемом первого регистра выдачи , выход девятого разряда - к счетному входу первого регистра адреса, остальные выходы четвертого регистра выдачи соединены с соответствующими входами первого регистра адреса.

Продолжение таблицы

Фи9.$

( Начало} I

27

Реферат

Изобретение относится к приборам времени. Цель изобретения - формирование временной информации для нескольких объектов. В первом такте по шине 27 запуска устр-ва поступает ,сигнал, устанавливающий в ноль первый 9 и четвертый 12 регистры адреса и запускающий генератор 23 прямоугольных импульсов. Схема формирования управляющего сигнала и его длительность зависят от того, какая элементная база используется для реализации устр-ва. В следующем такте по импульсу с выхода генератора 23 прямоугольных импульсов включается генератор 24. По импульсу с выхода последнего информация считывается из блока 4 памяти. По сигналу с выхода элемента 26 задержки она принимается в регистр 8 выдачи. 8 ил., 1 табл. S

Формула

Комментарии