Сбор данных - RU2541133C2

Код документа: RU2541133C2

Чертежи

Описание

Описанное далее в общем относится к сбору данных и находит конкретное применение в компьютерной томографии (CT). Однако это также может применяться в других медицинских приложениях формирования изображения и немедицинских приложениях формирования изображения.

Сканер компьютерной томографии (CT) содержит рентгеновскую трубку, установленную на поворотной платформе, которая вращается вокруг области исследования относительно продольной оси или оси z. Детекторная матрица охватывает угловую дугу напротив области исследования от рентгеновской трубки. Детекторная матрица обнаруживает излучение, которое пересекает область исследования и предмет или объект, находящийся в ней, и формирует сигнал, характерный для этого. Блок восстановления восстанавливает сигнал и генерирует данные объемного изображения. Данные объемного изображения могут быть обработаны для формирования одного или более изображений.

Детекторная матрица в общем случае содержит матрицу сцинтилляторов, оптически сопряженную с матрицей фотодатчиков, которая электрически связана с электронными средствами обработки. Матрица сцинтилляторов генерирует свет, показательный для излучения, падающего на нее, матрица фотодатчиков генерирует электрический сигнал, характерный для света, и электронные средства обработки содержат аналого-цифровой преобразователь (A/D), который генерирует цифровые данные, указывающие на детектированное излучение, на основе электрического сигнала. Цифровые данные обрабатываются для генерации сигнала, восстановленного блоком восстановления.

К сожалению, по мере того как технология детектирования продолжает развиваться в направлении большего количества срезов, меньших значений ширины среза, меньших сигналов и времен более быстрого вращения, ограничения, связанные с шумом и/или пространственным разрешением, могут ограничить рабочие показатели формирования изображения.

Аспекты настоящей заявки направлены на решение вышеуказанных и других вопросов.

Согласно одному аспекту детектор формирования изображения содержит матрицу сцинтилляторов, матицу фотодатчиков, оптически сопряженную с матрицей сцинтилляторов, преобразователь тока в частоту (I/F) и логику. Преобразователь I/F содержит интегратор и компаратор. Преобразователь I/F преобразует, во время текущего периода интегрирования, заряд, выводимый матрицей фотодатчиков, в цифровой сигнал, имеющий частоту, указывающую на заряд. Логика устанавливает усиление интегратора для следующего периода интегрирования на основе цифрового сигнала для текущего периода интегрирования.

В другом варианте осуществления способ содержит преобразование заряда, указывающего на падающее излучение, в цифровой сигнал, имеющий частоту, показательную для заряда, посредством преобразователя тока в частоту (I/F) мозаики детекторов, и идентификацию усиления для преобразователя I/F на основе выхода преобразователя I/F.

В другом варианте осуществления система формирования изображения содержит источник излучения, который испускает излучение, которое пересекает область исследования, и детекторную матрицу, которая обнаруживает излучение, пересекающее область исследования. Детекторная матрица содержит матрицу сцинтилляторов, матрицу фотодатчиков, оптически сопряженную с матрицей сцинтилляторов, и преобразователь тока в частоту (I/F). Преобразователь I/F содержит интегратор и компаратор и преобразует, во время текущего периода интегрирования, входной заряд от матрицы фотодатчиков в цифровой сигнал, имеющий частоту, показательную для заряда. Логика устанавливает усиление интегратора для следующего периода интегрирования на основе цифрового сигнала для текущего периода интегрирования.

Изобретение может принимать форму в различных компонентах и конфигурациях компонентов и в различных этапах и конфигурациях этапов. Чертежи представлены только в целях иллюстрации предпочтительных вариантов осуществления и не должны рассматриваться как ограничивающие изобретение.

ФИГ. 1 иллюстрирует примерную систему формирования изображения.

ФИГ. 2 иллюстрирует примерную мозаику детекторов.

ФИГ. 3 иллюстрирует примерные электронные средства детектора.

ФИГ. 4 иллюстрирует примерные электронные средства детектора.

ФИГ. 5 иллюстрирует примерные графики усиления.

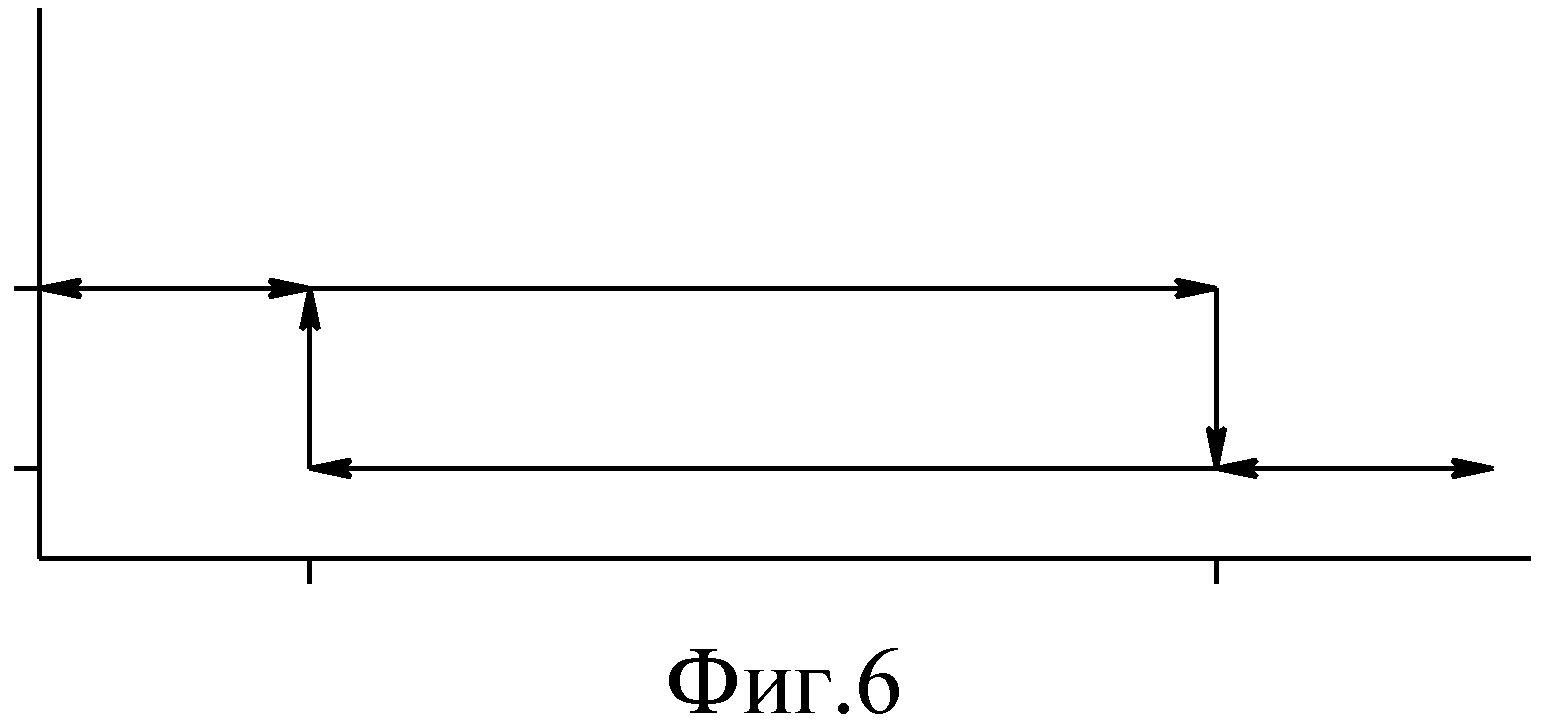

ФИГ. 6 иллюстрирует примерную ступенчатую диаграмму усиления.

ФИГ. 7 иллюстрирует примерную временную диаграмму переключения усиления.

ФИГ. 8 иллюстрирует примерный способ.

ФИГ. 9 иллюстрирует переключатель сброса интегратора с множеством конденсаторов.

ФИГ. 10 иллюстрирует переключатель сброса интегратора с шестнадцатью конденсаторами.

ФИГ. 1 иллюстрирует систему 100 формирования изображения, такую как сканер компьютерной томографии (CT). Система 100 формирования изображения содержит в принципе стационарную платформу 102 и поворотную платформу 104. Поворотная платформа 104 поддерживается с возможностью поворота стационарной платформой 102 и вращается вокруг области 106 исследования относительно продольной оси или оси z. Источник 108 излучения, такой как рентгеновская трубка, установлен на поворотной платформе 104 и испускает излучение, которое пересекает область 106 исследования.

Воспринимающая излучение детекторная матрица 112 охватывает угловую дугу напротив источников 108 излучения через область 106 исследования и детектирует излучение, пересекающее область 106 исследования. В проиллюстрированном варианте осуществления воспринимающая излучение детекторная матрица 112 содержит множество детекторных модулей 114, упорядоченных относительно друг друга вдоль направления, поперечного к оси z. Детекторный модуль 114 содержит множество детекторных мозаик или плиток 116, упорядоченных относительно друг друга вдоль оси z. В одном случае детекторная матрица 112 по существу подобна и/или основывается на детекторной матрице, описанной в патенте США 6,510,195 B1, поданной 18 июля 2001 и озаглавленной "Твердотельные модули детекторов рентгеновского излучения и образованные ими мозаики и использующие их способ и устройство формирования изображения", который полностью включен в настоящий документ посредством ссылки. Другие конфигурации матриц детекторов также могут быть использованы.

На фиг. 2 показан вид мозаики 116 детекторов в сечении по линии A-A на фиг. 1. Показанная мозаика 116 содержит матрицу 202 сцинтилляторов 202, физически и оптически связанную с матрицей 204 фотодатчиков, которая электрически связана с электронными средствами 208 через подложку 206. Электрические дорожки 212, такие как выводы соединителя или другие электрические дорожки, переносят электропитание и цифровые сигналы ввода/вывода. Пример такой мозаики описан в документе "A New 2D-Tiled Detector for Multislice CT", Luhta et al., Medical Imaging 2006: Physics of Medical Imaging, Vol.6142, pp. 275-286 (2006). Другая подходящая мозаика описана в патентной заявке № 60/743,976, поданной 30 марта 2006 и озаглавленной "Матрица детекторов излучения", которая полностью включена в настоящий документ посредством ссылки. Другие электронные средства также могут использоваться.

ФИГ. 3 иллюстрирует примерные электронные средства 208. Аналого-цифровой преобразователь (A/D) 314 содержит интегратор 302 (усилитель 304 и интегрирующий конденсатор 306) и компаратор 310. Интегратор 302 интегрирует заряд, выводимый матрицей 204 фотодатчиков, и ток 300 смещения, если используется, в течение периода интегрирования. Компаратор 310 сравнивает выход усилителя 304 с пороговым значением и генерирует сигнал, показательный для этого, такой как импульс, когда выход увеличивается выше порогового значения. Переключатель 308 сброса сбрасывает интегратор 302 во время периода интегрирования в ответ на генерацию импульса.

В вышеупомянутой конфигурации A/D преобразователь 314 используется как преобразователь тока в частоту (I/F) ввиду того, что он генерирует последовательность импульсов с частотой импульсов, показательной для входного заряда. Пример таких электронных средств дополнительно описан в патенте США 6,671,345 B2, дата подачи 7 ноября 2001, озаглавленном "Сбор данных для компьютерной томографии", который полностью включен в настоящий документ посредством ссылки. Другие подходящие электронные средства описаны в патенте США 4,052,620, дата подачи 28 ноября 1975, озаглавленном "Сбор данных для компьютерной томографии" который полностью включен в настоящий документ посредством ссылки. Другие преобразователи также могут использоваться.

Цифровая логика 312 управляет переключателем 308 сброса, включая замыкание переключателя 308 сброса, чтобы установить в исходное положение интегратор 302 в ответ на обнаружение импульса на выходе компаратора, на границе периода интегрирования, и/или иным образом. Как описано более подробно ниже, переключатель 308 сброса может быть конфигурирован, чтобы включать в себя две или более емкостей сброса, соответствующих двум или более усилениям интегратора, и цифровая логика 312 может быть конфигурирована, чтобы определять усиление для интегратора 302, что может использоваться, чтобы выбрать подходящую емкость сброса из двух или более емкостей сброса. Это обеспечивает возможность динамического выбора более высокого усиления для меньших сигналов заряда и более низкого усиления для больших сигналов заряда, или динамического переключения динамического диапазона, чтобы измерять меньшие и большие сигналы заряда.

Так как аналоговый ток смещения должен генерировать минимальный сигнал для преобразования в цифровую форму в отсутствие реальных сигналов детектора, понятно, что увеличение усиления позволяет снизить величину тока смещения 300, например, на коэффициент усиления или до нуля, и снижение тока смещения 300 может уменьшить дробовый шум (например, на квадратный корень из снижения тока смещения) и/или уменьшить фликкер-шум пропорционально снижению тока смещения. Ошибки линейности в общем случае масштабируются уровнем сигнала и усилением, и значение усиления может использоваться с коррекцией линейности, если она применяется. Низкие уровни сигнала, в общем, имеют подходящую линейность, и, таким образом, такая коррекция может быть ограничена или опущена. В конфигурациях, в которых электронные средства 208 содержат логарифмическое преобразование, коэффициент усиления может быть входом в логарифмический преобразователь, прозрачным для подсистемы восстановления, которая использует логарифмические данные.

Цифровая логика 312 также обрабатывает выход компаратора 310. В одном случае это включает в себя подсчет числа импульсов от компаратора 310 и определение времени от первого импульса периода интегрирования до последнего импульса периода интегрирования. Из этих данных блок 312 цифровой логики может генерировать выходной сигнал, показательный для частоты импульсов (например, число импульсов за период интегрирования/время между первым и последним импульсом в периоде интегрирования), который является характерным для входного заряда.

Согласно ФИГ.1 блок 118 восстановления восстанавливает сигнал детекторной матрицы 112 и генерирует данные объемного изображения, показательные для него. Процессор изображения или т.п. может генерировать одно или более изображений на основе данных изображения. Универсальная вычислительная система служит в качестве пульта 120 оператора. Программное обеспечение, загруженное в пульт 120, позволяет оператору управлять работой системы 100. Опора 122 для пациента, такая как медицинская кушетка, поддерживает объект или предмет, например пациента, в области 106 исследования.

ФИГ. 4 иллюстрирует примерный вариант осуществления переключателя 308 сброса и логики 312. Проиллюстрированный переключатель 308 сброса содержит первый конденсатор 402 с первой емкостью, соответствующей первому усилению интегратора, соединенный с первым переключателем 404, и второй конденсатор 406 со второй емкостью, соответствующей второму усилению интегратора, соединенный со вторым переключателем 408. Хотя две пары переключателя/конденсатора показаны в проиллюстрированном варианте осуществления, в других вариантах осуществления могут быть использованы более двух пар переключателя/конденсатора. В таких вариантах осуществления две или более, включая все из пар, могут соответствовать различным усилениям интегратора.

Каждый из переключателей 404 и 408 независимо переключается между первым состоянием, в котором соответствующий конденсатор 402 или 406 находится в электрической связи с опорным напряжением, и вторым состоянием, в котором соответствующий конденсатор 402 или 406 находится в электрической связи с входом интегратора 302. Переключатели 404 и 408 могут одновременно быть в первом состоянии, но только один из переключателей 404 или 408 находится во втором состоянии в любой момент времени. Во втором состоянии используется соответствующий конденсатор, чтобы сбросить интегратор 302.

Логика 312 содержит идентификатор 410 импульса, который идентифицирует импульс в выходном сигнале компаратора и генерирует сигнал сброса в ответ на это. Сигнал сброса содержит информацию, которая вызывает переключение выбранного одного из переключателей 404 и 408. Например, сигнал может включать в себя информацию, которая приводит к переключению переключателя 404 (или переключателя 408), во время периода интегрирования, которая соответствует усилению в течение этого периода интегрирования, чтобы сбросить интегратор 302 во время того периода интегрирования.

Логика 312 также содержит генератор 412 сигнала усиления, который генерирует сигнал усиления, основанный на отсчете импульсов за период интегрирования, и один или более порогов 414. Счетчик 416 отсчитывает идентифицированные импульсы во время периода интегрирования и генерирует значение отсчета импульсов. Сигнал усиления содержит информацию, указывающую на значение усиления или коэффициент усиления (например, представляя изменение в усилении), который указывает, какой из переключателей 404 или 408 должен быть установлен в исходное положение во время последующего периода интегрирования. Информация может быть представлена двоичными или недвоичными данными.

Вышеописанное позволяет динамически управлять усилением для последующего периода интегрирования на основе уровня сигнала заряда текущего периода интегрирования. Также, когда входной сигнал заряда и, таким образом, отсчет импульсов относительно высок в течение периода интегрирования, более низкое усиление/конденсатор большей емкости выбирается для следующего периода интегрирования. Использование конденсатора более низкого усиления расширяет верхний конец динамического диапазона усилителя, чтобы принимать большие сигналы до перехода в насыщение, по сравнению с использованием конденсатора более высокого усиления.

Когда входной сигнал заряда и, таким образом, отсчет импульсов относительно низкий для периода интегрирования, более высокое усиление/конденсатор меньшей емкости выбирается для следующего периода интегрирования. Использование конденсатора меньшего значения расширяет нижний конец динамического диапазона для измерения меньших сигналов по сравнению с использованием конденсатора более высокого значения. Как обсуждается здесь, расширение нижнего конца динамического диапазона позволяет снизить величину тока смещения, вводимого в интегратор 302.

В вышеописанном примере переключатели 404 и 408 независимо переключаются, и интегратор 302 сбрасывается путем электрического соединения либо первого конденсатора 402, который соответствует первому усилению, либо второго конденсатора 406, который соответствует второму усилению, с входом интегратора 302. В другом варианте осуществления переключатели 404 и 408 могут также одновременно переключаться. В таком варианте осуществления более низкое усиление сброса может быть установлено путем одновременного замыкания обоих переключателей 404 и 408, где емкость сброса является суммарным значением первой и второй емкостей. Более высокое усиление сброса может быть установлено, как описано выше, путем замыкания переключателя 404 (или, альтернативно, переключателя 408) и электрического соединения первого конденсатора 402 (или второго конденсатора 406) с входом интегратора 302.

Совместное использование конденсатора как такового позволяет уменьшить площадь, занимаемую переключателем сброса 308, поскольку второй конденсатор 406 (или первый конденсатор 402) могут быть меньшего размера относительно варианта осуществления без совместного использования конденсатора. Далее, в топологии интегральных схем конденсаторы данного размера могут быть выполнены из меньших конденсаторов, связанных управляемыми переключателями без пассивных элементов, где одно значение большой емкости может быть реализовано из множества (например, шестнадцати (16)) меньших конденсаторов равного или неравного размера, связанных через переключатели. Это позволяет выбирать усиление схемы (значение емкости сброса) цифровым двоичным способом (например, от одного (1) до (16)) и точно воспроизводить размеры конденсаторов за счет расположения их топологии, чтобы учитывать изменения процесса, что может привести к точной линейности для переключения усиления, таким образом, обеспечивая возможность реализации существенно линейного изменения усиления.

Одна неограничительная реализация вышеописанного показана в форме блок-схемы на ФИГ. 9, в который переключатель 308 сброса содержит множество конденсаторов 902, которые могут быть электрически соединены параллельно через переключатели 904, и конкретное значение емкости может быть установлено путем селективного замыкания одного или более переключателей 904. Другая неограничительная реализация показана в форме блок-схемы на ФИГ. 10, где переключатель 308 сброса содержит шестнадцать (16) конденсаторов С1,…, C16, которые могут быть селективно электрически соединены параллельно, чтобы обеспечить конкретные значения емкости сброса, такие как четыре (4), шестнадцать (16) или другое число значений емкости сброса. Те же самые переключатели без пассивных элементов, показанные на ФИГ. 9, могут использоваться в связи с ФИГ.10.

Таблица 1 показывает неограничительные комбинации конденсаторов С1,…,C16, которые могут использоваться, чтобы обеспечить четыре (4) значения емкости сброса RS1,…,RS4, таким образом, что двоичные комбинации емкостей могут быть выбраны, чтобы сформировать значения емкости в приращениях 1/16-й от полного значения, и таблица 2 показывает неограничивающие комбинации конденсаторов С1,…, C16, которые могут использоваться, чтобы обеспечить шестнадцать (16) значений емкостей сброса RS1,…, RS16.

Примерная иллюстрация нижнего и верхнего концов динамического диапазона для двух различных усилений показана на ФИГ.5, где ось y представляет выходной сигнал аналого-цифрового (A/D) преобразователя, и ось x представляет ток на входе интегратора 302. Две кривые усиления, нижняя кривая 504 усиления и верхняя кривая 502 усиления, показаны на ФИГ. 5. Нижняя кривая 504 усиления имеет более высокую точку 506 насыщения уровня заряда относительно точки 508 насыщения для верхней кривой усиления 502, но верхняя кривая 502 усиления имеет более низкий уровень шума 510 относительно уровня шума 512 нижней кривой 504. Как таковая, нижняя кривая 504 усиления подходит для более высоких уровней заряда, а верхняя кривая 502 усиления удовлетворительна для более низких сигналов заряда. Хотя проиллюстрированы линейные кривые усиления, нелинейные кривые усиления также могут быть рассмотрены здесь.

ФИГ. 6 содержит пример подходящей ступенчатой диаграммы усиления. Ось y представляет усиление в течение периода интегрирования, и ось х представляет значение отсчета для периода интегрирования. В проиллюстрированном варианте осуществления усиление переключается между 1x и 4x. Проиллюстрированные шаги усиления и местоположения переключения усиления обеспечены в объяснительных целях и не ограничивают изобретение. В других вариантах осуществления может использоваться другое значение усиления (например, 1, 2, 4, 16, 32 и т.д. или недвоичные шаги), и/или могут использоваться более двух значений усиления (например, 4, 8, 16..., 512 и т.д. или недвоичные значения).

В проиллюстрированном варианте осуществления в предположении, что усиление равно 1x, усиление остается на значении 1x, пока отсчет импульсов для последующего периода интегрирования равен 16 или выше. Если отсчет импульсов для периода интегрирования падает ниже 16, то усиление в течение следующего периода интегрирования переключается на 4x путем выбора конденсатора более низкой емкости, как описано выше. Усиление 4x остается на значении 4x, пока отсчет импульсов для последующего периода интегрирования является меньшим чем 128. Если отсчет импульсов для последующего периода интегрирования повышается выше 128, то усиление в течение следующего периода интегрирования переключается на 1x путем выбора конденсатора большей емкости, как описано выше.

ФИГ. 7 показывает диаграмму выбора времени переключения усиления в качестве примера. В проиллюстрированной диаграмме усиление переключается при 702 после импульса 704 сброса и во время положительной половины 706 тактового сигнала выборки. В одном случае это может гарантировать, что имеется достаточно времени для заряда конденсатора сброса интегратора, так чтобы заряд сброса был корректным. В другом варианте осуществления усиление переключается иным образом.

ФИГ. 8 иллюстрирует способ.

На этапе 802 устанавливается усиление интегратора.

На этапе 804 выполняется сброс интегратора 302 в течение периода интегрирования.

На этапе 806 накапливается заряд в течение периода интегрирования.

На этапе 808 генерируется импульс в течение периода интегрирования, если накопленный заряд превышает предопределенный порог заряда.

На этапе 810 выполняется сброс интегратора 302 в течение периода интегрирования, если накопленный заряд превышает предопределенный порог заряда.

На этапе 812 отсчитываются импульсы для периода интегрирования.

На этапе 814 изменяется значение усиления интегратора 302, если отсчет импульсов попадает за пределы предопределенного диапазона. Как описано здесь, это может включать увеличение усиления, если отсчет импульсов спадает ниже первого порога отсчета импульсов, и уменьшение усиления, если отсчет импульсов повышается выше второго порога отсчета импульсов.

Действия 804-814 повторяются для одного или более периодов интегрирования.

Изобретение было описано в отношении различных вариантов осуществления. Модификации и изменения могут быть выполнены на основе изучения представленного описания. Подразумевается, что изобретение охватывает все такие модификации и изменения, если они входят в объем приложенной формулы изобретения или ее эквивалентов.

Реферат

Изобретение относится к сбору данных и находит конкретное применение в компьютерной томографии (СТ). Сущность изобретения заключается в том, что детектор формирования изображения содержит матрицу (202) сцинтилляторов; матрицу (204) фотодатчиков, оптически сопряженную с матрицей (202) сцинтилляторов; преобразователь (314) тока в частоту (I/F), содержащий интегратор (302) и компаратор (310), который преобразует, во время текущего периода интегрирования, заряд, выведенный матрицей (204) фотодатчиков, в цифровой сигнал, имеющий частоту, указывающую на заряд; логику (312), которая устанавливает усиление интегратора (302) для следующего периода интегрирования на основе цифрового сигнала для текущего периода интегрирования, и переключатель (308) сброса, который сбрасывает интегратор (302) на основе усиления, установленного логикой (312), причем переключатель (308) сброса содержит, по меньшей мере, первый конденсатор (402) сброса с первой емкостью и второй конденсатор (406) сброса с второй отличающейся емкостью. Технический результат - повышение пространственного разрешения. 2 н. и 11 з.п. ф-лы, 10 ил., 2 табл.

Формула

матрицу (202) сцинтилляторов;

матрицу (204) фотодатчиков, оптически сопряженную с матрицей (202) сцинтилляторов;

преобразователь (314) тока в частоту (I/F), содержащий интегратор (302) и компаратор (310), который преобразует, во время текущего периода интегрирования, заряд, выведенный матрицей (204) фотодатчиков, в цифровой сигнал, имеющий частоту, указывающую на заряд;

логику (312), которая устанавливает усиление интегратора (302) для следующего периода интегрирования на основе цифрового сигнала для текущего периода интегрирования, и

переключатель (308) сброса, который сбрасывает интегратор (302) на основе усиления, установленного логикой (312), причем переключатель (308) сброса содержит, по меньшей мере, первый конденсатор (402) сброса с первой емкостью и второй конденсатор (406) сброса с второй отличающейся емкостью.

счетчик (416), который считает импульсы на выходе компаратора (310);

один или более порогов (414) отсчета; и

генератор (412) сигнала усиления, который генерирует сигнал усиления, указывающий на усиление, на основе отсчета и одного или более порогов (414) отсчета.

идентификатор (410) импульса, который идентифицирует импульсы на выходе компаратора (310),

причем счетчик (416) считает идентифицированные импульсы, и генератор (412) сигнала усиления генерирует сигнал усиления на основе отсчета идентифицированных импульсов.

преобразование заряда, указывающего на падающее излучение, в цифровой сигнал, имеющий частоту, указывающую на заряд, посредством преобразователя (314) тока в частоту (I/F), из детекторной мозаики (116), причем преобразователь I/F содержит интегратор и компаратор;

идентификацию усиления для преобразователя (314) I/F на основе выхода преобразователя (314) I/F, и

сброс интегратора на основе идентифицированного усиления, причем сброс выполняется посредством переключателя сброса, который включает в себя первый конденсатор сброса с первой емкостью и второй конденсатор сброса с второй отличающейся емкостью, причем первая емкость или вторая отличающаяся емкость соответствует первому усилению сброса, и суммарное значение первой емкости и второй отличающейся емкости соответствует второму усилению сброса.

Комментарии