Логика интерфейса для многоядерной "системы на кристалле" (soc) - RU2470350C2

Код документа: RU2470350C2

Чертежи

Описание

Уровень техники

По мере развития полупроводниковых технологий все большее количество функций может быть размещено на одной полупроводниковой микросхеме. Принимая во внимание, что использовавшиеся ранее отдельные интегральные схемы обеспечивали разные функции, такие как функции обработки, функции управления, функции интерфейса и т.д., современные полупроводники позволяют встраивать множество функций, таких как эти, в одной интегральной схеме.

Подтверждением этой тенденции является все увеличивающееся количество устройств типа "система на кристалле" (SoC), которые становятся доступными. Такие одиночные интегральные схемы (IC), размещенные на одном кристалле, включают в себя различные схемы, такие как схема обработки, схема интерфейса, схема специализированной функции и т.д. Таким образом, встроенные устройства и портативные устройства, такие как мобильные терминалы, сетевые компьютеры-ноутбуки и т.д. могут быть воплощены с использованием меньшего количества устройств. Эта тенденция также очевидна в процессорных технологиях, поскольку современные процессоры могут включать в себя множество ядер в одной упаковке, то есть становятся доступными двухъядерные, четырехъядерные и многоядерные варианты воплощения. Обычно SoC включают в себя процессор на одном ядре, что может представить ограничение при их использовании.

Краткое описание чертежей

На фиг.1 показана блок-схема "системы на кристалле" (SoC) в соответствии с одним вариантом выполнения настоящего изобретения.

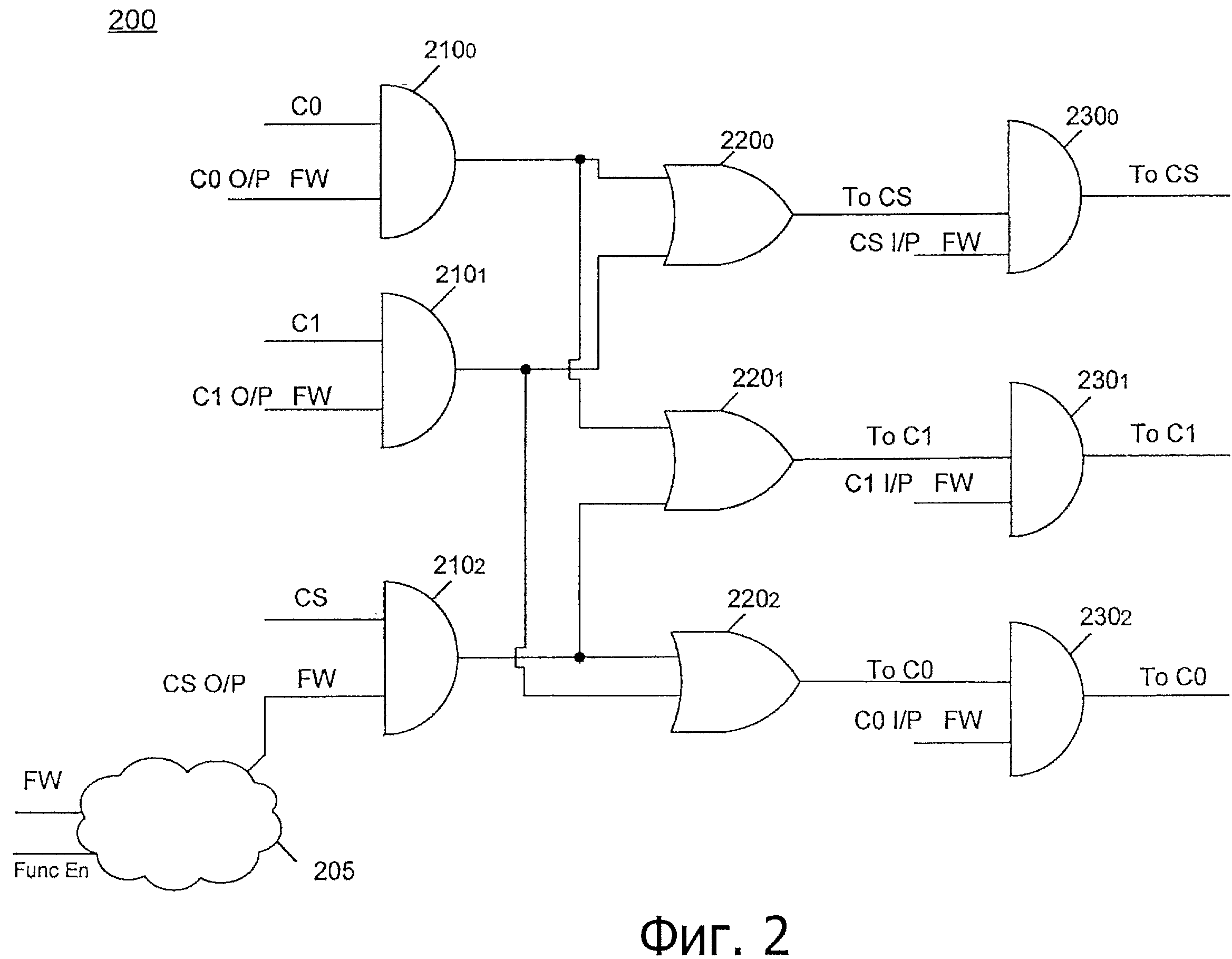

На фиг.2 показана схема логики для выполнения задач шины в соответствии с вариантом выполнения настоящего изобретения.

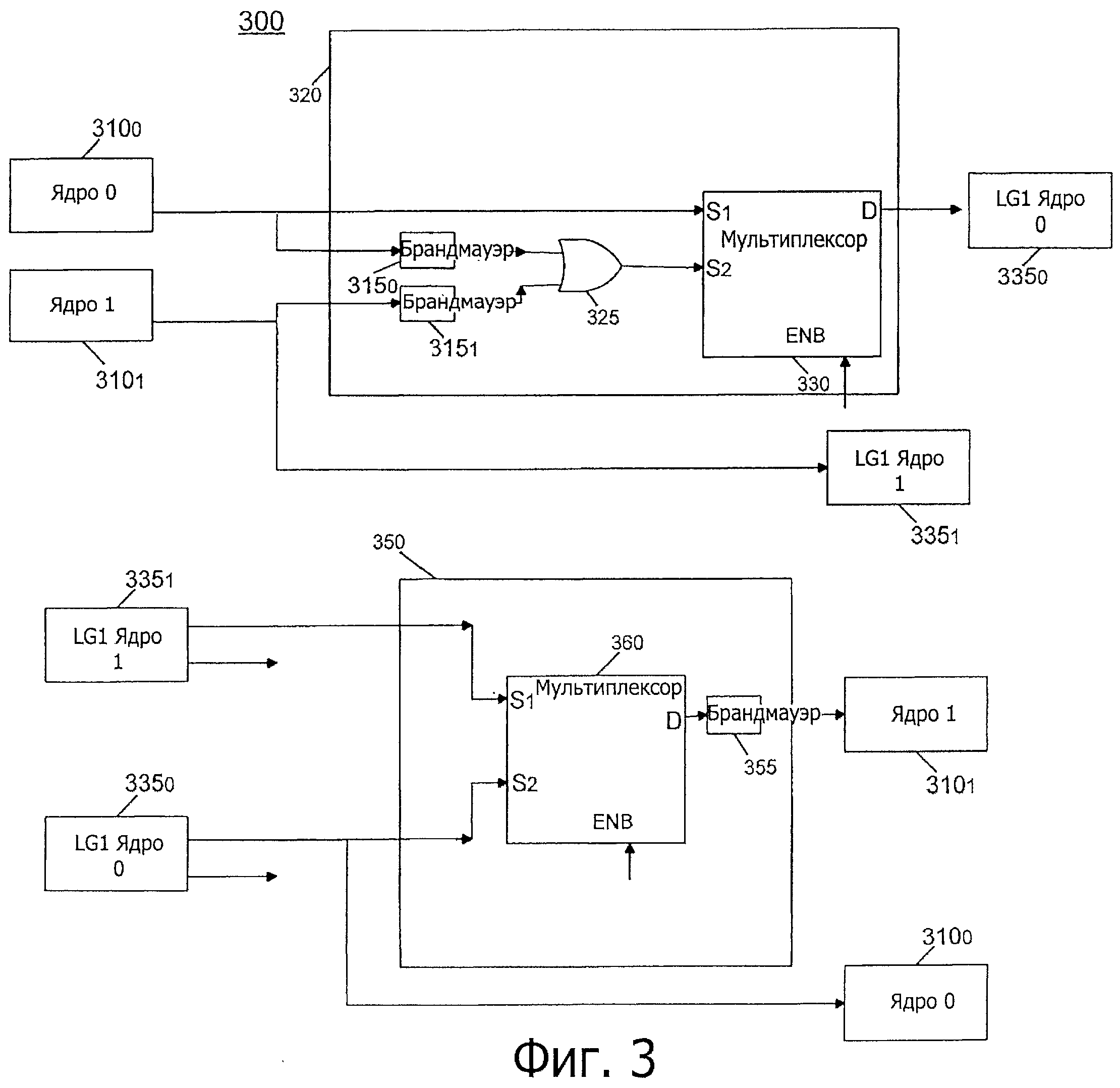

На фиг.3 показана блок-схема тестовой логики в соответствии с вариантом выполнения настоящего изобретения.

На фиг.4 показана блок-схема последовательности операций способа в соответствии с одним вариантом выполнения настоящего изобретения.

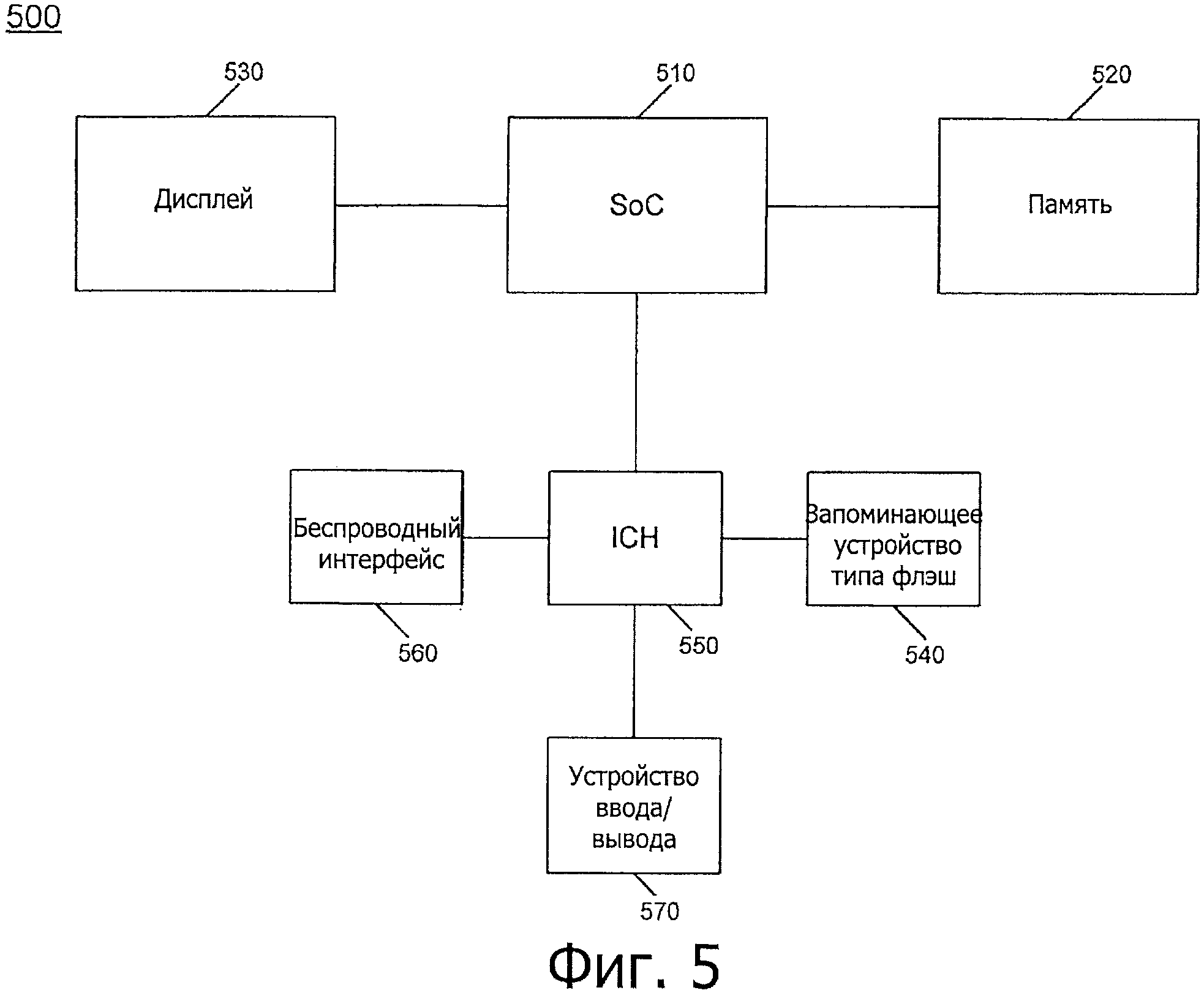

На фиг.5 показана блок-схема системы в соответствии с одним вариантом выполнения настоящего изобретения.

Подробное описание изобретения

В различных вариантах выполнения в многоядерной "системе на кристалле" (SoC) может быть предусмотрена логика интерфейса для соединения с одним или больше интегрированными ядрами, также называемыми здесь центральными процессорными устройствами (CPU, ЦПУ), с интегрированным контроллером памяти и ассоциированными буферами ввода-вывода (I/O). ЦПУ, которые в одном варианте выполнения могут представлять собой пару ядер, соединены с оставшейся SoC через взаимное соединение внутренней системной шины (FSB). Логика интерфейса дополнительно обеспечивает доступ к функциям и тестам в виде одноядерной конфигурации (в дополнение к двухъядерной) для обеспечения рыночной гибкости и гибкости при полномасштабном производстве (HVM). В одном варианте выполнения логический компонент интерфейса может соединять два ЦПУ с другой логикой набора схем (например, контроллером северного моста) в SoC. Логика интерфейса может быть объединена при поддержке одноядерных или двухъядерных единиц складского учета (SKU).

В одном варианте выполнения такая логика интерфейса может таким образом действовать для преобразования интерфейса двухъядерного ЦПУ iFSB (внутренняя системная шина) в одиночный iFSB для обмена данными с логикой набора схем (то есть, с соответствующим компонентом северного моста, имеющим функцию контроллера памяти). Кроме того, логика обеспечивает интерфейс и брандмауэр, которые способствуют размещению двухъядерной конструкции ЦПУ для тестирования (DFX), а также использованию брандмауэра для виртуального отключения одного из ядер (например, ЦПУ1). Логика может также обеспечить интерфейс для оверлея, загружаемого в конфигурацию при включении питания (РОС) из логики набора схем в независимую шину РОС в ЦПУ и интерфейс для оверлея тестирования прямого доступа (DAT) из логики набора схем в независимую шину DAT в ЦПУ. Также, кроме того, логика интерфейса выполняет маршрутизацию всех сигналов, для которых требуется сдвиг уровня между напряжением (Vcc) ядра и напряжением (Vnn) SoC.

Рассмотрим теперь фиг.1, на которой показана блок-схема системы на кристалле (SoC) в соответствии с одним вариантом выполнения настоящего изобретения. Как показано на фиг.1, SoC 100 может быть воплощена на одном полупроводниковом кристалле. В варианте выполнения, показанном на фиг.1, присутствует двухъядерный процессор 110, включающий в себя первое ЦПУ 1150 и второе ЦПУ 1151. Кроме того, каждое ЦПУ имеет свой собственный контур 1180 и 1181 фазовой автоматической синхронизации (PLL), который может использоваться для генерирования различных сигналов тактовой частоты, используемых ядрами.

Как можно видеть, различные взаимные соединения соединяют процессор 110 с другими компонентами SoC. Каждое ЦПУ может связываться с логикой 120 интерфейса через различные взаимные соединения, включающие в себя внутреннюю системную шину (iFSB), тестовое взаимное соединение прямого доступа (DAT) и канал унаследованных входов-выходов (LIO). Аналогично, FSB и тестовые каналы могут быть соединены через логику 120 интерфейса с каждым ЦПУ, в дополнение к передаче сигналов конфигурации при включении питания (РОС). Следует отметить, что в варианте выполнения, показанном на фиг.1, затушеванные компоненты ЦПУ 1 обозначают, что этот процессор может быть выполнен с возможностью его отключения (то есть он может быть виртуально отключен) в заданном варианте выполнения системы. Таким образом, общий набор масок и единый процесс изготовления можно использовать при производстве SoC из одной кремниевой пластины и, в зависимости от требований заказчика (и уровня цены), может быть включено одно или оба ЦПУ.

Как дополнительно показано на фиг.1, логика 120 интерфейса включает в себя различные логические компоненты, которые обеспечивают интерфейс между процессором 110 и другими компонентами SoC, включающими в себя логику 130 набора схем, которая в одном варианте выполнения может включать в себя различную логику интерфейса и управления, включая в себя графическую логику 134 и контроллер 136 памяти, которые могут обеспечивать возможность обмена данными с памятью, такую как динамическое оперативное запоминающее устройство (DRAM), соединенное с SoC. Как также можно видеть на фиг.1, логика 130 набора схем дополнительно включает в себя функции уровня через блоки 132a и 132b сдвига уровня, которые действуют так, что выполняется преобразование напряжения на уровень с уровня напряжений уровня ЦПУ (то есть VCC) и напряжения логики набора схем (то есть VNN). В различных вариантах выполнения логика 130 набора схем может иметь интерфейсы с компонентами, находящимися вне пределов микросхемы, такими как южный мост системной памяти, или другим интерфейсом с периферийными устройствами.

Как можно видеть, логика 120 интерфейса включает в себя логику 122 шины, предназначенную для обработки различной комбинационной логики, для передачи через интерфейс сигналов между логикой 130 набора схем и логикой 120 интерфейса через первое взаимное соединение 125 и для подготовки этих сигналов для передачи в процессор 110 через взаимные соединения 114. Кроме того, логика 120 интерфейса включает в себя логику 124 DFX для осуществления различного управления DFX, которое может быть передано как в процессор 110, так и в логику 130 набора схем. Логика 120 интерфейса также включает в себя логику 126 брандмауэра для выполнения операции брандмауэра как во время тестовых режимов, так и при выполнении функциональной операции, для виртуального отключения ЦПУ 1151, если он имеет такую конфигурацию. Другими словами, во время такого виртуального отключения двухъядерное ЦПУ преобразуется в одноядерное ЦПУ, что может быть выполнено, используя пережигание плавких перемычек для дифференциации продукта или для испытаний. Используя режимы брандмауэра, каждое ядро может быть независимо протестировано как отдельное ЦПУ или по одному ядру одновременно (например, ЦПУ 0 или ЦПУ1), или оба ЦПУ могут проходить один и тот же тест параллельно (как отдельные ядра). Следует отметить, что также имеется другая функция логики 126 брандмауэра, предназначенная для HVM. Она отличается от виртуального отключения, поскольку представляет собой испытательный режим (а не функциональный режим), при котором оба ЦПУ могут выполнять один и тот же тест параллельно, как если бы они представляли собой одно ядро.

Дополнительная логика интерфейса представлена через SoC 100. Как можно видеть, отдельная логика 138 виртуального брандмауэра расположена между логикой 130 набора микросхем и процессором 110. Такая отдельная логика может использовать разные энергетические ямы и, таким образом, показана как отдельный логический модуль, хотя с точки зрения функций ее можно рассматривать как часть логики 126 брандмауэра. Кроме того, различные интерфейсы ввода/вывода (I/O) могут соединять определенные компоненты для организации связей с элементами, расположенными вне микросхемы. Как можно видеть, каждое ядро может иметь индивидуальный интерфейс 145 и 150 I/O соответственно. Также, кроме того, общий интерфейс 140 I/O может также соединять процессор 110 с элементами, расположенными вне микросхемы. Еще один общий интерфейс 155 I/O может обеспечивать канал передачи данных между компонентами, расположенными за пределами микросхемы, и логикой 120 интерфейса, и ЦПУ 115. Хотя это показано в данном конкретном варианте осуществления, включающем в себя двухъядерный процессор, для варианта выполнения, представленного на фиг.1, следует понимать, что объем настоящего изобретения не ограничен этим, и могут присутствовать другие варианты выполнения многоядерного процессора, включающие в себя более чем два ядра, в которых одно или больше ядер могут быть выполнены с возможностью виртуального отключения для заданной системы конфигурации.

Для выполнения функции двухъядерного FSB каждое ЦПУ содержит логический элемент ИЛИ с его собственными сигналами обратной связи (как при работе с одним ядром, так и при работе с двумя ядрами). Для режима работы с двумя ядрами сигналы логического интерфейса И-ИЛИ iFSB из второго (то есть другого) ядра и логики набора схем могут быть предоставлены логикой интерфейса. Таким образом, каждое ЦПУ ожидает увидеть сигнал, переданный в него через логику набора схем и другое ЦПУ, а также сигнал, который оно формирует для эквивалентных сигналов FSB. Все сигналы в iFSB из ЦПУ и логики набора схем, как ожидается, равны нулю, когда они неактивны. Поскольку ЦПУ не вырабатывает ноль по умолчанию, когда он неактивен, это вместо ЦПУ выполняет логика интерфейса. В некоторых вариантах выполнения отсутствует последовательная логика в логике интерфейса (что может повлиять на некоторые режимы доступа к тестам), и тактовая частота ЦПУ не направляется через логику интерфейса.

Рассмотрим теперь фиг.2, на которой показана схема логики для выполнения задач FSB в соответствии с вариантом выполнения настоящего изобретения. Как показано на фиг.2, логика 200 может быть встроена как часть логики 120 интерфейса, то есть как часть логики 122 шины. Обычно логику 200 можно использовать для выполнения комбинационных операций для реализации логического элемента И-ИЛИ, как описано выше. В частности, как можно видеть, первый уровень логики 2100-2102 типа И может быть соединен для приема и вывода сигналов из соответствующего ядра (или компонента набора схем) и соответствующего выходного сигнала брандмауэра ядра. Как можно видеть, выходной сигнал брандмауэра может быть сгенерирован в независимом логическом блоке 205. Следует отметить, что на фиг.2 показан только один такой блок для элемента набора схем, хотя аналогичная логика присутствует для двух ядер. Как можно видеть, этот логический блок принимает сигналы брандмауэра вместе с функциональным сигналом включения, который может представлять собой сигнал включения адреса, выход которого действует как выходной сигнал брандмауэра в соответствующую логику 210 И. Как снова показано на фиг.2, выход логики 210 И может быть соединен в комбинации со вторым уровнем логики 2200-2202 И, что, в свою очередь, обеспечивает выход на третий уровень логики 2300-2302 И, что действует как объединение выходов логики 220 ИЛИ, и соответствующего входного сигнала брандмауэра. Соответствующие выходы логики 230 И передают в идентифицированное ядро (или набор схем), которое таким образом действует как логический элемент И-ИЛИ для сигналов интерфейсов из другой логики ядра и набора микросхем.

Как описано выше, варианты выполнения также обеспечивают возможность виртуального отключения. Виртуальное отключение ядра (VC) относится к возможности сделать так, чтобы двухъядерный процессор выглядел как одноядерный процессор, без физических изменений на кремниевой подложке. Такое свойство может быть включено для производимых деталей и также для обеспечения возможности отладки программ. SoC может быть выполнена с возможностью работы, как одноядерный продукт с подачей или без подачи питания к одному из ЦПУ (отключенное ЦПУ называется здесь ЦПУ 1). Однако в этом режиме возможность отключения питания не доступна как переключатель ЦПУ. Такое управление может быть выполнено с использованием решения в пакете/на материнской плате, которая может быть воплощена как SoC. Когда питание отключают в результате виртуального отключения SoC, его отключают для ЦПУ 1 и соответствующих компонентов, например, IOPLL1 и LGI_CORE1. В одном варианте выполнения ЦПУ 0 отключает тактовую частоту от ЦПУ 1, когда оно отключено, для сведения к минимуму потребления энергии в случае, если подача питания будет продолжена.

Для отключения одного ядра обычно практически каждый входной и выходной сигнал ЦПУ 1 отправляют в брандмауэр. Исключения брандмауэра отмечены ниже. Входные/выходные сигналы, которые обрабатывают в брандмауэре для неиспользуемого ЦПУ 1, принудительно переводят в состояние "0" (неактивное), когда индикатор VC является активным. В одном варианте выполнения исключения сигнала брандмауэра для ЦПУ 1 VC могут включать в себя следующие сигналы: POWERGOOD (нормальное питание), который обеспечивает возможность устранения активного состояния сигнала вначале, чтобы обеспечить возможность сброса конфликтных ситуаций в ЦПУ 1 с помощью тактовой частоты кольцевого генератора. Но затем сигнал POWERGOOD переводят в активное состояние для остановки кольцевого генератора для экономии энергии. Сигнал ЦПУ 1<->LGI_CORE 1 представляет собой другое исключение, поскольку для LGI_CORE 1 также отключают питание, или отключают тактовую частоту в режиме VC. Другой сигнал ЦПУ 1<->IOPLL 1 представляет собой другое исключение, поскольку питание для IOPLL 1 отключают или отключают тактовую частоту в режиме VC. Кроме того, определенные аналоговые сигналы, включающие в себя сигнал тактовой частоты ядра, и RESET могут представлять собой исключения из брандмауэра.

В одном варианте выполнения возможны два способа, которые обеспечивают возможности виртуального отключения ЦПУ 1. Во-первых, путем пережигания плавких перемычек среди плавких перемычек ЦПУ 0 включают VC ЦПУ 1. Две версии такого сигнала плавкой перемычки VC могут быть переданы, одна в логику 120 интерфейса и другая в логику 138 брандмауэра. Во-вторых, сигнал из логики 130 набора схем (например, сигнал связывания выводов (переопределение назначения других выводов при подаче сигнала на определенный вывод)) можно использовать для включения в случае необходимости VC ЦПУ 1. Вторую версию этого сигнала связывания выводов передают из логики 130 в логику 138 виртуального брандмауэра. Сигнал связывания вывода VC будет иметь разрешенное напряжение в течение нескольких циклов после объявления PWROK/CPUPWRGOOD. В одном варианте выполнения сигнал может быть по умолчанию отключен таким образом, что второе ЦПУ будет включено.

В одном варианте выполнения два включенных VC вместе могут представлять собой "ORed" для формирования сигнала включения ячейки брандмауэра. Таким образом они имеют равный приоритет. При отключении тактовой частоты для виртуально отключенного ЦПУ 1 может возникнуть следующее. Вначале параллельные плавкие перемычки становятся действительными, и сигнал разрешения плавкой перемычки VC подают в логику 130 интерфейса и в логику 138 виртуального брандмауэра. Затем убирают объявление PWRGOOD и запускают сигналы тактовой частоты кольцевого генератора для устранения конфликтов в ЦПУ 1. PWRGOOD заявляет и останавливает кольцевой генератор. В конечном итоге, сигнал RESET комбинируют с индикаторами VC в логике 138 виртуального брандмауэра с тем, чтобы отключить тактовую частоту ЦПУ 1. Следует отметить, что ((~RESET И (плавкая перемычка VC ИЛИ сигнал связывания VC)) обеспечивает подачу сигнала DEEPSLEEP в ЦПУ 1, когда происходит отключение объявления RESET и включает VC. Объявленный сигнал DEEPSLEEP отключает тактовую частоту ЦПУ 1.

Логика 124 DFX также может быть предусмотрена как часть логики 120 интерфейса, которая может использоваться для обеспечения тестирования двух ядер и для отладки и минимизации испытательных выводов и маршрутов путем мультиплексирования с функциональными сигналами. Логика 124 может обеспечивать DFX с тем, чтобы обеспечить возможность одновременного и независимого тестирования логики ЦПУ и SoC. Брандмауэр используется для поддержания входных/выходных сигналов ЦПУ на логическом "0" таким образом, что любое переключение сигнала, которое может происходить во время тестирования, будет подавлено между ЦПУ 0, ЦПУ 1 и логическими блоками набора схем. Это осуществляется с помощью обработки логической функцией И активных сигналов с определяющим сигналом. В одном варианте выполнения сигнал связывания выводов ЦПУ JTAG могут быть определены так, чтобы они обеспечивали работу брандмауэров DFX в логике 130 интерфейса. Например, сигнал связывания выводов JTAG выходит из ЦПУ 1 и поступает в логику 130 интерфейса и может использоваться для обеспечения брандмауэра для выходных сигналов ЦПУ 1 в логике 130 интерфейса.

Для определенных испытательных режимов, например, используя разъем для платы XDP, определенные режимы XDP можно использовать для мониторинга точки разрыва (ВРМ) или других тестовых выводов, используемых для отладки, или управляющих выводов из ЦПУ в ITP-XDP с виртуальным отключением. В частности, когда выводы ВРМ для ЦПУ 0 и ЦПУ 1 соединяют с помощью логической функции ИЛИ на материнской плате, и ЦПУ 1 виртуально отключают, может возникнуть проблема, связанная с электростатическим разрядом (ESD) диодов на отключенных выводах BPM_CPU 1, из-за чего напряжение падает до уровня земли, и логическая функция ИЛИ не будет работать. В зависимости от типа разъема XDP, могут быть предусмотрены разные режимы для решения этой задачи.

В первом режиме, то есть при малом XDP или в режиме совместного использования ВРМ, выполняют логическую функцию ИЛИ для выходов ВРМ CORE 1 с выходами ВРМ CORE 0. Входы ВРМ CORE 0 поступают в оба ядра. Входы и выходы ВРМ CORE 1 подвергают защите с помощью брандмауэра через функцию И в режиме виртуального отключения. Выходы ВРМ CORE 1 подвергают защите с помощью брандмауэра, используя логическую функцию И в режиме DFX. Малый XDP может представлять принятый по умолчанию режим, и только контактные площадки ВРМ CORE 0 используются для этого режима совместного использования ВРМ.

Во втором режиме, то есть при большом XDP или в режиме независимого ВРМ, входы/выходы ВРМ CORE 0 соединяются только с CORE 0. Входы/выходы ВРМ CORE 1 соединяются только с CORE 1. Режим большого XDP может быть разрешен с помощью сигнала связывания выводов объединенной группой действий во время тестирования (JTAG) в ядре. Такой сигнал связывания выводов предусмотрен для мультиплексирования между режимами XDP. Сигнал связывания выводов обеспечивает режим большого XDP, когда его заявляют. В обоих режимах режим объединения проводников через операцию ИЛИ не разрешен на материнской плате между ВРМ_С0 и ВРМ_С1 (и, по существу, может быть повторно заявлена плавкая перемычка, поддерживающая средний агент).

Рассмотрим теперь фиг.3, на которой показана блок-схема логики тестирования в соответствии с вариантом выполнения настоящего изобретения. Как показано на фиг.3, логика 300 тестирования может использоваться для управления операциями тестирования в режимах малых и больших XDP. Как можно видеть, логика 300 интерфейса включают в себя входную логику 320, которая в одном варианте выполнения может составлять часть логики 124 DFX логики 120 интерфейса. Входная логика 320 подключена для приема входящих выходных сигналов из соответствующих ядер 3100 и 3101. Как можно видеть, каждый из этих выходов подключен через соответствующую логику 3150-3151] брандмауэра к логическому элементу ИЛИ 325, выход которого поступает на вход мультиплексора 330. Как можно видеть, выход ядра 3100 также непосредственно подают на другой вход мультиплексора 330. В зависимости от режима тестирования (то есть малый XDP или большой XDP), выход из мультиплексора 330 выбирают из одного из этих двух входов и подают в интерфейс 3350, который, в свою очередь, может быть соединен с ядром 3100. В одном варианте выполнения сигнал ENB разрешения может быть по умолчанию принят равным нулю для режима малого XDP таким образом, что выход мультиплексора 330 может представлять собой версию типа логической операции ИЛИ, выводимую из логического элемента ИЛИ 325, в то время как в режиме большого XDP выход из ядра 3100 может быть подан в логику 3350 интерфейса. Как можно видеть, выход из ядра 3101 также поступает в логику 3351 интерфейса, соединенную с ядром 3101.

Кроме того, на фиг.3 показана входная логика 350, которая получает входные сигналы из входов в соответствующие ядра, то есть из логики 3350 и 3351 интерфейса, и предоставляет выбранный выходной сигнал в ядро 3101. Как можно видеть, ядро 3100 непосредственно принимает входные сигналы с выхода логики 3350 интерфейса. В выходной логике 350 мультиплексором 360 управляют на основе режима для вывода одного из двух выходных сигналов интерфейса, которые передают через логику 355 брандмауэра в ядро 3101. В одном варианте выполнения сигнал ENB разрешения может быть принят по умолчанию равным нулю для режима малого XDP, в котором выход мультиплексора 360 поступает из ядра 3350. В режиме большого XDP сигнал ENB может иметь высокий уровень, в результате чего выход мультиплексора 360 совпадает с выходом логики 3351 интерфейса.

В одном варианте выполнения сигналы DAT из ЦПУ в логику 130 интерфейса могут быть мультиплексированы (наложены) с сигналами iFSB для уменьшения маршрутизации. SoC будет направлять выходные сигналы DAT из каждого ЦПУ на контактные площадки входа/выхода SoC. Таким образом может быть устранена зависимость от жестко фиксированных операций ЦПУ. Таким образом, для уменьшения количества маршрутов в узком канале маршрутизации между двумя ядрами ЦПУ шины доступа DFX, используемые для режимов ATPG (сканирования) и DAT, могут быть мультиплексированы с шиной функциональных данных (то есть iFSB). В одном варианте выполнения мультиплексирование выполняют для младших битов данных для шины доступа DFX логики ЦПУ-набор схем, но для верхних битов данных шины доступа DFX для логики набора схем-ЦПУ. Основная топология для мультиплексирования шины доступа DFX показана на фиг.1. Предполагается, что оба режима ATPG и DAT являются взаимно исключающими, то есть тестовые режимы никогда не выполняют параллельно, но оба ядра ЦПУ могут входить в тестовый режим одновременно.

На фиг.4 показана блок-схема последовательности операций способа в соответствии с одним вариантом выполнения настоящего изобретения. Как показано на фиг.4, способ 400 можно использовать для операций управления в двухъядерном режиме или одноядерном режиме SoC, в соответствии с вариантом выполнения настоящего изобретения. Как показано на фиг.4, способ 400 может начинаться путем подачи питания к множеству ядер SoC во время инициализации (блок 410). Такая подача питания обеспечивает выполнение различного тестирования для обеспечения того, что оба процессора могут получать питание и что инициализация проходит правильным образом.

Управление затем переходит к ромбу 420, где, например, логика интерфейса SoC может принимать сигнал плавкой перемычки из первого ядра или сигнал связывания выводов из логики набора схем. Если это не происходит, это означает, что SoC имеет конфигурацию для двухъядерного режима. В соответствии с этим, управление переходит в блок 430, где могут поддерживаться подача питания и работа обоих ядер. Если вместо этого определяют, что, по меньшей мере, один из этих сигналов был принят в логике интерфейса, управление может быть переведено в блок 440, куда сигнал управления может быть передан для отключения второго ядра. В частности, индикатор виртуального отсоединения может быть установлен так, что он обозначает, что второе ядро должно не использоваться. Могут быть реализованы различные способы отключения этого ядра. Например, может быть предотвращена подача питания к ядру. Таким образом может быть реализована экономия энергии. Соответственно, в ромбе 450 может быть определено, требуется ли подавать питание во второе ядро. В противном случае, ядро отключают, и нормальная работа другого ядра может продолжиться. Если, однако, питание требуется подавать в оба ядра, управление переходит в блок 460, где сигналы тактовой частоты для второго ядра могут быть отключены, чтобы таким образом предотвратить его работу. Хотя это показано в данном конкретном варианте выполнения, представленном на фиг.4, объем настоящего изобретения не ограничивается в этом отношении.

SoC можно использовать во множестве разных систем. В качестве одного конкретного примера, SoC в соответствии с вариантом выполнения настоящего изобретения может быть встроена в компьютерную систему, такую как компьютер типа ноутбук. Рассмотрим теперь фиг.5, на которой показана блок-схема системы в соответствии с одним вариантом выполнения настоящего изобретения. Как показано на фиг.5, система 500 может представлять собой ноутбук или другой компьютер с малыми размерами.

Как можно видеть, SoC 510 может представлять собой SoC в соответствии с вариантом выполнения настоящего изобретения таким, как описано выше со ссылкой на фиг.1. Память 520, в одном варианте выполнения, может представлять собой динамическое оперативное запоминающее устройство (DRAM), которое может быть подключено к SoC 510, поскольку SoC может включать в себя интегрированный контроллер памяти. Кроме того, SoC 510 может быть соединена с дисплеем 530 таким, как жидкокристаллический дисплей (LCD) или другой такой дисплей, поскольку SoC может дополнительно включать в себя графические функции. Кроме того, SoC 510 может быть подключена к концентратору 550 контроллера ввода/вывода (ICH), который, в свою очередь, может быть подключен к различным компонентам системы, таким как запоминающее устройство 540 типа флэш, которое в одном варианте выполнения может действовать как запоминающее устройство большой емкости для системы, поскольку его малые размеры могут соответствовать компьютеру типа ноутбук или другому малому устройству. Кроме того, ICH 550 может быть соединен с беспроводным интерфейсом 560, который может обеспечить возможность обмена данными, например, через локальную вычислительную сеть (LAN, ЛВС), такую как соединение Bluetooth™, беспроводная ЛВС (WLAN), которая соответствует стандарту Института инженеров по электротехнике и радиоэлектронике (IEEE) 802.11 или другому такому стандарту. Кроме того, беспроводный интерфейс 560 может дополнительно обеспечить возможность передачи данных через глобальную вычислительную сеть, например через сотовую сеть связи. ICH 550 может дополнительно быть подключен к одному или больше устройствам 570 ввода/вывода, таким как клавиатура, мышь, устройство - указатель или другое устройство интерфейса пользователя. Хотя это показано в данном конкретном варианте выполнения на фиг.5, объем настоящего изобретения не ограничивается в этом отношении.

Варианты выполнения могут быть воплощены в виде кода и могут быть сохранены на носителе записи, в котором сохранены инструкции, которые можно использовать для программирования системы, для выполнения инструкции. Носитель записи может включать в себя, но не ограничивается этим, диск любого типа, включающий в себя гибкие диски, оптические диски, твердотельные устройства (SSD), запоминающие устройства на компакт-дисках, предназначенных только для считывания (CD-ROM), на перезаписываемых компакт-дисках (CD-RW), и магнитооптических дисках, полупроводниковых устройствах, таких как запоминающие устройства, предназначенные только для считывания (ROM), оперативных запоминающих устройствах (RAM), таких как динамические оперативные запоминающие устройства (DRAM), статические оперативные запоминающие устройства (SRAM), стираемые программируемые предназначенные только для считывания запоминающие устройства (EPROM), запоминающие устройства типа флэш, электрически стираемые программируемые предназначенные только для считывания запоминающие устройства (EEPROM), магнитные или оптические карты, или носители любых других типов, пригодные для сохранения электронных инструкций.

Хотя настоящее изобретение было описано в отношении ограниченного количества вариантов выполнения, для специалистов в данной области техники будут понятны различные модификации и их варианты. Предполагается, что приложенная формула изобретения охватывает все такие модификации и варианты, которые попадают в пределы истинной сущности и объема настоящего изобретения.

Реферат

Изобретение относится к многоядерным «системам на кристалле» (SoC). Техническим результатом является снижение потребления энергии SoC за счет отключения второго ядра во время нормальной работы для обеспечения одноядерной SoC. Устройство для управления потреблением энергией содержит "систему на кристалле", включающую в себя первое ядро и второе ядро; логику интерфейса, соединенную с первым ядром и вторым ядром, причем логика интерфейса включает в себя логику брандмауэра, логику шины и тестовую логику; логику набора схем, соединенную с логикой интерфейса и включающую в себя контроллер памяти, который обеспечивает возможность обмена данными с памятью, соединенной с SoC; и логику виртуального брандмауэра, соединенную между логикой набора схем и вторым ядром, в котором второе ядро может быть отключено во время нормальной работы для обеспечения одноядерной SoC. 3 н. и 17 з.п. ф-лы. 5 ил.

Формула

"систему на кристалле" (SoC), включающую в себя:

первое ядро и второе ядро;

логику интерфейса, соединенную с первым ядром и вторым ядром, причем логика интерфейса включает в себя логику брандмауэра, логику шины и тестовую логику;

логику набора схем, соединенную с логикой интерфейса и включающую в себя контроллер памяти, который обеспечивает возможность обмена данными с памятью, соединенной с SoC; и

логику виртуального брандмауэра, соединенную между логикой набора схем и вторым ядром, в котором второе ядро может быть отключено во время нормальной работы для обеспечения одноядерной SoC.

принимают сигнал плавкой перемычки в логике интерфейса "системы на кристалле" (SoC), включающий в себя, по меньшей мере, первое ядро и второе ядро, из первого ядра, и сигнал связывания выводов из логики набора схем SoC;

определяют, обеспечен ли, по меньшей мере, один из сигнала плавкой перемычки и сигнала связывания выводов; и

если это так, отключают второе ядро SoC для предотвращения работы второго ядра во время нормальной работы SoC.

"систему на кристалле" (SoC), включающую в себя первое ядро и второе ядро, логику интерфейса, соединенную с первым ядром и вторым ядром, причем логика интерфейса включает в себя логику брандмауэра, логику шины и тестовую логику, логика набора схем соединена с логикой интерфейса и включает в себя графический контроллер и контроллер памяти для обеспечения возможности обмена данными с памятью, подключенной к SoC, и виртуальной логикой брандмауэра, соединенной между логикой набора схем и вторым ядром, в котором второе ядро может быть отключено во время нормальной работы, для предоставления одноядерной SoC; и

динамическое оперативное запоминающее устройство (DRAM), соединенное с SoC.

Комментарии