Способ и устройство быстрого и эффективного переключения выводных штырьков при тестировании интегральной схемы - RU2163023C2

Код документа: RU2163023C2

Чертежи

Описание

Настоящее изобретение относится к области тестирования интегральных схем прикладной ориентации (ИСПО) согласно требованиям производителя ИСПО к тестированию выходного переключателя независимо от основного функционального назначения данной ИСПО.

Общеизвестным способом для тестирования сложных интегральных схем, реализованных, к примеру, в кристалле интегральной микросхемы (ИС), является стандарт IEEE 1149.1 международной Объединенной рабочей группы по тестированию (ОРГТ), включенный сюда посредством ссылки. Один из вариантов реализации этого стандарта включает в себя проектирование компонентов (например, интегральных схем) для последовательного периферийного сканирования путем обеспечения элементов сдвигового регистра, соединенных в цепочки с формированием тракта вокруг периферии компонента интегральной схемы.

Общая концепция последовательного тестирования с помощью стандарта ОРГТ состоит в сдвиге последовательных данных в несколько компонентов интегральной схемы и через них для стимуляции находящихся в них цепей или для выработки определенных выходных сигналов из схем. После этого данные, выработанные компонентами интегральной схемы или принятые на входах компонентов интегральной схемы, сдвигаются из этих компонентов интегральной схемы в главную тестовую схему по стандарту ОРГТ.

Если поток данных, возвращенный в главную тестовую схему, является не таким, как ожидалось, то этой тестовой схемой фиксируется нарушение работы схемы. Тщательный анализ отклонений в потоке данных под управлением программного обеспечения может выделить все ошибки работы схемы.

Большинство поставщиков интегральных схем прикладной ориентации (ИСПО) требуют, чтобы не только выходные штырьки, но и двунаправленные (ввод/вывод) штырьки тестируемой интегральной схемы (ИС) переключались в первых нескольких сотнях тестовых векторов в качестве части производственного тестирования ИС. Т.е. схема тестирования ИС должна обследовать переход от низкого напряжения к высокому напряжению, а также переход от высокого напряжения к низкому напряжению на каждом выходном штырьке. Это делается для того, чтобы гарантировать, что каждый из выходов работает правильно и способен переходить из состояния в состояние.

Однако из-за того, что множество тестируемых ИС может иметь сложные схемы конечных автоматов, обычно управляющие выходными переключаемыми штырьками, может потребоваться сложный анализ, чтобы гарантировать, что создаются правильные тестовые векторы, заставляющие каждый выходной штырек переключаться в течение первых нескольких сотен тестовых векторов. Переключение выходов с помощью стандарта ОРГТ неэффективно с точки зрения времени для ИС с большим количеством штырьков, так как каждый новый вектор должен последовательно загружаться через интерфейс ОРГТ. Желательно обеспечить стандартный способ переключения выходов ИСПО или подобной ИС, который не зависел бы от конкретных цепей внутри ИС. Таким образом, существует необходимость в простом и элегантном способе убедиться, что переключается каждый из выходных штырьков ИС.

Для достижения указанной цели предложен способ быстрого и эффективного переключения выводных штырьков при тестировании интегральной схемы, в которой каждый из упомянутых выводных штырьков соединен с соответствующим фиксатором периферийного сканирования, а каждый из упомянутых фиксаторов периферийного сканирования соединен с соответствующим элементом сдвигового регистра периферийного сканирования, и в которой упомянутые выводные штырьки дополнительно электрически связаны с тестирующей схемой, согласно которому последовательно проводят параллельную загрузку через упомянутые выводные штырьки первого тестового вектора из тестирующей схемы в упомянутые элементы сдвигового регистра периферийного сканирования в качестве первой тестовой комбинации, приводят упомянутую тестирующую схему в высокоимпедансное состояние, подают упомянутую первую тестовую комбинацию на упомянутые выводные штырьки из упомянутых фиксаторов периферийного сканирования в ответ на упомянутый первый тестовый вектор, проводят параллельную загрузку упомянутой первой тестовой комбинации в упомянутые элементы сдвигового регистра периферийного сканирования с упомянутых выводных штырьков, подают вторую тестовую комбинацию на упомянутые выводные штырьки из упомянутых фиксаторов периферийного сканирования, причем упомянутая вторая тестовая комбинация является дополнительной упомянутой первой тестовой комбинации, проводят параллельную загрузку упомянутой второй тестовой комбинации в упомянутые элементы сдвигового регистра периферийного сканирования с упомянутых выводных штырьков и подают третью тестовую комбинацию на упомянутые выводные штырьки из упомянутых фиксаторов периферийного сканирования, причем упомянутая третья комбинация является дополнительной к упомянутой второй тестовой комбинации. Предпочтительно упомянутая тестирующая схема содержит тестер интегральной схемы. Обычно упомянутую первую тестовую комбинацию сдвигают в упомянутых элементах сдвигового регистра периферийного сканирования после параллельной загрузки упомянутой первой тестовой комбинации в упомянутые элементы сдвигового регистра периферийного сканирования для выработки упомянутой второй тестовой комбинации, а упомянутую вторую тестовую комбинацию сдвигают в упомянутых элементах сдвигового регистра периферийного сканирования после параллельной загрузки упомянутой второй тестовой комбинации в упомянутые элементы сдвигового регистра периферийного сканирования для выработки упомянутой третьей тестовой комбинации. Предпочтительно тестирующая схема подает дополнительную тестовую комбинацию после загрузки упомянутого первого тестового вектора в упомянутые элементы сдвигового регистра периферийного сканирования до приведения их в упомянутое высокоимпедансное состояние.

Для реализации указанного способа предложено устройство для быстрого и эффективного переключения выводных штырьков при тестировании интегральной схемы, в которой каждый из упомянутых выводных штырьков электрически соединен с соответствующим фиксатором периферийного сканирования, а каждый из упомянутых фиксаторов периферийного сканирования электрически соединен с соответствующим элементом сдвигового регистра периферийного сканирования, и в которой упомянутые выводные штырьки дополнительно электрически соединены с тестирующей схемой, причем оно содержит сдвиговый регистр периферийного сканирования, определенный несколькими упомянутыми элементами сдвигового регистра периферийного сканирования, соединенными шлейфом с возможностью сдвига данным от одного элемента к следующему смежному элементу, при этом упомянутый сдвиговый регистр периферийного сканирования выполнен с возможностью приема параллельно загруженной тестовой комбинации с упомянутых выводных штырьков, причем упомянутая параллельно загруженная тестовая комбинация содержит чередующиеся логические нули и логические единицы, и мультиплексор, расположенный на конце упомянутого сдвигового регистра периферийного сканирования, причем упомянутый мультиплексор имеет первый вход, связанный с внутренней линией ввода тестовых данных, и второй вход, связанный с инвертированным выходом первого элемента сдвигового регистра периферийного сканирования, упомянутый выход упомянутого мультиплексора связан с входом в упомянутый первый элемент сдвигового регистра периферийного сканирования, при этом упомянутый мультиплексор выполнен с возможностью ввода с упомянутого инвертированного выхода упомянутого первого элемента сдвигового регистра периферийного сканирования на упомянутый вход упомянутого первого элемента сдвигового регистра периферийного сканирования в процессе нахождения упомянутого мультиплексора в режиме тестирования переключения, и при этом упомянутая параллельно загружаемая тестовая комбинация в упомянутых элементах упомянутого сдвигового регистра периферийного сканирования логически сдвигается на один элемент после загрузки упомянутой параллельно загружаемой тестовой комбинации из чередующихся логических единиц и логических нулей с формированием комбинации, дополнительной к упомянутой параллельно загружаемой тестовой комбинации в упомянутом регистре сдвига периферийного сканирования.

В дальнейшем изобретение будет рассмотрено с использованием графического материала.

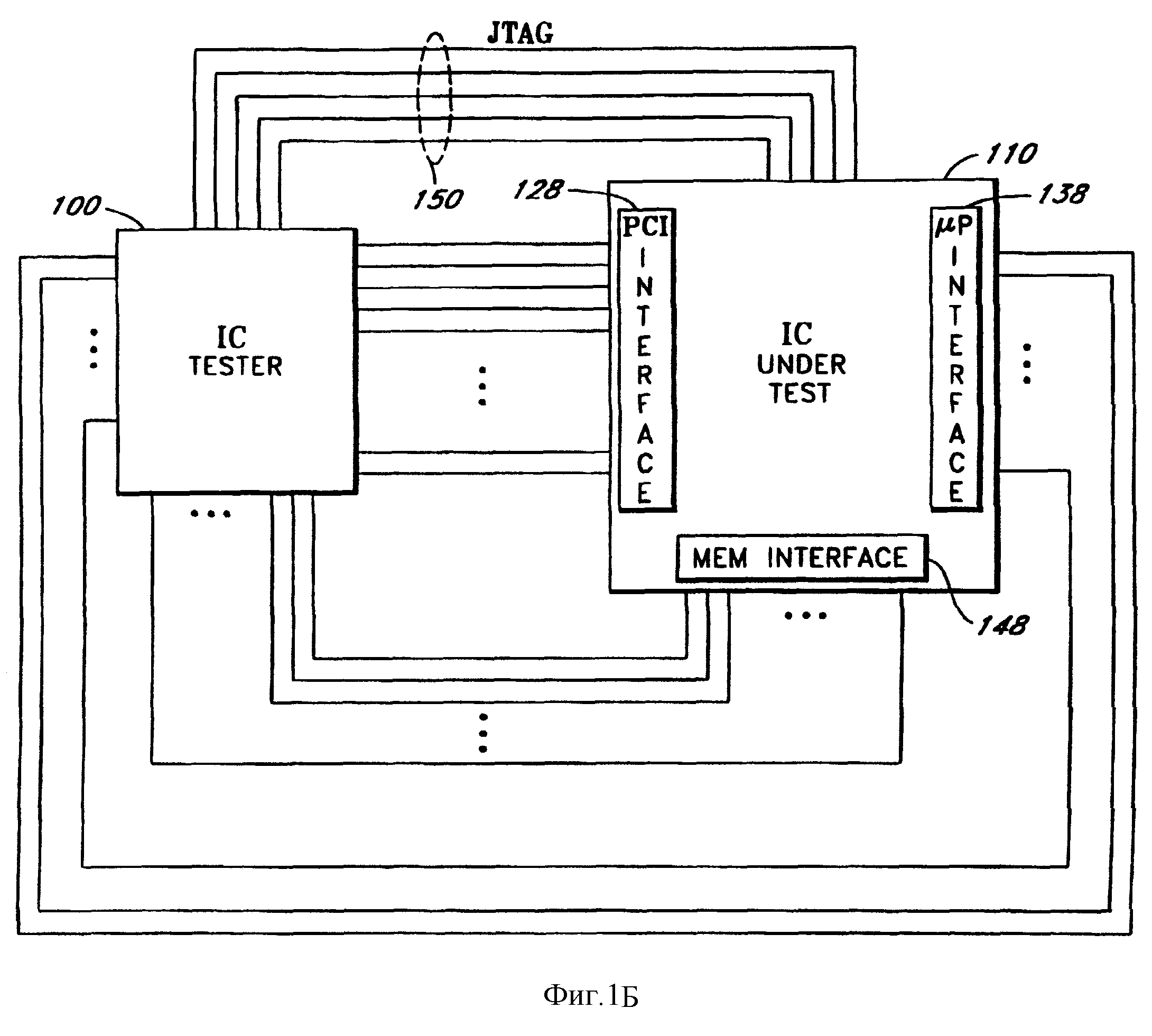

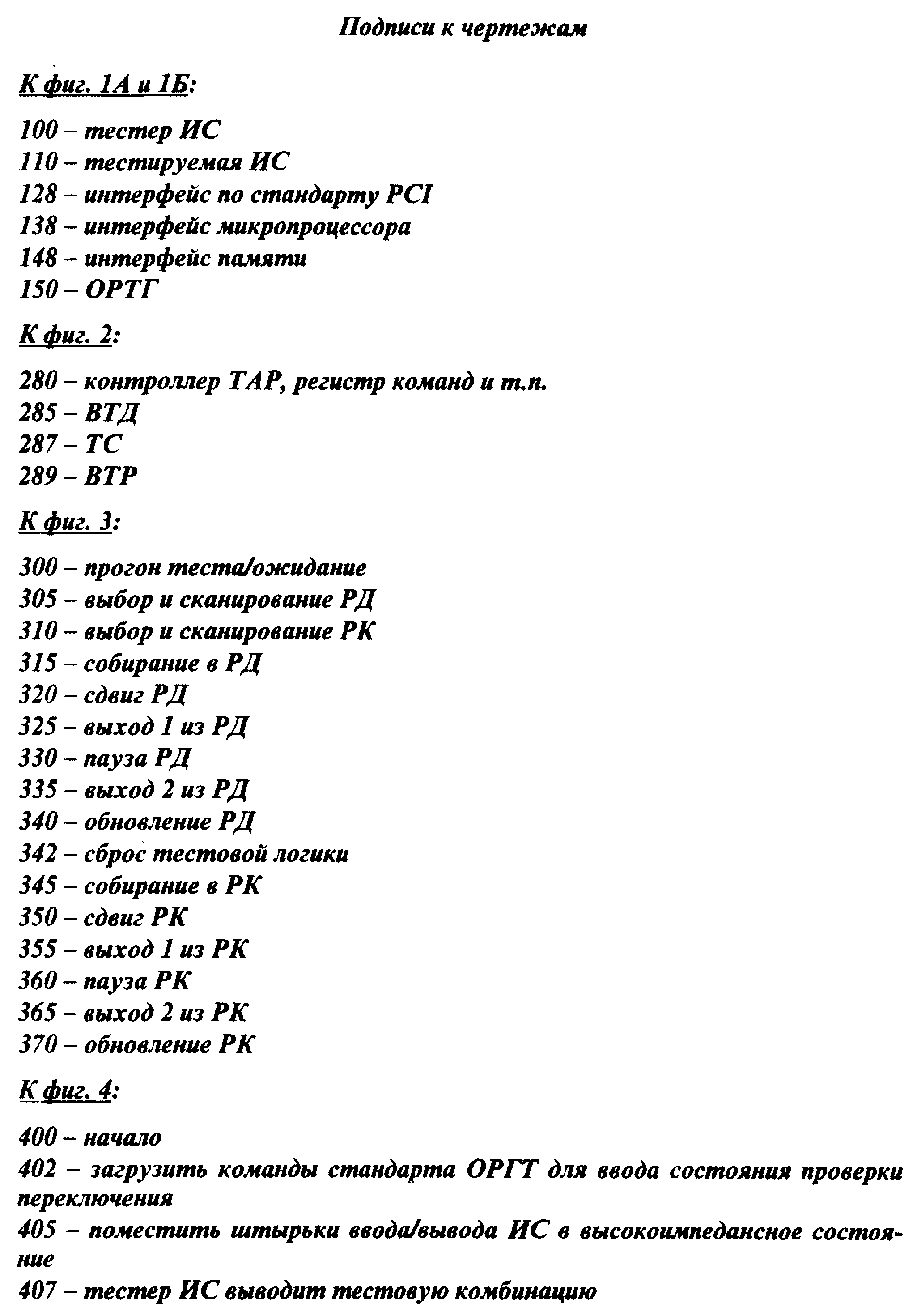

Фиг. 1А является перспективным видом кристалла ИС во время тестирования с помощью тестера ИС.

Фиг. 1Б является условной блок-схемой соединения тестера ИС и ИС по фиг. 1А.

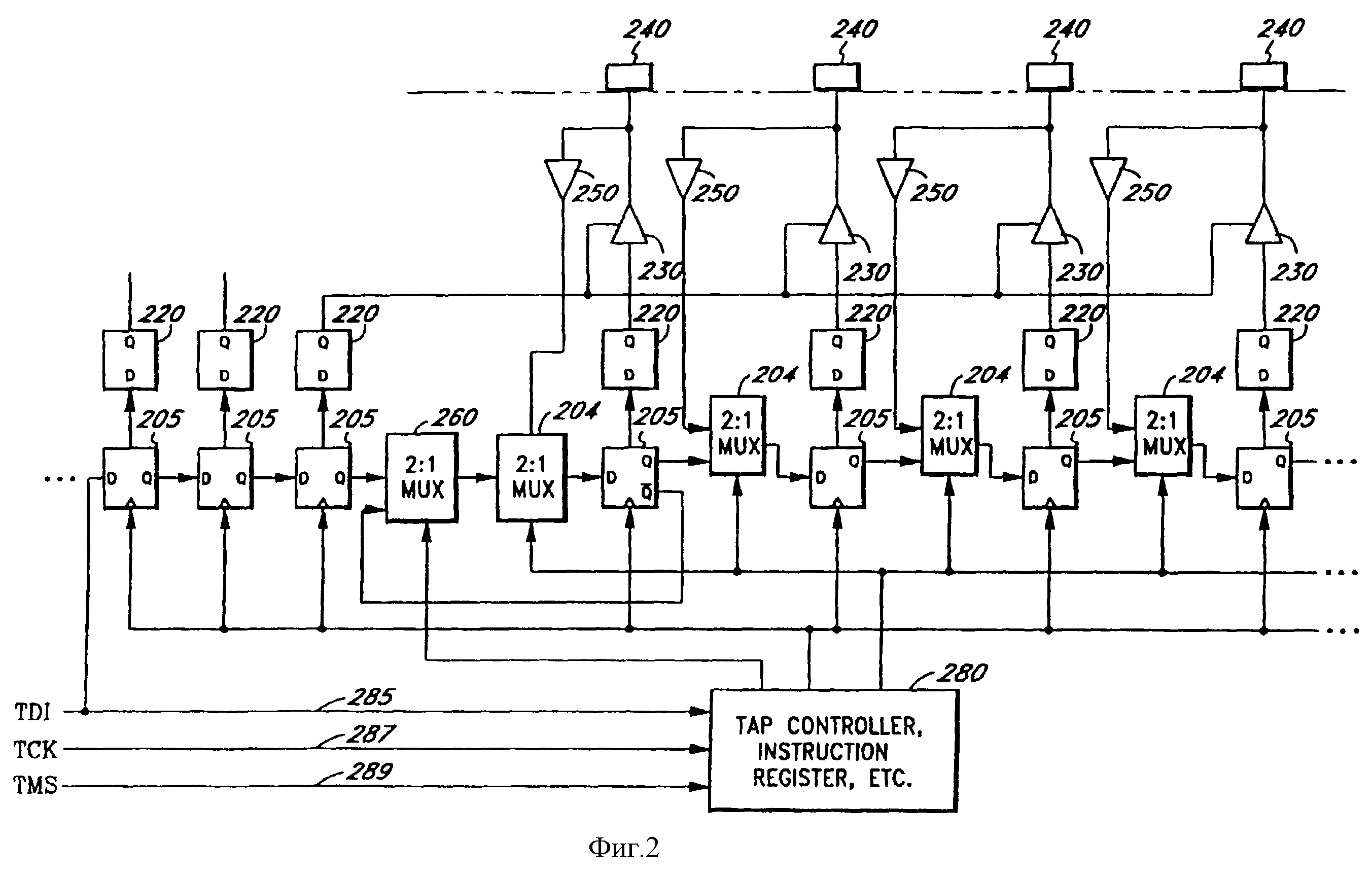

Фиг. 2 является условной блок-схемой, которая иллюстрирует часть внутренней тестирующей схемы периферийного сканирования по стандарту ОРГТ внутри кристалла ИС по фиг. 1.

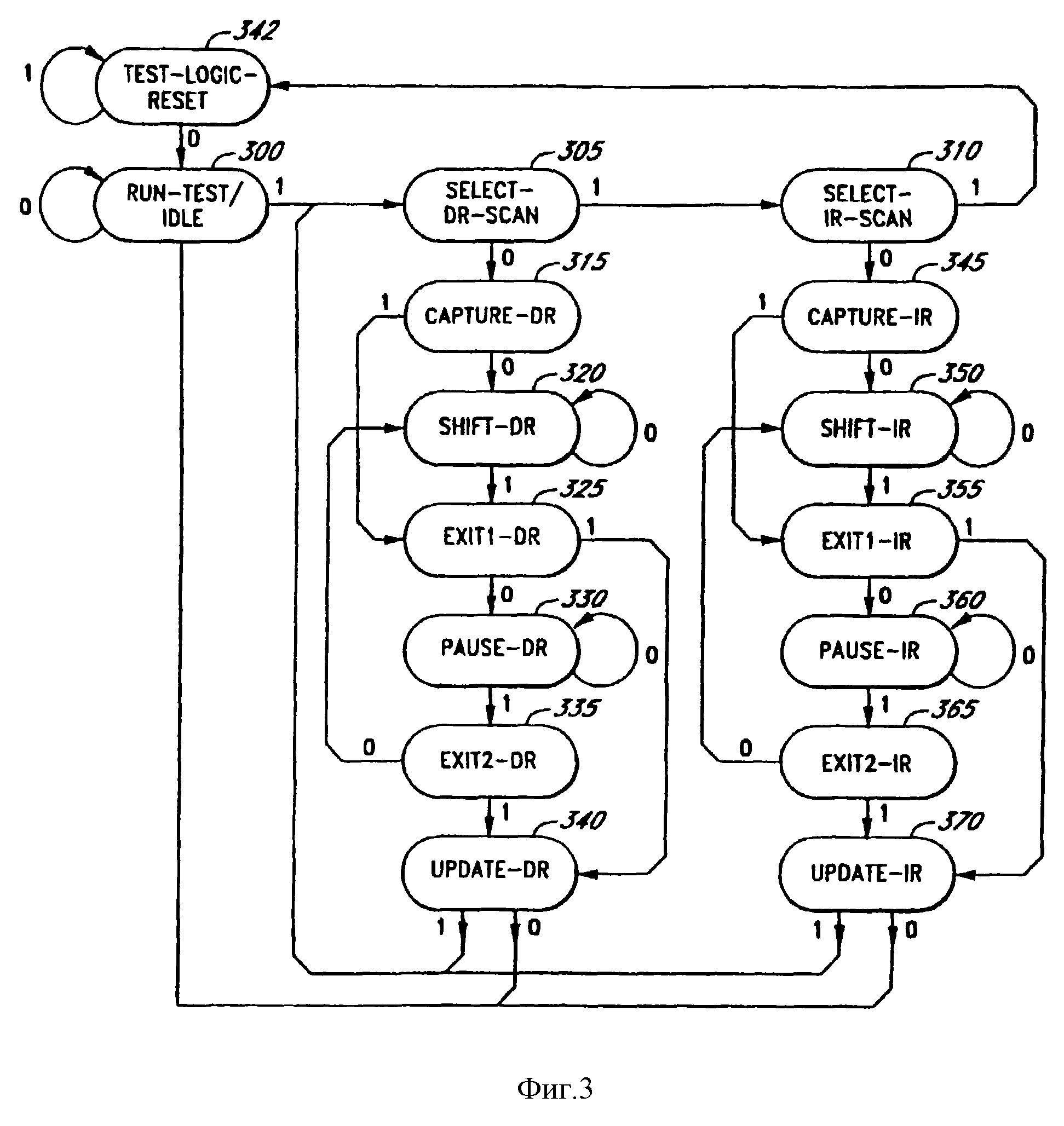

Фиг. 3 является диаграммой состояний, показывающей действие схемы контроллера ТАР по стандарту ОРГТ, используемой для управления тестирующей схемой периферийного сканирования по стандарту ОРГТ.

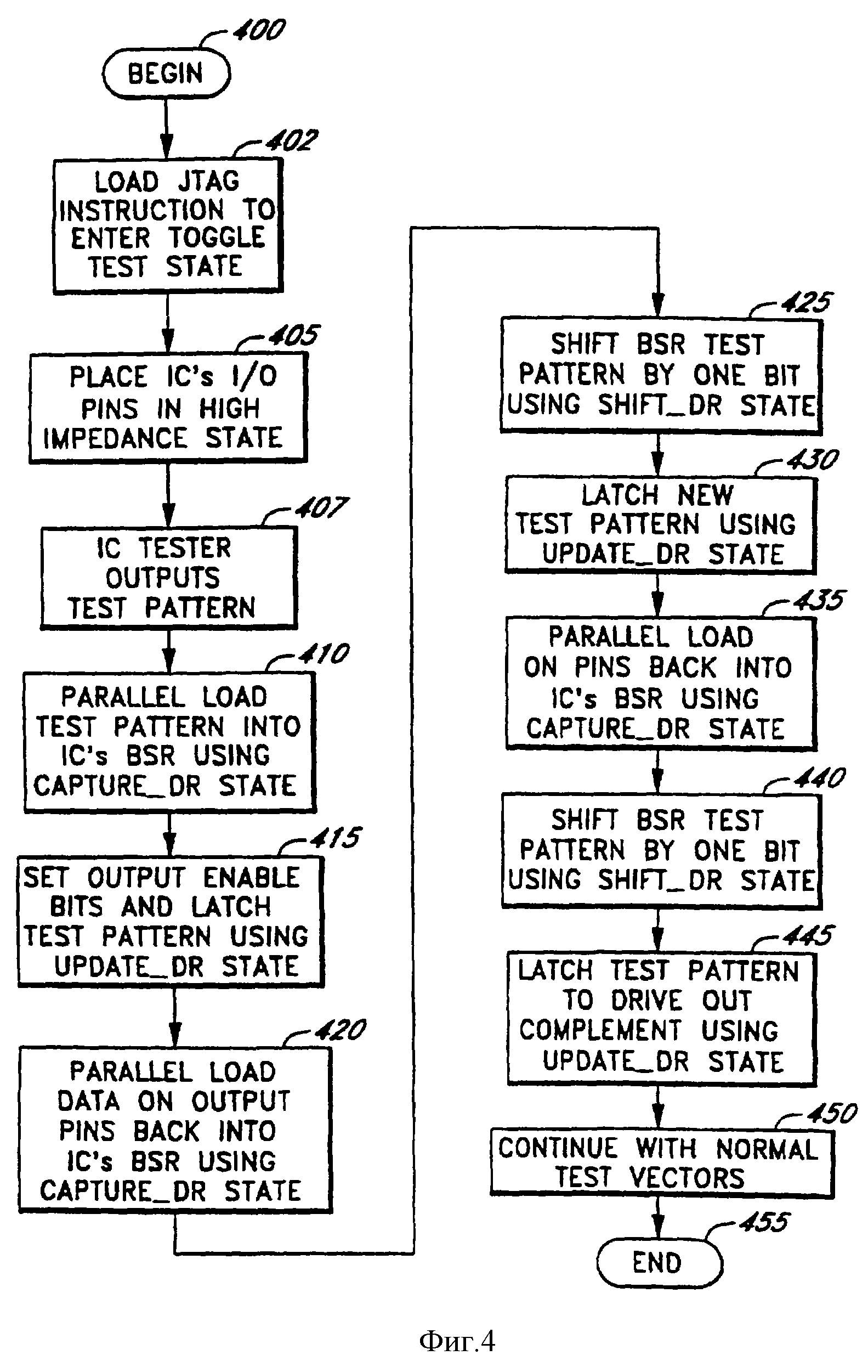

Фиг. 4 является блок-схемой алгоритма, которая иллюстрирует общий способ, используемый в соответствии с настоящим изобретением, чтобы убедиться, что все штырьки ввода/вывода кристалла ИС по фиг. 1 и 2 переключаются в нескольких тестовых векторах.

Фиг. 1А является видом в перспективе тестируемого кристалла 110 интегральной схемы (ИС) с помощью тестера 100 ИС. Кристалл 110 ИС вставляется в тестовое гнездо 120. Как показано на фиг. 1А, кристалл 110 ИС перед тестированием упаковывается. Однако специалисту будет ясно, что ИС 110 может тестироваться при изготовлении полупроводниковой пластины до упаковывания.

Фиг. 1Б является сильно упрощенной блок-схемой кристалла 110 ИС, подсоединенного к тестеру 100 ИС. Как представлено на фиг. 1Б, тестер 100 ИС подсоединяется, например, к интерфейсу 128 (периферийных устройств) стандарта PCI, интерфейсу 138 процессора и интерфейсу 148 памяти в ИС 110. Линии 150 стандарта ОРГТ (в том числе линии синхронизации, ввода последовательных данных, вывода последовательных данных и сигнала выбора режима) также соединяют ИС 110 с тестером 100 ИС. Интерфейс 128 стандарта PCI, интерфейс 138 процессора, и интерфейс 148 памяти содержат регистр периферийного сканирования (РПС) ОРГТ (не показан на фиг. 1Б) для тестирования штырьков ввода/вывода ИС 110.

При работе тестер 100 ИС, как хорошо известно из уровня техники, загружает заранее определенные тестовые векторы в тестируемую ИС и сравнивает выходы ИС с ожидаемыми результатами для того, чтобы определить, работает ли ИС 110 правильно. Если ИС 110 работает неправильно, то ИС 110 идентифицируется как дефектная.

Как кратко обсуждалось выше, большинство поставщиков ИСПО требуют, чтобы все выводные штырьки переключались в течение первых нескольких сотен тестовых векторов. Таким образом, в ходе тестирования кристалла 110 ИС будет необходимо убедиться, что все соединения ввода/вывода на кристалле 110 ИС переключаются. В частности, предпочтительно как можно быстрее определить, все ли соединения ввода/вывода могут переключаться. Причина этого состоит в том, что кристалл может немедленно маркироваться как дефектный, если одно из соединений ввода/вывода не переключается, так что дальнейшее тестирование ИС 110 не понадобится. Таким образом, сберегается ценное время тестирования, если тест переключения соединений ввода/вывода может выполняться в ходе первых нескольких периодов синхронизации тест.

Фиг. 2 является условной блок-схемой, которая иллюстрирует тестирующую цепь РПС по стандарту ОРГТ внутри кристалла 110 ИС по фиг. 1. Специалисту будет понятно, что часть тестирующей цепи 200 по стандарту ОРГТ, показанная на фиг. 2, упрощена для ясности и не содержит, например, цепи выходного мультиплексора логики ядра ИС и цепи управления выводом, которая обычно связана с цепью периферийного сканирования по стандарту ОРГТ и которая позволяет ИС функционировать нормально, когда она не находится под управлением по стандарту ОРГТ. Как показано на фиг. 2, множество элементов 205 сдвигового регистра данных соединяются последовательно через несколько мультиплексоров 204 так, что биты данных, хранящиеся в каждом из этих элементов 205 сдвигового регистра, могут сдвигаться в следующий элемент сдвигового регистра при подаче импульса синхронизации. Данные могут фиксироваться с выходов элементов 205 сдвигового регистра на выходы нескольких элементов 220 регистра фиксированных данных при подаче обновляющего запускающего импульса, так что все содержимое сдвигового регистра параллельно загружается в регистр 220 фиксированных данных. Когда сигнал отпирания выводов активен, выходные буферы 230 передают сигнал, присутствующий на выходе элементов 220 регистра фиксированных данных, на несколько ножек 240 ввода/вывода, так что данные в регистре 220 фиксированных данных могут использоваться для формирования выводов на штырьки 240 ввода/вывода.

Несколько входных буферов 250 позволяют сигналам, поданным на штырьки 240 ввода/вывода, загружаться в элементы 205 сдвигового регистра через мультиплексоры 204, когда предъявлен сигнал отпирания. Следует отметить, что входные буферы 250 также обеспечивают соединение между штырьками 240 ввода/вывода и другими цепями внутри кристалла ИС; однако для ясности иллюстрации настоящего изобретения эти соединения не показаны на фиг. 2.

В частном предпочтительном выполнении в тестовом регистре периферийного сканирования по стандарту ОРГТ предусматривается специальная цепь для упрощения способа по настоящему изобретению. В частности, каждый из элементов 205 сдвигового регистра, которые используются для хранения битов отпирания выводов, группируются друг с другом на одном конце сдвигового регистра периферийного сканирования, и мультиплексорная схема 260 размещается между элементами 205 сдвигового регистра, которые используются для хранения битов отпирания выводов, и элементами 205 сдвигового регистра, которые используются для хранения битов, подлежащих выведению через штырьки 240 ввода/вывода. Когда мультиплексор 260 находится в первом режиме выбора, мультиплексор 260 просто соединяет элементы 205 сдвигового регистра отпирания выводов с другими элементами 205 сдвигового регистра обычным образом, так что биты тестовых векторов могут сдвигаться через регистр сдвига периферийного сканирования без прерывания. Когда мультиплексор 260 находится во втором режиме выбора (т.е. в режиме тестового переключения), инвертированный вывод каждого элемента 205 сдвигового регистра соединяется с соответствующим ему вводом через мультиплексоры 260 и 204. Как более подробно будет обсуждаться ниже, эта конфигурация гарантирует, что, когда тестирующая по стандарту ОРГТ схема находится в режиме тестового переключения, бит данных, вдвинутый в первый элемент 205 сдвигового регистра после мультиплексора 260, является комплементарным (т. е. противоположным) биту, выдвинутому из первого элемента 205 сдвигового регистра.

Элементы 205 сдвигового регистра, элементы 220 фиксирующего регистра и мультиплексоры 260 и 204 управляются автоматом состояний контроллера ТАР по стандарту ОРГТ вместе с регистром команд и связанной с ним цепью, обозначенным в целом ссылочной позицией 280. Разумеется, специалисту ясно, что регистр команд содержит отдельные загружаемые сдвиговый регистр и фиксирующий регистры, которые используются для управления тестирующей цепью периферийного сканирования. Регистр команд включен в управляющую цепь 280 главным образом в качестве удобства для описания данного аспекта настоящего изобретения. Контроллер 280 принимает биты команд по сигналу ввода тестовых данных (ВТД) на линии 285, сигналу тестовой синхронизации (ТС) на линии ТС и сигналу выбора тестового режима (ВТР) на линии 289.

Фиг. 3 является диаграммой состояний, которая иллюстрирует действие контроллера 280 ТАР в ответ на управляющие сигналы ВТР и ТС, подаваемые по линиям 289, 287. Автомат состояний 280 контроллера ТАР начинается с состояния 342 сброса тестовой логики и остается в этом состоянии до тех пор, пока ВТР= 1. Если ВТР= 0, то автомат входит в состояние 300 ожидания. Состояние ожидания определяет состояние контроллера между операциями сканирования. Войдя в состояние 300 ожидания, контроллер 280 ТАР будет оставаться в этом состоянии ожидания до тех пор, пока сигнал ВТР остается низким. В состоянии 300 ожидания выбранная тестовая логика активируется только тогда, когда присутствуют определенные команды по стандарту ОРГТ, как хорошо известно из уровня техники. Для команд, загруженных в регистр 280 команд, это не влечет исполнения функций в состоянии 300 ожидания контроллера ТАР, а все регистры тестовых данных, выбранные текущей командой, должны сохранять свое предшествующее состояние.

Когда сигнал ВТР высокий и к сигналу ТС приложен нарастающий фронт, контроллер 280 ТАР переходит в состояние 305 выбора и сканирования регистров данных. Состояние 305 выбора и сканирования регистров данных является временным состоянием контроллера, в котором все регистры тестовых данных, выбранные текущей командой, сохраняют свое предшествующее состояние. Если сигнал ВТР сохраняется низким в то время, как к сигналу ТС приложен нарастающий фронт, контроллер 280 ТАР переходит к состоянию 315 собирания в регистрах данных, а если сигнал ВТР сохраняется высоким, а к сигналу ТС приложен нарастающий фронт, автомат 280 состояний контроллера ТАР переходит в состояние 310 выбора и сканирования регистров команд.

Если автомат 280 состояний контроллера ТАР переходит в состояние 315 собирания в регистрах данных, то в этом состоянии данные из буферов 250 ввода могут параллельно загружаться в сдвиговый регистр 205 данных на нарастающем фронте сигнала ТС. Далее биты, сохраненные в регистре 280 команд, остаются неизменными, когда автомат 280 состояний контроллера ТАР находится в состоянии 315 собирания в регистрах данных. Когда контроллер 280 ТАР находится в состоянии 315 собирания в регистрах данных в то время, как сигнал ВТР остается низким, а к сигналу ТС приложен нарастающий фронт, контроллер переходит в состояние 320 сдвига регистров данных. Однако, если сигнал ВТР остается высоким, а к сигналу ТС приложен нарастающий фронт импульса, то автомат 280 состояний контроллера ТАР переходит в состояние 325 выхода из регистра данных прямо из состояния 315 собирания в регистрах данных. В состоянии 320 сдвига регистров данных данные в линии 285 вдвигаются в сдвиговый регистр 205 данных. При приложении каждого нарастающего фронта сигнала ТС, если в это время сигнал ВТР остается низким, дополнительный бит данных вдвигается в сдвиговый регистр 205 данных по линии 205. Контроллер 280 ТАР продолжает находиться в состоянии 320 сдвига регистров данных, пока сигнал ВТР остается низким. Таким образом, в регистр 205 вдвигается столько битов данных, сколько необходимо для загрузки заранее определенных тестовых векторов в сдвиговые регистры 205, в то время, как сигнал ВТР остается низким в состоянии 320.

Когда контроллер 280 ТАР находится в состоянии 320 сдвига регистров данных, а к сигналу ТС приложен нарастающий фронт, тогда как сигнал ВТР остается высоким, автомат 280 состояний контроллера ТАР входит в состояние 325 выхода из регистра данных. Состояние 325 выхода из регистра данных является временным состоянием контроллера. Если сигнал ВТР остается высоким, приложенный к сигналу ТС нарастающий фронт заставляет контроллер 280 ТАР войти в состояние 340 обновления регистра данных, в то время, как если сигнал ВТР остается низким, а к сигналу ТС приложен нарастающий фронт, контроллер 280 ТАР входит в состояние 330 паузы в регистре данных. Состояние 330 паузы в регистре данных позволяет временно остановить сдвигание регистра 205 тестовых данных. Контроллер 280 ТАР остается в состоянии 330 паузы в регистре данных до тех пор, пока сигнал ВТР остается низким. Когда сигнал ВТР поддерживается высоким, а к сигналу ТС приложен нарастающей фронт, автомат 280 состояний контроллера ТАР входит в состояние 335 выхода 2 из регистра данных, которое также является временным состоянием контроллера. Если нарастающий фронт приложен к сигналу ТС в то время, когда сигнал ВТР поддерживается низким, автомат 280 состояний контроллера ТАР возвращается в состояние 320 сдвига в регистре данных. Однако, если сигнал ВТР поддерживается высоким в то время, как к сигналу ТС приложен нарастающий фронт, автомат 280 состояний контроллера ТАР переходит из состояния 335 выхода 2 из регистра данных в состояние 340 обновления регистра данных. Как показано на фиг. 2, сдвиговый регистр 205 данных соединен с фиксированным параллельным выводом 220 для предотвращения изменений данных в регистре 205 данных, в то время, как данные сдвигаются в связанном тракте 205 сдвигового регистра в ответ на определенные команды в регистре 280 команд. Таким образом, в состоянии 340 обновления регистра данных данные фиксируются из сдвигового регистра 205 на параллельном выводе сдвигового регистра 220 на падающем фронте сигнала ТС. Таким образом, эти данные сохраняются в фиксированном регистре 220 данных так, что данные в регистре 220 не изменяются по сравнению с состоянием обновления регистра данных, если только в процессе исполнения не требуется выполнить автотестирование (например, во время состояния ожидания в ответ на специфически разработанную команду по стандарту ОРГТ). Для каждого из состояний 305-335 команды, хранимые в сдвиговом регистре 280 команд и фиксированном регистре 280 данных команд, не изменяются, когда контроллер 280 ТАР данных находится в состоянии 340 обновления регистра данных. Когда контроллер ТАР находится в состоянии обновления регистра данных, а к сигналу ТС приложен нарастающий фронт, контроллер 280 ТАР входит в состояние 305 выбора и сканирования регистра данных, когда сигнал ВТР сохраняется высоким, или в состояние 300 ожидания, когда сигнал ВТР сохраняется низким.

Если сигнал ВТР сохраняется высоким, а к сигналу ТС приложен нарастающий фронт в то время, как автомат 280 состояний контроллера ТАР находится в состоянии 305 выбора регистра данных, автомат 280 состояний контроллера ТАР переходит в состояние 310 выбора и сканирования регистра команд.

Если автомат 280 состояний контроллера ТАР переходит в состояние 345 собирания в регистр команд, то в этом состоянии команды могут параллельно загружаться в регистр 280 команд из сдвигового регистра 280 команд на нарастающем фронте сигнала ТС. Далее биты, хранимые в регистрах 205, 220 данных, остаются неизменными в то время, когда автомат 280 состояний контроллера ТАР находится в состоянии 345 собирания в регистр команд. Когда контроллер 280 ТАР находится в состоянии 345 собирания в регистр команд, когда сигнал ВТР сохраняется низким, а к сигналу ТС приложен нарастающий фронт, контроллер входит в состояние 350 сдвига регистра команд. Однако, если сигнал ВТР сохраняется высоким в то время, как к сигналу ТС приложен нарастающий фронт, автомат 280 состояний контроллера ТАР переходит в состояние 355 выхода из регистра команд прямо из состояния 345 собирания в регистр команд. В состоянии 350 сдвига регистра команд команды по линии 285 вдвигаются в сдвиговый регистр 280 команд. После приложения каждого нарастающего фронта сигнала ТС в то время, как сигнал ВТР сохраняется низким, дополнительный бит команды вдвигается в сдвиговый регистр 280 команд по линии 285. Контроллер 280 ТАР продолжает находиться в состоянии 350 сдвига регистра команд до тех пор, пока сигнал ВТР сохраняется низким. Таким образом, в то время, как сигнал ВТР сохраняется низким в состоянии 350, в сдвиговые регистры 280 команд вдвигается столько битов команд, сколько необходимо для загрузки заранее определенных векторов команд.

Когда контроллер 280 ТАР находится в состоянии 350 сдвига регистра команд, и к сигналу ТС приложен нарастающий фронт, тогда как сигнал ВТР сохраняется высоким, автомат 280 состояний контроллера ТАР входит в состояние 355 выхода из регистра команд. Состояние 355 выхода из регистра команд является временным состоянием контроллера. Если сигнал ВТР сохраняется высоким, нарастающий фронт, приложенный к сигналу ТС, заставляет контроллер 280 ТАР войти в состояние 370 обновления регистра команд, в то время, как если сигнал ВТР сохраняется низким, когда к сигналу ТС приложен нарастающий фронт, контроллер 280 ТАР входит в состояние 360 паузы регистра команд.

Состояние 360 паузы регистра команд позволяет временно остановить сдвигание регистра 280 тестовых команд. Контроллер 280 ТАР остается в состоянии 360 паузы регистра команд до тех пор, пока сигнал ВТР сохраняется низким. Когда сигнал ВТР поддерживается высоким, а к сигналу ТС приложен нарастающий фронт, автомат 280 состояний контроллера ТАР входит в состояние 365 выхода 2 из регистра команд, которое также является временным состоянием контроллера. Если нарастающий фронт приложен к сигналу ТС в то время, как сигнал ВТР сохраняется низким, то автомат 280 состояний контроллера ТАР возвращается к состоянию 350 сдвига регистра команд. Однако, если сигнал ВТР сохраняется высоким, когда к сигналу ТС приложен нарастающий фронт, автомат 280 состояний контроллера ТАР переходит от состояния 365 выхода 2 из регистра команд в состояние 370 обновления регистра команд. Сдвиговый регистр 280 команд содержит фиксированный параллельный вывод для предотвращения изменений команды в регистре 280 команд во время сдвигания битов команд в сдвиговый регистр команд. Фиксатор 280 регистра команд обновляется только в состоянии 370 обновления РК (регистра команд). Когда контроллер 280 ТАР находится в состоянии 370 обновления регистра команд, и к сигналу ТС приложен нарастающий фронт, контроллер 280 ТАР входит в состояние 305 выбора и сканирования регистра данных, когда сигнал ВТР сохраняется высоким, или в состояние 300 ожидания, когда сигнал ВТР сохраняется низким.

Если в состоянии 310 выбора регистра команд сигнал ВТР сохраняется высоким в то время, как к сигналу ТС приложен нарастающий фронт, контроллер 280 ТАР входит в состояние 342 сброса тестовой логики. Когда автомат 280 состояний контроллера ТАР входит в состояние 342 сброса тестовой логики, тестовая логика отключается, так что нормальная работа находящейся в микросхеме системной логики может свободно продолжаться.

Фиг. 4 является блок-схемой, которая иллюстрирует способ по настоящему изобретению для быстрого и эффективного переключения выходных штырьков кристалла ИС. Когда способ инициализируется, как представлено в начальном блоке 400, регистр команд (содержащийся в контроллере 280) загружается соответствующими битами для установки тестовой схемы периферийного сканирования по стандарту ОРГТ в режим тестирования переключения, как представлено в функциональном блоке 402. Это означает, что биты, загруженные в регистр команд, таковы, что быт выбора мультиплексора 260 установлен, чтобы вызывать выработку на его выходе чередующейся битовой комбинации. Биты отпирания вывода последовательно устанавливаются так, чтобы привести штырьки 240 ввода/вывода в высокоимпедансное состояние, как представлено в функциональном блоке 405. Это достигается, например, сдвигом последовательности нулей (т.е. битов низкого уровня напряжения) в элементы 250 сдвигового регистра данных под управлением контроллера 280 до тех пор, пока все биты отпирания вывода не будут очищены. После того, как биты отпирания вывода в элементах 205 сдвигового регистра очищены, достигается состояние обновления регистра данных (см. фиг. 3), чтобы биты отпирания вывода, хранимые в элементах сдвигового регистра, были зафиксированы в соответствующие фиксирующие элементы 220 регистра данных. Затем буферы 230 переводятся в "третье состояние" (т.е. переводятся в высокоимпедансное состояние). Как обсуждалось выше, биты отпирания вывода группируются вместе на одном конце сдвигового регистра данных так, что все биты отпирания вывода могут быть установлены в течение нескольких периодов синхронизации. Альтернативно может быть предусмотрен специальный штырек (не показан), который либо параллельно загружает все элементы регистра отпирания вывода, либо переопределяет элементы регистра отпирания вывода, независимо от их позиции в регистре, на желательное битовое значение. Таким образом, в данном альтернативном выполнении может использоваться одна операция, позволяющая отпирать все выводы.

Далее тестер 100 ИС выдает тестовую комбинацию на штырьки 240 ввода/вывода, как представлено в функциональном блоке 407. Предпочтительно тестовая комбинация содержит чередующиеся высокие и низкие биты (т.е. двоичные единицы и нули), чтобы каждый элемент в сдвиговом регистре 205 данных был смежным со своим двоичным дополнением. Контроллер 280 затем входит в состояние собирания в регистр данных, что заставляет тестовую комбинацию параллельно загружаться (т.е., сканироваться) в элементы 205 сдвигового регистра данных, как представлено в функциональном блоке 410.

После того, как тестер 100 ИС переведен в высокоимпедансный режим, биты отпирания вывода последовательно устанавливаются для отпирания вывода по штырькам 240 ввода/вывода, как представлено в функциональном блоке 415. Это достигается, к примеру, путем вдвигания последовательности единиц (т.е. битов высокого уровня напряжения) в элементы 205 сдвигового регистра данных под управлением контроллера 280 до тех пор, пока не будут установлены все биты отпирания вывода. (Как отмечено выше, для этой функции может использоваться альтернативная логика. ) После того, как биты отпирания выводов в элементах 205 сдвигового регистра установлены, вводится состояние обновления регистра данных (см. фиг. 3), чтобы биты отпирания выводов, хранимые в элементах 205 сдвигового регистра, были зафиксированы в соответствующие фиксирующие элементы 220 регистра данных. В результате буферы 230 отпираются для вывода данных, присутствующих на выходе фиксирующих элементов 220 регистра данных.

Тестовая комбинация из чередующихся высоко- и низкоуровневых битов фиксируется в фиксирующий регистр данных одновременно с тем, как биты отпирания вывода фиксируются в фиксирующий регистр данных (т.е. под управлением той же обновляющей команды). Таким образом, тестовая комбинация подается на штырьки 240 ввода/вывода, поскольку выходы фиксирующих элементов 220 регистра данных соединены с ножками 240 ввода/вывода через открытые буферы 230.

Когда тестовая комбинация из чередующихся высоко- и низкоуровневых битов выдана на штырьки 240 ввода/вывода кристалла 110 ИС, эта комбинация данных дискретизируется для параллельной загрузки в элементы 205 сдвигового регистра данных, как представлено в функциональном блоке 420. Дискретизация битов, присутствующих на штырьках 240 ввода/вывода, осуществляется путем перевода контроллера 280 в состояние 315 собирания в регистр данных. Таким образом, сдвиговый регистр данных хранит точно такую же тестовую комбинацию, которая изначально хранилась до подачи тестовой комбинации на штырьки 240 ввода/вывода.

Состояние 320 сдвига регистра данных (РД) затем заставляет тестовую комбинацию, хранимую в элементах 205 сдвигового регистра данных, сдвигаться на один бит, как представлено в функциональном блоке 425. Таким образом, каждый из элементов 205 сдвигового регистра данных будет хранить дополнение бита, сохраненного в предыдущем периоде синхронизации (т.е. до того, как произошел сдвиг). Вследствие того, что мультиплексор 260 установлен на режим тестирования переключения, так что выход первого элемента сдвигового регистра инвертируется и загружается обратно в первый элемент сдвигового регистра каждый раз, когда производится сдвиг, сохраняется комбинация из чередующихся высоко- и низкоуровневых битов.

Когда тестовая комбинация сдвинута на один бит, эта сдвинутая тестовая комбинация фиксируется в фиксирующие элементы 220 регистра данных через состояние 340 обновления, как представлено в функциональном блоке 430. Таким образом, дополнение исходной тестовой комбинации, которая была выведена на выводные штырьки 240, выводится теперь так, что выводным штырькам 240 приходится переключаться либо с низкого состояния в высокое состояние, либо обратно из высокого состояния в низкое состояние. Таким образом, удовлетворяется первая половина требований к переключению.

Для удовлетворения второй половины требований к переключению (т.е. переключиться в обратном направлении так, чтобы если первое переключение происходило из низкого состояния в высокое состояние, то второе переключение было бы из высокого состояния в низкое состояние, и наоборот), данные на выводных штырьках 240 загружаются обратно в сдвиговый регистр 205 данных посредством состояния 315 собирания в РД, как представлено в функциональном блоке 435. Когда данная тестовая комбинация загружена в элементы 205 сдвигового регистра данных, эта тестовая комбинация сдвигается на один бит, как представлено в функциональном блоке 440. Затем эта сдвинутая тестовая комбинация фиксируется в фиксирующих элементах 220 регистра данных, как представлено в функциональном блоке 445, чтобы дополнение данных, находящихся в текущий момент на штырьках 240 ввода/вывода, подавалось на штырьки 240.

Таким образом, удовлетворяется вторая половина требований к переключению, так что нет дальнейшей необходимости убеждаться в том, что оставшиеся тестовые векторы специально подобраны для гарантии переключения для всех штырьков 240 ввода/вывода. Таким образом, как представлено в функциональном блоке 450, цепь по стандарту ОРГТ отключается переводом автомата 280 состояний контроллера ТАР в состояние 342 обнуления тестовой логики. Тестирование ИС в обычном режиме может теперь выполняться с помощью тестера 100 ИС. Этот способ затем прекращается, как видно из конечного блока 455.

Несмотря на то, что настоящее изобретение было подробно описано выше, следует понимать, что предшествующее описание является иллюстративным, а не ограничивающим. Специалистам будет ясно, что можно сделать много очевидных модификаций изобретения, не отходя от его духа или основных характеристик. Например, биты отпирания вывода могут управляться множеством разных способов, таких как параллельная загрузка или последовательный сдвиг желательных битовых значений. Далее не требуется воплощать схему 260 мультиплексора, чтобы гарантировать, что сохраняется чередующаяся тестовая последовательность. На практике могут использоваться другие специализированные цепи для выполнения тех же функций, как это диктуется конкретным приложением. Соответственно объем изобретения должен интерпретироваться в свете прилагаемой следующей формулы изобретения.

Реферат

Способ переключения выводных штырьков кристалла интегральной схемы ИС для удовлетворения тестовых требований производителя к переключению выводов заключается в том, что параллельно загружают данные из тестера ИС в регистр сдвига периферийного сканирования ИС так, что параллельно загруженные данные являются чередующимися высоко- и низкоуровневыми битами данных. Тестовая комбинация чередующихся битов данных затем фиксируется в регистре фиксации данных и подается на выводные штырьки кристалла ИС. Затем тестовая комбинация сдвигается на один бит в сдвиговом регистре ИС и параллельно загружается в фиксирующий регистр в следующем периоде синхронизации. Таким образом, дополнение тестовой комбинации, подаваемое на выводные штырьки внутренней тестирующей схемой, выдается из кристалла ИС. Затем этот процесс повторяется еще раз для обеспечения чередующегося перехода для каждого из выводных штырьков на кристалле ИС. Техническим результатом является упрощение и повышение надежности тестирования интегральной схемы. 2 с. и 4 з.п. ф-лы, 4 ил.

Комментарии