Демодулятор интегральной схемы cdma с встроенной генерацией тестовых комбинаций - RU2323447C1

Код документа: RU2323447C1

Чертежи

Описание

Область техники, к которой относится изобретение

Настоящее изобретение в целом относится к генерации комбинаций тестовых данных. В частности, содержание изобретения относится к способам и устройству для генерации комбинаций тестовых данных для интегральных схем.

Уровень техники

Современные типовые электронные схемы содержат тысячи или миллионы отдельных компонент, интегрированных в единую микросхему, которые слишком сложны для ручного тестирования. Для тестирования этих сложных электронных схем разработчики схем вынуждены полагаться на автоматическое тестирование.

Тестирование можно обеспечить путем генерации комбинаций тестовых данных, внешних по отношению к тестируемой микросхеме, и подачи сигналов тестовых комбинаций через входные выводы микросхемы. При использовании внешнего генератора для тестирования может потребоваться выделение для этого нескольких выводов микросхемы. Это уменьшает конечное количество выводов, доступных для действующих функций микросхемы. Вдобавок внешняя генерация тестовых комбинаций может оказаться весьма затратной, длительной и логически более сложной.

Микросхемы, разработанные для поддержки связи с множественным доступом с кодовым разделением каналов (CDMA), отличаются особой сложностью. Как правило, микросхемы CDMA включают в себя дополнительные функции обработки сигналов, которые могут потребоваться в других приложениях. Для тестирования этих микросхем CDMA с помощью реалистичных входных сигналов генератору комбинаций тестовых данных обычно необходимо генерировать комбинации данных со сравнительно сложной обработкой сигналов. Известное техническое решение (с целью исключения использования внешнего тестового генератора) включает в себя схему внутреннего генератора тестовых данных в самой микросхеме CDMA. Однако это усложняет и так уже сложную микросхему CDMA из-за увеличения объема ее аппаратных средств микросхемы CDMA. Другое известное техническое решение, уменьшающее требования к аппаратным средствам микросхемы CDMA, состоит во введении упрощенных внутренних аппаратных средств, генерирующих случайные комбинации тестовых данных. Однако это решение не удовлетворяет требованию тестирования микросхемы CDMA с помощью реалистичных входных сигналов.

Соответственно желательно генерировать реалистичные комбинации тестовых данных без внешнего генератора комбинаций тестовых данных и без значительного увеличения объема аппаратных средств микросхемы CDMA и ее сложности.

Сущность изобретения

Согласно одному аспекту настоящего изобретения интегральная схема для множественного доступа с кодовым разделением каналов включает в себя демодулятор, выполненный с возможностью корреляции входных данных с множеством кодов, и генератор комбинаций тестовых данных, выполненный с возможностью расширения входных тестовых данных одним из множества кодов для формирования расширенных тестовых данных и предоставления расширенных тестовых данных демодулятору.

Согласно другому аспекту настоящего изобретения интегральная схема для множественного доступа с кодовым разделением каналов включает в себя средство для корреляции входных данных с множеством кодов и средство для расширения входных тестовых данных одним из множества кодов для формирования расширенных тестовых данных и предоставления расширенных тестовых данных в качестве входных данных.

Согласно еще одному аспекту изобретения способ тестирования интегральной схемы для множественного доступа с кодовым разделением каналов включает в себя: корреляцию входных данных с множеством кодов в демодуляторе; расширение входных тестовых данных одним из множества кодов для формирования расширенных тестовых данных; и предоставление расширенных тестовых данных демодулятору.

Очевидно, что специалисты в данной области техники без труда смогут предложить другие варианты настоящего изобретения исходя из последующего подробного описания, в котором в качестве иллюстраций показаны и описаны различные варианты изобретения. При реализации изобретения возможны и другие варианты его осуществления, причем некоторые детали могут быть модифицированы в иных различных отношениях, не выходя за рамки существа и объема настоящего изобретения. Соответственно чертежи и подробное описание следует рассматривать исключительно как иллюстрации, а не как ограничения.

Краткое описание чертежей

Аспекты настоящего изобретения проиллюстрированы на примере, не являющемся ограничением, с использованием сопроводительных чертежей, на которых:

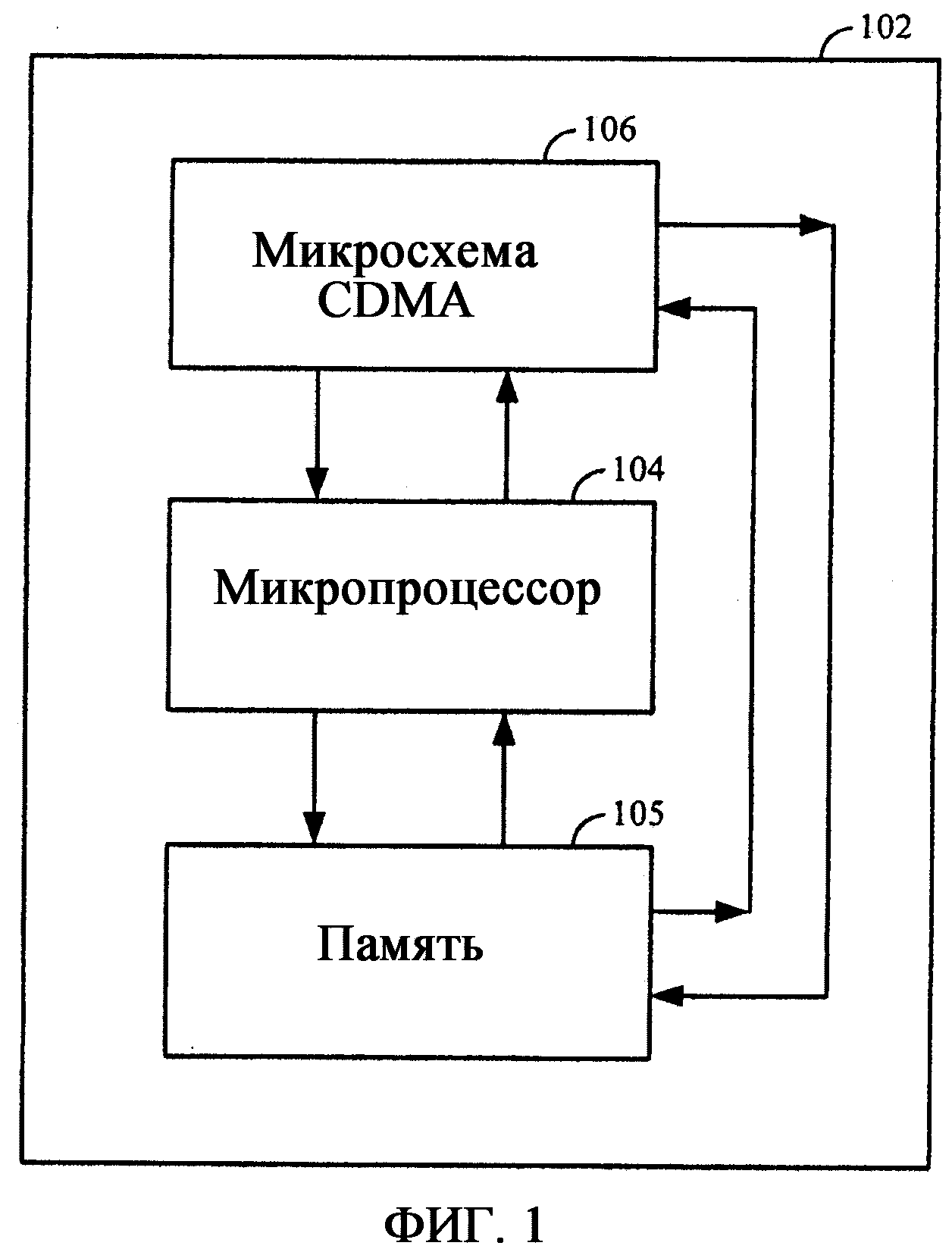

Фиг.1 - концептуальная блок-схема, иллюстрирующая пример устройства беспроводной связи;

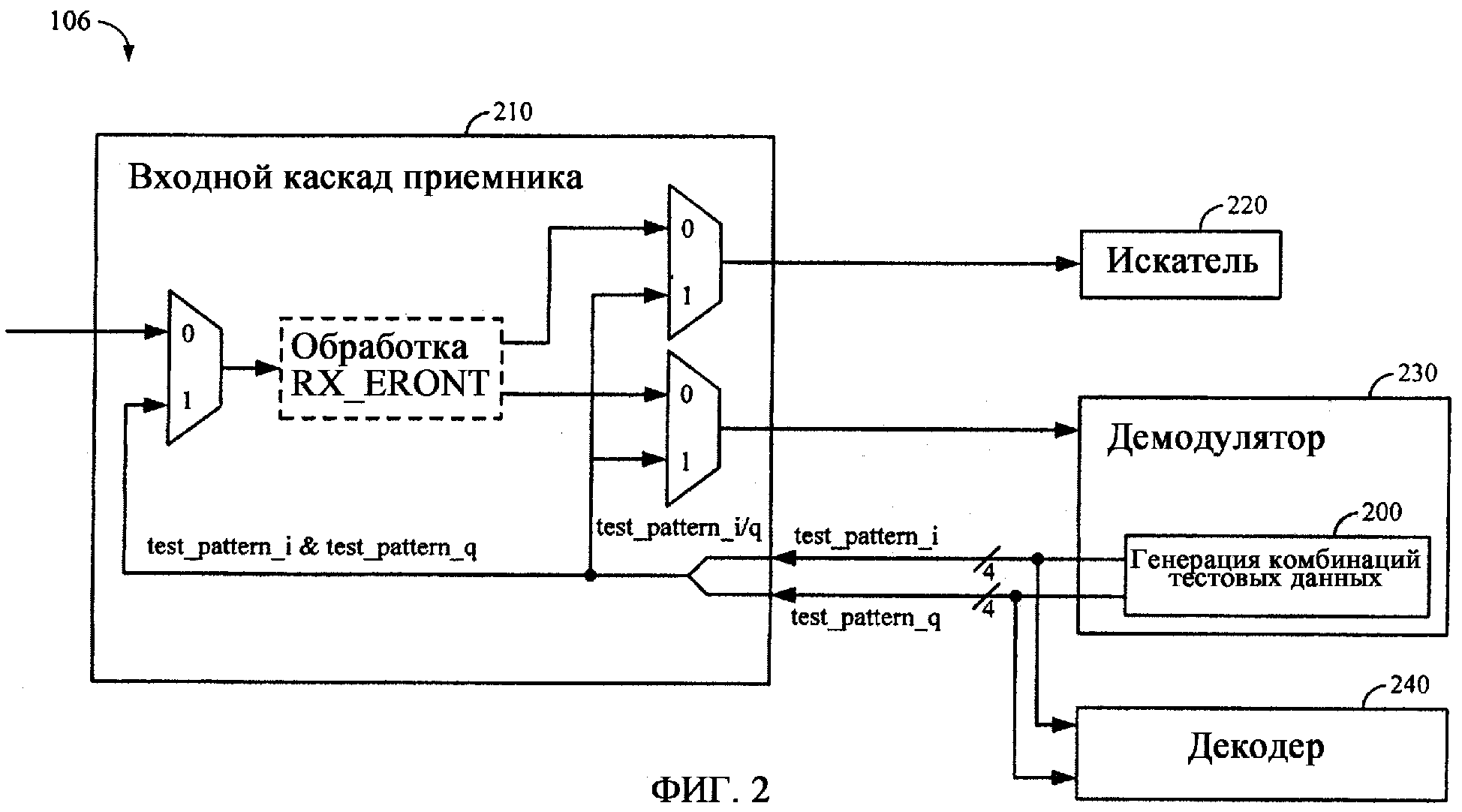

Фиг.2 - концептуальная блок-схема, иллюстрирующая пример микросхемы CDMA для использования в устройстве беспроводной связи; и

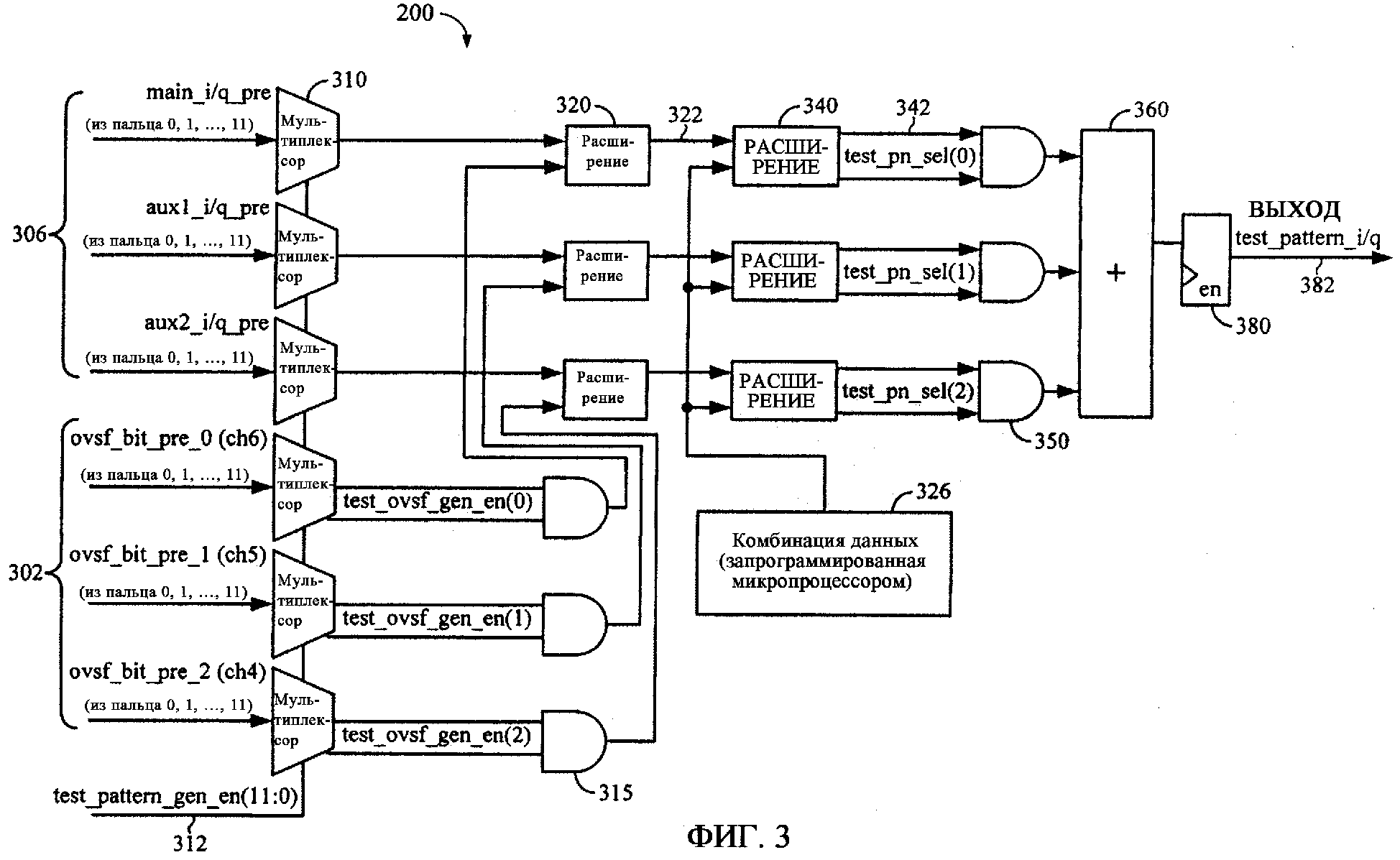

Фиг.3 - функциональная блок-схема, иллюстрирующая пример схемы генерации комбинаций тестовых данных.

Подробное описание изобретения

Изложенное ниже подробное описание вместе с сопроводительными чертежами предназначено для описания различных вариантов осуществления настоящего изобретения и не претендует на представление единственных вариантов, в которых настоящее изобретение можно реализовать на практике. Каждый из описанных здесь вариантов предложен просто в качестве примера или иллюстрации настоящего изобретения, и их не следует рассматривать как предпочтительные или имеющие преимущества перед другими вариантами. Данное подробное описание включает в себя конкретные детали, приведенные с целью обеспечения полного представления о настоящем изобретении. Однако специалистам в данной области техники должно быть очевидно, что настоящее изобретение можно реализовать на практике и без этих конкретных деталей. В некоторых случаях хорошо известные структуры и устройства показаны в виде блок-схем во избежание затруднений в понимании концепций настоящего изобретения. Акронимы и другую описательную терминологию, примененную в данном описании, можно использовать просто для удобства и ясности, а вовсе не для ограничения объема изобретения.

В последующем описании рассматриваются различные системы и способы в контексте устройства связи CDMA. Хотя эти способы хорошо подходят для использования в приложении указанного типа, специалистам в данной области техники очевидно, что эти системы и способы можно применить к любому устройству связи. Соответственно любую ссылку на устройство связи CDMA следует трактовать только как иллюстрацию различных изобретательских аспектов настоящего изобретения, понимая, что эти изобретательские аспекты имеют широкий диапазон применений.

На фиг.1 представлена концептуальная блок-схема, иллюстрирующая одну возможную конфигурацию устройства 102 беспроводной связи для CDMA приложений. Специалистам в данной области техники очевидно, что точная конфигурация устройства 102 беспроводной связи может изменяться в зависимости от конкретного приложения и общих проектных ограничений. Устройство 102 беспроводной связи может быть реализовано с помощью процессора на основе программного обеспечения или любой другой конфигурации. В варианте, показанном на фиг.1, программно реализованный процессор может содержать микропроцессор 104 с памятью 105. Микропроцессор 104 может обеспечить платформу для выполнения программно реализованных программ, которая среди прочего обрабатывает все поддерживаемые функции для различных пользовательских интерфейсов (не показаны) и координирует функции передачи команд и сигналов управления с базовой станцией (не показана). Базовая станция может быть использована для поддержки связи между множеством беспроводных устройств или в альтернативном варианте может быть использована для подсоединения беспроводного устройства к сети, такой как сеть с коммутацией каналов или пакетной коммутацией.

Устройство 102 беспроводной связи может включать в себя интегральную схему или микросхему 106 CDMA, которая выполняет конкретные алгоритмы, что снижает требования к обработке в микропроцессоре 104. Микросхема 106 CDMA может представлять собой процессор цифровых сигналов DSP, прикладную специализированную интегральную схему (ASIC), вентильную матрицу, программируемую пользователем (FPGA), или другое программируемое логическое устройство, дискретные логические элементы, транзисторную логику, дискретные аппаратные компоненты или любые другие эквивалентные или неэквивалентные структуры, которые могут выполнять одну или несколько описанных здесь функций. Конкретные алгоритмы, выполняемые микросхемой 106 CDMA, могут включать в себя функции кодирования и модуляции, а также различные другие операции с расширенным спектром для связи CDMA. В случае, более подробно описанном ниже, микросхема 106 CDMA может также включать в себя функцию тестирования на заводе для обеспечения правильной работы аппаратных средств.

При подаче питания на устройство 102 беспроводной связи оно может попытаться установить связь с базовой станцией (не показана), используя процедуру доступа. Процедура доступа может включать в себя получение пилот-сигнала, переданного от одной или нескольких базовых станций. Пилот-сигнал, переданный от каждой базовой станции, может быть скремблирован конкретным скремблирующим кодом другой базовой станции. Получение каждого пилот-сигнала включает в себя хорошо известные процедуры для определения скремблирующих кодов для каждой из соответствующих базовых станций. Эти скремблирующие коды могут запоминаться в памяти 105 для дальнейшего использования микросхемой 106 CDMA. Как только беспроводное устройство 102 получит пилот-сигнал, оно может осуществлять связь с каждой из базовых станций, используя разные каналы управления и трафика. Каналы управления и трафика могут различаться путем расширения каждого канала ортогональным кодом, таким как коды Уолша. В некоторых приложениях для поддержания более высоких скоростей передачи данных могут использоваться коды Уолша переменной длины. Коды Уолша переменной длины специалисты в данной области техники часто называют ортогональными кодами с переменным коэффициентом расширения (OVSF). Код Уолша для каждого канала управления может быть фиксированным и, следовательно, может быть заранее запрограммирован в микропроцессоре или микросхеме CDMA на заводе-изготовителе. Эти коды Уолша могут быть задействованы устройством 102 беспроводной связи для доступа к каналам управления, которые могут использоваться базовой станцией для присвоения кодов OVSF с целью поддержки различных каналов трафика. Присвоенные коды OVSF также могут запоминаться в памяти 105 для дальнейшего использования микросхемой 106 CDMA.

На фиг.2 представлена концептуальная блок-схема, иллюстрирующая пример микросхемы CDMA. Микросхема 106 CDMA включает в себя входной каскад 210 приемника, искатель 220, демодулятор 230 и декодер 240. Входной каскад 210 приемника принимает оцифрованный приемный сигнал от антенны (не показана) через аналоговый входной каскад (не показан) и выполняет фильтрацию в основной полосе частот принятого оцифрованного сигнала. Демодулятор 230 выполняет начальную обработку сигнала CDMA по отфильтрованному оцифрованному сигналу, такую как, но не только, обратное скремблирование сигнала различными скремблирующими кодами для идентификации источника передачи базовой станции и сжатия сигнала различными кодами (OVSF) для разделения каналов трафика и управления для каждой базовой станции. Затем декодер 240 может быть использован для обеспечения дополнительных функций обработки сигнала, таких как, но не только, обратное перемежение и декодирование.

Демодулятор 230 может быть реализован различными способами. Например, можно использовать прочесывающий приемник (не показан) для борьбы с замиранием посредством использования способов разнесения. Прочесывающий приемник, как правило, использует независимое замирание разрешимых многолучевых сигналов для достижения эффекта разнесения. Это может быть достигнуто посредством комбинированного действия искателя 220 и прочесывающего приемника. В частности, искатель 220 может быть выполнен с возможностью идентификации сильных многолучевых появлений для каждого пилот-сигнала с использованием подходящих скремблирующих кодов. Затем искатель 220 может выделить пальцы для идентификации временных сдвигов многолучевых сигналов. Пальцы могут использоваться прочесывающим приемником в качестве временной привязки для корреляции трафика для каждого ожидаемого многолучевого отражения для канала OVSF. Затем отдельные корреляции для каждого канала OVS могут быть когерентно объединены и предоставлены декодеру 240 для обратного перемежения и декодирования.

Схема 200 генератора комбинаций тестовых данных, находящаяся в микросхеме 106 CDMA, может быть использована для целей тестирования. В одном варианте схема 200 генерации комбинаций тестовых данных показана внутри демодулятора 230. Схема 200 генерации комбинаций тестовых данных генерирует комбинации тестовых данных для тестирования различных компонент микросхемы CDMA, таких как, но не только, входной каскад 210 приемника, искатель 220, демодулятор 230, декодер 240 или любая их комбинация. В других вариантах схема 200 генерации комбинаций тестовых данных может находиться в микросхеме 106 CDMA в виде отдельной компоненты или находиться в одной из других компонент микросхемы CDMA. Вместо микропроцессора 104 и памяти 105 на фиг.1 для присвоения различных скремблирующих кодов и кодов OVSF для работы прочесывающего приемника можно использовать тестовый микропроцессор и память (не показаны).

На фиг.3 представлена блок-схема схемы 200 генерации комбинаций тестовых данных. Схема 200 генерации комбинаций тестовых данных включает в себя мультиплексоры 310, объединители 320, расширители 340, сумматор 360 и элемент 380 задержки. В одном варианте объединители 320 являются логическими схемами «исключающее ИЛИ». Входы в мультиплексор 310 включают в себя множество входных сигналов 302 OVSF и множество скремблирующих кодов 306, генерируемых тестовым микропроцессором и памятью. Такая архитектура позволяет осуществлять многократное эффективное использование существующих аппаратных схем в микросхеме 106 CDMA, избегая дублирования аналогичных аппаратных средств в схеме 200 генерации комбинаций тестовых данных.

Коды 302 OVSF и скремблирующие коды 306 являются входными сигналами в логическую схему 320 «исключающее ИЛИ». Расширяющий код 322 (который является логической комбинацией кодов 302 OVSF и скремблирующих кодов 306) подается затем в качестве одного из двух входных сигналов в расширитель 340. Второй входной сигнал в расширитель 340 представляет собой комбинацию 326 входных тестовых данных, которая также может быть сгенерирована тестовым микропроцессором и памятью. Характеристика комбинации 326 входных тестовых данных выбирается на основе желаемого профиля тестирования и известна специалистам в данной области техники. Комбинация 342 расширенных тестовых данных является формой комбинации 326 входных тестовых данных с расширенным спектром, где используются способы расширения спектра, известные специалистам в данной области техники. Затем комбинация 382 выходных расширенных тестовых данных (которая соответствует комбинации 342 расширенных тестовых данных) используется для тестирования различных компонент микросхемы 106 CDMA, таких как, но не только, входной каскад 210 приемника, искатель 220, демодулятор 230, декодер 240 или любая их комбинация. Если имеется множество комбинаций 342 расширенных тестовых данных, то комбинация 382 выходных расширенных тестовых данных является суперпозицией множества комбинаций 342 расширенных тестовых данных. Если имеется только одна комбинация 342 расширенных тестовых данных, то комбинация 382 выходных расширенных тестовых данных будет такой же, как комбинация 342 расширенных тестовых данных.

В одном варианте расширяющий код 322 заблокирован, а расширитель 340 заменяется перемежителем (не показан), выполненным с возможностью перемежения комбинации 326 входных тестовых данных для создания перемежающейся комбинации тестовых данных для тестирования декодера 240 микросхемы 106 CDMA. При такой конфигурации тестирования функция декодирования декодера 240 игнорируется. В другом варианте расширяющий код 322 заблокирован, а расширитель 340 заменяется кодером (не показан), выполненным с возможностью кодирования комбинации 326 входных тестовых данных для получения комбинации кодированных тестовых данных для тестирования декодера 240 микросхемы 106 CDMA. При такой конфигурации тестирования игнорируется функция перемежения декодера 240. Еще в одном варианте расширитель 340 заменяется перемежителем и кодером, выполненными с возможностью перемежения и кодирования комбинации 326 входных тестовых данных для создания кодированной перемежающейся комбинации тестовых данных для тестирования декодера 240 микросхемы 106 CDMA.

В одном варианте коды 302 OVSF и скремблирующие коды 306 из множества пальцев вводятся по отдельности в два мультиплексора 310. В одном варианте входной сигнал в один мультиплексор 310 включает в себя двенадцать кодов 302 OVSF, а входной сигнал в другой мультиплексор 310 включает в себя двенадцать скремблирующих кодов 306. Сигнал 312 разрешения, генерируемый тестовым микропроцессором, обеспечивает последовательное разблокирование каждого из множества наборов кодов 302 OVSF и скремблирующих кодов 306 для последовательной генерации выходных сигналов 322 «исключающее ИЛИ». Такой последовательный подход позволяет использовать только один расширитель 340 в схеме 200 генерации комбинаций тестовых данных для синтеза расширенных комбинаций 342 тестовых данных.

В одном варианте в параллельные наборы из двух мультиплексоров 310 отдельно вводятся дополнительные параллельные ветви множества кодов 302 OVSF и множества скремблирующих кодов 306. В одном варианте, как показано на фиг.3, по отдельности вводятся три параллельные ветви множества кодов 302 OVSF и множества скремблирующих кодов 306 в три параллельных набора из двух мультиплексоров 310. В этом варианте имеется шесть мультиплексоров 310, три логических схемы 320 «исключающее ИЛИ» и три расширителя 340. Сумматор 360 суммирует параллельные ветви в виде единой комбинации 382 выходных расширенных тестовых данных.

В одном варианте для непропускания ветвей кодов 302 OVSF, если это необходимо, реализованы логические элементы И 315. В другом варианте логические элементы И 350 реализованы для непропускания ветви любой комбинации 342 расширенных тестовых данных, если это необходимо. Разблокирование логических элементов И 315, 350 осуществляется сигналами разрешения от тестового микропроцессора. Вдобавок в одном варианте реализован элемент 380 задержки для согласования временных задержек, связанных с микросхемой 106 CDMA.

Различные иллюстративные логические блоки, модули и схемы, описанные в связи с раскрытыми здесь вариантами, могут быть реализованы или выполнены с помощью процессора общего назначения, процессора DSP, интегральной схемы ASIC, матрицы FPGA или другого программируемого логического устройства, дискретного вентильной или транзисторной логики, дискретных аппаратных компонент или любой их комбинации, спроектированной для выполнения описанных здесь функций. Процессор общего назначения может представлять собой микропроцессор, а в альтернативном варианте этот процессор может быть любым стандартным процессором, контроллером, микроконтроллером или конечным автоматом. Процессор также может быть реализован в виде комбинации вычислительных устройств, например, комбинации из DSP и микропроцессора, множества микропроцессоров, одного или нескольких микропроцессоров в сочетании с ядром DSP или любой другой указанной конфигурации.

Способы или алгоритмы, описанные в связи с раскрытыми здесь вариантами, могут быть воплощены непосредственно аппаратным путем в виде программного модуля, выполняемого процессором, или в виде комбинации того и другого. Программный модуль может находиться в ОЗУ (RAM), флэш-памяти, ПЗУ (ROM), стираемом программируемом ПЗУ (EPROM), электрически стираемом программируемом ПЗУ (EEPROM), регистрах, жестком диске, на съемном диске, ПЗУ на компакт-диске или на носителе данных любого вида, известного в данной области техники. Носитель данных может быть связан с процессором так, что процессор может считывать из него информацию и записывать в него информацию. В альтернативном варианте носитель данных может быть интегрирован в процессор. Процессор и носитель данных могут находиться в специализированной микросхеме ASIC. Схема ASIC может находиться в устройстве беспроводной связи или где-либо еще. В альтернативном варианте процессор и носитель данных могут находиться в виде дискретных компонент в устройстве беспроводной связи или где-либо еще.

Предшествующее описание раскрытых вариантов предложено для того, чтобы дать возможность специалистам в данной области техники выполнить или использовать настоящее изобретение. Специалистам в данной области техники будет очевидно, что возможны различные модификации этих вариантов, а определенные здесь общие принципы могут быть применены к другим вариантам, не выходя за рамки существа или объема изобретения. Таким образом, подразумевается, что настоящее изобретение не ограничивается показанными здесь вариантами, а должно соответствовать самому широкому диапазону согласно раскрытым здесь принципам и новым признакам.

Реферат

Изобретение относится к генерации комбинаций тестовых данных для интегральных схем. Сущность: интегральная схема CDMA включает демодулятор для корреляции входных данных с одним из набора кодов и генератор комбинаций тестовых данных для расширения входных тестовых данных одним из набора кодов для формирования расширенных тестовых данных и предоставления расширенных тестовых данных демодулятору. Набор кодов может быть объединен с входными тестовыми данными для генерации набора расширенных тестовых данных, которые затем подаются в различные компоненты микросхемы CDMA для тестирования различных компонент. В одном варианте каждый код из набора кодов содержит скремблирующий код и расширяющий код. 3 н. и 20 з.п. ф-лы, 3 ил.

Комментарии