Схемная компоновка с деактивируемой цепью сканирования - RU2211457C2

Код документа: RU2211457C2

Чертежи

Описание

Изобретение относится к схемной компоновке с некоторым количеством функциональных блоков, причем каждый из функциональных блоков связан по меньшей мере с одним другим функциональным блоком, и по меньшей мере часть этих соединений реализуется посредством элемента блокировки, который посредством шины активизации переключается из нормального режима в режим тестирования и который имеет другой вход данных и другой выход данных, причем упомянутые другие вход данных и выход данных соединены между собой посредством участков шины данных таким образом, что элементы блокирования образуют регистр сдвига, реализующий цепь сканирования.

Подобная схемная компоновка известна из патента США 4534028. Описанная в этом патенте цепь сканирования, реализуемая упомянутой схемной компоновкой, предназначена для осуществления простейшего тестирования функциональных блоков схемной компоновки, так как посредством элементов блокировки, которые взаимно соединены для образования регистра сдвига и которые выполнены в виде триггерных схем, на отдельные функциональные блоки к определенному моменту времени могут подаваться определенные входные состояния, и накапливаемые в элементах блокировки промежуточные результаты могут вновь считываться посредством регистра сдвига. Функциональный блок может при этом представлять собой схемный элемент, который выполняет определенную тестируемую функцию.

Определенные типы электронных схем, такие как, например, схемы для карт с микросхемами (чип-карт), требуют высокой степени защиты схемной информации и зашифрованных данных, как, например, ключа шифрования для способов криптозащиты. Эта информация, принципиально важная с точки зрения защищенности, должна быть защищена как от анализа посторонними лицами, так и от противоправных манипуляций. Одновременно конструкция схемы требует обеспечения в минимальной степени прозрачности и доступа к таким блокам схемы и данным, критичным с точки зрения защищенности, чтобы гарантировать достаточную надежность тестирования. Чтобы гарантировать высокую степень маскирования тестирования в процессе производства и после его завершения, часто в электронную схему встраивают дополнительные тестовые компоненты, как, например, вышеупомянутая цепь тестирования, которые дают возможность установить функциональный блок практически во все требуемые состояния, чтобы проверить его функциональные возможности.

Эти добавляемые для целей тестирования компоненты часто активизируются и соответственно деактивизируются посредством центральных контроллеров тестирования. Такие контроллеры тестирования активизируются либо посредством программного обеспечения, либо посредством внешних сигналов через специальные тестовые контактные площадки. Оба варианта относительно просты для манипулирования, что создает потенциальный риск защищенности. Поэтому используемые до настоящего времени способы обеспечения анализа интегральных схем не совместимы с требуемой в настоящее время высокой надежностью специальных электронных компонентов.

Кроме того, известен способ, при котором специальные функциональные блоки схемной компоновки после тестирования или первого пуска в эксплуатацию необратимым образом отделяются от остальной схемы.

Так в заявке DE 19711478 A1 описано, что тестовое постоянное запоминающее устройство (ПЗУ) может считываться только через необратимым образом устанавливаемый мультиплексор, чтобы тем самым предотвратить возможность доступа к тестовому ПЗУ после тестирования.

В заявке DE 2738113 A1 описан способ необратимого предотвращения доступа к запоминающему устройству (ЗУ), содержащему данные, критичные для обеспечения защиты и для функционирования, за счет использования разрушаемых вентилей.

Эти известные устройства имеют, однако, недостаток, заключающийся в том, что необратимым образом устанавливаемые или разрушаемые компоненты схемы размещаются в легко обнаруживаемых положениях и относительно легко могут быть восстановлены, вследствие чего возникает возможность несанкционированного анализа и манипуляции.

Задача изобретения состоит в том, чтобы создать схемную компоновку вышеупомянутого типа таким образом, чтобы несанкционированный анализ с использованием цепи сканирования стал практически невозможным.

Указанная задача решается в схемной компоновке, охарактеризованной в пункте 1 формулы изобретения. Дальнейшие предпочтительные варианты осуществления изобретения представлены в зависимых пунктах формулы изобретения.

Элементы блокировки цепи сканирования распределены по всей поверхности интегральной схемы. Поэтому шина активизации и шина данных, составленная из отдельных участков шины данных, проходят по всей поверхности интегральной схемы. Следовательно, и элементы защиты децентрализованным образом распределены по всей поверхности интегральной схемы, вследствие чего существенно повышается защищенность по отношению к попыткам несанкционированного доступа и манипулирования. За счет соответствующего выбора технологии, помимо этого, достигается очень высокая защищенность против перепрограммирования элементов защиты. Примеры таких элементов защиты раскрыты в заявке DE 19604776 A1.

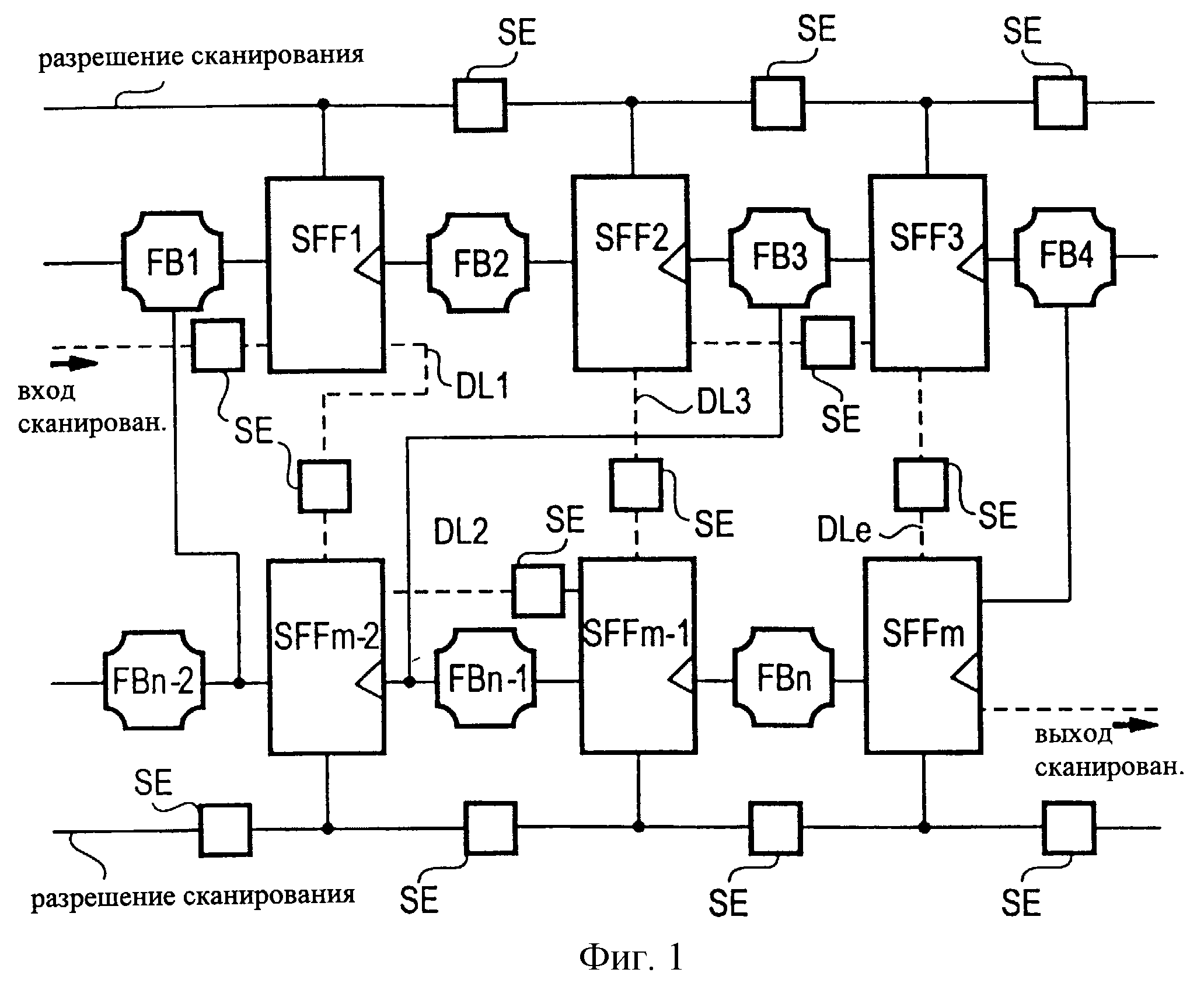

Выбор различных элементов защиты в виде разъединяемых или восстанавливаемых участков проводников, представляющих собой по существу "плавкие перемычки" и "плавкие антиперемычки", повышает защищенность, так как "взломщик" не может с ходу распознать, какой тип элементов используется в схеме. Очень выгодным является применение обоих типов элементов защиты. Элементы защиты могут также применяться в соединении с логическими схемами, чтобы путем приложения определенного потенциала на их входе обеспечить их функционирование в качестве разомкнутого или замкнутого переключателя.

Изобретение поясняется ниже на примерах его осуществления, иллюстрируемых чертежами, на которых представлено следующее:

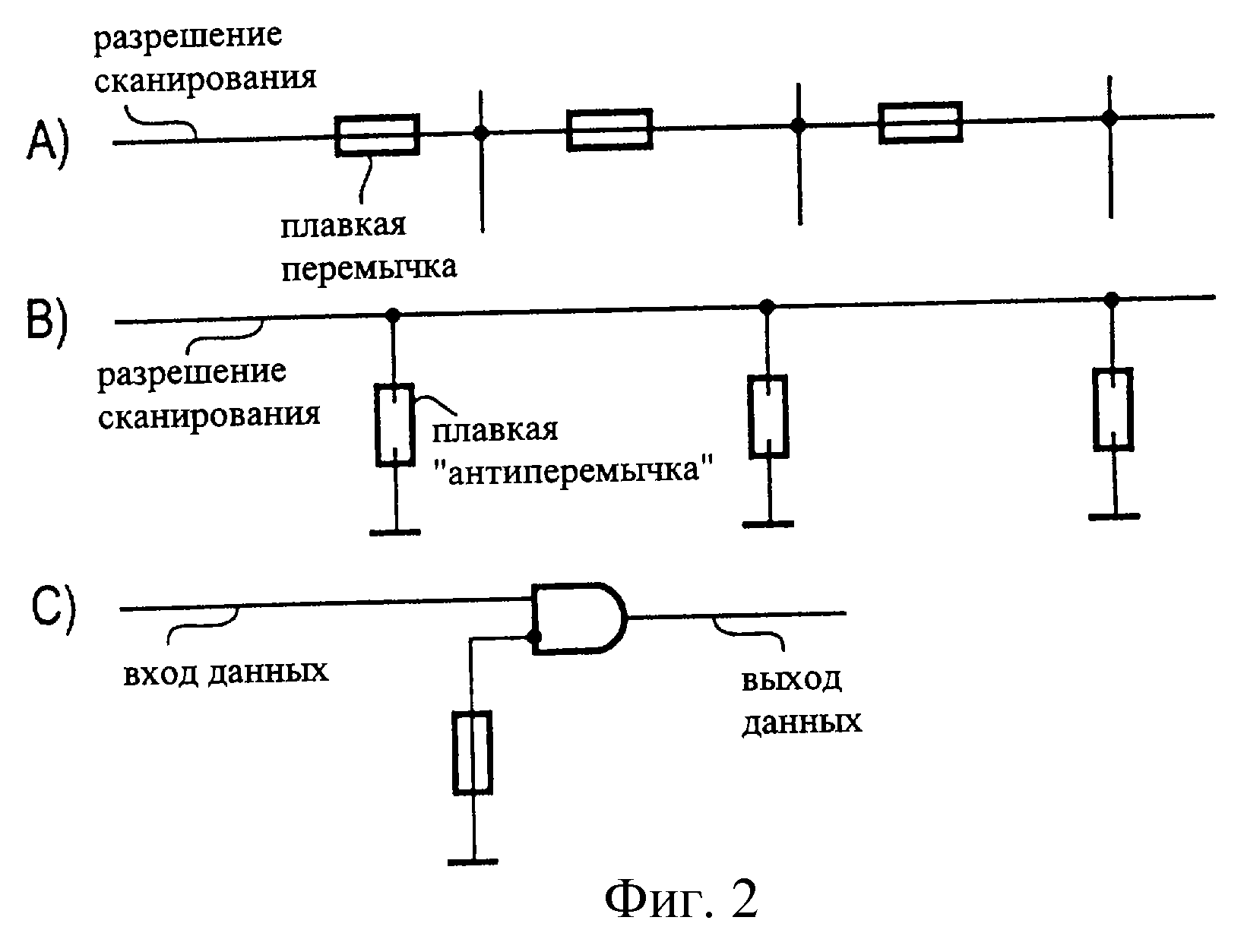

фиг.1 - соответствующая изобретению схемная компоновка и

фиг.2

- примеры осуществления элементов защиты.

Схемная компоновка, согласно фиг, 1, показывает функциональные блоки FB1...FBn, которые непосредственно или через соединительные элементы SFF1... SFFm соединены между собой. Функциональный блок может при этом соединяться с одним или несколькими другими функциональными блоками. Соединение может осуществляться непосредственно или через соединительные элементы. Соединительные элементы SFF1...SFFm чаще всего выполняются в виде специальных триггерных схем, называемых сканирующими триггерными схемами.

Соединительные элементы SFF1. . . SFFm, кроме этого, посредством шины активизации "разрешение сканирования" переключаются из нормального режима, при котором они обеспечивают соединение выхода одного функционального блока с входом следующего функционального блока, в режим тестирования. Для реализации режима тестирования они имеют дополнительный вход и дополнительный выход. Посредством этих входов и выходов они соединяются между собой посредством обозначенных пунктиром участков DL1...DLe шины данных для получения регистра сдвига. В режиме тестирования, следовательно, можно загрузить данные через вход регистра сдвига, обозначенный "вход сканирования", и затем путем переключения в нормальный режим посредством единственного тактового импульса загрузить данные из регистра сдвига в функциональные блоки FB1... FBn. Выходные данные функциональных блоков FB1...FBn загружаются в соединительные элементы, подсоединенные к соответствующему функциональному блоку, и могут после переключения в режим тестирования посредством регистра сдвига считываться с его выхода, обозначенного "выход сканирования". Посредством этой цепи сканирования каждый функциональный блок FB1...FBn приводится в любое состояние и отдельно тестируется.

В соответствии с изобретением, как в шине активизации "разрешение сканирования", так и в шине данных DL1...DLe, соединяющей соединительные элементы SFF1. . . SFFm, размещены защитные элементы SE. Они могут быть реализованы, как показано на фиг.2, как в виде разъединяемых предохранителей ("плавких вставок"), так и в виде восстанавливаемых соединений, которые, например, вызывают короткое замыкание на массу или постоянно подсоединяют проводник к потенциалу напряжения питания ("плавкие "анти-перемычки"). В качестве дополнительной возможности, во взаимосвязи с этими свойствами, применяется логическая схема, блокируемая в соответствии с определенной функцией. Эти защитные элементы SE распределены децентрализованно по всей поверхности интегральной схемы и позволяют после тестирования реализовать многократное разъединение или замыкание шины активизации "разрешение сканирования", а также участков DL1...DLe шины данных и, следовательно, цепи сканирования.

Реферат

Изобретение относится к электронике и используется для защиты информации в электронных схемах с использованием цепи сканирования. Технический результат - исключение несанкционированного анализа схемной компановки, которая имеет некоторое количество функциональных блоков (FB1...FBn), причем каждый из функциональных блоков соединен, по меньшей мере, с одним другим функциональным блоком и, по меньшей мере, часть этих соединений реализована посредством элемента блокирования (SFF1...SFFm), который посредством шины активизации (разрешение сканирования) может переключаться из нормального режима в режим тестирования и который имеет дополнительный вход данных и выход данных, причем эти дополнительные входы и выходы данных соединены между собой посредством участков шины данных (DL1...DLe) так, что элементы блокирования (SFF1...SFFm) образуют регистр сдвига, реализующий цепь сканирования. В шине активизации (разрешение сканирования) и/или на участках шины данных (DL1. . . DLe) размещен, по меньшей мере, один электрически программируемый защитный элемент (SE), который либо прерывает соответствующий проводник, либо соединяет его с определенным потенциалом. 3 з.п.ф-лы, 2 ил.

Комментарии