Устройство тестирования микросхем nand-памяти на основе плис - RU194203U1

Код документа: RU194203U1

Чертежи

Описание

Область применения

Полезная модель относится к области тестирования интегральных микросхем NAND-памяти и представляет собой устройство тестирования на основе программируемой логической интегральной схемы (ПЛИС), позволяющую одновременно и независимо тестировать множество микросхем памяти при операциях чтения, записи и стирания данных, в том числе в условиях повышенных и пониженных температур функционирования.

Уровень техники

Требование высокой скорости доступа к возрастающему объему хранимой информации является основным фактором перехода от магнитных накопителей (HDD) к твердотельным накопителям (ТН, SSD) на основе NAND-памяти. Для снижения стоимости хранения данных на SSD применяются различные технологии увеличения плотности записи, такие как многобитовые ячейки памяти (MLC, TLC, QLC) [1], переход к трехмерному производству ячеек памяти в кристалле (V-NAND, BiCS) [2, 3] и многокристальному корпусированию кристаллов памяти [4]. Первые два подхода могут быть реализованы только производителями кристаллов NAND-памяти, которых на данный момент в мире представлены лишь несколько компаниями, такими как Samsung, Toshiba, SK Hynix, и Micron/Intel. Тогда как этап корпусирования и создания многокристальных модулей может быть реализован для локального производства микросхем NAND-памяти и твердотельных накопителей на их основе. Все современные микросхемы NAND-памяти поддерживают один из двух стандартов: Open Nand Flash Interface (ONFI) и Toggle DDR. Эти стандарты описывают физический интерфейс, временные режимы работы, механизмы идентификации, набор поддерживаемых команд. Несмотря на различие стандартов, они обеспечивают схожий функционал и скорость работы микросхем NAND-памяти. ONFI в отличие от Toggle является открытым стандартом, что является важным преимуществом и позволяет свободно использовать различным производителям NAND-памяти и систем тестирования микросхем NAND-памяти. В настоящее время наиболее распространенным для микросхем NAND-памяти является корпус типа BGA (Ball grid array) с шариковыми выводами на нижней стороне микросхемы для поверхностного монтажа на печатные платы готового устройства, например, твердотельного накопителя. Корпусирование кристаллов в микросхемы NAND-памяти типа BGA, как правило, включает следующие операции: утонение и резка пластины с кристаллами NAND-памяти, монтаж кристаллов в стек на подложку, создание проволочных соединений между кристаллами и подложкой, герметизация компаундом, установка шариковых выводов с обратной стороны подложки и резка на отдельные микросхемы NAND-памяти.

В настоящее время рынок продукции на основе NAND-памяти динамично развивается, поэтому важным фактором конкурентоспособного производства является постоянная разработка и совершенствование выпускаемых изделий. Увеличенная сложность проектирования и изготовления микросхем NAND-памяти, в свою очередь, может приводить к появлению отказов в работе конечных устройств при определенных режимах работы [5]. Для предотвращения подобных ситуаций необходимо выполнять тестирование готовой продукции с учетом всех предъявляемых к ним требований. Одним из вариантов решения данной проблемы являются применение систем тестирования на базе микроконтроллеров [6]. Такие системы используют микроконтроллер с записанными тестовыми процедурами и ряд внешних устройств для сопряжения интерфейсов с устройством тестирования. Несмотря на достаточно простую архитектуру подобных устройств, они обладают недостатком - невозможностью гибкой настройки под различную продукцию из-за жесткой привязки к сигнальным линиям микроконтроллера. Другим подходом к решению проблемы является разработка и создание систем тестирования на основе программируемых логических интегральных схем (ПЛИС) [7], обладающих как минимально необходимым функционалом, так и достаточной гибкостью настройки функциональных тестов под требования заказчика продукции. Гибкость настройки функционального тестирования достигается за счет использования связки управляющего микроконтроллера и ПЛИС, реализующей интерфейс взаимодействия с микросхемами и тестовые процедуры. В случае изменения модели тестируемых микросхем NAND-памяти, ПЛИС может быть легко перепрограммирована для реализации новых тестовых процедур.

Одной из важных характеристик системы тестирования микросхем NAND-памяти является масштабируемость, поскольку выполнение функционального тестирования каждой микросхемы включает процедуры записи и чтения всего объема памяти и занимает значительное время (десятки минут). Для приемлемого времени тестирования изготавливаемой продукции тестовые процедуры требуется распараллеливать, поэтому большинство тестовых систем имеют модульную архитектуру и состоят из набора устройств тестирования с разъемными BGA-сокетами для микросхем NAND-памяти объединенных управляющим компьютером (рабочей станцией). При этом устройства тестирования могут размещаться в климатической камере для проведения испытаний и подтверждения соответствия требованиям надежности функционирования микросхем NAND-памяти.

Изготовление промышленных партий микросхем NAND-памяти наряду с отработкой производства отдельных образцов и малых опытных партий ставит дополнительные задачи распараллеливания этих процессов как в производственном цикле, так и при тестировании. Кроме того, к тестированию отдельных партий микросхем NAND-памяти могут предъявляться более строгие требования, отличные от требований к коммерческим изделиям, в том числе по воздействию внешних условий. При этом важно отметить, что тестирование разных партий микросхем NAND-памяти может происходить одновременно, в результате чего такой характеристики как модульность системы тестирования уже недостаточно и возникает дополнительное требование - автономность работы тестовых модулей для реализации тестовых процедур вне автоматизированной системы.

Таким образом, одним из направлений развития систем тестирования NAND-памяти является обеспечение возможности работы ее отдельных модулей (устройств тестирования), как в составе модульной системы тестирования, так и в автономном режиме. Это позволит обеспечить универсальность работы модульной системы тестирования и ее параллельное использование, как при тестировании больших промышленных партий микросхем, так и при отработке производства отдельных образцов и малых опытных партий, без остановки тестирования основной линейки продукции.

В качестве примера немодульного исполнения можно привести устройство проверки NAND-памяти с использование вычислительной среды Mathlab [8]. Система тестирования состоит из управляющего компьютера, на котором установлена вычислительная среда Mathlab и платы тестирования, соединенной через интерфейс USB 2.0. На тестовой плате имеется ПЛИС, оперативная память DDR3, сокет для установки тестируемой микросхемы NAND-памяти и коммуникационный интерфейс USB 2.0, соединяющий управляющий компьютер и ПЛИС. Система тестирования может быть использована для микросхем с корпусами BGA-132, BGA-152 TSOP-48 или TLGA-52. В качестве примера исполнения указываются микросхемы ПЛИС Xilinx Spartan-6 и коммуникационного интерфейса Cypress 2131. Процедура тестирования заключается запуске среды разработки Mathlab на управляющем компьютере и загрузке тестового модуля, состоящего из нескольких библиотек и исполняемых файлов, конфигурации тестирования и генерации базы данных с тестовыми данными, установке микросхемы NAND-памяти в сокет, установке соединения между управляющим компьютером и ПЛИС с помощью среды Mathlab, выполнении процедуры тестирования согласно тестовым команда и тестовым данным.

Недостатками данного устройства являются отсутствие возможности тестирования более одной микросхемы и использования устройства тестирования в автономном режиме, необходимом при отработке производства отдельных образцов и малых опытных партий микросхем.

Известно устройство тестирования микросхем NAND-памяти [9], состоящее из основной управляющей платы, к которой присоединится множество тестовых плат, представляющих собой контроллеры NAND-памяти, непосредственно осуществляющие тестированием микросхем. В состав управляющей платы входит центральный процессор, оперативная память, постоянное запоминающее устройство, память со встроенным программным обеспечением и буфер данных. В памяти со встроенным программным обеспечением имеется программный код двух видов: один предназначен для функционирования управляющей платы (отвечает за вызов тестовых команд, получение и отображение результатов), а второй - для функционирование тестовых плат (получение тестовых команд, выполнение тестовых процедур и отправки результатов тестирования). Управляющая плата имеет разъемы для подключения к тестовым платам, к дисплею для вывода результатов тестирования и к электронному блоку, который позволяет обновлять встроенное программное обеспечение. В состав тестовой платы входит центральный процессор, оперативная память, постоянное запоминающее устройство, буфер данных. Тестовая плата имеет разъемы для подключения к управляющей плате и к микросхемам NAND-памяти. Работа устройства тестирования микросхем NAND-памяти осуществляется следующим образом: после подключения тестируемых микросхем NAND-памяти к тестовым платам и подачи питания на устройство тестирования микросхем производится загрузка управляющего встроенного программного обеспечения в оперативную память центрального процессора на управляющей плате. Затем управляющая плата осуществляет передачу встроенного программного обеспечения для тестирования в оперативную память тестовых плат и отправляет тестовые команды. Тестовые платы проводят процедуру тестирования микросхем под управлением загруженного программного обеспечения и принятых команд, после чего отправляют результаты тестирования обратно на управляющую плату, где они отображаются на дисплее. Таким образом, данное устройство тестирования микросхем NAND-памяти может применяться независимо от подключения к компьютеру для осуществления процедуры тестирования, но тестовые платы не могут работать автономно без использования управляющей платы.

Недостатком данного устройства является отсутствие автономного режима работы тестовых плат, необходимого при отработке производства отдельных образцов и малых опытных партий микросхем. Кроме того, процесс функционального тестирования осуществляется с помощью процессоров без использования ПЛИС, что не обеспечивает гибкую настройку под широкий выбор интерфейсов и тестируемых микросхем NAND-памяти. Также не указана возможность функционального тестирования согласно стандарту ONFI, без поддержки которого невозможно протестировать ряд современных моделей микросхем NAND-памяти, поддерживающих этот стандарт.

Известен метод программирования и тестирования полупроводниковых микросхем, а также устройство реализующее данный метод [10]. Тестирующая система состоит из персонального компьютера, тестирующего программного обеспечения, и загрузочных печатных плат. Печатные платы могут помещаться в единую стойку и соединяются с компьютером по магистральной шине данных. Каждая плата имеет быстрый элемент памяти для хранения тестовых шаблонов, множество тестирующих микросхем (testing integrated-circuit chips, TIC) и множество тестируемых полупроводниковых микросхем. Все TIC соединяются между собой и быстрым элементом памяти с помощью шины данных средней скорости (по сравнению с магистральной шиной данных). Каждый TIC соединяется с одной или множеством тестируемых устройств с использованием самой быстрой шины данных. В качестве TIC могут использоваться специализированные микросхемы (ASIC) или ПЛИС с использованием дополнительных микросхем (например, операционных усилителей). В качестве тестируемых микросхем могут использоваться, например, микросхемы NAND-памяти. Разделение шин, данных по скоростям обусловлено разным объемом информации, передаваемой в единицу времени. Магистральная шина используется для инициализации процедуры тестирования и получения конечных результатов. Шина, связывающая TIC и быстрый элемент памяти на плате, отвечает за передачу тестовых шаблонов из памяти в TIC и периодически используется во время процедуры тестирования. Самая быстрая шина используется на каждом цикле тестирования для связи TIC и тестируемой микросхемой, и поэтому должна обладать наибольшей скоростью работы.

Если TIC реализуется с помощью ПЛИС, то для его работы также необходим тактирующий генератор, который синхронизует работу ПЛИС и тестируемой микросхемы, EEPROM-память, хранящая конфигурацию ПЛИС, используемая на этапе инициализации процедуры тестирования. Так как TIC должен выполнять не только функциональное тестирование, но электрическое тестирование (уровни напряжений и токов, потребляемая мощность), то в его состав также входит блок аналоговой электроники, который может состоять в том числе из операционных усилителей.

Недостатками данного устройства является отсутствие возможности тестирования микросхем NAND-памяти в BGA-корпусе согласно стандарту ONFI, что не позволяет протестировать ряд современных моделей микросхем NAND-памяти, поддерживающих этот стандарт. Также TIC не может работать в автономном режиме, необходимом при отработке производства отдельных образцов и малых опытных партий микросхем.

Наиболее близким к заявляемому устройству, выбранному за прототип, является устройство автоматизированного тестирования [11], предназначенное для проведения испытания для микросхем NAND-памяти семейства MT29F, в том числе на контролируемое старение. Данная память выпускается компанией Micron и включает в себя модули памяти, реализованные по различным технологиям (SLC, MLC, TLC) с использованием стандарта ONFI для взаимодействия с внешними устройствами. Устройство может работать с микросхемами NAND-памяти, имеющими BGA-корпус (например, BGA-100). Устройство включает в себя рабочую станцию, представляющую собой компьютер, преобразователь интерфейсов USB-UART, управляемый источник питания, набора объединительных плат, представляющих собой материнские платы, и устройство тестирования, состоящее из сигнальных и тестовых плат. Рабочая станция с управляющей программой подсоединяется к преобразователю USB-UART по интерфейсу USB. Данный преобразователь позволяет мультиплексировать несколько UART-линий, которые подключаются множеству объединительных плат. Также к объединительным платам подключаются силовые линии контроллера питания, управляемого по LAN с рабочей станции. Каждая объединительная плата содержит коннекторы для подключения устройств тестирования, причем на каждое устройство тестирования приходится по два коннектора. Один из коннекторов служит для подключения питания устройства тестирования, а второй - для приема/передачи данных посредством UART. Каждая сигнальная плата в устройстве тестирования содержит ПЛИС, микросхему флэш-памяти для хранения конфигурации, и коннекторы для подключения к тестовым платам. Тестовая плата содержит коннекторы для подключения к сигнальной плате, и высокотемпературные BGA-сокеты для монтажа микросхем NAND-памяти. Общее количество одновременно тестируемых микросхем NAND-памяти зависит от количества тестовых плат в составе устройства тестирования и количества устройств тестирования. Система тестирования может содержать N объединительных плат, М устройств тестирования, в составе которых может быть K тестовых плат, где М, N, K - положительные целые числа. Тестирование осуществляется следующим образом. После подсоединения микросхем NAND-памяти к тестовым платам и включения системы происходит загрузка конфигурации ПЛИС из микросхемы флэш-памяти, располагающейся на устройстве тестирования. С рабочей станции поступает команда инициализации всех ПЛИС, которые в свою очередь посылают команды сброса на все подключенные микросхемы NAND-памяти. Затем поступает команда считывания серийного номера микросхемы (ID) и информации о неисправных блоках памяти (bad blocks). Эта информация передается назад на рабочую станцию и на интерфейсе управляющего программного обеспечения высвечивается количество подключенных к тестовым платам микросхем памяти и их состояние. После этого может выполняться функциональное тестирования путем выполнения последовательных команд записи и чтения с использованием тестовых шаблонов (все "0", все "1", шахматный порядок). Для осуществления контролируемого старения тестовые платы с тестируемыми микросхемами NAND-памяти помещаются в климатическую камеру, работающую при температуре 85°С и проводится непрерывное циклическое функциональное тестирование в течение десятков и сотен часов.

Недостатками прототипа является неспособность работы устройств тестирования в автономном режиме отдельно от модульной системы тестирования, необходимом при отработке производства отдельных образцов и малых опытных партий микросхем.

Технический результат предлагаемого устройства состоит в возможности автономного использования устройств тестирования, то есть отдельно от модульной системы тестирования, что позволяет выполнять отработку производства отдельных образцов и малых опытных партий микросхем.

Достигается технический результат за счет того, что устройство тестирования представляет собой единую плату, на которой установлен управляющий микроконтроллер, алгоритмический генератор тестовых шаблонов на основе ПЛИС, цифровые индикаторы для вывода результатов тестирования.

Перечень фигур

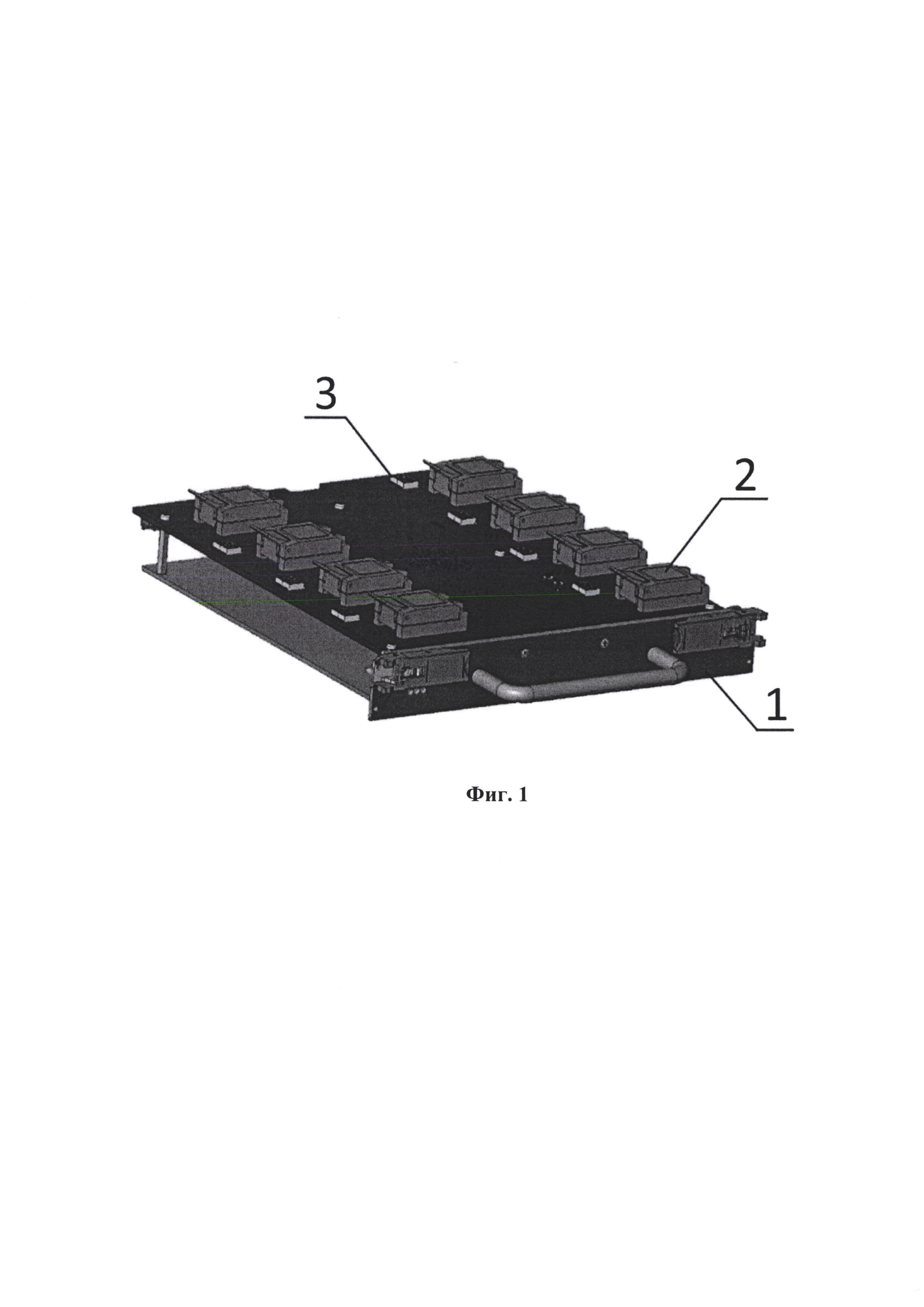

Фиг. 1 Устройство тестирования (1) с BGA-сокетами (2) и цифровыми индикаторами (3).

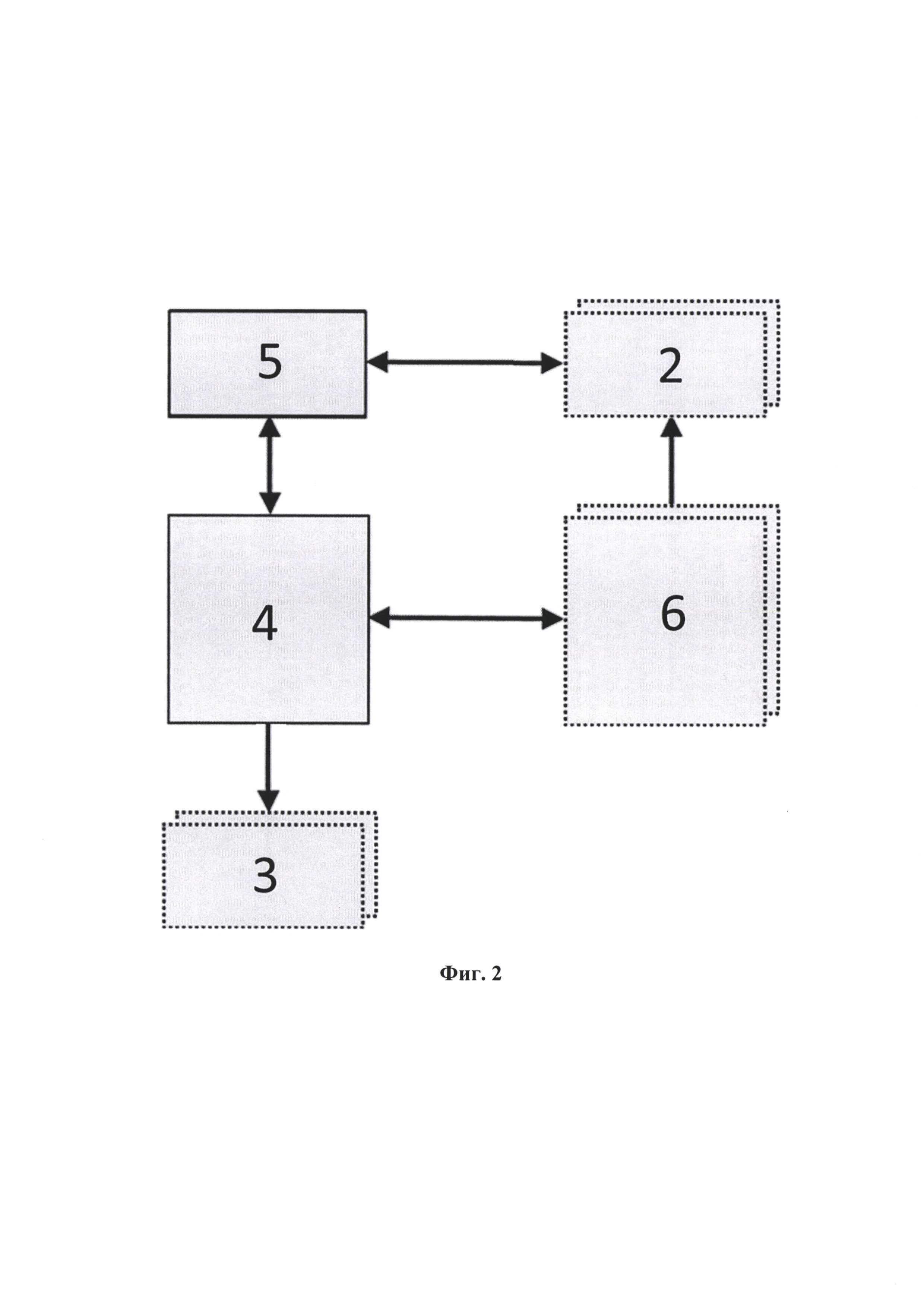

Фиг. 2 Функциональная схема устройства тестирования, состоящего из управляющего микроконтроллера (4), ПЛИС (5), программируемых преобразователей напряжения (6), BGA-сокетов (2) и цифровых индикаторов (3).

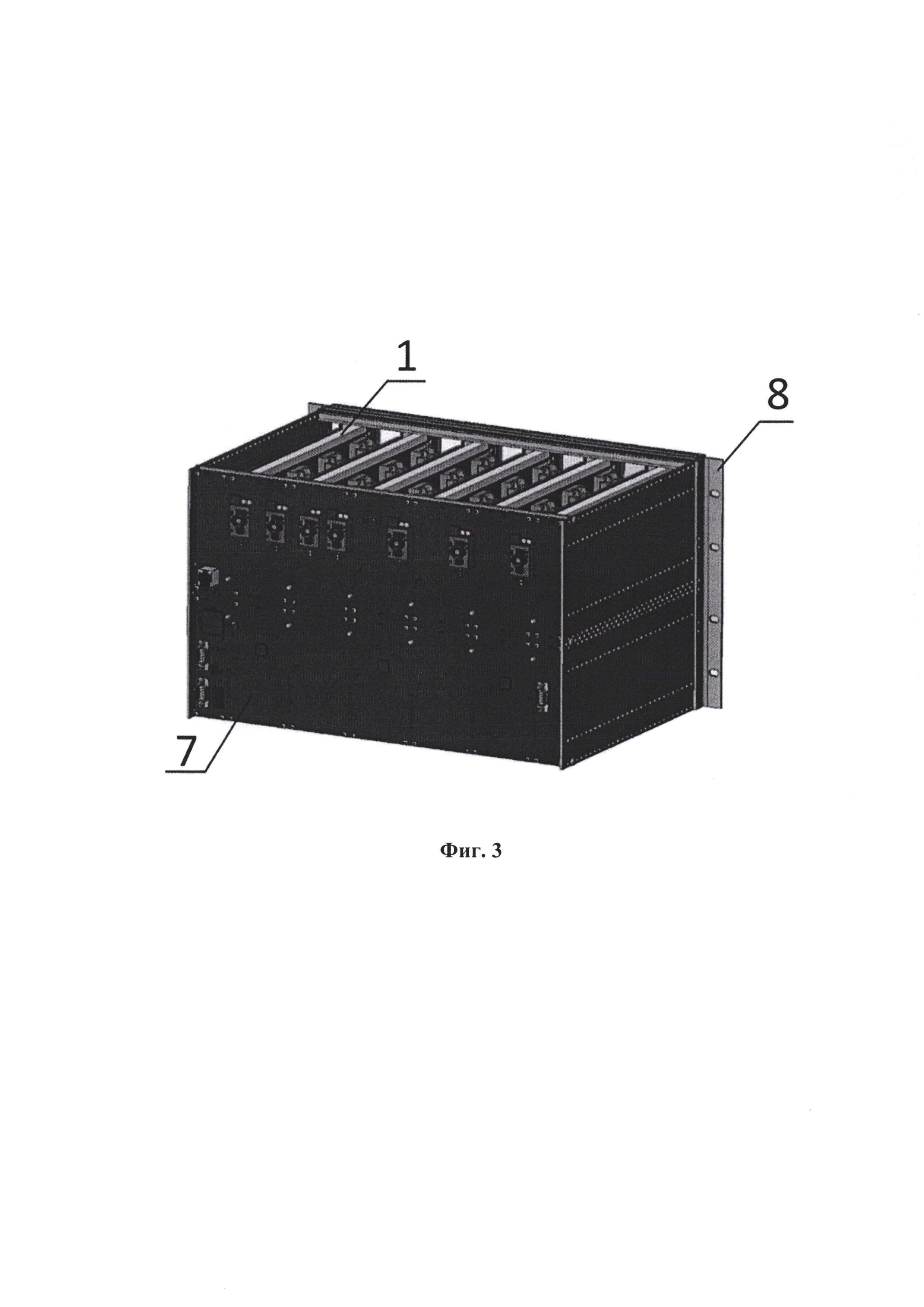

Фиг. 3 Модульная система тестирования (8) с установленными устройствами тестирования (1), соединенными с объединительной платой (7), вид сзади.

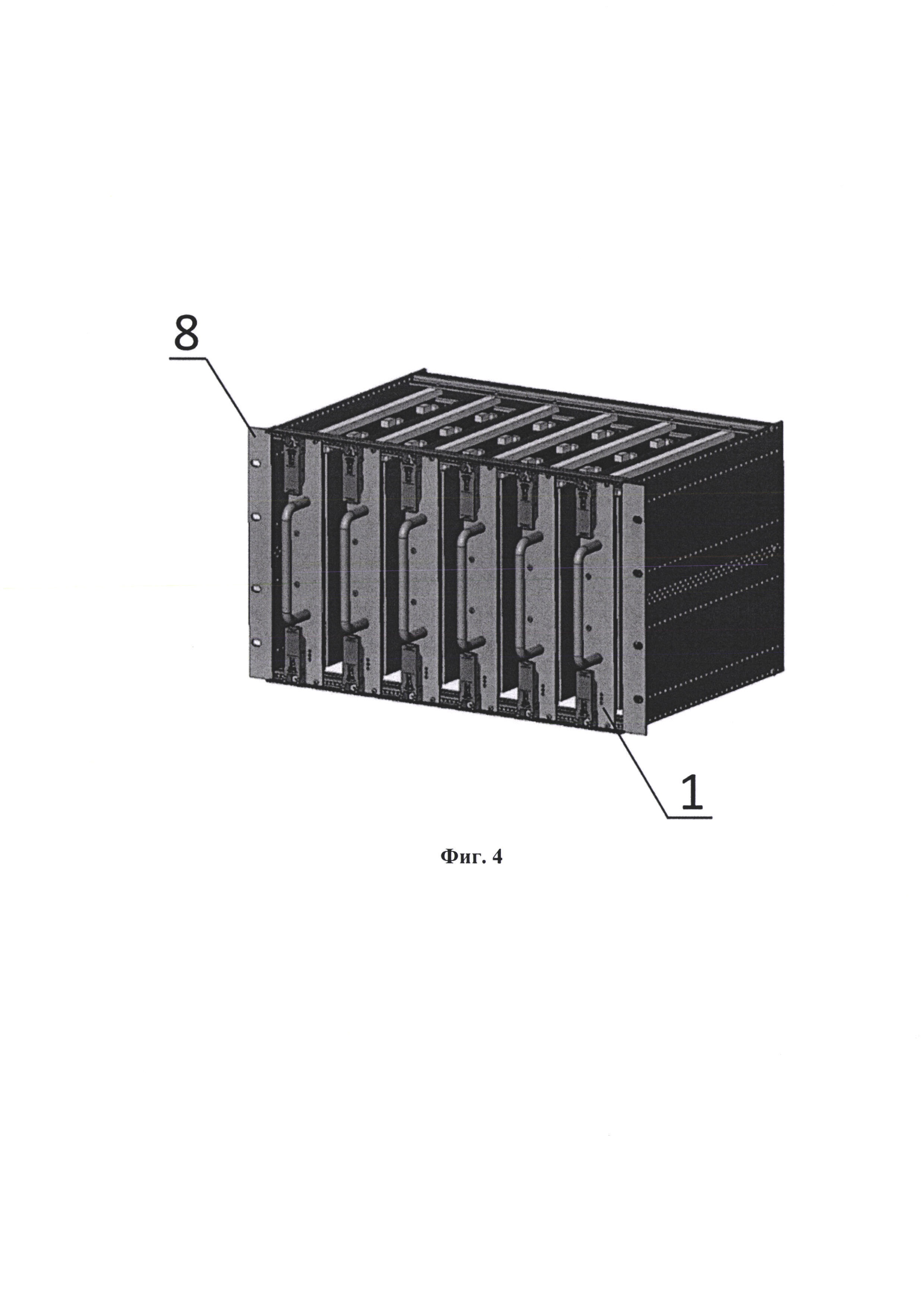

Фиг. 4 Модульная система тестирования (8) с установленными устройствами тестирования (1), вид спереди.

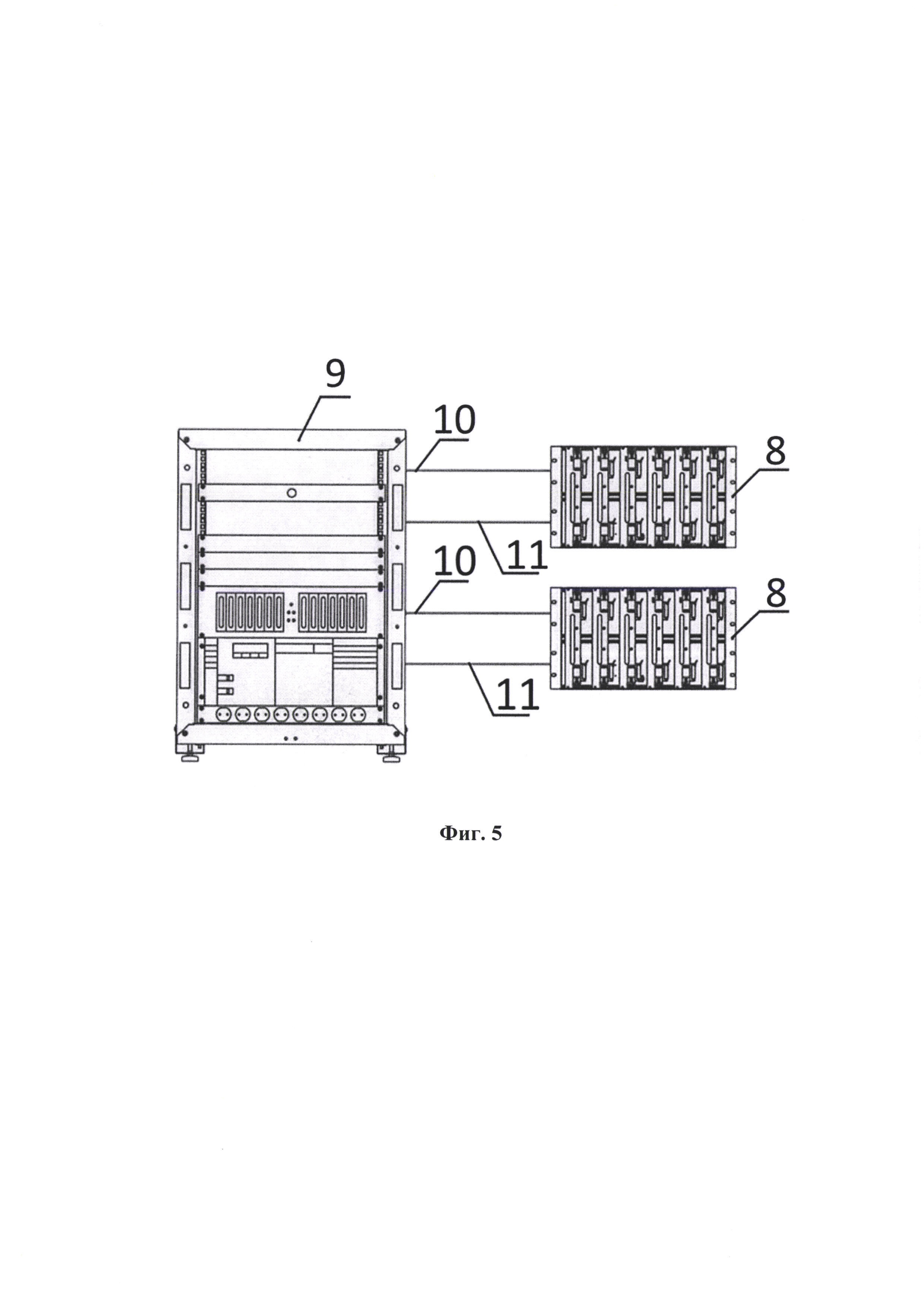

Фиг. 5 Схема подключения блока управления (9) к модульным системам тестирования NAND-памяти (8) с помощью кабелей передачи данных стандарта RS-485 (11) и кабелей питания (10).

Пример реализации полезной модели

Устройство тестирования микросхем NAND-памяти на основе ПЛИС (1) оборудовано BGA-сокетами (2), позволяющими производить монтаж и демонтаж микросхем NAND-памяти в BGA-корпусе без пайки и специального инструмента (Фиг. 1). Также устройство тестирования (1) имеет восемь цифровых индикаторов (3), позволяющих выводить результаты тестирования. В каждом устройстве тестирования (1) может устанавливаться и одновременно тестироваться до восьми микросхем NAND-памяти. Основными функциями устройства тестирования (1) являются проверка микросхем NAND-памяти, выполнение необходимых процедур обращения к микросхеме NAND-памяти согласно заданной методике испытаний и вывод результатов тестирования. Для этого в составе устройства тестирования (1) имеется микроконтроллер (4), ПЛИС (5), восемь программируемых источников напряжения (6), восемь BGA-сокетов (2) и восемь цифровых индикаторов (3), обозначенных на Фиг. 2. В качестве управляющего микроконтроллера (4) может использоваться STMicroelectronics Cortex-M4, ПЛИС (5) - Xilinix Artix-7, программируемого источника напряжения (6) -микросхема LTM4675.

Кроме того, устройство тестирования имеет возможность подключения к объединительной плате (7) для реализации работы в составе модульной системы тестирования (8), как показано на Фиг. 3 и 4. Для этого в составе устройства тестирования (1) присутствуют специальные контакты в разъеме подключения, которые определяют режим работы (автономный или в составе модульной системы тестирования). В случае установки устройства тестирования (1) в объединительную плату (7) эти контакты замыкаются и устройство тестирования (1) переходит в режим работы в составе модульной системы тестирования (8). Если же эти контакты разомкнуты, то устройство тестирования (1) переходит в автономный режим работы. Для запуска процедуры тестирования в автономном режиме в составе устройства тестирования (1) имеется кнопка запуска тестирования.

Модульная система тестирования (8) имеет возможность подключения к блоку управления (9) с использованием линий питания (10) и передачи данных (11), как показано на Фиг. 5. Блок управления (9) состоит из рабочей станции, преобразователя интерфейсов и источников питания. К блоку управления может быть подключено несколько модульных систем тестирования (8). Взаимодействие между блоком управления (9) и модульными системами тестирования (8) осуществляется с использованием стандартизированных интерфейсов (например, RS-485).

Каждая модульная система тестирования (8) состоит из шести устройств тестирования (1) и одной объединительной платы (7), как показано на Фиг. 3 и 4. Модульная система тестирования (8) проверяет работоспособность тестируемых микросхем NAND-памяти, а также задает и измеряет требуемые временные параметры согласно программе тестирования. Объединительная плата (7) предназначена для организации двустороннего обмена данными между блоком управления (9) и устройствами тестирования (1), а также для преобразования интерфейсов (RS-485 - Ethernet).

Основные задачи управляющего микроконтроллера (4) в составе устройства тестирования (1) заключаются в следующем:

• управление ПЛИС (5), запуск процедур записи, чтения, стирания, реализация доступа к внутренним регистрам для настройки ПЛИС (5), чтение результатов и ошибок выполнения тестовых процедур;

• получение информации о работе микросхемы NAND-памяти, о степени завершенности запущенной процедуры тестирования, ошибках, возникших в ходе выполнения тестирования, статистики о времени выполнения отдельных команд микросхемой NAND-памяти;

• передача в блок управления (9) информации о ходе выполнения тестирования микросхемы NAND-памяти в случае работы под управлением блока управления (9) или отображение результатов на цифровых индикаторах (3) в случае работы в автономном режиме;

Также управляющий микроконтроллер (4) управляет питанием микросхем NAND-памяти с помощью программируемого преобразователя напряжения (6).

ПЛИС (5) в составе устройства тестирования (1) может работать в режимах «работа» или «отладка». Режим «работа» предназначен для функционального тестирования микросхемы NAND-памяти. В данном режиме ПЛИС (5) используется в качестве алгоритмического генератора шаблонов, реализующего запись и чтение данных в микросхемах NAND-памяти в соответствие с некоторым шаблоном (например, все "0", все "1", шахматный порядок). В режиме «отладка» осуществляется проверка корректной работы команд. В этом режиме ПЛИС (5) взаимодействует с выбранными микросхемами NAND-памяти и с конкретной страницей или блоком, или логическим элементом (LUN). Взаимодействие управляющего микроконтроллера (4) и ПЛИС (5) осуществляется по интерфейсу Serial Peripheral Interface (SPI), а обмен данными и управление путем обращения к внутренним регистрам ПЛИС (5). Внутренние регистры ПЛИС (5) позволяют сконфигурировать режимы работы системы тестирования, настроить параметры тестирования, процедуру обработки ошибок, в том числе условий прерывания выполнения команд тестирования, осуществить регистрацию результатов выполнения теста. ПЛИС (5) поддерживает асинхронный Single Data Rate (SDR) и синхронные Non-Volatile Double Data Rate (NV-DDR и NV-DDR2) интерфейсы взаимодействия с микросхемой NAND-памяти, выбор интерфейса определяется значением одного из регистров. Результаты взаимодействия ПЛИС (5) с микросхемой NAND-памяти и управляющим микроконтроллером (4), а также конфигурационные данные режима работы сохраняются во внутренних регистрах ПЛИС (5). Регистры ПЛИС (5) объединены в три группы:

1. Конфигурационные регистры, задающие режим работы в условиях тестирования: выбор микросхемы NAND-памяти для тестирования, настройка интерфейса микросхемы NAND-памяти, настройка обработчика ошибок и условия завершения тестирования и т.д.;

2. Информационные регистры, содержащие информацию, необходимую для корректной работы устройства тестирования (1), которую ПЛИС (5) получает входе обмена с управляющим микроконтроллером (4) и микросхемой NAND-памяти: максимальное время выполнения команд, список ошибок, определяющих условия завершения выполнения команды тестирования и т.д.;

3. Регистры, содержащие информацию о результатах выполнения тестовых операций и процедур: выбор микросхемы NAND-памяти для выполнения команд тестирования, тестового шаблона, режима работы системы тестирования и т.д.

Тестирование может выполняться как для однокристальных, так и для многокристальных (до 16 кристаллов) микросхем NAND-памяти различных типов, выполненных в корпусе типа BGA.

Для работы в автономном режиме необходимо, чтобы устройство тестирования (1) было отсоединено от объединительной платы (7). После этого устройство тестирования (1) подключается к питающему напряжению, а в BGA-сокеты (2) вставляются тестируемые микросхемы NAND-памяти. Затем производится нажатие кнопки запуска тестирования, расположенной на устройстве тестирования (1), после чего начинается выполнение функционального тестирования установленных микросхем NAND-памяти. Результаты каждого тестирования отображаются в виде кодов ошибки (или отсутствия ошибки) на цифровых индикаторах (3), расположенных рядом с каждым BGA-сокетом (2). Наличие управляющего микроконтроллера (4) в составе устройства тестирования (1) позволяет автономно выполнять процедуры тестирования без использования блока управления (9). Также автономность работы обеспечивается наличием цифровых индикаторов (3), на которых отображаются результаты тестирования. В данном режиме работы тестовые команды и конфигурационные данные для ПЛИС (5) должны быть записаны в память устройства тестирования (1).

Для работы под управлением блока управления (9) устройство тестирования (1) должно быть подключено к объединительной плате (7) в составе модульной системы тестирования (8). В этом случае тестовые команды и конфигурационные данные для ПЛИС (5) передаются в управляющий микроконтроллер (4) из блока управления (9) и задаются оператором с использованием установленного на рабочей станции программного обеспечения. По окончании тестирования результаты передаются обратно на рабочую станцию и выводятся на монитор.

Процедура тестирования микросхем NAND-памяти с помощью устройства тестирования (1) начинается с конфигурирования внутренних регистров ПЛИС (5), определяющих тип интерфейса памяти, скоростной режим, вид тестового шаблона. По сигналу с управляющего микроконтроллера (4) программируемый преобразователь напряжения (6) подает номинальное напряжение питания на микросхемы NAND-памяти. После этого запускается функциональное тестирование, в ходе которого производится запись и чтение тестовых шаблонов (например, все "0", все "1", шахматный порядок) и измерение временных характеристик микросхем NAND-памяти. В процессе тестирования управляющий микроконтроллер (4) опрашивает внутренние регистры ПЛИС (5) и получает информацию о результатах тестирования, ошибках выполнения тестовых процедур, степени завершенности запущенной процедуры, статистику о времени выполнения отдельных команд. Полученные данные в зависимости от режима работы устройства тестирования (1) отображаются на цифровых индикаторах (3) или передаются в блок управления (9) и отображаются в графическом интерфейсе программного обеспечения рабочей станции.

Библиография

[1] S. Liu and X. Zou, "QLC NAND study and enhanced Gray coding methods for sixteen-level-based program algorithms," Microelectronics J., vol. 66, pp.58-66, Aug. 2017.

[2] R. Yamashita et al., "11.1 A 512Gb 3b/cell flash memory on 64-word-line-layer BiCS technology," in 2017 IEEE International Solid-State Circuits Conference (ISSCC), 2017, pp.196-197.

[3] J.-W. Im et al., "7.2 A 128Gb 3b/cell V-NAND flash memory with 1Gb/s I/O rate," in 2015 IEEE International Solid-State Circuits Conference - (ISSCC) Digest of Technical Papers, 2015, pp. 1-3.

[4] H. Huang and R. Micheloni, "3D Multi-chip Integration and Packaging Technology for NAND Flash Memories," in 3D Flash Memories, Dordrecht: Springer Netherlands, 2016, pp. 261-279.

[5] Y. Wang, Y. Liu, M. Li, K. N. Tu, and L. Xu, "Interconnect Quality and Reliability of 3D Packaging," Springer, Cham, 2017, pp. 375-420.

[6] C.A. Papachristou, F. Martin, and M. Nourani, "Microprocessor based testing for core-based system on chip," in Proceedings 1999 Design Automation Conference (Cat. No. 99CH36361), pp. 586-591.

[7] M. Zhang, F. Wu, H. Huang, Q. Xia, J. Zhou, and C. Xie, "FPGA-based failure mode testing and analysis for MLC NAND flash memory," in Design, Automation & Test in Europe Conference & Exhibition (DATE), 2017, 2017, pp. 434-439.

[8] L. Sheng and W. Chao, "Testing system and method of Nand Flash based on Matlab," CN Patent application No. CN 108109670 A, 01.06.2018.

[9] F. Jianyun, F. Lingyan, and X. Jianhui, "NAND FLASH memory chip test system," CN Patent application No. CN 101727989 B, 27.11.2013.

[10] M. Gefen, "Semiconductor programming and testing method and apparatus," WO Patent application No. WO 2003003033 A2, 09.01.2003.

[11] W. He et al., "MT29F series NAND FLASH test aging system with customizable process," CN Patent application No. CN 106571166 A, 19.04.2017.

Реферат

Полезная модель относится к области тестирования интегральных микросхем NAND-памяти и представляет собой устройство тестирования на основе ПЛИС, с возможностью закрепления на объединительной плате модульной системы тестирования, которая имеет возможность подключения к блоку управления. Устройство тестирования представляет собой отдельную плату с управляющим микроконтроллером, ПЛИС, программируемыми преобразователями напряжения, разъемными BGA-сокетами и цифровыми индикаторами. Устройство тестирования позволяет одновременно и независимо тестировать множество микросхем NAND-памяти при операциях чтения, записи и стирания данных, в том числе в условиях повышенных и пониженных температур функционирования. Устройство тестирования может использоваться в составе модульной системы тестирования, состоящей из объединительной платы и нескольких устройств тестирования. Модульная система тестирования может подключаться к блоку управления, состоящему из рабочей станции, преобразователя интерфейсов и источников питания. Особенностью полезной модели является возможность работы устройств тестирования как в составе модульной системы под управлением блока управления, так и в автономном режиме без внешнего управления с выводом результатов тестирования на цифровые индикаторы. 5 ил.

Комментарии