Устройство тестирования многокристальной микросхемы - RU199432U1

Код документа: RU199432U1

Чертежи

Описание

Область техники

Полезная модель относится к области тестирования многокристальных интегральных микросхем, а более конкретно к устройствам электрического и функционального тестирования микросхем, выполненных по методу монтажа «корпус на корпусе» (англ. Package on package, сокр. РоР) или «система в корпусе» (англ. System in Package, сокр. SiP) и содержащих в своем составе микропроцессор и микросхему памяти.

Предшествующий уровень техники

Электрическое и функциональное тестирование микросхем является важным производственным этапом. В процессе производства микросхем могут возникать различные дефекты в электрической части изделия, влияющие на его функциональность. Например, на этапе пайки кристалла методом монтажа перевернутого кристалла (англ. Flip-Chip) могут образовываться дефекты: перемычки между соседними шариковыми выводами; не пропаянные соединения кристалла с подложкой; отсутствие контакта с подложкой в результате углового и линейного смещения кристалла. При разварке кристаллов методом проволочной распайки (англ. Wire Bonding) могут формироваться недостаточно прочные соединения, которые в процессе заливки микросхем компаундом на этапе герметизации в пластиковые корпуса могут обрываться или замыкаться друг с другом.

Для определения качества сборки каждый образец проходит электрическое и функциональное тестирование. При электрическом тестировании проверяется целостность цепей и отсутствие коротких замыканий, при функциональном - проверка собранных микросхем на выполнение заданной функциональности и на соответствие параметрам, которые заложены в спецификации электронного устройства.

Для целей тестирования используется различное оборудование. Например, для электрического тестирования электронных изделий на стадии производства применяют системы с тестовыми адаптерами типа «поле контактов» (англ. bed-of-nails). Система предполагает наличие соединительного устройства с подпружиненными контактами, размещаемыми напротив контрольных точек на тестируемой электронной микросхеме. В процессе тестирования обеспечивается касание подпружиненных контактов со всеми узлами тестируемой микросхемы.

Недостатком, ограничивающим применение такого оборудования, является необходимость изготовления тестовых адаптеров для каждого электронного изделия, обеспечивающих сопряжение проверяемого изделия и установки тестирования. Это приводит к дополнительным трудозатратам и потерям времени при освоении производства новых электронных изделий. Кроме того, такое оборудование является дорогостоящим. В качестве примера оборудования с тестовыми адаптерами типа «поле контактов» можно привести устройство тестирования печатных плат, содержащее пресс-пластину, верхнюю пластину, игольчатую пластину, опорную пластину, зонд и пьедестал, причем верхняя пластина установлена в нижней части пресс-пластины [1].

Известно оборудование для тестирования электронных изделий, основанное на применении подвижных или «летающих» зондов (англ. Flying Probe Tester, сокр. FPT). Оборудование такого рода имеет тестовую головку (обычно несколько), снабженную зондами и приводами по осям X, Y и Z. Тестовые головки перемещаются над тестируемым электронным изделием. Зонды вступают в контакт с переходными отверстиями и контактными площадками электронного изделия. Таким образом, обеспечивается последовательный доступ к контрольным точкам тестируемого изделия.

Недостатком такого оборудования является сложность конструкции, требующая высокого уровня обслуживания. Кроме того, такое оборудование является дорогостоящим.

Примером оборудования с применением «летающих» зондов является устройство тестирования, содержащее головку с зондом, две оси X, две оси Y и две оси Z, снабженные приводами и обеспечивающими перемещение головки с зондом в пространстве [2].

В целом системы с тестовыми адаптерами типа «поле контактов» или оборудование с «летающими» зондами предназначены для крупносерийного производства и в условиях мелкосерийного производства не могут быть использованы ввиду их стоимости, сложности обслуживания и содержания. В производственных линиях такие установки являются наиболее загруженными.

Кроме того, следует также отметить то, что при разработке и отладке производства новых электронных изделий, собираемых по методу монтажа РоР или SiP, одним из этапов является прототипирование. При этом изготавливается опытный образец - макет будущей системы на корпусе, в котором некоторые основные функциональные компоненты (кристаллы) частично или полностью заменены на аналогичные по технологии и параметрам монтажа. На таких опытных образцах проводится и отлаживается весь технологический процесс, включая тестирование микросхем, маркировку, сканирование и упаковку. Для определения качества сборки каждый образец проходит электрическое и функциональное тестирование. Затем, для выявления ошибок технологического процесса, дефектные образцы подвергаются структурному анализу с помощью методов рентгеновского просвечивания, сканирующей акустической микроскопии, инфракрасной термографии и др. Выделение для этих целей машинного времени систем с тестовыми адаптерами типа «поле контактов» или оборудования с «летающими» зондами на практике проблематично, так как оно загружено на основной производственной линии.

Для мелкосерийного производства и прототипирования применяются относительно более простые устройства или устройства ручного типа. Например, известно устройство тестирования микросхем NAND-памяти на основе программируемой логической интегральной схемы (ПЛИС), выполненное с возможностью подключения к рабочей станции через преобразователь интерфейсов и к источнику питания, а также с возможностью закрепления на объединительной плате, содержащей разъемные BGA-сокеты для микросхем NAND-памяти, поддерживающих стандарт ONFI, и представляющее собой единую плату, на которой установлен управляющий микроконтроллер, алгоритмический генератор тестовых шаблонов на основе ПЛИС, цифровые индикаторы для вывода результатов тестирования [3].

Описанное устройство предназначено для тестирования NAND-памяти. Количество выводов NAND-памяти, как правило, значительно меньше, чем количество выводов микропроцессоров. Поэтому если тестируемое микроэлектронное устройство в своем составе будет иметь микропроцессор, то применение предложенного технического решения приведет к значительному усложнению конструкции единой платы, процесса ее изготовления, увеличению количества брака при изготовлении, а также уменьшению надежности и долговечности устройства в целом.

Конструкция единой платы усложняется, так как для тестирования микросхемы, имеющей в составе микропроцессор, потребуется микроконтроллер с большим количеством выводов, и для разведения всех токопроводящих дорожек необходимо увеличить количество слоев единой платы, уменьшить ширину электропроводящих дорожек и расстояний между ними. Увеличение брака при изготовлении устройства тестирования обусловлено повышением плотности монтажа компонентов на единой плате вследствие близко расположенных друг к другу токопроводящих дорожек.

Уменьшение надежности и долговечности устройства обусловлено следующим. Во-первых, многослойная подложка в процессе эксплуатации подвержена расслоению. Во-вторых, чем меньше ширина токопроводящей дорожки, тем слабее адгезия между материалом дорожки и основой (текстолитом), а, следовательно, в процессе применения устройства может произойти обрыв дорожки даже при относительно небольшом физическом воздействии, например, при падении устройства и деформации единой платы. Кроме того, уменьшение ширины токопроводящей дорожки приводит к увеличению сопротивления, а следовательно, и нагреву дорожки, что также в процессе эксплуатации может привести к ее разрушению. Следует также отметить, что чем меньше расстояние между токопроводящими дорожками, тем больше повышается вероятность их пробоя в процессе эксплуатации.

Наиболее близким аналогом заявляемого технического решения, выбранным в качестве прототипа, является устройство тестирования микросхем, выполненных по методу монтажа SiP, включающее печатную плату с установленными разъемом для подключения тестируемой многокристальной микросхемы, средствами индикации результатов тестирования, кнопками управления устройством, микропроцессорную плату, закрепленную на обратной стороне печатной платы [4].

Недостатком устройства является сложность конструкции печатной платы и процесса ее изготовления, относительно низкая надежность и долговечность устройства. Это обусловлено тем, что для тестирования микросхем, имеющих в составе микропроцессор, потребуется использование печатной платы с большим количеством проводящих слоев (от шести и более), относительно небольшой шириной токопроводящих дорожек и расстоянием между ними.

Кроме того, данное устройство не является универсальным. Возможность проведения тестирования многокристальной микросхемы определяется конструкцией микропроцессорной платы, т.е. изменение конструкции тестируемой многокристальной микросхемы потребует замены конструкции микропроцессорной платы.

Раскрытие сущности полезной модели

Техническим результатом, на достижение которого направлена заявляемая полезна модель, является упрощение конструкции печатной платы, повышение надежности и долговечности устройства тестирования, а также снижение брака и трудоемкости при его изготовлении. Кроме того, возникает дополнительный технический результат, заключающийся в том, что обеспечивается возможность тестирования различных многокристальных микросхем без необходимости внесения изменений в конструкцию устройства, т.е. обеспечивается универсальность устройства.

Технический результат достигается тем, что устройство тестирования многокристальной микросхемы, содержащей микропроцессор и кристалл памяти, включает печатную плату с установленными разъемом для подключения тестируемой многокристальной микросхемы, основным микроконтроллером, выполненным с возможностью взаимодействия с персональным компьютером и электрически связанный с разъемом для подключения тестируемой многокристальной микросхемы, средствами индикации результатов тестирования, кнопками управления устройством, дополнительным микроконтроллером, причем дополнительный микроконтроллер электрически связан с основным микроконтроллером и разъемом для подключения тестируемой многокристальной микросхемы.

Упрощение конструкции печатной платы обусловлено тем, что применение основного и дополнительного микроконтроллера позволяет развести токопроводящие дорожки с меньшим необходимым количеством слоев при тестировании микросхем, содержащих в своем составе микропроцессор, а также отказаться от дополнительных коммутирующих устройств. По этой же причине достигается снижение трудоемкости изготовления устройства.

Повышение надежность устройства и его долговечности объясняется тем, что благодаря применению основного и дополнительного микроконтроллера имеется возможность выполнять токопроводящие дорожки при их разведении с большей толщиной и расстоянием между ними.

Снижение брака при изготовлении объясняется снижением плотности монтажа элементов на печатной плате и уменьшение их количества, что уменьшает вероятность неправильной установки компонента. Снижение плотности монтажа также объясняется возможностью выполнения токопроводящих дорожек с относительно большей шириной и расстоянием между друг другом.

Так как контакты разъема для подключения тестируемой многокристальной микросхемы соединены с линиями ввода-вывода основного и дополнительного микроконтроллеров, имеется возможность смены алгоритма тестирования, что позволяет осуществить электрическое и функциональное тестирование различных конструкций многокристальных микросхем.

Краткое описание чертежей

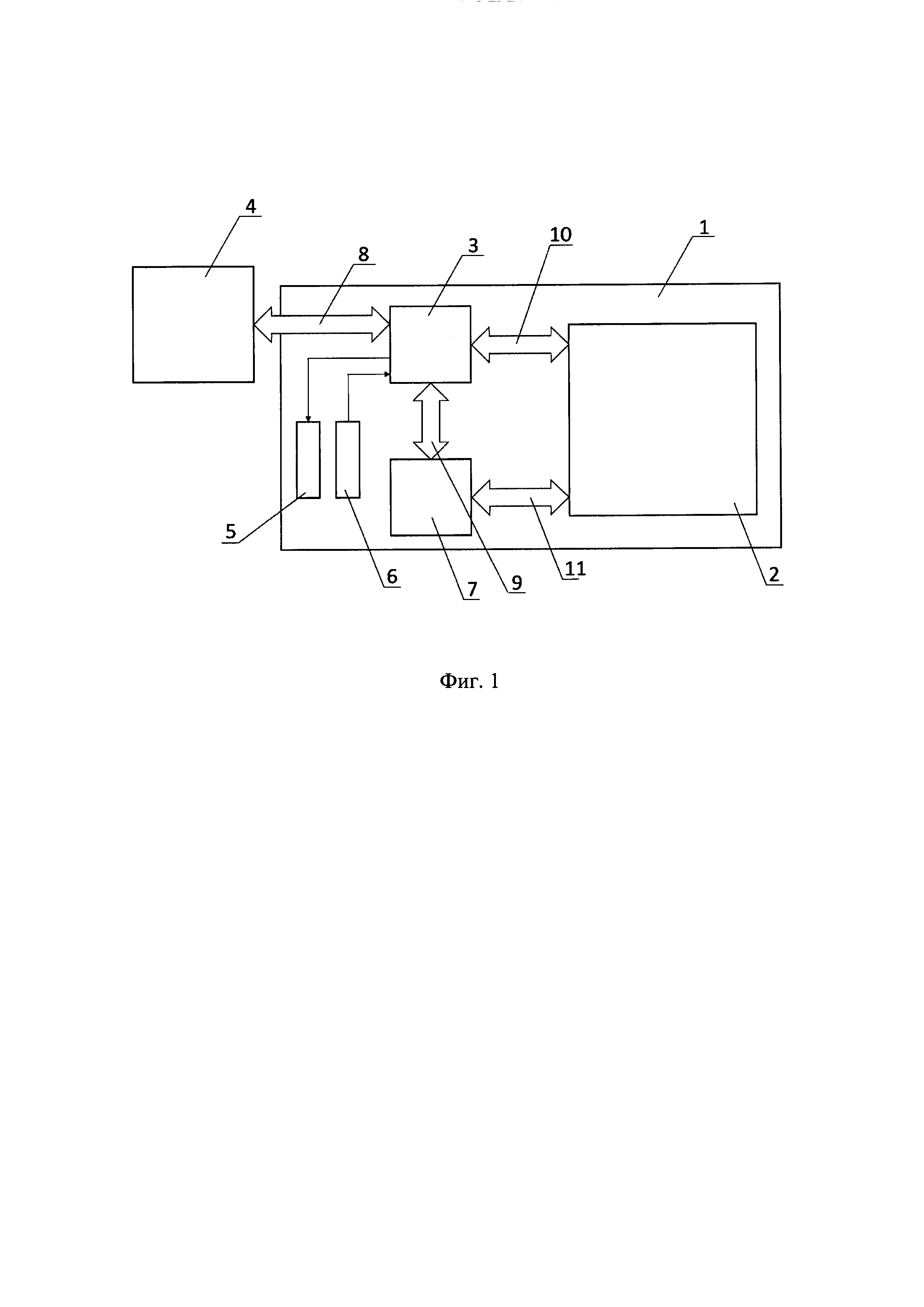

Реализация технического решения пояснена на схеме, где: фиг. 1 -схема устройства тестирования.

Осуществление технического решения

Устройство тестирования многокристальных микросхем включает печатную плату 1 с установленными разъемом для подключения тестируемой многокристальной микросхемы 2, основным микроконтроллером 3, выполненным с возможностью взаимодействия с персональным компьютером 4 и электрически связанный с разъемом для подключения тестируемой многокристальной микросхемы 2, средствами индикации результатов тестирования 5, кнопками управления устройством 6, дополнительным микроконтроллером 7.

В общем виде устройство выполнено в виде печатной платы 1 с установленными на ней электронными компонентами и электрическими соединителями. Основные элементы устройства тестирования, используемые при работе с ним, расположены на верхней стороне печатной платы 1.

Разъем для подключения тестируемой многокристальной микросхемы 2 представляет собой, например, сокет для микросхемы в BGA корпусе.

Средства индикации результатов тестирования 5 выполнены в виде двух светодиодов зеленого и красного цветов. Светодиод зеленого цвета предназначен для индикации успешно завершившегося теста, светодиод красного света - неудачно завершившегося теста.

Кнопки управления устройством 6 включают кнопку запуска теста и кнопку перезагрузки устройства.

Питание устройства осуществляется по интерфейсу USB 8 от персонального компьютера 4. Для этого на печатной плате 1 смонтирован разъем PWR/IO.

Микроконтроллеры 1 и 7 предназначены для выполнения процедуры тестирования. В качестве основного микроконтроллера 1 и дополнительного микроконтроллера 7 может использоваться, например, контроллер STM32F429BIT. Дополнительный микроконтроллер 7 электрически связан с основным микроконтроллером 3 и разъемом для подключения тестируемой многокристальной микросхемы 2. Электрическая связь 9 между микроконтроллерами 3 и 7 выполнена по интерфейсу SPI (Serial Peripheral Interface). Таким образом, часть выводов микроконтроллеров 3 и 7 связаны между собой, а оставшиеся свободные выводы имеют соединения (10 и 11) с контактными площадками разъема для подключения тестируемой многокристальной микросхемы 2.

Микроконтроллеры 3 и 7 имеют встроенную программу для ЭВМ, обеспечивающую: взаимодействие устройства тестирования с персональным компьютером 4 через интерфейс USB 8, а именно получение настроек, запуск теста, передачу результатов теста; выполнение электрического и функционального тестирования согласно последним полученным настройкам при нажатии на кнопку запуска теста или команды с персонального компьютера 4; управление средствами индикации результатов тестирования 5 (включение зеленого индикатора при успешно пройденном тесте или красного при неудачном).

Электрическое тестирование встроенная программа для ЭВМ осуществляет путем проверки входных/выходных сигнальных линий на обрыв и замыкание. Для этого производится последовательное тестирование всех связанных пары входов и выходов тестируемой микросхемы, путем установки сигнала на входных и считывания на выходных линиях микросхемы. Логической «1» на одной входной линии микросхемы соответствует только одна логическая «1» на связанной с ней выходной линии и логические «0» на остальных выходных линиях микросхемы. Отсутствие логической «1» на связанном выходе определяется как обрыв сигнальных линий. Наличие логической «1» на одном или нескольких несвязанных выходах определяется как замыкание сигнальных линий.

Встроенная программа для ЭВМ обеспечивает возможность проведения функционального тестирования кристаллов памяти тестируемой микросхемы. Взаимодействие с кристаллами памяти тестируемой микросхемы производится по SPI-интерфейсу. В рамках функционального тестирования кристаллов памяти проверяется наличие ошибок при выполнении операции чтения идентификатора микросхемы памяти и наличие ошибок при операции записи/чтения заданных шаблонов.

Кроме того, встроенная программа для ЭВМ поддерживает получение по интерфейсу USB 8 карты выводов сокета для тестируемой микросхемы и тестовых сценариев. Карта выводов и тестовые сценарии сохраняются в энергонезависимой памяти микроконтроллеров 3 и 7.

Для управления и взаимодействия с устройством тестирования на персональном компьютере 4 устанавливается программа для ЭВМ (далее ПОЭВМ). ПОЭВМ обеспечивает: детектирование подключения устройства тестирования по USB интерфейсу 8; конфигурирование тестов устройства тестирования; запуск теста микросхемы на устройстве и отображение хода процедуры тестирования; отображение результатов теста и запись их в текстовый файл на персональном компьютере 4.

Конфигурирование тестов производится следующим образом: подгружается текстовый файл с настройками, настройки преобразуются цифровой код и передаются в устройство тестирования (микроконтроллеры 3 и 7). В текстовом файле настроек может содержаться: конфигурация электрических тестов (указываются пары ног микросхемы вход-выход, где будет установлена логический «1» и должна будет считываться «1»); конфигурация функциональных тестов (здесь указываются ноги микросхемы на которые выведены контакты микросхемы памяти, идентификатор микросхемы, шаблон для записи в микросхему памяти).

Каждой конфигурации присваивается свой идентификатор. При подключении устройства тестирования к персональному компьютеру 4 на экране посредством интерфейса ПОЭВМ отображается идентификатор конфигурации, загруженный в устройство тестирования.

Устройство работает следующим образом. В разъем 2 подключают многокристальную микросхему. Для включения устройства тестирования необходимо подключить его к USB персонального компьютера 4. После включения устройство тестирования готово к тестированию многокристальной микросхемы по последней успешно загруженной в микроконтроллеры 7 и 3 сценарию тестирования.

Пользователь посредством ПОЭВМ через интерфейс USB 8 может загрузить новые настройки в основной микроконтроллер 3 и дополнительный микроконтроллер 7. Далее при нажатии кнопки запуска теста на устройстве тестирования или путем команды с персонального компьютера 4 дается команда начала тестирования.

Встроенная программа для ЭВМ осуществляет проверку целостности электрических цепей многокристальной микросхемы (электрическое тестирование). Далее встроенная программа для ЭВМ производит функциональное тестирование микросхемы памяти.

В процессе тестирования на персональном компьютере 4 посредством интерфейса ПОЭВМ отображается тестируемая пара выводов и есть ли замыкания на другие выводах многокристальной микросхемы, или отображается процесс записи данных на кристалл памяти многокристальной микросхемы.

Многокристальная микросхема, которая содержит в своем составе микропроцессор и кристалл памяти, может иметь более 200 выводов. Поэтому для тестирования таких многокристальных микросхем потребуется использование микроконтроллера, у которого количество выводов будет более 200. Для разведения такого количества выводов от микропроцессора до разъема для подключения тестируемой многокристальной микросхемы и других функциональных элементов, расположенных на печатной плате, необходимо использовать многослойную печатную плату. Это приводит к увеличению сложности конструкции печатной платы и процесса ее изготовления, снижению надежности и долговечности устройства. Кроме того, сам микроконтроллер с большим количеством выводов является сложным и дорогостоящим электронным изделием.

Решение описанной проблемы осуществляется путем использования двух более простых микроконтроллеров, у которых количество выводов менее 200. Например, контроллер STM32F429BIT, приведенный в качестве примера использования основного микроконтроллера 1 и дополнительного микроконтроллера 7 имеет 216 выводов, 168 из которых составляют линии ввода-вывода. Использование двух более простых микроконтроллеров позволяет развести токопроводящие дорожки с использованием относительно меньшего количества слоев печатной платы, а также отказаться от дополнительных коммутирующих устройств. При тестировании микросхемы с количеством выводов примерно до 300 применение двух микроконтроллеров позволяет использовать четырехслойную печатную плату и реализовать весь функционал, необходимый для проведения электрического и функционального тестирования.

Кроме того, ввиду того что контакты разъема для подключения тестируемой многокристальной микросхемы соединены с линиями ввода-вывода основного и дополнительного микроконтроллеров, имеется возможность смены алгоритма тестирования. Контакты разъема для подключения тестируемой многокристальной микросхемы могут быть программно сконфигурированы под различные конфигурации микросхем. Это позволяет осуществить электрическое и функциональное тестирование различных многокристальных микросхем без изменения конструкции устройства.

Таким образом, заявляемая полезная модель обеспечивает упрощение конструкции печатной платы, повышение надежности и долговечности устройства тестирования, а также снижение брака и трудоемкости при изготовлении устройства.

Библиография

1. Патент CN 103063959 «Bed-of-nails tool for detecting circuit board», опубликован 24.04.2013 г.

2. Патент CN 103176121 «Flying probe tester», опубликован 16.09.2015 г.

3. Патент на полезную модель RU 194203 «Устройство тестирования микросхем NAND-памяти на основе ПЛИС», опубликован 03.12.2019 г.

4. Заявка РСТ WO 2018144561 «Automatic test equipment method for testing system in a package devices», опубликована 09.08.2018 г.

Реферат

Устройство тестирования многокристальной микросхемы, содержащей микропроцессор и кристалл памяти, включает печатную плату с установленными разъемом для подключения тестируемой многокристальной микросхемы, основным микроконтроллером, выполненным с возможностью взаимодействия с персональным компьютером и электрически связанный с разъемом для подключения тестируемой многокристальной микросхемы, средствами индикации результатов тестирования, кнопками управления устройством. Устройство снабжено дополнительным микроконтроллером. Дополнительный микроконтроллер электрически связан с основным микроконтроллером и разъемом для подключения тестируемой многокристальной микросхемы.Полезная модель обеспечивает упрощение конструкции печатной платы, повышение надежности и долговечности устройства тестирования, а также снижение брака и трудоемкости при его изготовлении.

Комментарии