Способ и устройство для определения параметров матрицы рассеяния испытуемого устройства преобразования частоты - RU2634733C2

Код документа: RU2634733C2

Чертежи

Описание

Изобретение относится к способу и устройству для определения параметров матрицы рассеяния испытуемого устройства преобразования частоты.

Для описания электрических свойств частотно-преобразующего элемента, предпочтительно смесителя, определяют параметры матрицы рассеяния частотно-преобразующего элемента с помощью схемного анализатора. На основе сопоставлений ошибок в портах испытуемого устройства, или соответственно схемного анализатора, а также неидеального поведения схемного анализатора, системные ошибки при сравнении с соответствующими правильно измеренными значениями накладываются на зарегистрированные измеренные значения.

Эти системные ошибки должны быть определены заранее при калибровке, а затем использованы для компенсации системных ошибок измеренных значений, зарегистрированных для определения точно измеренных значений. Для этого могут быть использованы обычные одно- или двухпортовые модели ошибок, например известны методы семи, девяти или десяти параметров. Ниже, в качестве примера показано использование метода семи параметров, либо соответственно использование двух методов трех и четырех параметров.

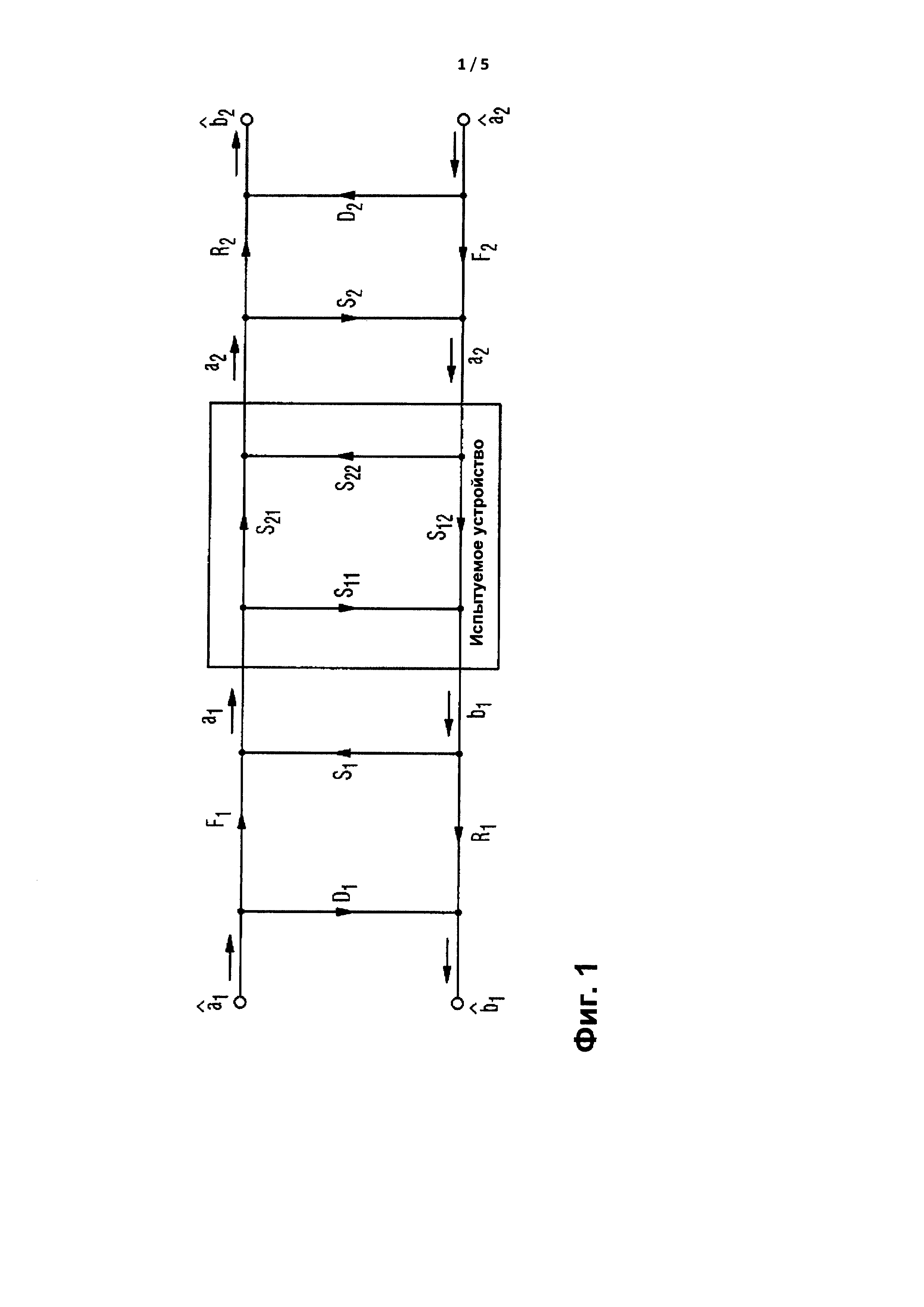

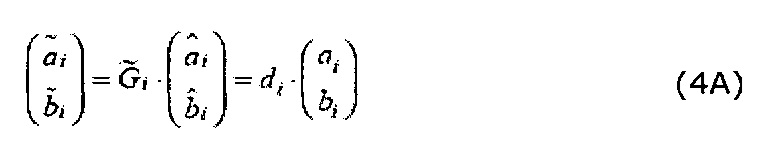

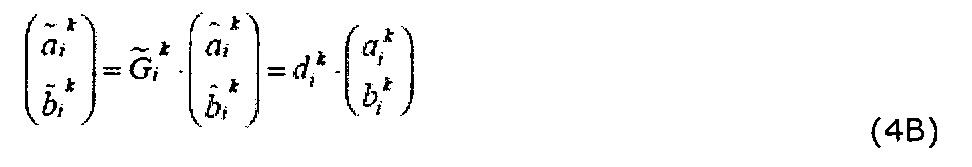

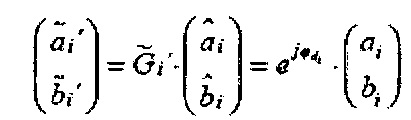

В этом случае, системными ошибками, определяемыми для каждого подлежащего измерению порта i испытуемого устройства преобразования частоты, являются направленность Di, согласование источника Si, прямая трассировка Fi и корреляция отражений Ri, показанные на фиг. 1 для испытуемого устройства с 2-мя портами. Соотношение между измеренными значениями входной волны или соответственно выходной волны , и точным значением входной ai или соответствующей выходной волны bi определенных системных ошибок получено по формуле (1) с помощью матрицы Gi системных ошибок, включающей в себя отдельные измеренные системные ошибки по формуле (2)

Значения входных/выходных волн представляют собой частотно-зависимые сигналы и, для простоты, именуются ниже входными/выходными сигналами.

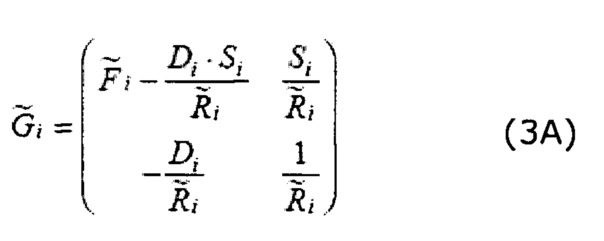

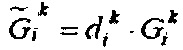

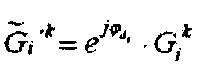

Матричные элементы матрицы определенных системных ошибок, отличные, за исключением неизвестного комплексного коэффициента di, от точных системных ошибок соответствующего порта i, получают исключительно при измерении основной гармоники по формуле (3А), с помощью матрицы Gi точных системных ошибок посредством взвешивания с неизвестным комплексным коэффициентом di. При измерении высших гармоник и интермодуляционных помех при частоте k матрицу определенных системных ошибок согласно формуле (3B) получают из матрицы точных системных ошибок для высших гармоник и интермодуляционных помех при частоте k посредством взвешивания с неизвестным комплексным коэффициентом di

При исследовании устройств, не обладающих способностью преобразования частоты, параметры ошибок в двухпортовой модели ошибок, каждый из которых получен при двухпортовой калибровке, последовательно сопоставляют друг с другом, и зависят только от постоянной, которая соответственно одинакова для обоих портов. Неизвестный комплексный коэффициент di одинаков для каждого порта i испытуемого устройства. Так как каждый параметр матрицы рассеяния испытуемого устройства получен как отношение двух сигналов - входного и выходного - одного и того же порта или двух разных портов, этот неизвестный комплексный коэффициент di исключен из последнего и соответственно не представляет никакой проблемы.

При исследовании устройств преобразования частоты с различной частотой, а, следовательно, и разным фазовым соотношением между двумя подлежащими измерению портами, амплитудную составляющую |di| неизвестного комплексного коэффициента di определяют с помощью калибровки уровня в обоих портах и учета при компенсации системной ошибки. При этом амплитудная составляющая |di| неизвестного комплексного коэффициента di различна для каждого порта вследствие различия частот. Для определения фазовой составляющей

Использование при калибровке фазовой ошибки опорной фазы, соответственно эталона фазы, как например, в патенте США 6,292,000 В1, как правило, ограничивает диапазон частот и частотный интервал выполняемой калибровки фазы. Кроме того, качество определения фазовой составляющей

Таким образом, задача настоящего изобретения состоит в создании способа и устройства компенсации системной ошибки при электрической характеризации испытуемого устройства преобразования частоты, обеспечивающих высокую точность измерений при малых затратах.

Для решения поставленной задачи предложены способ определения параметров матрицы рассеяния испытуемого устройства преобразования частоты, основные признаки которого заявлены в пункте 1 формулы изобретения, и устройство для определения параметров матрицы рассеяния испытуемого устройства преобразования частоты, основные признаки которого заявлены в пункте 12 формулы изобретения. Предпочтительные технические решения раскрыты в каждом зависимом пункте формулы.

Согласно предложенному способу, соответственно определяют соответствующие системные ошибки каждого подлежащего измерению порта испытуемого устройства преобразования частоты, и соответственно измеряют каждый входной или соответственно выходной сигналы подлежащего измерению порта испытуемого устройства преобразования частоты, все еще содержащие системные ошибки. Посредством взвешивания каждого измеренного входного или соответственно выходного сигналов с системной ошибкой отдельных подлежащих измерению портов испытуемого устройства преобразования частоты с соответствующими определенными системными ошибками, и определяют соответствующие входной или соответственно выходной сигналы со скорректированной системной ошибкой, которые все еще содержат амплитуду и неопределенность фазы неизвестного коэффициента. По входному или соответственно выходному сигналам со скорректированной ошибкой отдельных подлежащих измерению портов испытуемого устройства преобразования частоты определяют его параметры матрицы рассеяния.

В частности для компенсации фазовой погрешности в определенных системных ошибках отдельных подлежащих измерению портов испытуемого устройства преобразования частоты, фазы сигнала, возбуждающего испытуемое устройство, согласно изобретению инициализированы одинаковым образом при каждом измерении. Это обеспечивает, как более подробно будет показано ниже, удаление фазовой погрешности из вычисленных таким образом параметров отражения испытуемого устройства преобразования частоты.

Кроме того, фазу локального сигнала осциллятора для испытуемого устройства преобразования частоты предпочтительно инициализируют фазокогерентным способом по отношению к фазе сигнала возбуждения при каждом измерении. Это обеспечивает наличие соответственно идентичной фазы во время инициализации на всех трех портах испытуемого устройства преобразования частоты.

И, наконец, фазы сигналов осциллятора для отдельных смесителей в отдельных трактах измерения сигналов предпочтительно инициализируют фазокогерентным способом по отношению к фазе сигнала возбуждения, так что во время инициализации также получают идентичную фазу в детекторах на выходе отдельных трактов измерения сигналов.

Амплитудная составляющая неизвестного комплексного коэффициента di в отдельных коэффициентах матрицы Gi определенных системных ошибок предпочтительно определяют посредством калибровки уровня.

Несмотря на то что эти меры обеспечивают возможность компенсации амплитудных составляющих и, одновременно, фазовых составляющих параметров отражения испытуемого устройства преобразования частоты, предпочтительно только амплитудные составляющие компенсируют в параметрах передачи испытуемого устройства. Параметры передачи испытуемого устройства преобразования частоты продолжают вносить фазовую погрешность. Однако, при рассмотрении фактической величины параметров передачи неопределенность фазы не учитывают.

Для выполнения фазокогерентной инициализации сигнала возбуждения и локальных сигналов осциллятора при каждом отдельном измерении, соответствующие генераторы сигналов, которые соответственно генерируют сигнал возбуждения или локальный сигнал осцилятора, предпочтительно настроены в соответствии с принципом прямого цифровогосинтеза (DDS) или как осцилляторы с числовым программным управлением. Для этого каждый генератор содержит по меньшей мере один буфер, значения фазы синусоидального сигнала которого эквидистантно разнесены во времени.

Кроме того, может быть использован генератор синхронизирующих импульсов, выполненный с возможностью формирования синхронизирующего сигнала, подаваемого на буферы генераторов сигналов, и служащий синхронизированным выходом отдельных значений фаз синусоидального сигнала на выходе соответствующего буфера.

Блок высвобождения предпочтительно выполнен с возможностью генерирования сигнала инициализации буферов генераторов сигналов, подаваемого на буферы для конечного выхода идентичного значения фазы на выходе соответствующего буфера при следующем синхронизирующем импульсе синхронизирующего сигнала, следующего после инициализации.

Если генератором сигналов служит цифровой генератор прямого синтеза, значения фаз, которые выводятся с синхронизирующим импульсоми синхронизирующего сигнала на выходе соответствующего буфера соответственно предпочтительно подают на аналого-цифровой преобразователь, расположенный после соответствующих буферов, и выполенный с возможностью генерирования аналогового сигнала, соответствующего дискретным значениям фаз во время отдельных синхронизирующих импульсов. Этот аналоговый сигнал, в свою очередь, может быть предпочтительно выдан в виде опорного сигнала каждого генератора сигналов, работающего по принципу прямого цифрового синтеза, на фазорегулятор, на выходе которого генерирован сигнал возбуждения, или соответственно локальный сигнал осциллятора.

Вследствие нелинейной передаточной характеристики испытуемого устройства преобразования частоты, в частности смесителя, при основной гармонике соответственно входного и выходного сигналов на отдельных портах испытуемого устройства преобразования частоты, высшие гармоники и интермодуляционные помехи входного и выходного сигналов соответственно в этих портах возникают при других частотах. В другом варианте реализации изобретения, параметры матрицы рассеяния испытуемого устройства преобразования частоты дополнительно определяют при частотах, при которых возникают высшие гармоники и интермодуляционные помехи входного и выходного сигналов соответственно в отдельных портах испытуемого устройства. В случае дополнительных частот определение параметров матрицы рассеяния выполняют аналогичным образом по входному и выходному сигналам со скорректированной системной ошибкой соответствующих портов испытуемого устройства преобразования частоты.

Ниже приведено более подробное объяснение вариантов реализации предложенного способа и устройства для определения параметров матрицы рассеяния испытуемого устройства преобразования частоты в качестве примера со ссылкой на прилагаемые чертежи.

На фиг. 1 показаны две однопортовые модели ошибок испытуемого двухпортового устройства;

на фиг. 2 показана принципиальная схема варианта реализации устройства для определения параметров матрицы рассеяния испытуемого устройства преобразования частоты согласно изобретению;

на фиг. 3 показана часть принципиальной схемы варианта реализации устройства для определения параметров матрицы рассеяния испытуемого устройства преобразования частоты согласно изобретению;

на фиг. 4 показана блок-схема варианта реализации способа определения параметров матрицы рассеяния испытуемого устройства преобразования частоты согласно изобретению;

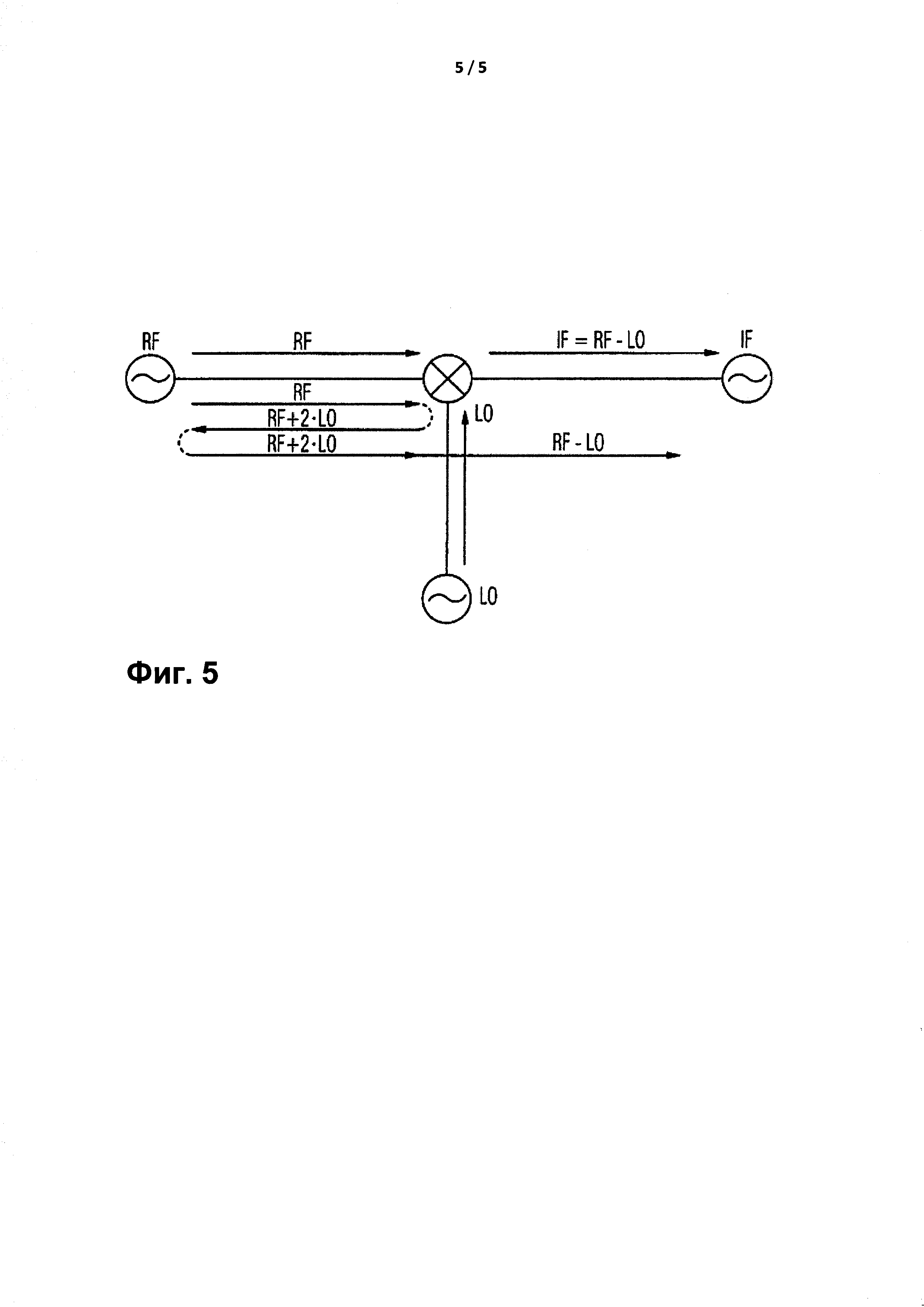

на фиг. 5 показаны примеры спектральных составляющих, возникающих соответственно в отдельных портах смесителя.

Ниже приведено математическое обоснование, необходимое для понимания изобретения, представленное на основе математических зависимостей.

Взвешивание входного и выходного сигналов

При высших гармониках и интермодуляционных помехах с частотой k, входной и выходной сигналы

Посредством калибровки уровня амплитудная составляющая |di| неизвестного комплексного коэффициента di, может быть определена и учтена в формуле (4). Соответственно в случае измерения только основной гармоники, начиная с формулы (4), получают математическую зависимость, зависящую теперь только от фазы

При измерении высших гармоник и интермодуляционных помех с частотой k, с учетом оптимизированной по уровню матрицы

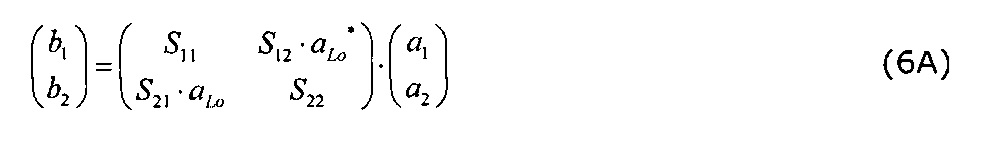

Определяемые параметры S матрицы рассеяния испытуемого устройства преобразования частоты, предпочтительно смесителя, могут быть получены по формуле (6А). Амплитуда |aLo| локального сигнала aLo осциллятора регулируют с возможностью получения ее масштабированного значения |aLo|=1

Параметры S матрицы рассеяния смесителя в режиме зеркального отражения получают по формуле (6В)

В дальнейшем будут рассмотрены смесители по формуле (6А). Однако изобретение также относится и к смесителям, работающим в режиме зеркального отражения. В частности, приведенное ниже описание ограничено основными гармониками. Распространение на высшие гармоники будет рассмотрено ниже.

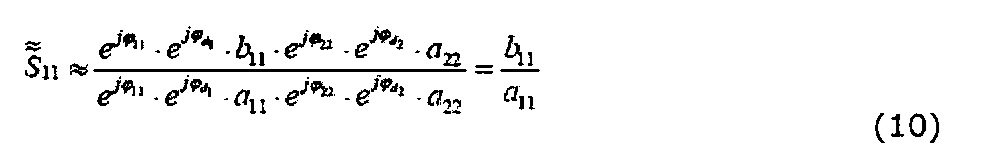

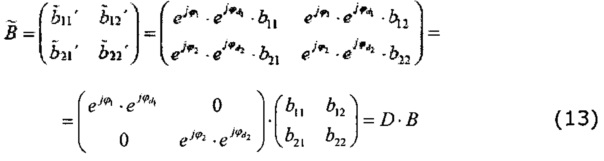

Параметры S матрицы рассеяния испытуемого устройства преобразования частоты могут быть определены соответственно по формуле (7) по входному и выходному сигналам в одном из двух отдельных подлежащих измерению портах испытуемого устройства преобразования частоты соответственно возбуждения указанного устройства по матричным элементам матрицы А, содержащей соответственно входные сигналы, и матрицы В, содержащей соответственно выходные сигналы. Каждым матричным элементом aij или bij является соответственно входной или выходной сигнал каждого порта i в случае возбуждения в порту j испытуемого устройства преобразования частоты

На первом этапе, измеренные параметры или соответственно параметры со скорректированной системной ошибкой матрицы рассеяния испытуемого устройства преобразования частоты получают соответственно с помощью генератора невоспроизводимых фазных сигналов.

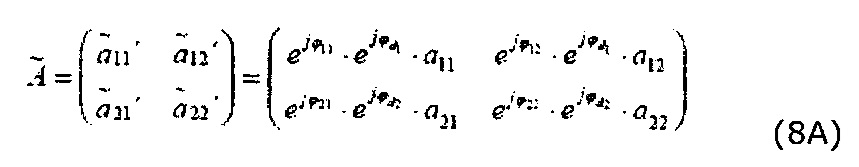

Если фаза генератора сигналов не инициализирована с одинаковой фазой при каждом измерении и если фазовое искажение в каждом отдельном тракте измерения сигнала между соответствующим устройством сопряжения и соответствующим регистратором неизвестно, то на основании формулы (8А) или (8В) с учетом формулы (4) получают с каждом случае соотношение между входным и выходным сигналами

При использовании генератора невоспроизводимых фазных сигналов измеренные или соответственно параметры

Согласно формуле (9) точные параметры S матрицы рассеяния и параметры

При приближенных значениях b12=a12=0, приближенно выраженный параметр

Аналогично, при b12=a12=0, приближенно выраженный параметр

Аппроксимация параметра

На втором этапе, параметры матрицы рассеяния испытуемого устройства преобразования частоты теперь получают соответственно при использовании генератора воспроизводимых фазных сигналов согласно изобретению.

При использовании генератора воспроизводимых фазных сигналов согласно изобретению, фазы сигнала возбуждения испытуемого устройства преобразования частоты, локального сигнала осциллятора испытуемого устройства, и сигналов осциллятора для смесителей, используемых в отдельных трактах измерения сигнала, инициализируют при каждом измерении до идентичного значения фазы. Таким образом, отдельные входной и выходной сигналы со скорректированной системной ошибкой создают неопределенности

где

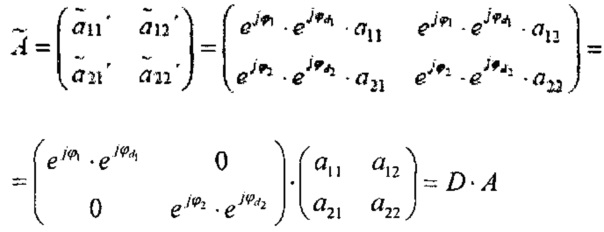

Матрица

При использовании генератора воспроизводимых фазных сигналов согласно изобретению и входного и выходного сигналов

Исходя из формулы (14) и на основании формулы (7), параметр

В противоположность этому, исходя из формулы (14) и на основании формулы (7), параметры

Эти неопределенности фазы содержат неизвестные фазовые искажения

На основе своей нелинейной передаточной характеристики испытуемое устройство преобразования частоты, в частности смеситель, может выдавать высшие гармоники или соответственно интермодуляционные помехи. Они могут накладываться на основные гармоники в портах испытуемого устройства и передаваться к портам схемного анализатора. После сопоставления ошибок в порте схемного анализатора, высшие гармоники, соответственно интермодуляционные помехи, отражают к портам испытуемого устройства, где их дополнительно смешивают с учетом частотного положения, а затем вновь переданы к портам схемного анализатора с возможностью неоднократного наложения при одинаковой частоте с основными гармониками входного и выходного сигналов соответствующего порта.

На фиг. 5 наряду с высокочастотным сигналом возбуждения RF, показаны сигнал генератора при частоте LO смесителя и выходной сигнал смесителя при промежуточной частоте IF, например интермодуляционная помеха, сформированная, главным образом, в смесителе при частоте RF=2*LO. Эта интермодуляционная помеха может быть передана на высокочастотный порт RF схемного анализатора и отражена там при частоте RF=2*LO, а затем вновь смешана в смесителе с образованием высокой частоты RF-LO. Сигнал, сформированный таким образом на основе интермодуляционной помехи, накладывается на сигнал возбуждения, образованный в высокочастотном порте RF схемного анализатора при высокой частоте RF, вызывая искажение измеренного результата. Для выявления этого искажения, необходимо выполнить дополнительное измерение в смесителе при первоначальной частоте RF=2*LO интермодуляционной помехи.

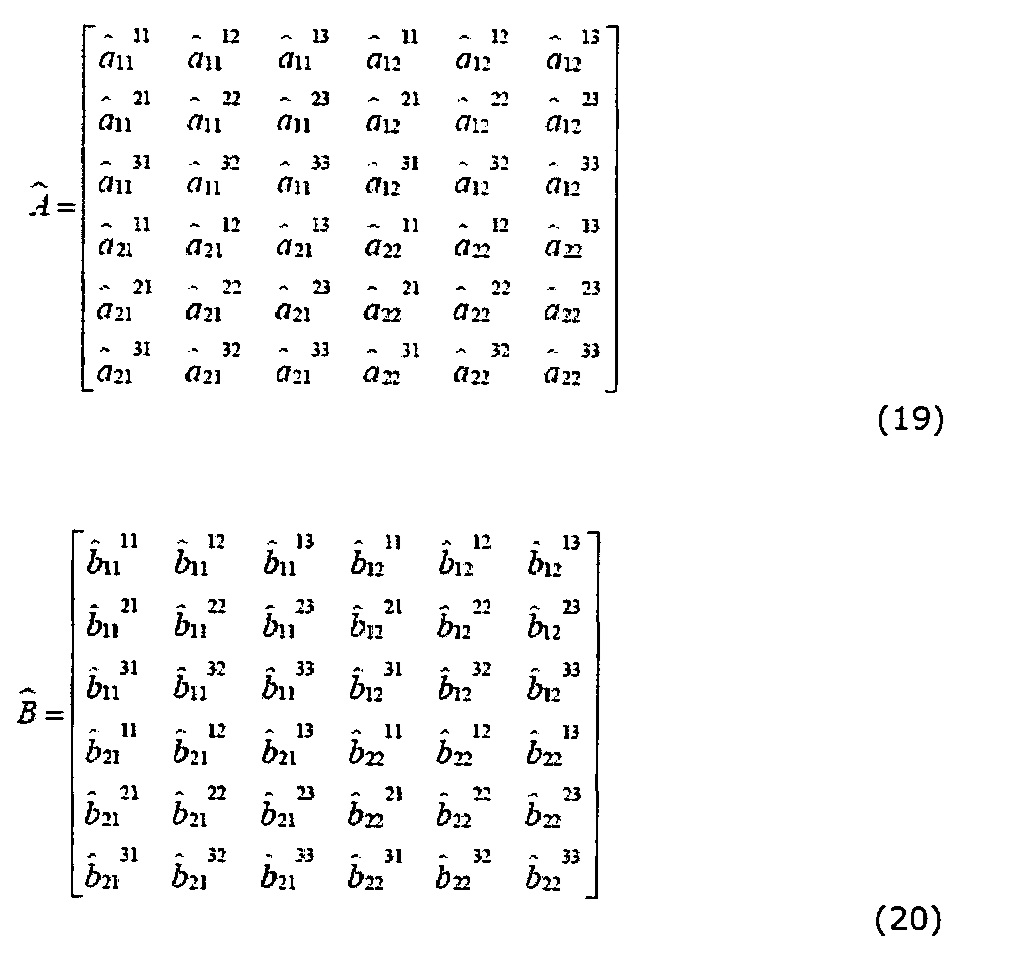

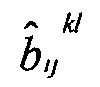

Для этого, как и для основных гармоник соответственно входного и выходного сигналов отдельных портов испытуемого устройства, соответственно входной и выходной сигналы отдельных портов испытуемого устройства также зарегистрированы при дополнительных частотах. На примере возбуждения порта j испытуемого устройства при трех различных частотах k, матрица

После коррекции системной ошибки матричных элементов двух матриц

Со ссылкой на формулы (14)-(18), используемые при анализе методом сеток с одной частотой, матрицу

При работе смесителя в режиме зеркального отражения и при измерении входного и выходного сигналов при зеркальной частоте, коэффициенты в матрицах

При этом условии, матрицу

С учетом данного математического обоснования, подробное описание способа определения параметров матрицы рассеяния испытуемого устройства преобразования частоты согласно изобретению будет приведено со ссылкой на блок-схему, изображенную на фиг. 4, а описание устройства для определения параметров матрицы рассеяния испытуемого устройства преобразования частоты будет приведено со ссылкой на принципиальные схемы, показанные на фиг. 2 и 3.

При выполнении первого шага S10, системные ошибки, возникающие соответственно в подлежащем измерению порте 1 и 2 испытуемого устройства 3 преобразования частоты, определяют посредством традиционного способа калибровки системной ошибки. При этом могут быть использованы известные способы калибровки с 7-ю, 9-ю и/или 10-ю параметрами.

При выполнении следующего шага S20, амплитудную составляющую |di| неизвестного комплексного коэффициента di, содержащаяся, согласно формуле (5А) или (5В), в каждом коэффициенте оптимизированной по уровню матрицы

Таким образом, матрица

При выполнении следующего шаг S30, фаза сигнала возбуждения инициализирована при одинаковом значении фазы при каждом измерении. Для этого блок высвобождения 7 генерирует сигнал инициализации, поступающий на буфер 8, значения фазы которого эквидистантны по времени синусоидального сигнала в первом генераторе 9 сигналов, формирующем сигнал возбуждения. При последующем синхронизирующем импульсе синхронизирующего сигнала, сгенерированного генератором 10 синхронизирующих импульсов, буфер 8 оповещается сигналом инициализации для записи на выходе выбранного и ранее установленного значения фазы, хранящегося в буфере 8.

Записанное в буфер 8 значение фазы, а также все последующие значения фазы синусоидального сигнала, записанные на выходе буфера 8 с синхронизирующим импульсом синхронизирующего сигнала, преобразуют в соответствующий аналоговый сигнал, в расположенном после буфера 8 цифроаналоговом преобразователе 11, управляемом синхронизирующим сигналом генератора 10 синхронизирующих импульсов. Аналоговый сигнал подают на вход фазового детектора 12, соединенного с фазорегулятором, для сравнения с сигналом возбуждения с уменьшенной частотой.

Уменьшение частоты высокочастотного сигнала возбуждения может быть выполнено после разъединения в соединителе 16 внутри частотного разделителя 13, также управляемого синхронизирующим сигналом генератора 10 синхронизирующих импульсов. Как правило, разность фаз фазового детектора 12 подают на фильтр 14 низких частот для ослабления составляющих сигнала повышенной частоты в схеме фазовой синхронизации и на управляемый напряжением осциллятор 15 для формирования высокочастотного сигнала возбуждения, зависящего от разности фаз, отфильтрованной фильтром низких частот.

Фазу локального сигнала осциллятора для испытуемого устройства 3 преобразования частоты инициализируют в начале каждого измерения фазокогерентным способом по отношению к фазе сигнала возбуждения, предпочтительно с тем же значением фазы. Для этого, как и в случае инициализации фазы сигнала возбуждения в первом генераторе 9 сигналов, буфер 8' второго генератора 9' сигналов, отвечающего за генерирование локального сигнала осциллятора, получает сигнал инициализации от блока высвобождения 7 и синхронизирующий сигнал от генератора 10 синхронизирующих импульсов. Как показано на фиг. 2, конструкция второго генератора 9' сигналов идентична конструкции первого генератора 9 сигналов и также включает в себя цифроаналоговый преобразователь 11', фазовый детектор 12', фильтр низких частот 14', управляемый напряжением осциллятор 15', соединитель 16' и частотный разделитель 13'.

Фазы отдельных сигналов осциллятора для смесителей, содержащихся в каждом отдельном тракте измерения сигнала, также инициализированы фазокогерентным способом в начале каждого измерения по отношению к фазе сигнала возбуждения, предпочтительно с тем же значением фазы. Все четыре тракта 26, 26', 26ʺ и 26ʺ' измерения сигнала для измерения соответственно входного сигнала

Локальный сигнал осциллятора для первого аналогового смесителя 18, 18', 18ʺ и 18ʺ' генерируют соответственно в присоединенном к нему генераторе 23, 23', 23ʺ и 23ʺ' сигналов, который обеспечивает идентичную структурную установку для первого генератора 9 сигналов, выполненного с возможностью формирования сигнала возбуждения, или соответственно для второго генератора сигналов 9', выполненного с возможностью формирования локального сигнала осциллятора испытуемого устройства 3 преобразования частоты, и принимает для этого сигнал инициализации от блока высвобождения 7 и синхронизирующий сигнал от генератора 10 синхронизирующих импульсов.

Локальный сигнал осциллятора для второго цифрового смесителя 20, 20', 20ʺ и 20ʺ' формируют в присоединенном к нему осцилляторе 24, 24', 24ʺ и 24ʺ' с числовым программным управлением, который содержит по меньшей мере один буфер, значения фазы синусоидального сигнала которого эквидистантны по времени, и также подают с сигналом инициализации блока высвобождения 7 и синхронизирующим сигналом генератора 10 синхронизирующих импульсов. Кроме того, управление аналого-цифровыми преобразователями 19, 19', 19ʺ и 19'ʺ в отдельных трактах измерения сигнала осуществляют синхронизирующим сигналом генератора 10 синхронизирующих импульсов.

При выполнении следующего шага S40, сигнал возбуждения, сформированный в первом генераторе 7 сигналов, подают при соответствующем положении переключателя 25, через соответствующий порт 4 или 5 схемного анализатора, на один из двух подлежащих измерению портов 1 или 2 испытуемого устройства 3 преобразования частоты, причем соответственно каждый входной сигнал

При проведении анализа методом сеток с несколькими частотами для каждого подлежащего измерению порта испытуемого устройства 3 преобразования частоты, входной

При выполнении следующего шага S50, в случае анализа методом сеток с одной частотой для каждого подлежащего измерению порта испытуемого устройства 3 преобразования частоты, соответственно входные сигналы

Аналогично, при проведении анализа методом сеток с несколькими частотами для каждого подлежащего измерению порта испытуемого устройства 3 преобразования частоты, соответственно входные

При выполнении следующего шага S60, в случае анализа методом сеток с одной частотой для каждого порта, параметры S11 и S22 отражения в двух подлежащих измерению портах 1 и 2 испытуемого устройства 3 преобразования частоты определяют по формулам (15) и (16) соответственно с помощью входных сигналов

При проведении анализа методом сеток с несколькими частотами для каждого порта испытуемого устройства 3 преобразования частоты, отдельные параметры

И, наконец, выполняемый в качестве опции, шаг S70: при проведении анализа методом сеток с одной частотой для каждого порта испытуемого устройства преобразования частоты, определяют параметры

При анализе методом сеток с несколькими частотами для каждого порта испытуемого устройства 3 преобразования частоты, параметры

Для приводимого в качестве примера измерения с тремя частотами каждого подлежащего измерению порта испытуемого устройства 3 преобразования частоты, по формуле (23) определяют матрицу

Изобретение не ограничено проиллюстрированным вариантом реализации. В частности настоящее изобретение охватывает все сочетания признаков, раскрытых в формуле изобретения, в описании и чертежах.

Реферат

Изобретение относится к способу и устройству для определения параметров матрицы рассеяния испытуемого устройства преобразования частоты. Устройство для определения параметров матрицы рассеяния испытуемого устройства преобразования частоты с использованием схемного анализатора определяет системные ошибки, возникающие между отдельными портами (1, 2) испытуемого устройства (3) преобразования частоты и портами (4, 5) схемного анализатора (6), соединенными с портами (1, 2) испытуемого устройства (3) преобразования частоты, и измеряет входные и выходные сигналы, имеющие системную ошибку соответственно в отдельных портах (1, 2) испытуемого устройства (3) преобразования частоты. После этого входные и выходные сигналы со скорректированной системной ошибкой соответственно в отдельных портах (1, 2) испытуемого устройства (3) преобразования частоты определены посредством взвешивания входных и выходных сигналов с системной ошибкой соответственно в отдельных портах (1, 2) испытуемого устройства (3) преобразования частоты с соответствующими вычисленными системными ошибками, а параметры матрицы рассеяния испытуемого устройства (3) преобразования частоты определены по входным и выходным сигналам со скорректированной системной ошибкой соответственно в отдельных портах (1, 2) испытуемого устройства (3) преобразования частоты. Фаза подлежащего измерению сигнала, возбуждающая соответственно порт (1, 2) испытуемого устройства (3) преобразования частоты, инициализирована одинаковым образом при каждом измерении. Технический результат заключается в повышении точности измерений. 2 н. и 18 з.п. ф-лы, 5 ил.

Формула

Комментарии