Устройство для функционального конт-роля больших интегральных cxem - SU802970A1

Код документа: SU802970A1

Чертежи

Описание

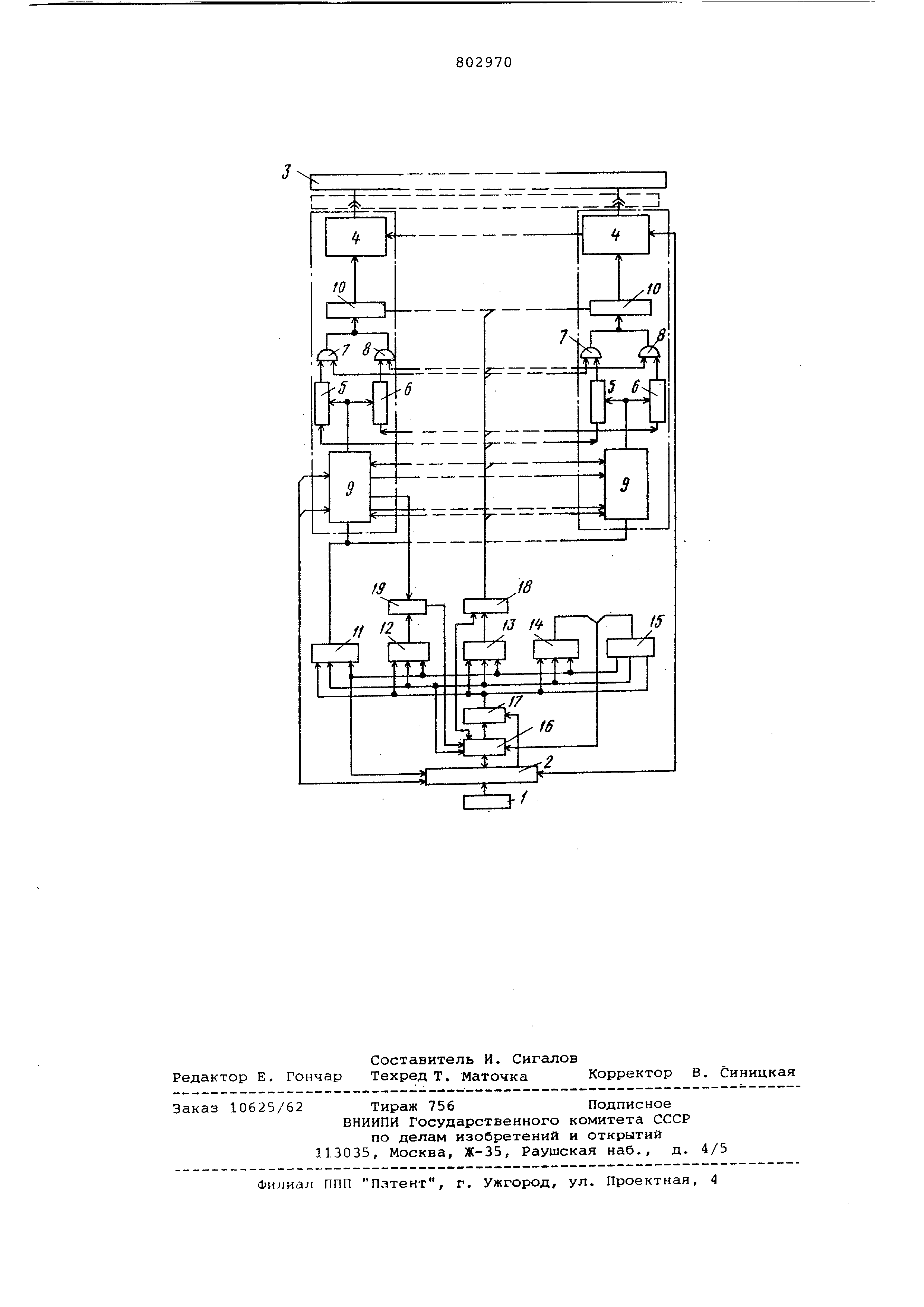

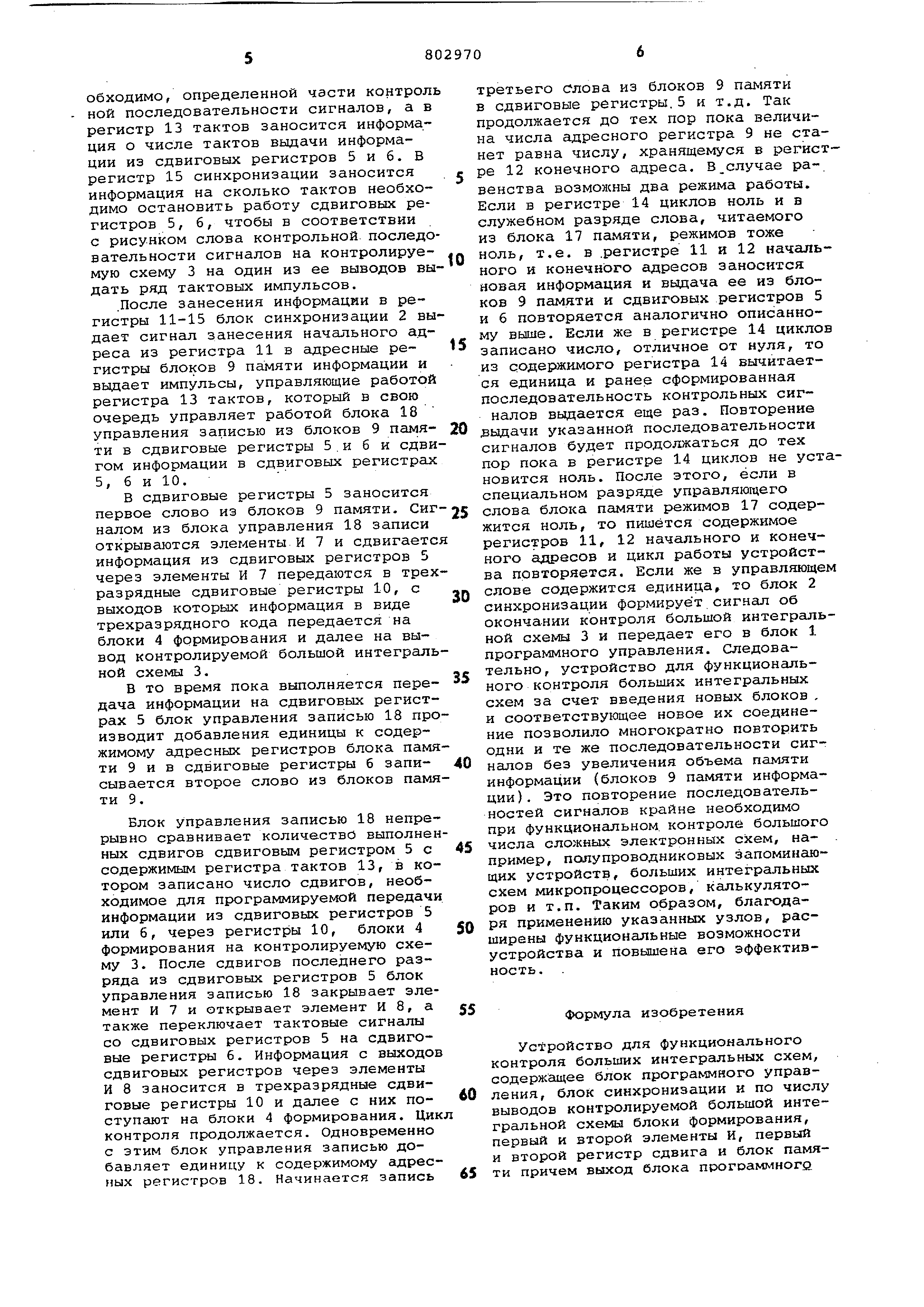

Изобретение относится к вычислительной и контрольно-измерительной технике и может быть использовано для функционального контроля цифровых больших интегральных схем. Известно устройство для функционального контроля цифровых интеграл ных схем, содержащее генератор конт рольных сигналов, регистры сдвига, блоки коммутации, блок сравнения, блоки с эталлонной логической схемой , блок индикации l. Недостатком известного устройств является необходимость применения эталонной схемы. Известно устройство для функционального контроля больших интегрешь ных схем, содержащее блок программного управления, соединенный с блоком синхронизации, и по числу выводов контролируемой большой интеграл ной схемы блоки сравнения, подключенные к соответствующим выходс1М бл ка синхронизации и к большой интегральной схеме, группу регистров сдвига, управлякхцие входы которых подключены к соответствующим выхода блока синхронизации 2 . Недостатком этого устройства явл ется его иовыс )кая надежность и огр ниченное быстродействие из-за наличия многоразрядного регистра сдвига на каждом выводе контролируемой интегральной схемы. Наиболее близким к изобретению техническим решением является устройство для функционального контроля больших интегральных схем содержащее блок программного управления, блок синхронизации и по числу выводов контролируемой большой интегральной схемы блоки формирования, первый и второй элементы И, первый и второй регистр сдвига и блок памяти, причем выход блока программного управления соединен с первым входом блока синхронизации, первый выход и второй вход которого соединен соответственно с первым входом и первым выходом всех блоков формирования, выход каждого блока памяти соединен с информационными входами.первого и второго регистра, выходы которых соединены с первыми входами соответственно первого и второго элемента И, выходы каждого блока формирования соединены с соответствующим контактом контролируемой большой интегральной схемы, второй выход и третий вход блока синхронизации соединен с первым входом всех блоков памяти з. Недостатком известного устройства для функционального контроля больших интегральных схем является отсутствие возможности многократного повторения части или всей контрольной последовательности сигналов без затрат большого объема памяти. Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения многократного повторения части или всей контрольной последовательности сигналов . Достигается это тем, что в устройство введены регистр начального адреса , регистр конечного адреса, регистр тактов, регистр циклов, блок управления режимами, блок сравнения блок управления трехразрядного сдвигового регистра, кроме того на каждый вывод большой интегральной схемы введены трехраэрядные сдвиговые регистры , информационные входы которых соединены с выходами первого и второ го элементов И, выход каждого трехразрядного сдвигового регистра соеди нены с вторьм входом блока формирования , третий выход блока синхрюниза ции соединен с первыми входами регис ра начального адреса, регистра конеч ного адреса, регистра тактов, регист ра циклов, регистра синхронизации, четвертый выход и четвертый .вход бло ка синхронизации соединен соответственно с первым входом и первым выходом блока управления режимами, вто рой выход которого соединен с вторым входами регистра начального адреса, регистра конечного адреса, регистра тактов, регистра циклов и регистра синхронизации, третий выход блока уп равления режимами соединен с первым входом блока памяти режимов, второй вход которого соединен с пятым выходом блока синхронизации, выход блока памяти режимов соединен с третьим входом регистра начального адреса, регистра конечного адреса, регистра тактов, регистра синхронизации, вторые выходы регистра начального адреса , регистра конечного адреса, регистра тактов, регистра циклов и регистра синхронизации соединены с вто рым входом блока управления режимами третий выход регистра начального адреса соединен с вторыми входами всех блоков памяти, третий выход регистра конечного сщреса соединен с первым входом блока сравнения, выход которо го соединен с третьим входом блока управления режимами,.четвертый выход которого соединен с вторым входом блока управления трехразрядного сдви гового регистра, третий выход регист ра тактов соединен с вторь 1М входом блока управления трехразрядного сдви гового регистра, выход которого соединен с третьими входами всех блоков памяти, с управляющими входами всех трехразряднЕлх сдвиговых регистров,. с вторыми входами всех элементов И и с управляющими входами всех первых и вторых регистров сдвига, третьи выходы регистра циклов и регистра синхронизации соединены с четвертым входом блока управления режимами, второй выход одного из блоков памяти соединен с вторым входом блока сравнения . На чертеже изображена блок-схема устройства для функционального контроля больших интегральных схем. Устройство содержит блок программного управления 1, блок синхронизации 2 и по числу выводов контролируемой большой интегральной схемы 3 блок формирования, первый регистр сдвига 5, второй регистр сдвига 6, первый элемент И 7, второй элемент И 8, блок памяти 9, трехразрядный сдвиговый регистр 10. Кроме того в состав устройства входят регистр начального адреса И, регистр конечного адреса 12, регистр тактов 13, регистр циклов 14, регистр синхронизации 15, блок управления режимами 16, блока памяти режимов 17, блок управления записью 18 и блок сравнения 19. Работа устройства для функционального контроля больших интегральных схем в этом случае происходит следующим образом. Перед началом работы в контактный узел устанавливается подлежащая контролю большая интегральная схема 3 из блока 1 программного .управления через блок 2 синхронизации в блоки 9 памяти заносится информация о последовательности контрольных сигналов, которую необходимо подать на выводы контролируемой большой интегральной схемы, чтобы оценить ее работоспособност.ь. В блок памяти режимов 17 заносится код режимов работы устройства. После ввода информации в блок памяти9 и блок памяти режимов 17 управление работой блоков устройства для функционального контроля больших интегральных схем передается блоку 2 синхронизации, который заносит информацию из блока памяти режимов 17 в регистры начального адреса 11, конечного адреса 12, тактов 13, циклов 14 и синхронизации 15. В регистр 11 заносится начальный адрес выдачи информации контрольной последовательности сигналов, в регистр 12 - конечный адрес массива информации контрольной последовательности сигналов, т.е. в целом информация в регистрах 11 и 12 определяет массив информации, выдавая который на блоке 4 формирования, формируется необходимая контрольная последовательность сигналов или ее часть. В регистр 14 циклов заносится информация о числе повторений, если это необходимо , определенной части контрол ной последовательности сигналов, а в регистр 13 тактов заносится информа ция о числе тактов выдачи информации из сдвиговых регистров 5 и 6. В регистр 15 синхронизации заносится информация на сколько тактов необходимо остановить работу сдвиговых ре гистров 5, б, чтобы в соответствии с рисунком слова контрольной последо вательности сигналов на контролируе мую схему 3 на один из ее выводов вы дать ряд тактовых импульсов. .После занесения информации в регистры 11-15 блок синхронизации 2 вы дает сигнал занесения начального адреса из регистра 11 в адресные регистры блоков 9 памяти информации и вьщает импульсы, управляющие работой регистра 13 тактов, который в свою очередь управляет работой блока 18 управления записью из блоков 9 пгшяти в сдвиговые регистры 5.и 6 и сдви гом информации в сдвиговых регистрах 5, б и 10. В сдвиговые регистры 5 заносится первое слово из блоков 9 памяти. Сиг налом из блока управления 18 записи открываются элементы И 7 и сдвигаетс информация из сдвиговых регистров 5 через элементы И 7 передаются в трех разрядные сдвиговые регистры 10, с выходов которых информация в виде трехразрядного кода передается на блоки 4 формирования и далее на вывод контролируемой большой интеграль ной схемы 3. В то время пока выполняется передача информации на сдвиговых регистрах 5 блок управления записью 18 про изводит добавления единицы к содержимому адресных регистров блока памя ти 9 и в сдвиговые регистры б записывается второе слово из блоков памя ти 9. Блок управления записью 18 непрерывно сравнивает количество выполнен ных сдвигов сдвиговым регистром 5с содержимым регистра тактов 13, в котором записано число сдвигов, необходимое для программируемой передачи информации из сдвиговых регистров 5 или 6, через регистры 10, блоки 4 формирования на контролируемую схему 3. После сдвигов последнего разряда из сдвиговых регистров 5 блок управления записью 18 закрывает элемент и 7 и открывает элемент И 8, а также переключает тактовые сигналы со сдвиговых регистров 5 на сдвиговые регистры б. Информация с выходов сдвиговых регистров через элементы И 8 заносится в трехразрядные сдвиговые регистры 10 и далее с них поступают на блоки 4 формирования. Цикл контроля продолжается. Одновременно с этим блок управления записью добавляет единицу к содержимому адресных регистров 18. Начинается запись третьего слова из блоков 9 памяти в сдвиговые регистры.5 и т.д. Так продолжается до тех пор пока величина числа адресного регистра 9 не станет равна числу, хранящемуся в регистре 12 конечного адреса. В случае равенства возможны два режима работы. Если в регистре 14 циклов ноль и в служебном разряде слова, читаемого из блока 17 памяти, режимов тоже ноль, т.е. в .регистре 11 и 12 начального и конечного адресов заносится новая информация и вьадача ее из блоков 9 памяти и сдвиговых регистров 5 и б повторяется аналогично описанному выше. Если же в регистре 14 циклов записано число, отличное от нуля, то из содержимого регистра 14 вычитается единица и ранее сформированная последовательность контрольных сигналов выдается еще раз. Повторение выдачи указанной последовательности сигналов будет продолжаться до тех пор пока в регистре 14 циклов не установится ноль. После этого, если в специальном разряде управляющего слова блока памяти режимов 17 содержится ноль, то пишется содержимое регистров 11, 12 начального и конечного адресов и цикл работы устройства повторяется. Если же в управляющем слове содержится единица, то блок 2 синхронизации формирует сигнал об окончании контроля большой интегральной схемы 3 и передает его в блок 1 программного управления. Следовательно , устройство для функционального контроля больших интегральных схем за счет введения новых блоков , и соответствующее новое их соединение позволило многократно повторить одни и те же последовательности сигналов без увеличения объема памяти информации (блоков 9 памяти информации ). Это повторение последовательностей сигналов крайне необходимо при функциональном контроле большого числа сложных электронных схем, например , полупроводниковых запоминающих устройств, больших интегральных схем микропроцессоров, калькуляторов и т.п. Таким образом, благодаря применению указанных узлов, расширены функциональные возможности устройства и повышена его эффективность . Формула изобретения Устройство для функционального контроля больших интегральных схем, содержащее блок программного управления , блок синхронизации и по числу выводов контролируемой большой интегральной схемы блоки формирования, первый и второй элементы И, первый и второй регистр сдвига и блок памяти причем выход блока прогоаммногй

управления соединен с первым входом блока синхронизации, первый выход и второй вход которого соединен соответственно с первым входом и первым выходом всех блоков формирования, выход каждого блока пс1мяти соединен с ин(1 ормадионными входами первого и второго регистров,,выходы которых соединены с первыми входами соответственно первого и второго элемента и, выходы каждого блока формирования соединены с соответствующим контактом контролируемой большой интегральной схемы, второй выход и третий вход блока синхронизации соединены с первым входом всех блоков памяти, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения многократного повторения части или всей контрольной последовательности сигналов, в устройство введены регистр начального сщреса, регистр конечного адреса, регистр тактов, регистр циклов и регистр синхронизации блок памяти режимов, блок управления режимами, блок сравнения, блок управления трехразрядного сдвигового регистра , кроме того на каждый вывод большой интегральной схемы введены трехразрядные сдвиговые регистры, информационные входы которых соединены с выходами первого и второго элементов И, выход каждого трехразрядного сдвигового регистра соединен со вторым входом блока формирования и третий выход блока синхронизации соединен с первыми входами регистра начального адреса, регистра конечного адреса, регистра тактов, регистра циклов, регистра синхронизации, четвертый выход и четвертый вход блока синхронизации соединены соответственно с первым входом и первым выходом блока управления режимами, второй вход которого соединен с вторыми входами регистра начального адреса, регистра конечного адреса, регистра тактов, регистра циклов и регистра синхронизации,третий выход блока управления режимами соединен с первым входом блока памяти режимов, второй вход которого соединен с пятым выходом блока синхронизации, выход блика памяти режимов соединен с третьими входами регистра начального адреса, регистра конечного адреса, регистра тактов, регистра циклов и регистра синхронизации, вторые выходы регистр начального адреса, регистра конечного адреса, регистра тактов,регистра циклов и регистра синхронизации соединены со вторым входом блока управлния режимами, третий выход регистра начального адреса соединен со вторыми входами всех блоков пё1мяти, третий выход регистра конечного адреса соединен с первым входом блока сравнения , выход которого соединен с третьим входом блока управления режимами , четвертый выход которого соединен с вторым входом блока управления трехразрядного сдвигового регистра, третий выход регистра тактов соеди .нен с вторым входом блока управления трехразрядного сдвигового регистра, выход которого соединен с третьими входами всех блоков памяти, с управляющими входами всех трехразрядных сдвиговых регистров, с вторыми входами всех элементов И и с управляющими всех первых и вторых регистров сдвига, третьи выходы регистра циклов и Е егистра синхронизации соединены с четвертьш входом блока управления и режимами, второй выход одного из блоков памяти соединен с вторым входом блока сравнения.

Источники информации, принятые во внимание при экспертизе

1.Патент Японии 48-41739,

кл. 97(7) G 01 М. кл. G Об F 11/00, опублик. 08.12.73.

2.Журнал Comouter Design 1970 12 p.p. 65-70. К D Smith a minicomputer aideduios array Tester.

3.Авторское свидетельство по заявке W 2035014/24, кл. G 06 F 15/46, 19.06.74 (прототип).

Реферат

Формула

Комментарии