Цифровое пятиканальное реле с функцией самодиагностики - RU2671545C1

Код документа: RU2671545C1

Чертежи

Описание

Изобретение относится к средствам автоматизации и может быть использовано в частности в системах управления электроагрегатов генераторных с приводом от двигателя внутреннего сгорания.

Известны аналоговые реле различного типа, содержащие измерительный преобразователь и выходной каскад, использующие различные способы измерения контролируемой физической величины /1, 2/.

Их недостатками являются ограниченные функциональные возможности в частности достоверность выходной информации и точность настройки.

Известен цифровой измеритель скорости вращения, содержащий импульсный датчик, генератор эталонной частоты, счетчик импульсов, элемент задержки и электронные ключи /3/. Он обеспечивает удовлетворительную точность.

Его недостатком являются невысокие функциональные возможности, заключающиеся в наличии лишь одного выходного канала и невысокая достоверность выходной информации.

Известно реле частоты вращения с трехканальным выходом по числу уставок, содержащее формирователь коротких импульсов, преобразователь частоты в постоянное напряжение, три пороговых устройства с задатчиками уставок, шесть индикаторов состояния и выходное устройство с тремя каскадами /4/. Наличие трех выходных каналов расширяет возможности РЧВ.

Однако возможные сбои в измерительной части и в выходных каналах при отсутствии самодиагностики отражаются на достоверности выходной информации РЧВ и могут привести к сбою в работе системы автоматического управления.

Наиболее близким по технической сущности к изобретению является цифровое реле частоты вращения с функцией реконструктивной диагностики, содержащее формирователь коротких импульсов, первый, второй и третий числовые компараторы, к разрядам первых входов которых подключены соответствующие разряды выходов соответственно первого, второго и третьего задающего регистра, выходное устройство с тремя выходными каскадами, три индикатора и элемент задержки, выход которого подключен к сбросовым входам первого и второго счетчика и входу записи исходного числа реверсивного счетчика, а вход соединен с выходом формирователя коротких импульсов, к которому так же подключены: вход распределителя импульсов, вход записи первого регистра памяти, единичный вход второго RS-триггера и первые входы пятого и десятого логического элемента И, вторые входы которых подключены соответственно к первому и второму выходу четвертого числового компаратора, разряды первого входа которого соединены с соответствующими разрядами выхода четвертого задающего регистра, разряды второго входа - с соответствующими разрядами выхода реверсивного счетчика, суммирующий вход которого подключен к выходу четвертого логического элемента И, вычитающий вход - к выходу третьего логического элемента И, а выход заема - к сбросовому входу второго RS-триггера прямой и инверсный выходы которого соответственно соединены со вторыми входами третьего и четвертого логических элементов И, первые входы которых подключены к выходу генератора импульсов стабильной частоты, к которому так же подключены первые входы первого и второго логических элементов И, ко вторым входам которых подключены соответственно прямой и инверсный выходы первого RS-триггера, а к выходам - счетные входы соответственно первого и второго счетчика, разряды выходов которых соответственно через первый и второй электронные ключи подключены к соответствующим разрядам входа первого регистра памяти, причем управляющий вход первого электронного ключа связан со вторым выходом распределителя импульсов и сбросовым входом первого RS-триггера, а управляющий вход второго электронного ключа - с первым выходом распределителя импульсов и единичным входом первого RS-триггера, кроме того соответствующие разряды выхода первого регистра памяти подключены к соответствующим разрядам входа исходного числа реверсивного счетчика и вторых входов первого, второго и третьего числовых компараторов выходы БОЛЬШЕ которых подключены соответственно к первому, второму и третьему разрядам входа дешифратора нулевой выход которого подключен к сбросовому входу третьего RS-триггера инверсный выход которого соединен с первым входом восьмого логического элемента И, прямой выход - с первым входом девятого логического элемента И, а единичный вход - с третьим выходом дешифратора, второй выход которого подключен к вторым входам восьмого и девятого логического элемента И, четвертый выход - к входу третьего индикатора входу первого логического элемента НЕ, выход которого подключен ко второму входу шестого логического элемента И, соединенного первым входом с выходом третьего числового компаратора, а выходом - с третьим разрядом входа второго регистра памяти, первый, второй и третий разряды выхода которого подключены соответственно к входам первого, второго и третьего выходного каскада, второй разряд входа - к выходу третьего логического элемента ИЛИ, а первый разряд входа - к выходу первого логического элемента ИЛИ, первый вход которого связан с выходом первого числового компаратора, второй вход - с вторым входом второго логического элемента ИЛИ и шестым выходом дешифратора, пятый выход которого соединен со вторым входом третьего логического элемента ИЛИ и первым входом четвертого логического элемента ИЛИ, выход которого подключен к входу второго индикатора, а второй вход - к выходу восьмого логического элемента И, связанного с входом второго логического элемента НЕ, выход которого соединен со вторым входом седьмого логического элемента И, подключенного выходом к первому входу третьего логического элемента ИЛИ, а первым входом - к выходу второго числового компаратора, кроме того выход девятого логического элемента И связан с третьим входом первого логического элемента ИЛИ и первым входом второго логического элемента ИЛИ, связанного выходом со входом первого индикатора, а выход десятого логического элемента И соединен с единичным входом четвертого RS-триггера, сбросовый вход которого подключен к шине сброс, а выход пятого логического элемента И - к входу записи второго регистра памяти /5/. Три задающих регистра и три числовых компаратора по существу представляют три приемных реле. Самоконтроль обеспечивает достоверность выходной информации.

Однако это реле имеет возможность контроля лишь трех каналов информации.

Цель изобретения - расширение функциональных возможностей путем увеличения числа контролируемых каналов выходной информации.

Цель изобретения достигается тем, что цифровое пятиканальное реле с функцией самодиагностики, содержащее три приемных реле, первый формирователь коротких импульсов, элемент задержки, первый, второй и третий логические элементы ИЛИ, логический элемент И, к первому входу которого подключен выход генератора импульсов, а к второму - прямой выход первого RS-триггера, второй RS-триггер, первый и второй логический элемент НЕ, регистр памяти, индикатор состояния, счетчик импульсов, к счетному входу которого подключен выход логического элемента И, числовой компаратор, снабжено четвертым и пятым приемным реле, со второго по двенадцатый формирователями коротких импульсов, с третьего по пятый логическими элементами НЕ, диодом, шиной ПУСК и блоком памяти, к разрядам входа адреса которого подключены соответствующие разряды выхода счетчика импульсов, а разряды выхода - к соответствующим разрядам второго входа числового компаратора, разряды первого входа которого связаны с соответствующими разрядами входа регистра памяти, с выходами соответствующих приемных реле, с входами соответственно с первого по пятый логических элементов НЕ и входами соответственно с первого по пятый формирователей коротких импульсов, выходы которых подключены к соответствующим с первого по пятый входам второго логического элемента ИЛИ, к другим с шестого по десятый входам которого соответственно подключены выходы с шестого по десятый формирователей коротких импульсов, кроме того входы с шестого по десятый формирователей коротких импульсов подключены соответственно к выходам с первого по пятый логических элементов НЕ, а выход второго логического элемента ИЛИ соединен с первым входом третьего логического элемента ИЛИ, связанного вторым входом с шиной ПУСК, а выходом - с входом элемента задержки, нулевым входом второго RS-триггера и третьим входом первого логического элемента ИЛИ, выход которого подключен к сбросовому входу счетчика импульсов, выход переполнения которого соединен с единичным входом второго RS-триггера, прямой выход которого связан с входом индикатора и входом двенадцатого формирователя коротких импульсов, выход которого подключен к первому входу первого логического элемента ИЛИ и к нулевому входу первого RS-триггера, единичный вход которого подключен к выходу элемента задержки, причем выход РАВНО числового компаратора соединен с входом одиннадцатого формирователя коротких импульсов, связанного через диод с нулевым входом первого RS-триггера и непосредственно - с входом записи регистра памяти и вторым входом первого логического элемента ИЛИ, а выход регистра памяти является выходом устройства.

Четвертый и пятый приемные реле увеличивают числи информационных каналов. С третьего по пятый логические элементы НЕ и со второго по десятый формирователи коротких импульсов и их связи обеспечивают контроль изменения сигналов на выходах приемных реле и выбор момента проверки их состояния. По адресам блока памяти записана естественная последовательность кодов, возникающая на выходе информационного блока, когда все приемные реле исправны, и которая необходима для выявления сбоя.

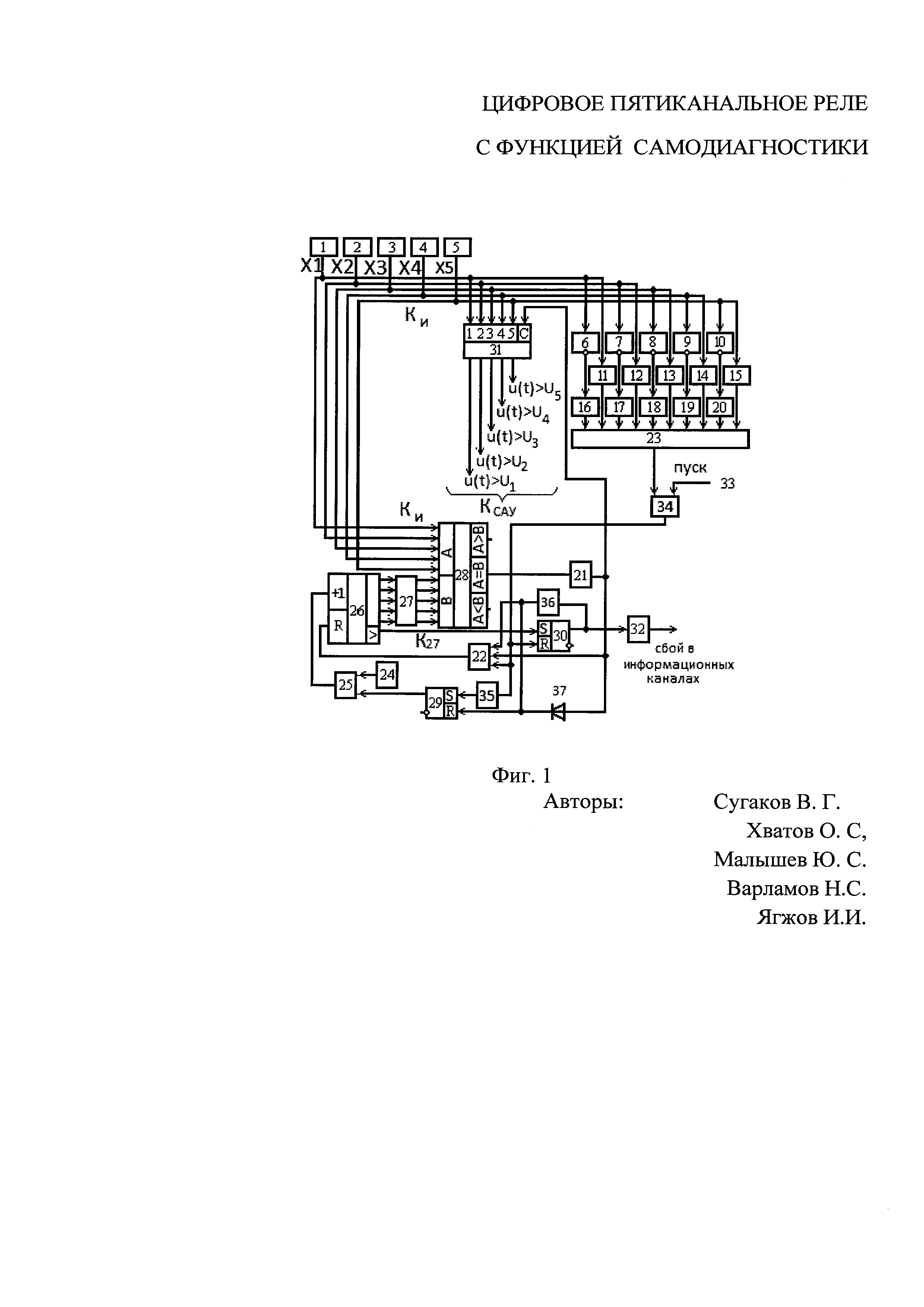

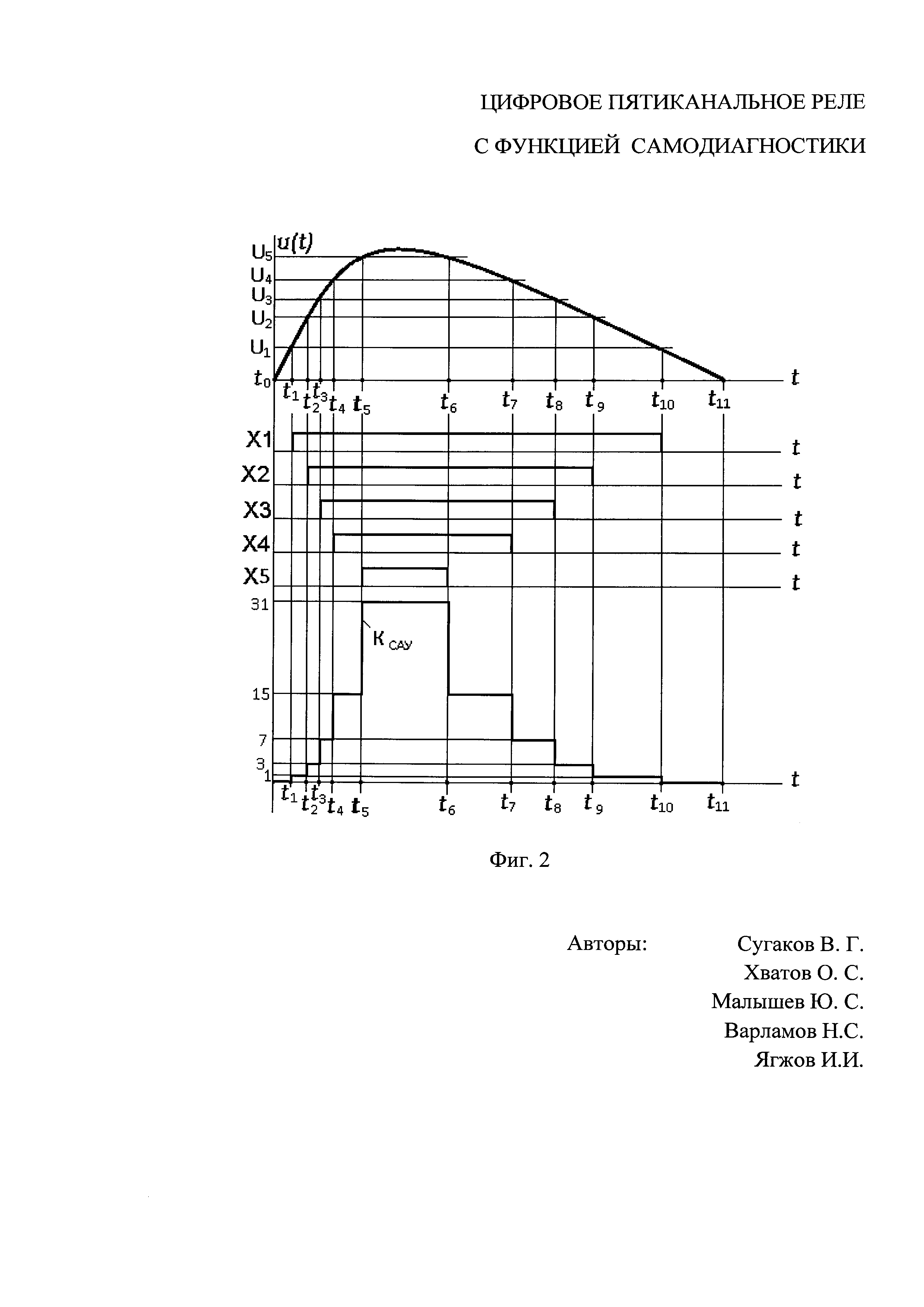

На фиг. 1 представлена схема цифрового пятиканального реле с функцией самодиагностики, на фиг. 2 - эпюры сигналов на элементах устройства.

Реле (фиг. 1) включает первый 1, второй 2, третий 3, четвертый 4 и пятый 5 приемные датчики соответствующих уставок (приемные реле), первый 6, второй 7, третий 8, четвертый 9 и пятый 10 логические элементы НЕ, первый 11, второй 12, третий 13, четвертый 14, пятый 15, шестой 16, седьмой 17, восьмой 18, девятый 19, десятый 20 и одиннадцатый 21 формирователи коротких импульсов, первый 22 и второй 23 логические элементы ИЛИ, генератор импульсов 24, логический элемент И 25, счетчик импульсов 26, блок памяти 27, числовой компаратор 28, первый 29 и второй 30 RS-триггер, регистр памяти 31, индикатор состояния (сбоя) 32, шину ПУСК 33, третий логический элемент ИЛИ 34, элемент задержки 35, двенадцатый формирователь коротких импульсов 36 и диод 37. В блоке памяти 27 по адресам записаны двоичные коды К27 чисел равных 2i-1, где i - номер адреса i=0…5 (000002, 000012, 000112, 001112, 011112 и 111112).

Реле работает следующим образом. Датчики 1…5 настроены на параметры срабатывания соответственно U1, U2, U3, U4 и U5, причем U5>U4>U3>U2>U1 (фиг. 2). При включении системы автоматического управления (САУ) подается сигнал на шину ПУСК 33 и появляется сигнал на выходе элемента ИЛИ 34. При этом через элемент ИЛИ 22 проходит сигнал, обнуляющий счетчик 26, триггер 30 переводится в нулевое состояние, а триггер 29 переводится в единичное состояние с задержкой за счет элемента задержки 35. Пусть в исходный момент времени t0 (фиг. 2) контролируемая величина u(t) меньше первой уставки U1, тогда на выходах датчиков 1…5 сигналы отсутствуют и на первый вход компаратора 28 подается нулевой код Ки. На второй вход компаратора 28 подается нулевой код К27 с выхода блока памяти 27 так, как с выхода счетчика 26 установлен нулевой адрес. Появляется сигнал на выходе РАВНО компаратора 28. По фронту этого сигнала формирователь 21 вырабатывает импульс, который производит запись нулевого кода Ки с выходов датчиков 1…5 в регистр 31. С выхода регистра 31 код КСАУ=Ки=000002 поступает в САУ. Одновременно сигналом с выхода формирователя 21 триггер 29 переводится в нулевое состояние, предотвращая изменение кода на выходе счетчика 26.

По мере возрастания контролируемой величины u(t) в момент времени U (фиг. 2) срабатывает датчик 1 и на его выходе появляется сигнал X1. На первый вход компаратора 28 поступает код Ки=000012=110. Одновременно сигнал X1 с выхода датчика 1 поступает на формирователь 11. Импульс с его выхода через элементы ИЛИ 23, 34 и элемент задержки 35 переводит триггер 29 в единичное состояние и подготавливает элемент И 25 по второму входу. С выхода генератора импульсов 24 через элемент И 25 проходит импульс на вход счетчика 26, и код на его выходе возрастает на единицу. С выхода блока памяти 27 на второй вход компаратора 28 поступает код К27 равный коду на его первом входе. По фронту сигнала с выхода компаратора 28 формирователем 21 вырабатывается импульс, записывающий в регистр 31 новый код КСАУ=Ки=000012. Вместе с тем импульс с выхода формирователя 21 переводит триггер 29 в нулевое состояние, предотвращая прохождение импульсов на вход счетчика 26, и через элемент ИЛИ 22 поступает на сбросовый вход счетчика 26, обнуляя его.

В момент времени t2 (фиг. 2) срабатывает датчик 2 и на его выходе появляется сигнал Х2. На первом входе компаратора 28 устанавливается код Ки=000112=310. По фронту сигнала Х2 формирователь 12 вырабатывает короткий импульс, который через элементы ИЛИ 23, 34 и элемент задержки 35 переводит триггер 29 в единичное состояние, открывая элемент И 25. На вход счетчика 26 начинают поступать импульсы с выхода генератора 24. Одновременно с изменением кода на выходе счетчика 26, поступающего на вход адреса блока памяти 27, меняется код К27 на его выходе, который поступает на второй вход компаратора 28. При наступлении равенства кодов на входах компаратора 28 появляется сигнал на его выходе, и в регистр 31 записывается новый код КСАУ=Ки=000112, поступающий в САУ. Сигналом с выхода формирователя 21 схема, как и в предыдущем случае приводится в исходное состояние.

По мере возрастания контролируемой величины в момент времени t3 (фиг. 2) появляется сигнал Х3 на выходе датчика 3. На первый вход компаратора 28 подается код Ки=001112=710. Формирователь 13 по фронту сигнала Х3 выдает импульс, который, как в предыдущих случаях, обеспечивает перебор адресов блока памяти 27. При совпадении кодов на входах компаратора 28 в регистр 31 записывается очередной код КСАУ=Ки=001112, который подается в САУ.

При дальнейшем возрастании контролируемой величины u(t) в момент времени t4 (фиг. 2) срабатывает датчик 4 и на его выходе появляется сигнал Х4. На первый вход компаратора 28 поступает код Ки=011112=1510. Импульсом с выхода формирователя 14 инициируется запись в регистр 31 нового кода КСАУ=Ки=011112 для САУ.

В момент времени t5 (фиг. 2) срабатывает датчик 5 и на его выходе появляется сигнал Х5. Импульсом с выхода формирователя 15 инициируется запись в регистр 31 кода КСАУ=Ки=111112, который поступает в САУ.

В результате при монотонном возрастании контролируемой величины и исправном состоянии информационных каналов в САУ подается естественная последовательность кодов КСАУ: 000002, 000012, 000112, 001112, 011112 и 111112, которая записана по адресам блока памяти 27.

При уменьшении контролируемой величины u(t) в момент времени t6 (фиг. 2) исчезает сигнал Х5 на выходе датчик 5 и на первый вход компаратора 28 поступает код Ки=011112=1510. Одновременно исчезает сигнал на входе элемента НЕ10, а на его выходе появляется сигнал, который поступает на вход формирователя 20. Импульс с выхода формирователя 20 через элементы ИЛИ 23, 34 и элемент задержки 35 поступает на единичный вход триггера 29. Сигнал с прямого выхода триггера 29 открывает элемент И 25, через который начинают проходить импульсы генератора 24 на вход счетчика 26. Возрастающий код на выходе счетчика 26 производит перебор адресов блока памяти 27. При совпадении кода К27 на выходе блока памяти 27 и кода на первом входе компаратора 28 на выходе компаратора 28 появляется сигнал и формирователь 21 выдает импульс на запись нового кода КСАУ=Ки=011112 в регистр 31 для подачи в САУ.

Аналогично происходит перезапись кода в регистр 31 при последующем уменьшении контролируемой величины.

В момент времени t7 (фиг. 2), когда исчезает сигнал Х4 на выходе датчика 4, появляется импульс на выходе формирователя 19, и в регистр 31 записывается код КСАУ=Ки=001112.

В момент времени t8 (фиг. 2) при исчезновении сигнала Х3 на выходе датчика 3 и появлении импульса на выходе формирователя 18 в регистр 31 заносится код КСАУ=Ки=000112.

В момент времени t9 (фиг. 2) с исчезновением сигнала Х2 на выходе датчика 2 и появлением импульса на выходе формирователя 17 в регистр 31 заносится код КСАУ=Ки=000012.

В момент времени t10 (фиг. 2) пропадает сигнал X1 на выходе датчика 1. Появляется импульс на выходе формирования 16, и в регистр 31 заносится код КСАУ=Ки=000002.

В результате при монотонном уменьшении контролируемой величины и исправности измерительных каналов в САУ поступают коды из указанной выше естественное последовательности кодов КСАУ: 000002, 000012, 000112, 001112, 011112.

Таким образом, при любом поведении контролируемой величины и исправности измерительных каналов в САУ поступают коды, входящие в естественную последовательность кодов, а появление сбойного кода, не принадлежащего этой последовательности, является признаком неисправности измерительного канала. Поступление сбойного кода предотвращается устройством следующим образом.

Пусть в исходном состоянии на выходах всех датчиков 1…5 присутствует сигналы и в регистр 31 записан код КСАУ=111112 подаваемый в САУ.

Если возникает сбой, например, датчика 3 и сигнал Х3 на его выходе пропадает, на первый вход компаратора 28 поступает сбойный код Ки=110112, не принадлежащий к числу кодов из естественной последовательности, записанных в блок памяти 27. Одновременно исчезает сигнал на входе логического элемента НЕ 8, а на его выходе сигнал появляется. По фронту этого сигнала формирователь 18 вырабатывает импульс, который проходит через логические элементы ИЛИ 23, 34 и 22 и поступает на сбросовый вход счетчика 26, обнуляя его. В то же время импульс с выхода формирователя 18 через логические элементы ИЛИ 23, 34 и элемент задержки 35 подается на единичный вход триггера 29, который с выдержкой времени подготавливает логический элемент И 25 по второму входу. Импульсы с выхода генератора 24 через элемент И 25 начинают поступать на вход счетчика 26. С ростом кода на выходе счетчика 26 происходит перебор кодов К27, записанных в блоке памяти 27, которые поступают на второй вход компаратора 28. Поскольку в блоке памяти 27 отсутствуют сбойные коды, то равенства кодов на входах компаратора 28 не наступает и сигнал на его выходе не появляется и перезапись кода в регистр 31 не производится. При этом в САУ подается прежний код, а сбойный код локализуется. Счетчик 26 не сбрасывается и код на его выходе продолжает возрастать, В момент переполнения счетчика 26 появляется сигнал его выходе переполнения, который переводит триггер 30 в единичное состояние. Сигнал с прямого выхода триггера 30 включает индикатор состояния (сбоя 32), указывающий, что САУ работает в режиме ограниченной функциональности. Одновременно по фронту сигнала с прямого выхода триггера 30 формирователь 36 вырабатывает импульс, который переводит устройство в исходное состояние. Этот импульс, проходя через элемент ИЛИ 22, обнуляет счетчик 26 и переводит триггер 29 в нулевое состояние, предотвращая поступление на вход счетчика 26 импульсов.

При возникновении других сбойных кодов работа устройства осуществляется как описано выше.

Таким образом, реле имеет расширенные функциональные возможности, заключающиеся в повышении достоверности выходной информации путем предотвращения поступления в САУ информации по пяти каналам при их сбое, что на две трети больше, чем у прототипа.

Источники информации

1. Сугаков В.Г. Основы автоматизации военных передвижных источников электрической энергии: учеб. пособие. - Кстово: НФВИУ, 2003. 168 с.

2. Дудченко В.Н., Аверкиев А.Н. Измерение неэлектрических величин: конспект лекций. - Кстово: НВВИКУ, 1997. 54 с.

3. Цифровой измеритель скорости вращения. Описание изобретения к авторскому свидетельству RU 1075167, 1984.

4. Комплекс средств контроля дизеля КСКД 17.5. Техническое описание и инструкция по эксплуатации ЗУ2.008.006 ТО. 1994. С. 35-37.

5. Патент на изобретение №2618495 по заявке 2016112100 от 30.03.2016, кл. G01P 3/54

Реферат

Изобретение относится к средствам автоматизации и может быть использовано, в частности, в системах управления генераторных электроагрегатов с приводом от двигателя внутреннего сгорания. Цифровое пятиканальное реле с функцией самодиагностики включает первый 1, второй 2, третий 3, четвертый 4 и пятый 5 приемные датчики соответствующих уставок (приемные реле), первый 6, второй 7, третий 8, четвертый 9 и пятый 10 логические элементы НЕ, первый 11, второй 12, третий 13, четвертый 14, пятый 15, шестой 16, седьмой 17, восьмой 18, девятый 19, десятый 20 и одиннадцатый 21 формирователи коротких импульсов, первый 22 и второй 23 логические элементы ИЛИ, генератор импульсов 24, логический элемент И 25, счетчик импульсов 26, блок памяти 27, числовой компаратор 28, первый 29 и второй 30 RS-триггеры, регистр памяти 31, индикатор состояния (сбоя 32), шину ПУСК 33, третий логический элемент ИЛИ 34, элемент задержки 35, двенадцатый формирователь коротких импульсов 36 и диод 37. В блоке памяти 27 по адресам записаны двоичные коды Кчисел ,равных 2-1, где i - номер адреса i=0…5 (00000, 00001, 00011, 00111, 01111и 11111). Технический результат - расширение функциональных возможностей, повышение достоверности выходной информации путем увеличения числа контролируемых каналов. 2 ил.

Формула

Документы, цитированные в отчёте о поиске

Цифровое реле частоты вращения с функцией реконструктивной диагностики

Комментарии