Устройство для контроля параллельного двоичного кода на чётность - RU207051U1

Код документа: RU207051U1

Чертежи

Описание

Полезная модель относится к импульсной технике и предназначена для использования в интегральных микросхемах счетных и управляющих устройств на комплементарных полевых транзисторах структуры металл-окисел-полупроводник (КМОП).

Известны устройства для контроля параллельного двоичного кода на четность, построенные по древовидной структурной схеме на элементах ИСКЛЮЧАЮЩЕЕ 2ИЛИ с однофазными входами и выходами. См., например, патент США №3141962 НПК 235 - 153, МПК G06F 11/10, G06F 7/48, G06F 7/50, G06F 7/501, опубликованный 21 июля 1964 г. [1]. В случае выполнения элементов таких устройств на КМОП-транзисторах, логические цепи элементов содержат по два каскада КМОП-вентилей, что снижает быстродействие.

Этот недостаток устранен в устройстве, описанном в авторском свидетельстве СССР №404084 МПК G06F 7/38, G05F 11/10, опубликованном 26 октября 1973 г. [2], логические цепи которого, реализующие операции 2(2И)-2ИЛИ, выполняют функции ИСКЛЮЧАЮЩЕЕ 2ИЛИ, принимая сигналы и распространяя их далее в парафазной форме, то есть в виде пар взаимно инверсных логических сигналов. Такие функции над парафазными сигналами выполнимы однокаскадными КМОП-вентилями, как, например, описанными в патенте США №3252011, НПК 307-88.5, МПК G06F 7/50, G06F 7/502, H03K 19/0948, H03K 19/21, опубликованном 17 мая 1966 г. [3]. По своей технической сущности данные решения в совокупности наиболее близки заявляемой полезной модели.

Наиболее близкий аналог содержит логические элементы ИСКОЛЮЧАЮЩЕЕ 2ИЛИ в количестве, равном числу разрядов контролируемого кода N за вычетом одного. Они образуют древовидную цепь, состоящую из нескольких каскадов, число которых K равно округленному до ближайшего большего целого значению логарифма по основанию два от разрядности N проверяемого на четность параллельного двоичного кода, то есть K=⎡log2N⎤.

Каждый элемент ИСКЛЮЧАЮЩЕЕ 2ИЛИ с парой взаимно инверсных выходов содержит по два КМОП-вентиля, каждый из которых состоит из четырех пар КМОП-транзисторов с индуцированными каналами р- и n-типа проводимости. Для формирования инверсий, дополняющих однофазные входные сигналы устройства, в его состав входят инверторы, содержащие по одной КМОП-транзисторной паре.

Общее количество содержащихся в устройстве комплементарных транзисторных пар равно 8(N - 1)+N.

Большое количество КМОП-транзисторов в составе устройства является его недостатком.

Технический результат полезной модели, заключающийся в устранении данного недостатка, достигается тем, что в устройстве для контроля параллельного двоичного кода на четность, содержащем элементы ИСКЛЮЧАЮЩЕЕ 2ИЛИ в количестве, равном числу разрядов контролируемого кода N за вычетом одного, образующие древовидную цепь, состоящую из нескольких каскадов, число которых K равно округленному до ближайшего большего целого значению логарифма по основанию два от N, то есть K=⎡log2N⎤, элементы ИСКЛЮЧАЮЩЕЕ 2ИЛИ, составляющие первый каскад имеют по два прямых входа, являющихся входами устройства для приема пар разрядов контролируемого двоичного кода, в каждом следующем каскаде элементы ИСКЛЮЧАЮЩЕЕ 2ИЛИ имеют по две пары из прямого и инверсного входов, которые соответственно подключены к парам из прямого и инверсного выходов двух элементов ИСКЛЮЧАЮЩЕЕ 2ИЛИ из предыдущих каскадов, если количество разрядов контролируемого двоичного кода нечетно, в одном из следующих за первым каскаде содержится элемент ИСКЛЮЧАЮЩЕЕ 2ИЛИ с одним прямым входом, являющимся входом устройства для приема, не имеющего пары разряда контролируемого кода, и с одной парой из прямого и инверсного входов, подключенных к аналогичной паре выходов элемента ИСКЛЮЧАЮЩЕЕ 2ИЛИ одного из предыдущих каскадов, прямой и инверсный выходы элемента ИСКЛЮЧАЮЩЕЕ 2ИЛИ последнего каскада соответственно являются выходами устройства для сигналов признаков нечетности и четности числа единиц среди значений разрядов контролируемого кода, каждый элемент ИСКЛЮЧАЮЩЕЕ 2ИЛИ состоит из семи пар МОП-транзисторов обогащенного типа с индуцированными каналами р- и n-типа проводимости, истоки первых, четвертых и пятых р- и n-МОП-транзисторов соответственно подключены к шинам положительного напряжения питания и нулевого потенциала, а стоки соответственно соединены с истоками вторых, третьих и шестых р- и n-МОП-транзисторов, стоки второго, третьего р-МОП- и шестого, седьмого n-МОП-транзисторов соединены и являются инверсным выходом элемента, а стоки шестого, седьмого р-МОП- и второго, третьего n-МОП-транзисторов - его прямым выходом, у первых р- и n-МОП-транзисторов затворы соединены и являются первым прямым входом элемента, а затворы третьего, шестого р-МОП- и третьего n-МОП-транзисторов - его первым инверсным входом, затворы второго, пятого р-МОП- и второго n-МОП-транзисторов соединены и являются вторым прямым входом элемента, а затворы четвертого, седьмого р-МОП- и четвертого n-МОП-транзисторов - его вторым инверсным входом, внесены следующие отличия, в каждом элементе ИСКЛЮЧАЮЩЕЕ 2ИЛИ истоки седьмых МОП-транзисторов подключены к стокам первых МОП-транзисторов аналогичных типов, затворы пятого, шестого и седьмого n-МОП-транзисторов соответственно подключены ко второму прямому, первому и второму инверсным входам элемента, первый инвертирующий вход внутри каждого элемента ИСКЛЮЧАЮЩЕЕ 2ИЛИ первого каскада и элемента ИСКЛЮЧАЮЩЕЕ 2ИЛИ с одной парой взаимно инверсных входов подключен к соединенным стокам первых р- и n-МОП-транзисторов, а второй инвертирующий вход внутри каждого элемента ИСКЛЮЧАЮЩЕЕ 2ИЛИ первого каскада - к соединенным стокам пятых МОП-транзисторов обоих типов.

Каждый элемент ИСКЛЮЧАЮЩЕЕ 2ИЛИ конструктивно выполнен в виде первой и второй смежных продольными сторонами областей МОП-структур р-типа и примыкающих к ним продольными сторонами также смежных первой и второй областей МОП-структур n-типа, причем первые р- и n-МОП области расположены рядом, поперек всех четырех областей МОП-структур, разделяя их на области стоков-истоков соответствующих типов, проходят четыре полоски затворов, которые, пересекая первые области р- и n-МОП-структур в порядке номеров, образуют области каналов с первых по четвертые р- и n-МОП-транзисторов соответственно, а, пересекая вторые области МОП-структур р-и n-типа, вторая, третья и четвертая полоски затворов образуют области каналов пятых, шестых и седьмых МОП-транзисторов соответственно р- и n-типа, крайние области истоков первой области р-МОП-структур и крайняя со стороны второй полоски затворов область истока второй области р-МОП-структур подключены к шине положительного напряжения питания, а крайние области истоков первой области n-МОП-структур и крайняя со стороны второй полоски затворов область истока второй области n-МОП-структур - к шине нулевого потенциала, области стоков-истоков, расположенные между первой и второй полосками затворов в первых областях МОП-структур обоих типов, электрически связаны с крайними со стороны четвертой полоски затворов областями истоков вторых областей МОП-структур аналогичных типов, области стоков, расположенные между второй и третьей полосками затворов в первой области р-МОП-структур и между третьей и четвертой полосками затворов во второй области n-МОП-структур, электрически связаны с инверсным выходом элемента, а области стоков, расположенные между третьей и четвертой полосками затворов во второй области р-МОП-структур и между второй и третьей полосками затворов в первой области n-МОП-структур, электрически связаны с прямым выходом элемента, первая и вторая полоски затворов соответственно подключены к первому и второму прямым входам элемента.

В каждом элементе ИСКЛЮЧАЮЩЕЕ 2ИЛИ первого каскада третья полоска затворов электрически связана с областями стоков-истоков, расположенными между первой и второй полосками затворов в первых областях МОП-структур обоих типов, а четвертая полоска затворов - с областями стоков-истоков между второй и третьей полосками затворов во вторых областях р- и n-МОП-структур.

У каждого элемента ИСКЛЮЧАЮЩЕЕ 2ИЛИ следующих каскадов третья и четвертая полоски затворов соответственно подключены к первому и второму инвертирующим входам элемента.

В случае нечетной разрядности контролируемого двоичного кода в элементе ИСКЛЮЧАЮЩЕЕ 2ИЛИ с одним прямым входом и одной парой из прямого и инверсного входов третья полоска затворов электрически связана с областями стоков-истоков, расположенными между первой и второй полосками затворов в первых областях МОП-структур обоих типов, а четвертая полоска затворов подключена ко второму инверсному входу элемента.

Указанное выполнение устройства для контроля параллельного двоичного кода на четность позволяет сократить число МОП-транзисторов, а изменение их связей дает возможность применения определенных конструктивных решений элементов, обеспечивающих высокую плотность упаковки устройства в интегральном исполнении и снижение паразитных емкостей.

Отличительными признаками полезной модели являются связи МОП-транзисторов в составе элементов ИСКЛЮЧАЮЩЕЕ 2ИЛИ и конструктивное выполнение элементов.

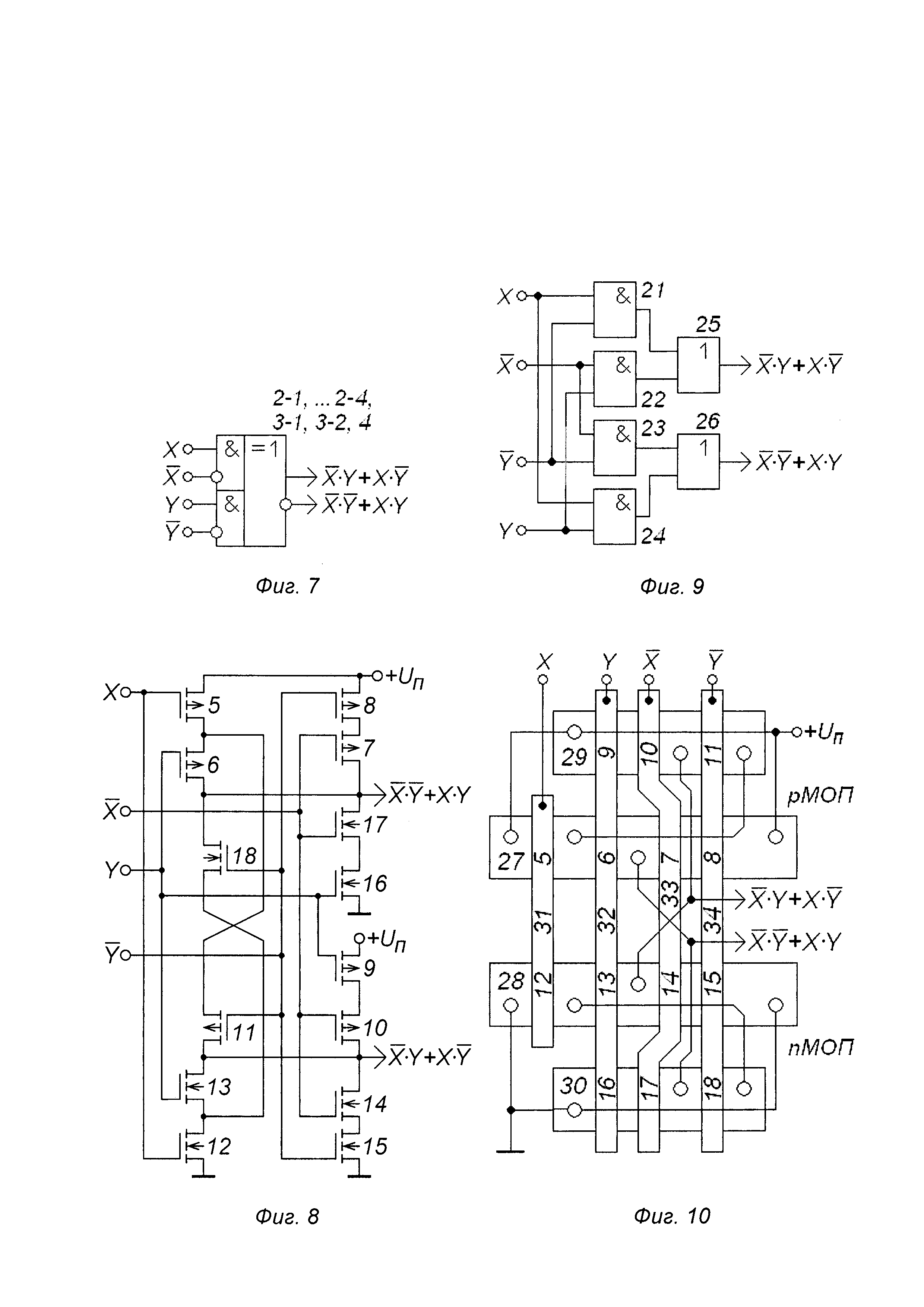

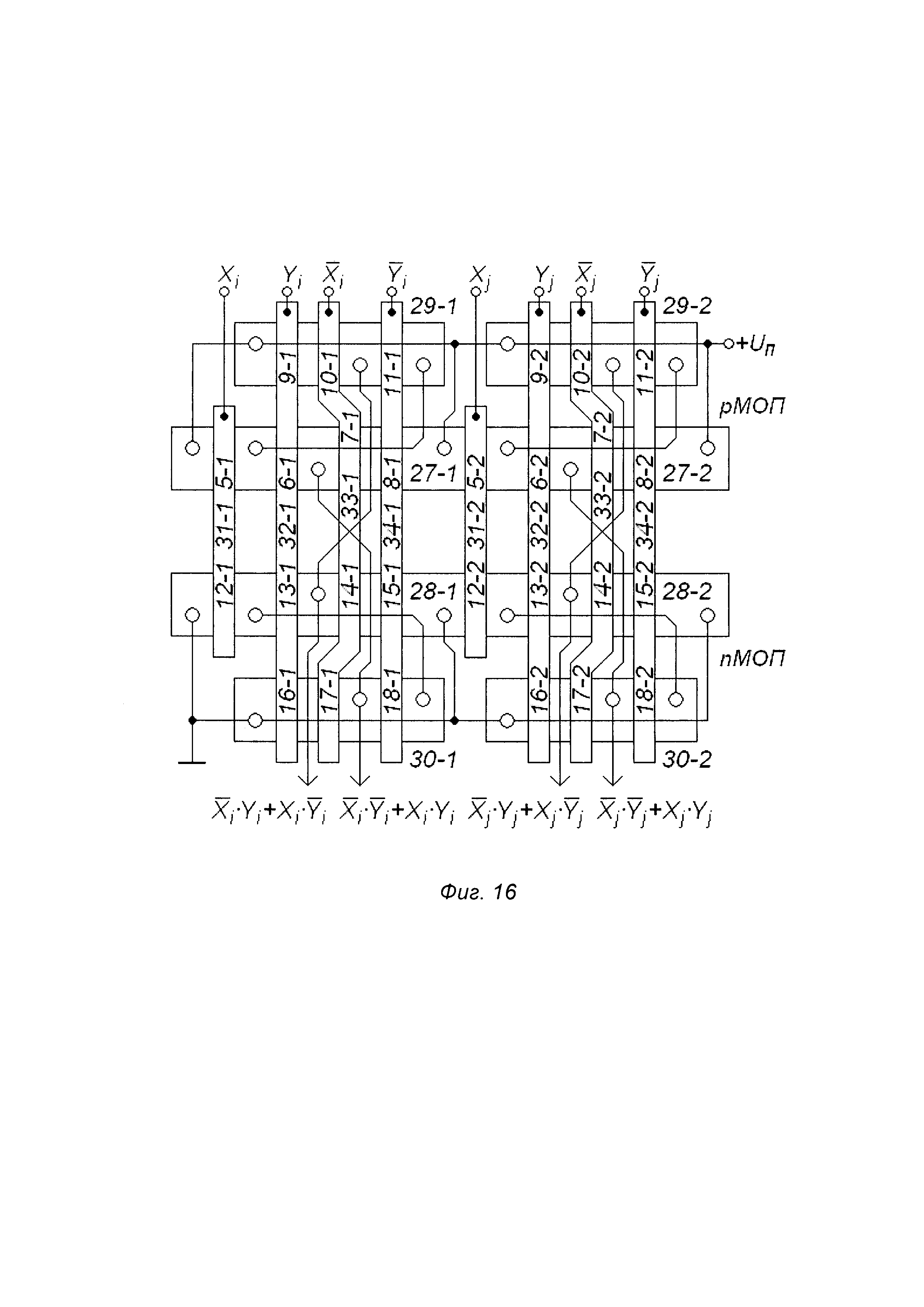

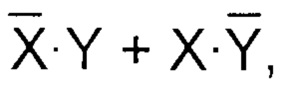

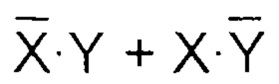

Полезную модель поясняют чертежи. Фиг. 1 и 2 представляют функциональные электрические схемы 16- и 13-разрядных устройств для контроля параллельного двоичного кода на четность. На фиг. 3, 4, 5, 6 изображены условное графическое обозначение, принципиальная и эквивалентная ей функциональная электрические схемы, схема конструктивного выполнения элемента МСКЛЮЧАЮЩЕЕ 2ИЛИ первого каскада. Те же изображения для элементов ИСКЛЮЧАЮЩЕЕ 2ИЛИ последующих каскадов и имеющего один прямой вход и одну пару из прямого и инверсного входов представляют фиг. 7, 8, 9, 10 и фиг. 11, 12, 13, 14 соответственно. На фиг. 15 и 16 показаны примеры объединения областей МОП-структур соседних элементов ИСКЛЮЧАЮЩЕЕ 2ИЛИ первого и последующих каскадов.

Устройство для контроля параллельного двоичного кода на четность содержит элементы ИСКЛЮЧАЮЩЕЕ 2ИЛИ в количестве, равном числу разрядов контролируемого кода N за вычетом одного. Элементы образуют древовидную цепь, состоящую из нескольких каскадов, число которых K, равно округленному до ближайшего большего целого значению логарифма по основанию 2 от N, то есть K=⎡log2N⎤. В приведенных примерах N=16 и 13. Элементы ИСКЛЮЧАЮЩЕЕ 2ИЛИ 1-1, 1-2, … 1-8, составляющие первый каскад имеют по два прямых входа, являющихся входами устройства для приема пар разрядов a1 и а2, а3 и а4, … а15 и а16 контролируемого двоичного кода. В каждом следующем каскаде элементы ИСКЛЮЧАЮЩЕЕ 2ИЛИ 2-1, 2-2, 2-3, 2-4, 3-1, 3-2, 4 имеют по две пары из прямого и инверсного входов, которые соответственно подключены к парам из прямого и инверсного выходов двух элементов ИСКЛЮЧАЮЩЕЕ 2ИЛИ из предыдущих каскадов. Если количество разрядов контролируемого двоичного кода нечетно, как в примере на фиг. 2 с N=13, в одном из следующих за первым каскаде содержится элемент ИСКЛЮЧАЮЩЕЕ 2ИЛИ 3-3 с одним прямым входом, являющимся входом устройства для приема, не имеющего пары разряда а13 контролируемого кода, и с одной парой из прямого и инверсного входов, подключенных к аналогичной паре выходов элемента ИСКЛЮЧАЮЩЕЕ 2ИЛИ 2-3 предыдущего каскада. Прямой и инверсный выходы элемента ИСКЛЮЧАЮЩЕЕ 2ИЛИ 4 последнего каскада соответственно являются выходами устройства для сигналов Нечет и Чет признаков нечетности и четности числа единиц среди значений разрядов а1, а2, а3, … a16 контролируемого кода.

Каждый элемент ИСКЛЮЧАЮЩЕЕ 2ИЛИ состоит из семи МОП-транзисторов 5, 6, … 11 обогащенного типа с индуцированными каналами р-типа проводимости, истоки первого, четвертого и пятого из которых - 5, 8 и 9 подключены к шине +Uп положительного напряжения питания, и из семи МОП-транзисторов 12, 13, … 18 обогащенного типа с индуцированными каналами n-типа проводимости, истоки первого, четвертого и пятого из которых - 12, 15 и 16 подключены к шине нулевого потенциала. Стоки первых МОП-транзисторов 5 и 12 обоих типов соответственно соединены с истоками пар из второго, седьмого р- и n-МОП-транзисторов 6, 11 и 13, 18, а стоки четвертых и пятых р- и n-МОП-транзисторов 8 и 9, 15 и 16 соответственно подключены к истокам третьих и шестых МОП-транзисторов 7 и 10, 14 и 17 аналогичных типов. Стоки второго, третьего р-МОП- и шестого, седьмого n-МОП-транзисторов 6, 7 и 17, 18 соединены и являются инверсным выходом

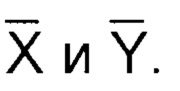

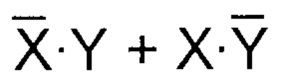

Затворы первых р- и n-МОП-транзисторов 5 и 12 соединены и являются первым прямым входом X элемента, а затворы вторых и пятых МОП-транзисторов 6, 13 и 9, 16 обоих типов - его вторым прямым входом Y. У третьих, шестых р- и n-МОП-транзисторов 7, 10 и 14, 17 затворы соединены, в элементах ИСКЛЮЧАЮЩЕЕ 2ИЛИ первого каскада (фиг. 4) и в элементе с одной парой взаимно инверсных входов (фиг. 12) они подключены к стокам первых МОП-транзисторов 5 и 12, а в элементах последующих каскадов (фиг. 8) являются первым инверсным входом

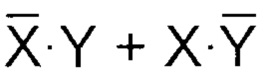

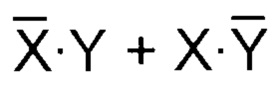

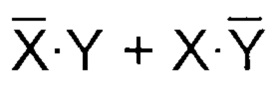

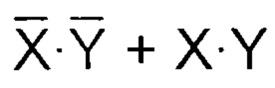

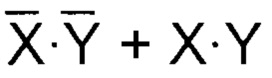

Устройство работает следующим образом. Элементы 1-1, 1-2, … 1-8 ИСКЛЮЧАЮЩЕЕ 2ИЛИ первого каскада, принимая на свои входы X и Y пары разрядов a1 и а2, а3 и а4, … а15 и а16 контролируемого двоичного кода, формируют на своих прямых и инверсных выходах сигналы, соответствующие функциям

Работу элементов 1-1, 1-2, … 1-8 первого каскада поясняет эквивалентная функциональная схема на фиг. 5. Содержащиеся в ней инверторы 19 и 20 входных сигналов X и Y соответствуют вентильным цепям на первых и пятых р- и n-МОП-транзисторах 5, 12 и 9, 16, со стоков которых инверсия сигнала X и инверсия сигнала Y поступают на затворы третьих, шестых и четвертых, седьмых МОП-транзисторов 7, 14, 10, 17 и 8, 15, 11, 18 обоих типов.

Последовательная цепь из р-МОП-транзисторов 5 и 6 подключает инверсный выход

Аналогичным образом формируются логические уровни на прямом выходе

Элементы ИСКЛЮЧАЮЩЕЕ 2ИЛИ 1-1, 1-2, … 1-8 формируют на своих прямых и инверсных выходах

Результаты парных сложений далее идут на входы элементов ИСКЛЮЧАЮЩЕЕ 2ИЛИ 2-1, 2-2, … 2-4, составляющих второй каскад, которые формируют из них результаты сложения по модулю два для пар 2-разрядных сумм a1, а2 и а3, а4, … а13, а14 и а15, a16.

Для работы элементов ИСКЛЮЧАЮЩЕЕ 2ИЛИ 2-1, 2-2, 2-3, 2-4, 3-1, 3-2 и 4 второго и последующих каскадов по эквивалентной функциональной схеме на фиг. 9 инверторы не требуются, так как инверсии сигналов X и Y они получают в готовом виде по первому и второму инвертирующим входам

Сложение по модулю два полученных во втором каскаде 4-разрядных сумм выполняют элементы 3-1 и 3-2, а составляющий последний каскад сложения элемент 4 формирует сигналы полной суммы, высокие уровни которых на прямом и инверсном выходах элемента 4 соответствуют нечетности и четности числа логических единиц среди значений контролируемых разрядов a1, а2, … а16, поступающих на все входы устройства.

Во втором примере выполнения устройства на фиг. 2 оно проверяет нечетное количество разрядов a1, а2, … а13 кода. Не имеющий пары разряд а13 элемент ИСКЛЮЧАЮЩЕЕ 2ИЛИ 3-3 с одной парой взаимно инверсных входов прибавляет к сумме по модулю два из разрядов а9, а10, а11, а12, сигналы которой в двухфазной форме выполняет элемент 2-3.

Каждый элемент ИСКЛЮЧАЮЩКК 2ИЛИ в устройстве складывает по модулю два пару разрядов контролируемого кода или две частичные суммы разрядов, сформированные в предыдущих каскадах. На каждом каскаде этих элементов вдвое уменьшается количество складываемых частей, из которых можно составить пары, Если для одной части пары нет, она передается на ближайший из последующих каскадов, где сможет объединиться с одной оставшейся там без пары частью. Так происходит до полного объединения всех частичных сумм.

Максимальное количество N разрядов контролируемого кода, которые может сложить по модулю два древовидная цепь элементов ИСКЛЮЧАЮЩЕЕ 2ИЛИ, состоящая из K каскадов, равно 2K. А если количество разрядов превысит 2K, но останется меньше 2⋅2K, понадобится добавить еще один каскад. Следовательно, количество каскадов K равно степени, в которую следует возвести число 2, чтобы получить равное N или ближайшее превышающее N целое число, что выражает формула K=⎡log2N⎤.

Выражение для количества элементов ИСКЛЮЧАЮЩЕЕ 2ИЛИ легко получить в случае равенства разрядности N двум в целой степени, равной K, то есть N=2K. Так как в первом каскаде количество элементов равно N / 2 и уменьшается вдвое на каждом следующем каскаде, их общее число будет соответствовать сумме SK из K членов геометрической прогрессии со знаменателем q=0,5. Подставив в известную формулу значения q, первого и последнего членов прогрессии p1=2K-1 и pK=1, получим следующее выражение для SK

Количество элементов ИСКЛЮЧАЮЩЕЕ 2ИЛИ останется равным N - 1 при любом N потому, что каждое увеличение N на один разряд потребует добавить один элемент.

В конструкции каждого элемента ИСКЛЮЧАЮЩЕЕ 2ИЛИ (фиг. 6, 10 и 14) первые области 27 и 28 р- и n-МОП-структур примыкают друг к другу, а вторые области 29 и 30 - расположены по краям элемента. Поперек всех четырех областей 27, 28, 29, 30 МОП-структур, разделяя их на области стоков-истоков соответствующих типов, проходят четыре полоски 31, 32, 33, 34 затворов. Пересекая первые области 27 и 28 р- и n-МОП-структур, полоски 31, 32, 33, 34 образуют области каналов с первых по четвертые р-МОП-транзисторы 5, 6, 7, 8 и n-МОП-транзисторов 12, 13, 14, 15 соответственно, а, пересекая вторые области 29 и 30 МОП-структур р-и n-типа, вторая, третья и четвертая полоски 32, 33, 34 затворов образуют области каналов пятых, шестых, седьмых МОП-транзисторов 9, 10, 11 и 16, 17, 18 соответственно р- и n-типа. Крайние области истоков первых областей 27 и 28 р- и n-МОП-структур и крайние со стороны второй полоски 32 затворов области истоков вторых областей 29 и 30 р- и n-МОП-структур соответственно подключены к шинам +Uп положительного напряжения питания и нулевого потенциала. Области стоков-истоков, расположенные между первой и второй полосками 31 и 32 затворов в первых областях 27 и 28 МОП-структур обоих типов, электрически связаны с крайними со стороны четвертой полоски 34 затворов областями истоков вторых областей 29 и 30 МОП-структур аналогичных типов. Области стоков, расположенные между второй и третьей полосками 32 и 33 затворов в первой области 27 р-МОП-структур и между третьей и четвертой полосками 33 и 34 затворов во второй области 30 n-МОП-структур, электрически связаны с инверсным выходом

В каждом элементе ИСКЛЮЧАЮЩЕЕ 2ИЛИ первого каскада (фиг. 6) третья полоска 33 затворов электрически связана с областями стоков-истоков, расположенными между первой и второй полосками 31 и 32 затворов в первых областях 27 и 28 МОП-структур обоих типов. Четвертая полоска 34 затворов соединена с областями стоков-истоков, расположенными между второй и третьей полосками 32 и 33 затворов во вторых областях 29 и 30 р- и n-МОП-структур.

У элементов ИСКЛЮЧАЮЩЕЕ 2ИЛИ следующих каскадов (фиг. 10) третья и четвертая полоски 33 и 34 затворов соответственно подключены к первому и второму инверсным входам

В элементе ИСКЛЮЧАЮЩЕЕ 2ИЛИ с одним прямым входом и одной парой из прямого и инверсного входов (фиг. 14) третья полоска 33 затворов электрически связана с областями стоков-истоков, расположенными между первой и второй полосками 31 и 32 затворов в первых областях 27 и 28 МОП-структур обоих типов. Четвертая полоска 34 затворов подключена ко второму инверсному входу Y элемента.

Конструктивное выполнение элементов ИСКЛЮЧАЮЩЕЕ 2ИЛИ дает возможность повысить плотность размещения этих элементов на поверхности кристалла при интегральном исполнении устройства. На фиг. 15 и 16 показаны фрагменты компоновки массивов элементов первого и последующих каскадов устройства, позволяющей минимизировать шаг размещения МОП-транзисторных структур за счет двухрядного размещения областей МОП-структур, уменьшения площади изолирующих областей и совмещения подключенных к шинам питания областей истоков соседних МОП-структур.

Таким образом, устройство для контроля параллельного N-разрядного двоичного кода на четность имеет в своем составе КМОП логические элементы ИСКЛЮЧАЮЩЕЕ 2ИЛИ в количестве N-1, в общем содержащие 7(N-1) пар КМОП-транзисторов. Элементы связаны в древовидную цепь, в которой критический путь распространения сигналов от входов до выходов составляет последовательность из инвертора и логических КМОП-вентилей вида 2(2И)-2ИЛИ-НЕ, число которых равно ⎡log2N⎤. Схемотехническое и конструктивное выполнение элементов устройства позволяет повысить плотность его упаковки в интегральном исполнении.

Реферат

Полезная модель относится к импульсной технике и предназначена для использования в интегральных микросхемах счетных и управляющих устройств на комплементарных полевых транзисторах структуры металл-окисел-полупроводник (КМОП). Техническим результатом является уменьшение количества транзисторов и площади, занимаемой устройством на поверхности кристалла. Устройство содержит элементы ИСКЛЮЧАЮЩЕЕ 2ИЛИ в количестве, равном числу разрядов контролируемого кода N за вычетом одного, образующие древовидную цепь, состоящую из нескольких каскадов, число которых K равно округленному до ближайшего большего целого значению логарифма по основанию два от N, то есть K=⎡log2N⎤, при этом каждый элемент ИСКЛЮЧАЮЩЕЕ 2ИЛИ состоит из семи МОП-транзисторов обогащенного типа с индуцированным каналом р-типа проводимости и семи МОП-транзисторов обогащенного типа с индуцированным каналом n-типа проводимости. 16 ил.

Формула

Документы, цитированные в отчёте о поиске

Устройство пирамидальной структуры для детектирования групп нулевых и единичных бит и определение их количества

Комментарии