Генератор случайного полумарковского процесса с симметричными законами распределения - RU170412U1

Код документа: RU170412U1

Чертежи

Описание

Полезная модель относится к вычислительной технике и может быть использована при построении имитационных моделей систем, работающих в условиях случайных возмущений, настройке и эксплуатации различных устройств автоматики.

Известен генератор случайных интервалов с симметричными законами распределения (Патент на полезную модель №156596 от 16.10.2015 г.), работа которого основана на преобразовании случайного числа, распределенного но заданному вероятностному закону, в случайный интервал.

Известен генератор случайного полумарковского процесса (SU 1377853 от 07.08.1986), работа которого основана на преобразовании случайного числа, распределенного по заданному вероятностному закону, в случайный интервал.

Наиболее близким по технической сущности к предлагаемому техническому решению является генератор случайного полумарковского процесса, содержащий блок синхронизации, первый выход которого подключен к входу синхронизации первого регистра памяти, выход которого является выходом генератора, выход первого регистра памяти соединен с информационным входом второго регистра памяти, выход которого подключен к первому адресному входу первого блока памяти, второй адресный вход которого соединен с выходом третьего регистра памяти, информационный вход которого соединен с выходом датчика равномерно распределенных случайных чисел, выход первого блока памяти соединен с информационным входом первого регистра памяти, три ключа, элемент ИЛИ-НЕ, второй блок памяти, счетчик, блок ключей, элемент ИЛИ, первый вход которого соединен с вторым выходом блока синхронизации, выход элемента ИЛИ соединен с входом "Опрос" датчика равномерно распределенных случайных чисел, выход которого соединен с информационным входом блока ключей, выход которого соединен с адресным входом второго блока памяти, выход которого соединен с выходом предварительной установки счетчика, счетный вход которого соединен с первым входом блока синхронизации, выход счетчика подключен к входу элемента ИЛИ-НЕ, выход которого соединен с управляющими входами первого, второго и третьего ключей, информационные входы первого и второго ключа объединены и подключены к третьему входу блока синхронизации, четвертый выход которого подключен к информационному входу третьего ключа, выход которого подключен к входу синхронизации третьего регистра памяти, выход первого ключа соединен с вторым входом элемента И, выход второго ключа подключен к управляющему входу блока ключей и к входу синхронизации второго регистра памяти (SU 1377853 от 07.08.1986).

Недостатком прототипа, проявляющимся при моделировании случайных интервалов, распределенных по симметричным относительно математического ожидания законам распределения, является высокая стоимость, обусловленная использованием блока памяти неоправданно большого объема и большой разрядности ячеек памяти.

Для достижения высокой точности моделирования распределения вероятностей интервалов количество ячеек памяти должно выбираться достаточно большим. Это существенно удорожает устройство, так как блок памяти является наиболее дорогостоящим элементом стохастических устройств подобного типа, а стоимость изготовления и программирования блоков памяти монотонно растет с увеличением количества ячеек памяти.

Техническим результатом, получаемым в данном техническом решении, является упрощение генератора случайного полумарковского процесса путем уменьшения количества ячеек блока памяти, в котором задаются длительности моделируемого случайного процесса, в 2 раза и уменьшения их разрядности.

Технический результат достигается тем, что в генератор случайного полумарковского процесса с симметричными законами распределения содержащий блок синхронизации, первый выход которого подключен к входу синхронизации первого регистра памяти, выход которого является выходом генератора, выход первого регистра памяти соединен с информационным входом второго регистра памяти, выход которого подключен к первому адресному входу первого блока памяти, второй адресный вход которого соединен с выходом третьего регистра памяти, информационный вход которого соединен с выходом датчика равномерно распределенных случайных чисел, выход первого блока памяти соединен с информационным входом первого регистра памяти, три ключа, элемент ИЛИ-НЕ, второй блок памяти, счетчик, блок ключей, элемент ИЛИ, первый вход которого соединен с вторым выходом блока синхронизации, выход элемента ИЛИ соединен с входом "Опрос" датчика равномерно распределенных случайных чисел, выход которого соединен с информационным входом блока ключей, счетчик, счетный вход которого соединен с первым входом блока синхронизации, выход счетчика подключен к входу элемента ИЛИ-НЕ, выход которого соединен с управляющими входами первого, второго и третьего ключей, информационные входы первого и второго ключа объединены и подключены к третьему входу блока синхронизации, четвертый выход которого подключен к информационному входу третьего ключа, выход которого подключен к входу синхронизации третьего регистра памяти, выход первого ключа соединен с вторым входом элемента И, выход второго ключа подключен к управляющему входу блока ключей и к входу синхронизации второго регистра памяти, введен сумматор-вычитатель, выход которого соединен с информационным входом счетчика, а управляющий вход соединен со старшим разрядом блока ключей, причем первый вход сумматора-вычитателя соединен с выходом блока памяти, а второй вход является входом генератора, через который вводится требуемое среднее значение длительности интервалов.

Введение новых признаков и связей между ними, отличающих заявленное решение от прототипа, в своей совокупности дает возможность упростить генератор путем использования блока памяти с уменьшенным в два раза количеством ячеек с меньшим количеством разрядов.

Сущность технического решения заключается в том, что при моделировании случайных интервалов, распределенных по симметричным относительно математического ожидания вероятностным законам (усеченному Гауссовскому. Коши и т.д.), нет необходимости хранить в блоке памяти все числа из диапазона возможных значений, а достаточно, во-первых, их центрировать и, во-вторых, оставить лишь половину центрированных чисел, например положительных. Первая мера позволяет уменьшить разрядность ячеек блока памяти, а вторая - количество ячеек блока памяти в два раза.

Каждое из таких центрированных положительных чисел xi записано в mi ячеек блока памяти

mi=]2N-1 рi[,

где pi - вероятность появления числа xi в соответствии с законом распределения;

]•[ - знак округления до целого числа;

N - разрядность датчика равномерно распределенных случайных чисел;

N-1 - разрядность адресной шины блока памяти.

Всего блок памяти содержит 2N-1 ячеек, т.е. в 2 раза меньше, чем общее количество 2N комбинаций на выходе датчика равновероятных случайных кодов. Для половины комбинаций равновероятных кодов (при нулевом уровне в старшем разряде) случайные числа, выбираемые из блока памяти, соответствуют положительной половине центрированного распределения, для другой половины кодов (при единичном уровне в старшем разряде) эти же числа представляются в обратном коде и соответствуют отрицательной половине центрированного распределения. После суммирования полученных чисел с математическим ожиданием, в результате получаются числа с заданным вероятностным распределением, с помощью которых моделируются случайные интервалы.

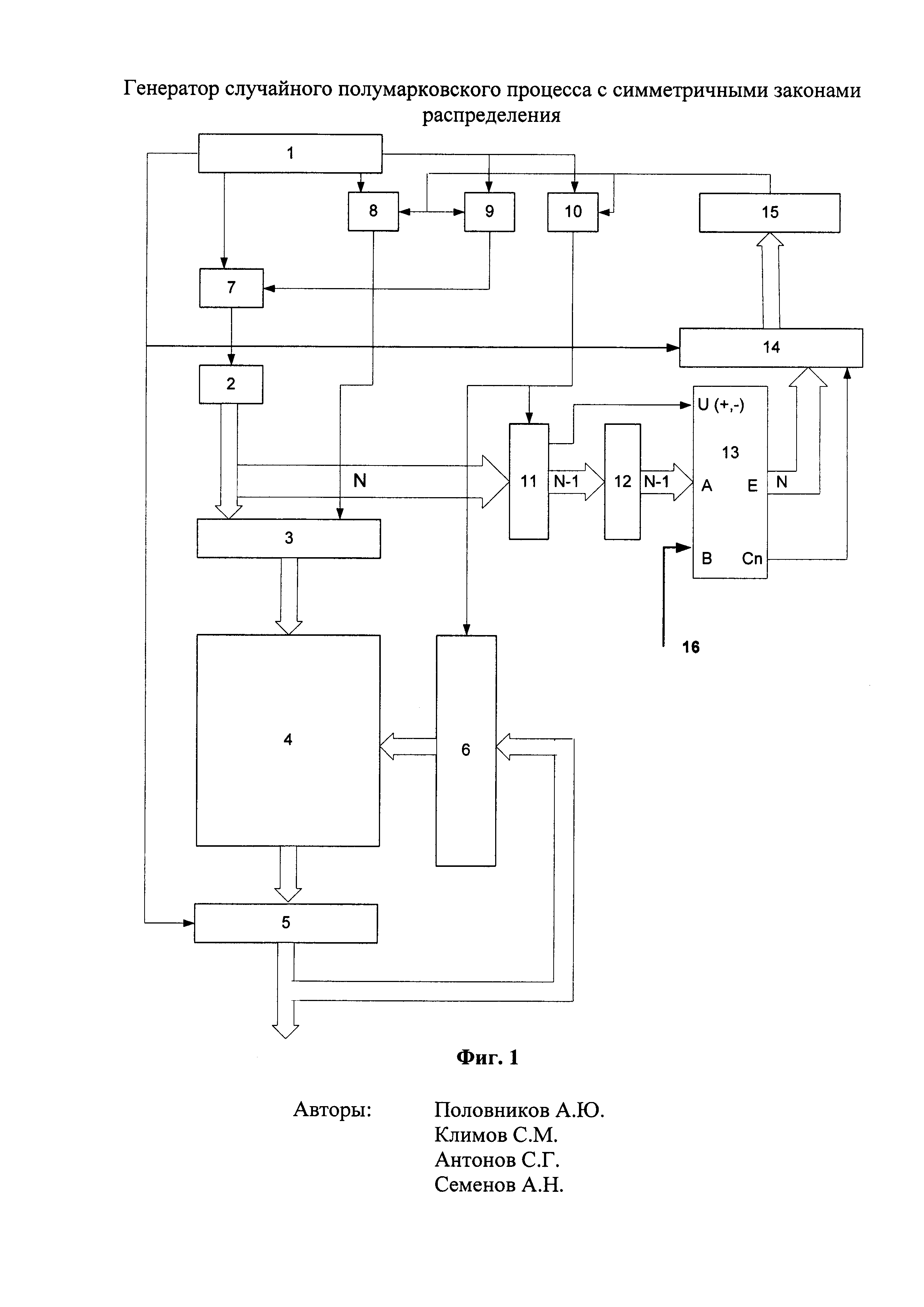

На фиг. 1 изображена функциональная схема генератора. Генератор случайного полумарковского процесса с симметричными законами распределения стоит из блока 1 синхронизации, датчика 2 равномерно распределенных случайных чисел, регистров 3-6, элемента ИЛИ 7, ключей 8-10, блока 11 ключей, блока 12 памяти, сумматора-вычитателя 13, регистра 14, элемент ИЛИ-НЕ 16. Блок 1 содержит генератор тактовых импульсов и счетчик аналогично прототипу,

Сумматор-вычитатель 13 в зависимости от сигнала на управляющем входе производит операции сложения или вычитания. Если на управляющем входе сумматора-вычитателя нулевой уровень, то он производит сложение двух кодов, поступающих на его входы, если на управляющем входе единичный уровень, то сумматор-вычитатель вычитает из числа, поступившего на второй вход, число, поступившее на первый вход. (Алексеенко А.Г., Шагурин И.И. Микросхемотехника: Учеб. пособие для ВУЗов под ред. И.Л. Степаненко. - М.: Радио и связь, 1982. - 416 с. (стр. 124)).

Генератор работает следующим образом.

Пусть моделируется случайный процесс с n состояниями. В каждом из состояний процесс может находиться I тактов, причем I - дискретная случайная величина с распределением вероятностей W(I). Вероятности перехода из i-го состояния в к-е заданы матрицей {Рik}, причем

Заданная вероятность перехода моделируемого процесса из одного состояния в другое обеспечивается специальной конструкцией блока 4 памяти. Длительность состояний процесса, подчиненная требуемому закону распределения, формируется путем подсчета количества тактов работы генератора в счетчике 14 и сравнения подсчитанного количества с распределенным по заданному закону числом, формируемым на выходе сумматора-вычитателя 13.

Каждая i-я строка блока 4 памяти содержит 2m ячеек, где m - разрядность случайного числа на выходе датчика 2, причем каждая из них рассчитана на хранение целого числа, не превышающего n. Все 2m ячеек разбиты на n групп таким образом, что количество ячеек аik,

Сигнал с блока 10 открывает блок ключей 11 и подает случайный код от датчика 2 равномерно распределенных случайных кодов на блок памяти 12. Если случайный код, являющийся адресом некоторой ячейки блока памяти 12 имеет в старшем разряде нулевой уровень, то считываемый код из блока памяти 12 поступает на первый вход сумматора-вычитателя 13 и складывается с кодом математического среднего значения длительности интервалов (вход 16), т.к. на управляющем входе сумматора-вычитателя 13 присутствует нулевой уровень. Если же в старшем разряде адреса присутствует единица, то число, считываемое из блока памяти 12, поступает на сумматор-вычитатель 13 и вычитается из кода среднего значения длительности интервалов, поскольку на управляющем входе сумматора-вычитателя присутствует единичный уровень.

Случайное число с выхода сумматора-вычитателя 13 заносится в счетчик 14, где осуществляется преобразование его во временной интервал.

Очевидно, что интервалы времени Ti между сигналами обнуления счетчика 14 будут случайными и распределенными по закону распределения, идентичному закону распределения кодов xi, записанных в блоке памяти 12.

Таким образом, введение новых признаков позволяет генерировать случайный полумарковский процесс, используя генератор с блоком памяти, имеющим в два раза меньшее количество ячеек, чем в прототипе, а также их меньшую разрядность.

Регистр 3 предназначен для хранения случайного числа, являющегося номерам (адресом) столбца блока 4 памяти. Регистр 6 предназначен для хранения номера (адреса) строки блока 4 памяти. В регистре 5 хранится считанный из матричной памяти номер состояния генерируемого процесса.

В начальный момент времени до прихода первого тактирующего сигнала от блока 1 регистр 5 устанавливается в начальное состояние, регистры 3, 6 и счетчик 13 устанавливаются в нулевое состояние. На выходе элемента ИЛИ-НЕ появляется "1" и ключи 8-10 открыты. Блок 1 начинает выдавать на своих выходах тактирующие сигналы. Сигнал с второго выхода блока 1 через элемент ИЛИ 7 инициирует работу датчика 2 случайных чисел, на выходе которого появляется m-разрядное двоичное число rt1=Сt12m. Сигнал с четвертого выхода блока 1 через открытый ключ 8 инициирует запись величины Сt1 в регистр 3 памяти. Величина Сt1' является номером столбца блока 4 памяти. Сигнал с третьего выхода блока 1 через открытый ключ 10 инициирует запись в регистр 6, хранящуюся в регистре 5 (согласно начальной установке этот номер равен i). По номеру столбца Ct1 и номеру строки (i) в блоке 4 памяти возбуждается ячейка, содержимое которой и будет равно номеру состояния генерируемого процесса. Предположим, что это состояние имеет номер k. Вероятность реализации k-го состояния при условии, что в регистре 6 содержится номер i, будет равна Pik. Действительно, выбор из матричной памяти k-го номера состояния означает, что величина Ct попала в k-ю группу ячеек i-й строки. В k-й группе содержится aik ячеек.

Вероятность того, что равномерно распределенное в интервале [0-1] число примет одно из aik значений, равна aik/2m=Pik.

Одновременно с выбором из блока 4 памяти номера состояния сигнал с третьего выхода блока 1 открывает блок 11 ключей и через открытый ключ 9 и элемент ИЛИ 7 инициирует работу датчика 2 случайных чисел. Случайное число Ct1 через блок 11 ключей поступает на вход 12 блока памяти, где преобразуется в число 1, которое заносится в вычитающий счетчик 14. На входе элемента ИЛИ-НЕ 15 появляется "0" и ключи 8-10 закрываются.

Сигнал с первого выхода блока 1 обеспечивает запись выбранного из блока 4 памяти номера состояния выходного регистра 5, разрядные выходы которого являются выходом всего устройства. Одновременно этот же сигнал поступает на вход счета счетчика 14 и уменьшает его содержимое на единицу. На пятом такте генератора тактирующих сигналов счетчик-делитель блока синхронизации 1 приходит в исходное состояние, и первый такт работы генератора случайного полумарковского процесса с симметричными законами распределения заканчивается.

Работа генератора на следующем такте зависит от значения числа, содержащегося в счетчике 14. Если содержимое счетчика равно нулю, то на выходе элемента ИЛИ-НЕ 15 присутствует "1", ключи 8-10 открыты, и работа генератора протекает описанным образом. Если содержимое счетчика больше нуля, то на выходе элемента ИЛИ-НЕ сохраняется "0" и ключи 8-10 закрыты. Сигнал со второго выхода блока управления через элемент ИЛИ 7 инициирует работу датчика 2. Однако сигнал с четвертого выхода блока 1 через закрытый ключ 8 не проходит и содержимое регистра 3 остается таким же, как и на предыдущем такте. Сигнал с третьего выхода блока 1 также не проходит через закрытый ключ 10 и поэтому, во-первых, содержимое регистра 6 остается прежним, во-вторых, случайное число с выхода датчика 2 через блок 11 ключей не проходит на адресный вход блока 12 и не оказывает влияния на содержимое счетчика 14. Сигнал с первого выхода блока 1 уменьшает содержимое счетчика 14 на единицу и инициирует запись в регистр 5 содержимого выбранной на этом такте ячейки блока 4 памяти.

Поскольку номера столбца и строки, хранящиеся в регистрах 3, 5, не изменились, то считывание произойдет из той же самой ячейки, что и на предыдущем такте, а значит, и номер состояния генерируемого процесса не изменится.

Состояние моделируемого процесса на выходе устройства будет оставаться неизменным до тех пор, пока содержимое счетчика 14 больше нуля. Поскольку занесенное в счетчик 14 число распределено по закону W(I), то количество тактов, на которых состояние моделируемого процесса будет неизменным, также распределено по закону W(I).

Технико-экономический эффект от использования полезной модели определяется использованием блока памяти меньшего объема, а следовательно, более дешевого.

Реферат

Полезная модель относится к области вычислительной техники и может быть использована при построении имитационных моделей систем, работающих в условиях случайных возмущений, настройке и эксплуатации различных устройств автоматики.Техническим результатом, получаемым в данном техническом решении, является упрощение генератора случайного полумарковского процесса путем уменьшения количества ячеек блока памяти, в котором задаются длительности моделируемого случайного процесса, в 2 раза и уменьшения их разрядности.Технический результат достигается тем, что в генератор случайного полумарковского процесса с симметричными законами распределения, содержащий блок синхронизации, первый выход которого подключен к входу синхронизации первого регистра памяти, выход которого является выходом генератора, выход первого регистра памяти соединен с информационным входом второго регистра памяти, выход которого подключен к первому адресному входу первого блока памяти, второй адресный вход которого соединен с выходом третьего регистра памяти, информационный вход которого соединен с выходом датчика равномерно распределенных случайных чисел, выход первого блока памяти соединен с информационным входом первого регистра памяти, три ключа, элемент ИЛИ-НЕ, второй блок памяти, счетчик, блок ключей, элемент ИЛИ, первый вход которого соединен с вторым выходом блока синхронизации, выход элемента ИЛИ соединен с входом "Опрос" датчика равномерно распределенных случайных чисел, выход которого соединен с информационным входом блока ключей, счетчик, счетный вход которого соединен с первым входом блока синхронизации, выход счетчика подключен к входу элемента ИЛИ-НЕ, выход которого соединен с управляющими входами первого, второго и третьего ключей, информационные входы первого и второго ключа объединены и подключены к третьему входу блока синхронизации, четвертый выход которого подключен к информационному входу третьего ключа, выход которого подключен к входу синхронизации третьего регистра памяти, выход первого ключа соединен с вторым входом элемента И, выход второго ключа подключен к управляющему входу блока ключей и к входу синхронизации второго регистра памяти, введен сумматор-вычитатель, выход которого соединен с информационным входом счетчика, а управляющий вход соединен со старшим разрядом блока ключей, причем первый вход сумматора-вычитателя соединен с выходом блока памяти, а второй вход является входом генератора, через который вводится требуемое среднее значение длительности интервалов. 1 ил.

Комментарии