Устройство для формирования периодических функций - SU414822A3

Код документа: SU414822A3

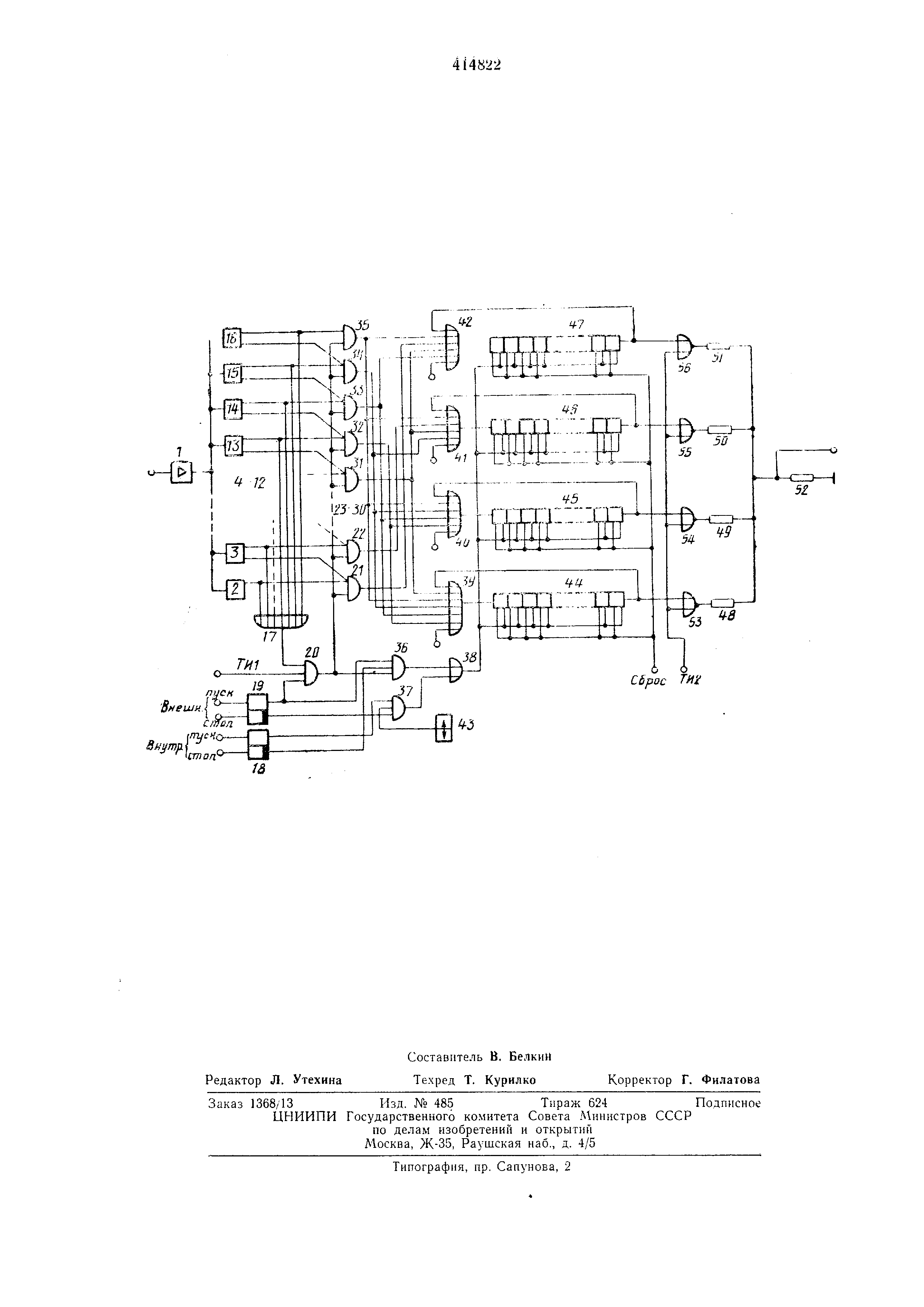

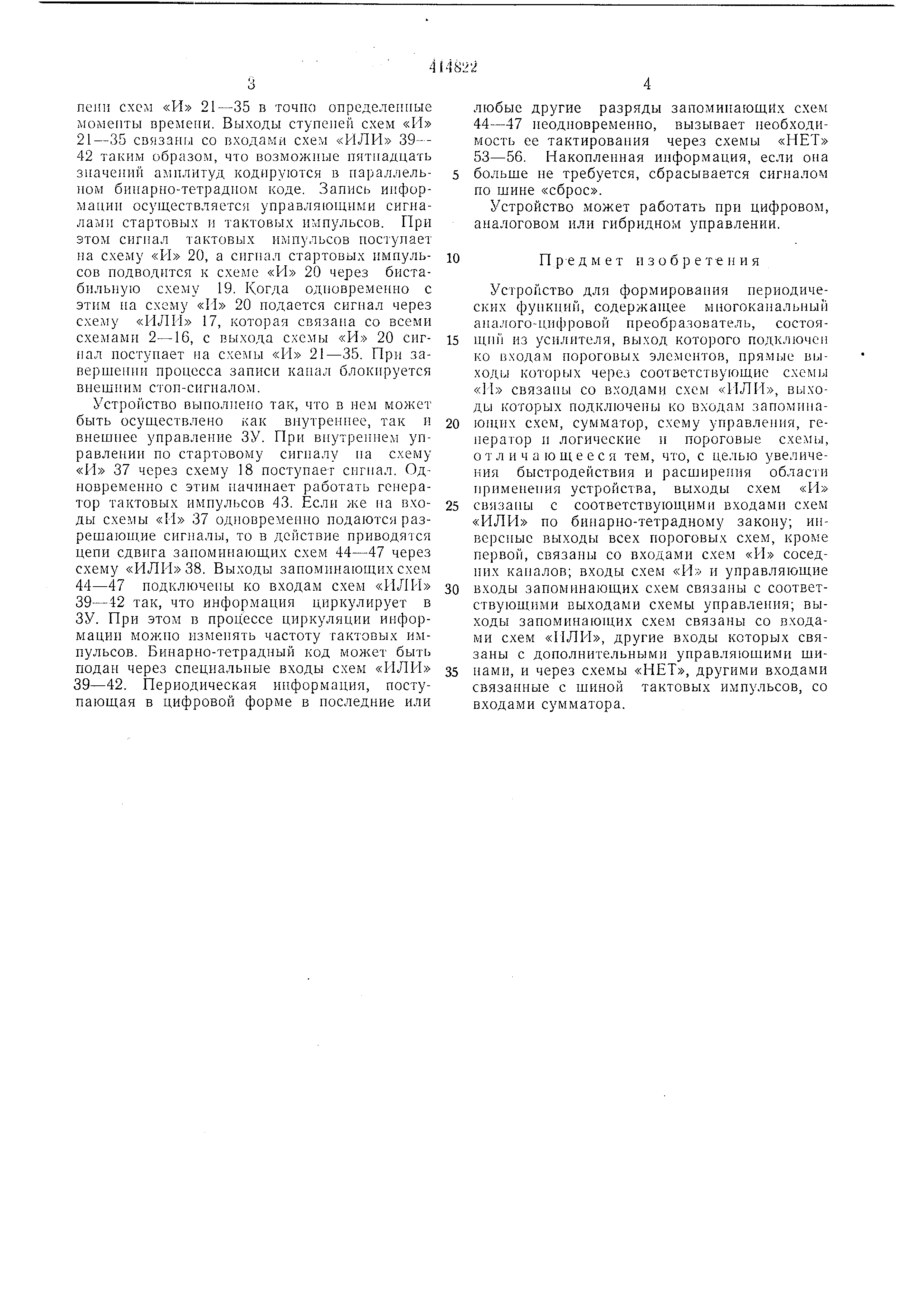

Чертежи

Описание

1

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при реализации технических средств автоматики и аналоговых вычислительных машин.

Известно устройство для формирования периодических функций, содержащее многоканальный аналого-цифровой преобразователь, состоящий из усилителя, выход которого подключен ко входам пороговых схем, прямые выходы которых через соответствующие схемы «И, связаны со входами схем «ИЛИ, выходы которых подключены ко входам запоминающих схем, резистивный сумматор, схему управления, генератор и логические схемы.

Однако известные устройства имеют малое быстродействие и не позволяют формировать сигналы нужной формы с регулируемым периодом повторения.

Предложенное устройство отличается тем, что в нем выходы схем «И связаны с соответствующими входами схем «ИЛИ по бинарно-тетрадному закону. Инверсные выходы всех пороговых схем, кроме первой, связаны со входами схем «И соседних каналов, входы схем «И и управляющие входы запомилающих схем соединены с соответствующими выходами схемы управления. Выходы запоми2

нающих схем связаны со входами схем «ИЛИ, другие входы которых связаны с дополнительными управляющими шинами, и через схемы «НЕТ, другими входами связанные с шиной тактовых импульсов, со входами сумматора.

Блок-схема предложенного устройства представлена на чертеже. Устройство содержит усилитель 1, пороговые схемы 2-16, схему «ИЛИ 17, бистабильные схемы 18, 19, схемы «И 20-37, схемы «ИЛИ 38-42, генератор 43, запоминающие 44-47, резистивный сумматор 48-52.

Схемы «1-Ь 20, 36, 37, схема «ИЛИ 38 и бистабильные схемы 18 и 19 составляют схему управления.

Предложенное устройство работает следующим образом.

Входная информация в аналоговой форме через усилитель 1 поступает на входы расположенных в определенной последовательности пороговых схем 2-16 на пороговых схемах 3-11 определяется величина амплитуды приложенного аналогового сигнала. Тактовый сигнал проходит от лпнии тактовых импульсов через логическую схему «И 20, так что передача информации происходит через ступени схем «И 21-35 в точно определенные моменты времени. Выходы стуненей схем «И 21-35 связаны со входами схем «ИЛИ 39-42 таким образом, что возможные пятнадцать значений амплитуд кодируются в нараллельном бинарно-тетрадном коде. Запись информании осуществляется управляющими сигналами стартовых и тактовых имнульсов. При этом спгпал тактовых импульсов ностунает на схему «PI 20, а сигнал стартовых импульсов подводится к схеме «И 20 через бистабильиую схему 19. Когда одновременно с этим на схему «И 20 нодается сигнал через схему «ИЛИ 17, которая связана со всеми схемами 2-16, с выхода схемы «И 20 сигнал постуиает иа схемы «И 21-35. При заверщенни процесса записи канал блокируется внеилним с1оп-сигиалом.

Устройство выполнено так, что в нем может быть осуществлено как внутреннее, так и внешнее управление ЗУ. При внутреннем управлении по стартовому сигиалу на схему «И 37 через схему 18 поступает сигнал. Одновременно с этнм начинает работать генератор тактовых импульсов 3. Если же на входы схемы «И 37 одновременно подаются разрешаюн1 ,ие сигналы, то в действие приводятся цепи сдвига запоминающих схем 44-47 через схему «ИЛИ 38. Выходы запоминающих схем 44-47 иодключены ко входам схем «ПЛИ 39-42 так, что информация циркулирует в ЗУ. При этом в процессе циркуляции информации можно измепять частоту тактовых импульсов . Бинарно-тетрадный код может быть подан через специальные входы схем «ПЛП 39-42. Периодическая информация, поступающая в цифровой форме в последние или

любые другие разряды запоминающих схем 44-47 иеодиовременно, вызывает необходимость ее тактирования через схемы «ПЕТ 53-56. Пакоплеиная информация, если она больше не требуется, сбрасывается сигналом по шине «сброс.

Устройство может работать при цифровом, аналоговом или гибридном управлении.

Предмет изобрет-ения

Устройство для формирования периодических функций, содержаи.1,ее многоканальный аналого-н.ифровой преобразователь, состоящнй из усилителя, выход которого подключен ко входам иороговых элементов, прямые выходы которых через соответствующие cxeMi i «II связаны со входами схем «ПЛИ, выходы которых нодключены ко входам запомннаЮНП1Х схем, сумматор, схему управления, генератор и логические и пороговые схемы, отличающееся тем, что, с целью увеличения быстродействия и расширения области применения устройства, выходы схем «И

связаны с соответствующими входами схем «ИЛИ по бинарно-тетрадному закону; инверсные выходы всех пороговых схем, кроме первой, связаны со входами схем «И соседиих каналов; входы схем «И и унравляющие

входы запоминающих схем связаны с соответствующими выходами схемы управления; выходы заномииаюи1.их схем связаны со входами схем «ИЛИ, другие входы которых связаны с дополнительными управляющими шииами , и через схемы «ПЕТ, другими входами связанные с шиной тактовых импульсов, со входами сумматора.

чв

5f

Реферат

Формула

Комментарии