Преобразователь код - временной интервал - SU1736000A1

Код документа: SU1736000A1

Чертежи

Описание

Изобретение относится к автоматике и вычислительной технике и может использоваться в устройствах преобразования цифровой информации.

Цель изобретения - повышение точности формирования временного интервала .

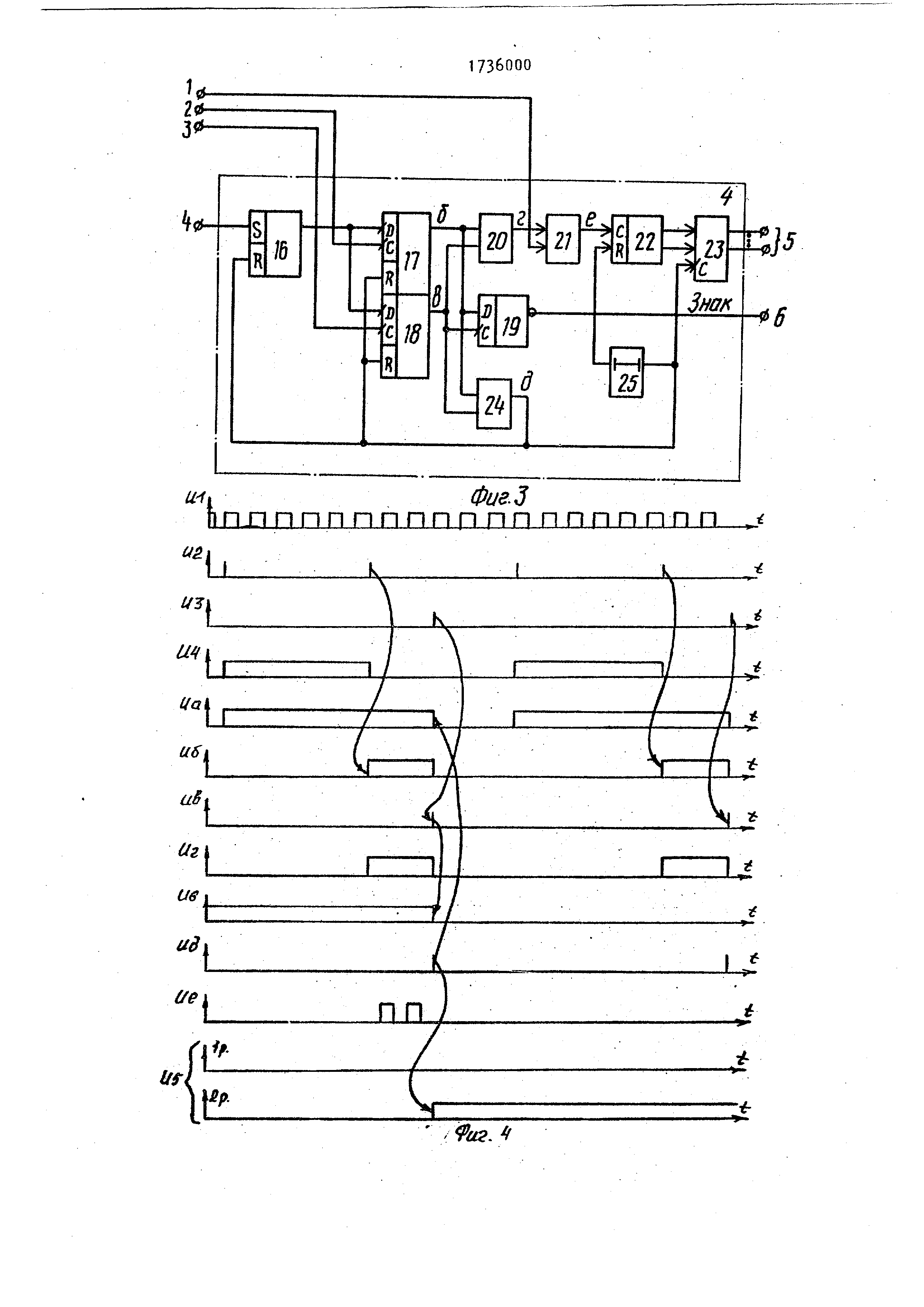

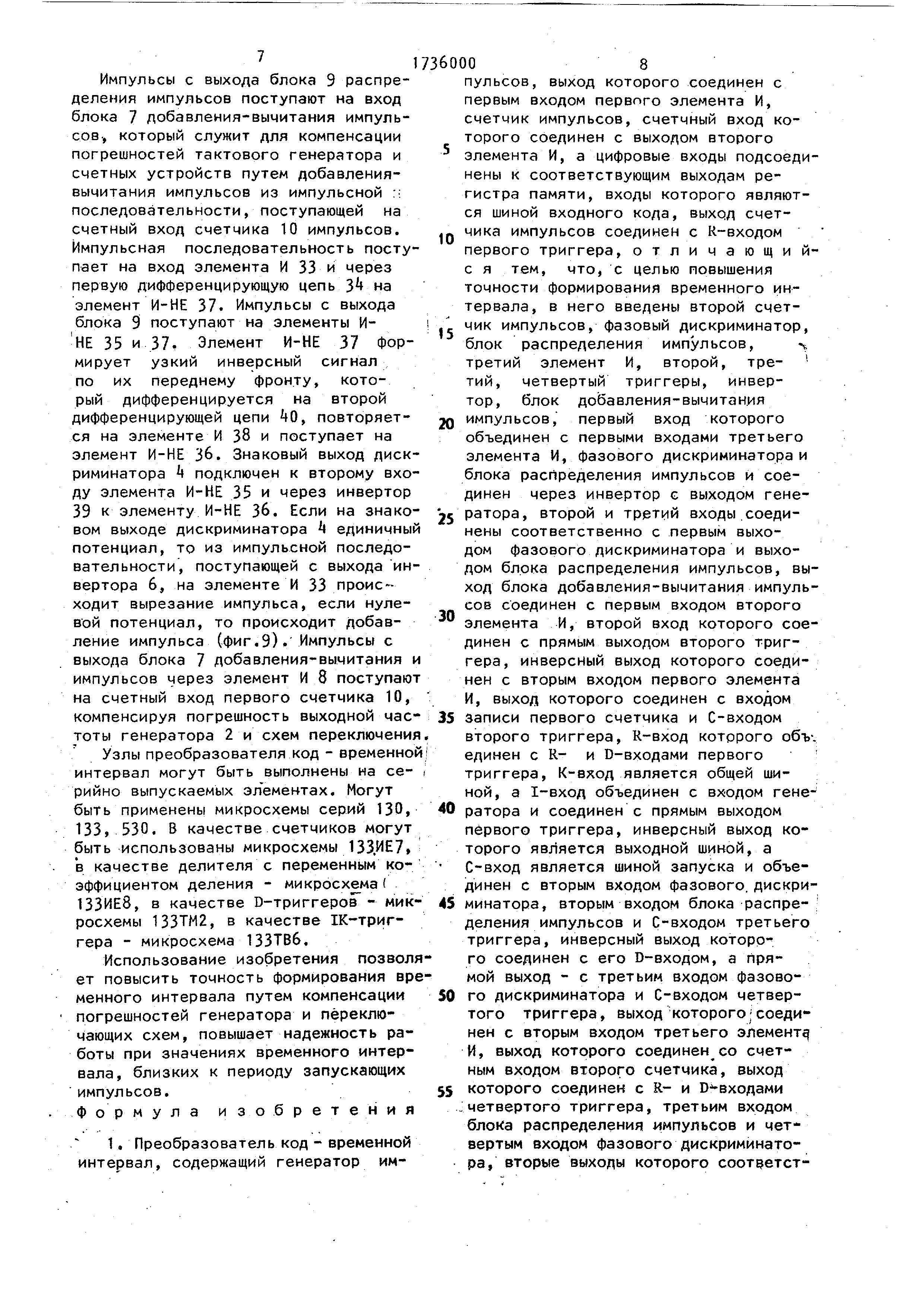

На фиг.1 приведена функциональная схема образователя; на фиг.2 - диаграммы работы преобразователя; на фиг.З - схема фазового дискриминато- оа; на фиг.k и 5 - временные диаграммы работы дискриминатора; на фиг.6 - схема блока распределения импульсов; на фиг.7 временные диаграммы рабо-з ты блока распределения; на фиг.8 - схема блока добавления-вычитания; на фиг.9 - временные диаграммы работы блока добавления-вычитания.

Преобразователь код - временной интервал содержит триггер 1, генератор 2 импульсов, триггер 3 фазовый дискриминатор , элемент И 5, инвертор 6, блок 7 добавления-вычитания импульсов, элемент И 8, блок 9 распрделения импульсов, счетчик 10 импульсов , регистр 11 памяти,триггер 12, счетчик 13 импульсов, триггер И и элемент И 15.

Фазовый дискриминатор Ь содержит RS-триггер 16, D-триггеры 17 и 18, D-триггер 19, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 20, элемент И 21, счетчик 22, регистр 23, элемент И 2 и линию 25 задержки.

Блок 9 распределения импульсов содержит делитель 26 с переменным коэффициентом деления, первый двоичный счетчик 27, регистр 28, линию 29 задержки, второй довичный вычитающий счетчик 30, элемент ИЛИ-НЕ 31 элемент ИЛИ 32.

Блок 7 добавления-вычитания импульсов содержит элемент И 33, дифференцирующую цепь 3, элементы И- НЕ , элементы И 38, инвертор 39 и дифференцирующую цепь fO.

Преобразователь работает следующим образом.

После установления в рабочее состояние, которое равно шести тактам запускающих импульсов, прямой выход триггера 1 находится в нулевом состоянии. Генератор 2 генерирует импульсы с произвольной фазой. По переднему фронту запускающего импульса триггеры 1 и 3 устанавливаются в единичное состояние. Триггер 3

0

5

разрешает работу фазового дискриминатора 4, инверсный выход триггера 1 формирует передний фронт временного интервала, а прямой выход фазирует генератор 2 импульсов, который формирует передний фронт тактовых импульсов , которые поступают на элемент И 5 и через инвертор 6 на блок 7 добавления-вычитания импульсов, элемент И 15, фазовый дискриминатор k, блок 9 распределения импульсов.

Первый импульс через элемент И 5 проходит на вход записи счетчика 10 и производит запись информации из регистра 11 памяти в счетчик, Счетчик 10 импульсов преобразователя работает на принципе досчета до переполнения, и запись информации в связи с этим

0 производится в обратном коде за

время длительности тактового импульса , Задним фронтом первого импульса триггер 12 переводится в единичное состояние, инверсным выходом запре5 Щая прохождение импульсов записи и прямым разрешая прохождение тактовых импульсов через элемент И 8 на счетный вход счетчика 10, которые поступают через блок, 7 и инвертор 6 с выхода генератора 2. Таким образом, счетчик 10 начинает счет с отставанием на полтакта по отношению к перед нему фронту временного интервала, сформированного триггером 1.

Одновременно со счетчиком 10 начинает счет счетчик 13, так как rep разрешает прохождение импульсов через элемент И 15, тактовые импульсы поступают также на фазовый дискриминатор и блок распределения импульсов. Счетчики 10 и 13 следует выполнять на счетчиках с параллельным переносом, так как в этом случае задержки переключения счетных триггеров в счетчике минимальны. Особенность данных счетчиков заключается в том, что импульс переноса в них формируется за полтакта до окончания заполнения счетчика, тем самым счетчик 10 за полтакта до переполнения

0 формирует импульс переноса и обнуляет передним фронтом триггеры 1 и 12, тем самым выравнивая отставание счета счетчика.

Инверсный выход триггера 1 форми5 рует задний фронт временногоi интервала , генератор 2 продолжает свою работу, счетчик 13 продолжает считать импульсы генератора. Если погреш0

5

0

5

ности генератора и счетчика отсутствуют или меньше чувствительности фазового дискриминатора, то импульс переполнения счетчика 13 должен совпасть со следующим импульсом запуска обнуляя триггер k, тем самым запрещая прохождение импульсов счета, занося нулевую информацию в блок распределения импульсов, а блок добавления-вычитания импульсов пропускает импульсную последовательность с выхода генератора 2 без изменения.

Если существуют погрешности, то фазовый дискриминатор вырабатывает цифровой код фазового рассогласовани между импульсом переполнения счетчика 13 и вторым запускающим импульсом следукщим образом. С выхода D-триггера З приходит сигнал разрешения работы на S-вход КЗ-триггера 16. Он устанавливается в единичное состояние. Запускающий импульс устанавливает D-триггер 17 в единичное состояние, импульс переполнения счетчика 13 также устанавливает в единичное состояние D-триггер 18. Выход D-триггера 18 подключен к С-входу D-триггера 19, Ь-вход которого подключен к выходу D-триггера 17. Если импульс переполнения счетчика 13 придет позже импульса запуска, то инверсный выход D-триггера 19 установится в нулевое состояние, если раньше - то в единичное. Тем самым осуществляется определение знака погрешности .

Временное рассогласование между импульсами запуска и импульсами переполнения определяет элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 20, который подключен к выходам D-триггеров 17 и 18. Элемент И 21 вырабатывает серию импульсов частоты тактового генератора 2 и длительностью, равной временному рассогласованию между импульсами запуска и импульсами переполнения счетчика 13. которая поступает на вход счетчика 22, преобразующего последовательность в двоичный код, который поступает на вход регистра 23, выходы которого являются выходами фазового дискриминатора. Элемент И 2 в момент установки триггеров 17 и 18 в единичное состояние формирует импульс окончания временного рассогласования , который обнуляет триггеры 16 - 18, а также производит занос кода в регистр 23. Линия 25 задержки осуществляет временную задержку им0

5

0

5

пульса окончания временного россоглт- сования и обнуляет счетчик 22. Временные диаграммы работы фазового дискриминатора k приведены на фиг. | и Ь. ,i

Код с выхода фазового дискриминатора k поступает на блок 9 распределения импульсов, который служит для равномерного распределения импульсов фазового рассогласования на формируемом временном интервале. Код величи ны погрешности преобразования поступает на делитель 26 с переменным коэффициентом деления,на него также поступают импульсы тактовой частоты и импульсы с выхода переполнения счетчика 13, которые осуществляют занос кода в делитель. На выход делителя |2б пооходит число импульсов, пропор |циональчое записанному коду. Например, если код равен двум, то проходит каждый второй импульс тактовой последовательности , если десяти - то десятый . Импульсы поступают на счетчик

27,где преобразуются в параллельный код, который поступает в регистр

28.Следующим импульсом переполнения счетчика 13 происходит занос кода в регистр 28 и обнуление счетчика 2 импульсом, сформированным элементом

29задержки. Код с выхода регистра 28 поступает на вычитающий двоичный счетчик 30. Если временного рассогласования нет и код регистра 28 равен нулю, то элемент ИЛИ-НЕ 31 формирует сигнал обнуления счетчика 30. Если код не равен нулю, то импульсом запуска он заносится в счетчик, на вычитающий вход которого поступает частота тактового генератора . Счетчик начинает обратный счет, формируя сигнал заема, который одновременно является выходным сигналом блока 9 распределения импульсов и

5 производит перезапись кода в счетчик

30через элемент ИЛИ 32, на второй вход которого подается импульс запуска , осуществляющий синхронизацию начала распределения импульсов в

0 блоке 9. Таким образом, на выходе блока 9 распределения импульсов по приходу запускающего импульса вырабатываются равномерно распределенные импульсы, количество которых равно

5 коду погрешности. На фиг.7 для кода погрешности, равного двум, и периода запускающих импульсов, равного 16 тактовым импульсам, приведены временные диаграммы работы блока.

0

5

0

Импульсы с выхода блока 9 распределения импульсов поступают на вход блока 7 добавления-вычитания импульсов , который служит для компенсации погрешностей тактового генератора и счетных устройств путем добавления- вычитания импульсов из импульсной - последовательности, поступающей на счетный вход счетчика 10 импульсов. Импульсная последовательность поступает на вход элемента И 33 и через первую дифференцирующую цепь 3 на элемент И-НЕ 37. Импульсы с выхода блока 9 поступают на элементы И- НЕ 35 и 37. Элемент И-НЕ 37 Формирует узкий инверсный сигнал по их переднему фронту, который дифференцируется на второй дифференцирующей цепи 40, повторяется на элементе И 38 и поступает на элемент И-НЕ 36. Знаковый выход дискриминатора 1 подключен к второму входу элемента И-НЕ 35 и через инвертор 39 к элементу И-НЕ 36. Если на знаковом выходе дискриминатора 4 единичны потенциал, то из импульсной последовательности , поступающей с выхода инвертора 6, на элементе И 33 происходит вырезание импульса, если нулевой потенциал, то происходит добавление импульса (фиг.9). Импульсы с выхода блока 7 добавления-вычитания импульсов через элемент И 8 поступаю на счетный вход первого счетчика 10, компенсируя погрешность выходной частоты генератора 2 и схем переключени

Узлы преобразователя код - временно интервал могут быть выполнены на се- рийно выпускаемых элементах. Могут быть применены микросхемы серий 130, 133, 530. В качестве счетчиков могут быть использованы микросхемы 133.ИЕ7 в качестве делителя с переменным коэффициентом деления - микросхема( 133ИЕ8, в качестве D-триггеров - микросхемы 133ТМ2, в качестве 1К-триг- гера - микросхема 133ТВ6.

Использование изобретения позволет повысить точность формирования врменного интервала путем компенсации погрешностей генератора и переключающих схем, повышает надежность работы при значениях временного интервала , близких к периоду запускающих импульсов. Формула изобретения

1. Преобразователь код - временной интервал, содержащий генератор им

8

0

5

0

5

0

5

0

5

0

5

пульсов, выход которого соединен с первым входом первого элемента И, счетчик импульсов, счетчный вход которого соединен с выходом второго элемента И, а цифровые входы подсоединены к соответствующим выходам регистра памяти, входы которого являются шиной входного кода, выход счетчика импульсов соединен с К-входом первого триггера, отличающий- с я тем, что, с целью повышения точности формирования временного интервала , в него введены второй счетчик импульсов, фазовый дискриминатор, блок распределения импульсов, ч третий элемент И, второй, третий , четвертый триггеры, инвертор , блок добавления-вычитания импульсов, первый вход которого объединен с первыми входами третьего элемента И, фазового дискриминатора и блока распределения импульсов и соединен через инвертор с выходом генератора , второй и третий входы соединены соответственно с первым выходом фазового дискриминатора и выходом блока распределения импульсов, выход блока добавления-вычитания импульсов соединен с первым входом второго элемента И, второй вход которого соединен с прямым выходом второго триггера , инверсный выход которого соединен с вторым входом первого элемента И, выход которого соединен с входом записи первого счетчика и С-входом второго триггера, R-вход которого объ-. единен с R- и D-входами первого триггера, К-вход является общей шиной , а I-вход объединен с входом генератора и соединен с прямым выходом первого триггера, инверсный выход которого является выходной шиной, а Свход является шиной запуска и объединен с вторым входом фазового, дискриминатора , вторым входом блока распределения импульсов и С-входом третьего триггера, инверсный выход которого соединен с его D-входом, а прямой выход - с третьим входом фазового дискриминатора и С-входом четвертого триггера, выход которого;соединен с вторым входом третьего элементз И, выход которого соединен со счетным входом второго счетчика, выход которого соединен с R- и Выходами четвертого триггера, третьим входом блока распределения импульсов и четвертым входом фазового дискриминатора , вторые выходы которого соответственно соединены с четвертыми входаи блока распределения импульсов.

2,Преобразователь по п.1, о т- ичающийся тем, что фазовый искриминатор выполнен на RS-триг- ере, первом, втором, третьем D-три)- герах, элементе ИСКЛЮЧАЮЩЕЕ ИЛИ, первом , втором элементах И, двоичном счетчике импульсов, регистре,линии задержки, выход которой подключен к входу сброса счетчика импульсов, а вход - к выходу первого элемента И

и объединен с R-входами RS-триггера, первого и второго U-триггеров и с входом синхронизации регистра, цифровые выходы которого являются вторыми выходами фазового дискриминатора, а входы подключены соответственно к выходам двоичного счетчика, счетный вход которого подключен к выходу второго элемента И, первый вход которого является первым входом фазового дискриминатора , а второй вход подключен к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого подключен к выходу первого D-триггера и объединен с первым входом первого элемента И и D-входом третьего D-триггера, инверсный выход которого является первым выходом фазового дискриминатора ,а С-вход объединен с вторым входом первого элемента И, вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и соединен с выходом второго D-триггера, С-вход которого является четвертым входом фазового дискриминатора, а D-вход объединен с D-входом первого D-триггера и подключен к выходу RS-триггера, S-вход которого является третьим входом фазового дискриминатора , вторым входом которого является С-вход первого D-триггера.

3.Преобразователь по п.1, о т - личающийся тем, что блок распределения импульсов выполнен на делителе с переменным коэффициентом деления, первом двоичном счетчике, линии задержки, регистре, элементе. ИЛИ, элементе ИЛИ-НЕ, втором двоичном вычитающем счетчике, выход заема которого является выходом блока и подключен к первому входу элемента ИЛИ,второй вход которого является вто0

5

рым входом блока, выход подключен к входу синхронизации второго двоичного вычитающего счетчика, вход сброса которого соединен с выходом элемента ИЛИ-НЁ, входы которого объединены с соответствующими информационными входами второго двоичного вычитающего счетчика и соединены с соответствующими выходами регистра, вход синхронизации которого является третьим входом блока и объединен с входом записи делителя с переменным коэффициентом деления и входом линии

j задержки, выход которой соединен с входом сброса первого двоичного счетчика , выходы которого соединены с соответствующими информационными входами регистра, а счетный вход соединен с выходом делителя с переменным ко эффициентом деления, информационные входы которого являются четвертыми входами блока, а тактовый вход является третьим входом блока и подключен к входу вычитания второго двоичного вычитающего счетчика.

k. Преобразователь по п.1, о т- личающийся тем. что блок добавления-вычитания импульсов выполнен на инверторе, первой, второй дифференцирующих RC-цепях,первом, втором, третьем элементах И-НЕ, первом и втором элементах И, выход последнего из которых является выходом блока, первый вход является первым

5 входом блока и объединен с входом первой дифференцирующей RC-цепи, второй вход соединен с выходом первого элемента И-НЕ, третий вход соес выходом второго элемента НЕ, первый вход которого, через инвертор , является вторым входом блока и объединен -с первым входом первого элемента И-НЕ, второй вход соединен с выходом первого элемента И, пер5 вый и второй входы которого подключены к выходу второй дифференцирующей RC-цепи, вход которой подключен к выходу тртеьего элемента И-НЕ, первый вход которого объединен с вторым

0 входом первого элемента И-НЕ и является третьим входом блока, а второй вход соединен с выходом первой дифференцирующей RC-цепи.

0

динен 0 и.

Ъ 1

ппппппппппппвппппппппппппппппппг ,

JL

л

JL

JL

JL

JL

Реферат

Изобретение относится к автоматике и вычислительной технике, может использоваться в устройствах преобразования цифровой информации и позволяет повысить точность формирования временного интервала путем компенсации Погрешностей генератора импуль- |сов и задержек переключения счетных схем преобразователя. Преобразователь содержит счетчики 10, 13 импульсов , регистр памяти 11, триггеры 1, 3, 12,14, инвертор 6, до.бавле- ния-вычитания импульсов 7, элементы И 5,. 8, 15, фазовый дискриминатор 4, который вырабатывает код рассогласования и знак, генератор 2 импульсов, блок распределения импульсов 9, который распределяет импульсы погрешности равномерно по всему временному интервалу. Равномерно распределенные импульсы поступают на блок добавления-вычитания импульсов 7, а в зависимости от знака - в импульсной последовательности, поступающей на вход счетчика 10, или добавляется импульс или вычитается, тем самым осуществляется компенсация погрешностей генератора и задержек переключения счетных схем преобразователя. 3 з.п.ф-лы, 9 ил. о ©

Формула

Комментарии