1

Изобретение относится к устройству

для детектирования закодированно информации, особенно к устройству, в котором код хранится в активном

самоответчике. Такие устройства полезны при распознавании предметов или, например, для регулирования

входа персонала в зоны с ограниченным доступом.

Известны устройства для передачи сигналов на расстоянии, использующие

частотно-временной способ раделения каналов, содержащие на пункте управления формирователи команд

и аппаратуру передачи сигналов с частотным уплотнением, на каждом приемном пункте устройства содержат

декодер адреса в виде Фильтра и декодеры команд Cl.

Наиболее близким по технической сущности к предлагаемому является устройство для передачи и приема

сигналов, содержащее первый приемник , выход которого через детектор

соединен с первым входом блока логического сравнения и через последовательно соединенные инвертор,

преобразователь частоты и модулятор соединен с входом передатчика, выход преобразователя частоты через

счетчик подключен к первому входу Формирователя сигналов и к второму входу блока логического сравнения,

первый выход которого соединен с вторьам входом формирователя сигналов , выход которого подключен к

управляющему входу модулятора 23.

Недостаток известного устройств

заключается в том, что если код выбран, то его нельзя легко сменить

. Однако схема устройства технологически выполнена в виде чипа и представляет собой очень экономичный

способ производства в большом количестве указанных приемоответчиков

. Выгодно изготовлять такие приемоответчики, в которых кодиро вание можно было бы изменять по же5

ланию.

Цель изобретения - повышение информационной гибкости устройства,

т.е. создание дешевого, легкого приемоответчика массового произ0 водства с малым током потребления.

Указанная цель достигается тем, что в устройство для передачи и приема сигналов, содержащее первый

приемник, выход которого через де5 тектор соединен с первым входом блока

логического сравнения и через последовательно соединенные инвертор,

преобразователь частоты и модулятор соединен с входом передатчика, выход

преобразователя частоты через счетчик подключен к первому входу формирователя сигналрв и к второму

входу блока логического сравнения, первый выход которого соединен с

вторым входом формирователя сигналов , выход которого подключен к управляющему

входу модулятора, введены второй приемник и блок запрета, выход второго приемника подключен к

первому Bxofiy блока запрета, выход

0 блока запрета соединен с третьим входом

блока логического сравнения, второй выход которого соединен с вторым входом блока запрета.

Блок логического сравнения вы5 полнен на счетчике, селекторе и регистре

, информационные выходы счетчика подключены к входам первой группы селектора, входы второй группы

которого соединены с выходами ре0 гистра, первый вход которого явля-,

ется третьим входом блока, второй вход регистра является первым входом блока, вход счетчика является

вторым входом блока, выход селектора является первым выходом блока,

выход счетчика является вторым выходом блока.

Блок запрета выполнен на ключе,

счетчиках и триггере, выход ключа является выходом блока, выход первого счетчика соединен с первым входом

триггера, первый вход блока соединен с первыми входами первого счетчика и ключа, второй вход которого

подключен к выходу триггера, выход второго счетчика соединен с вторым входом триггера, вход второго

счетчика -является вторым входом блока.

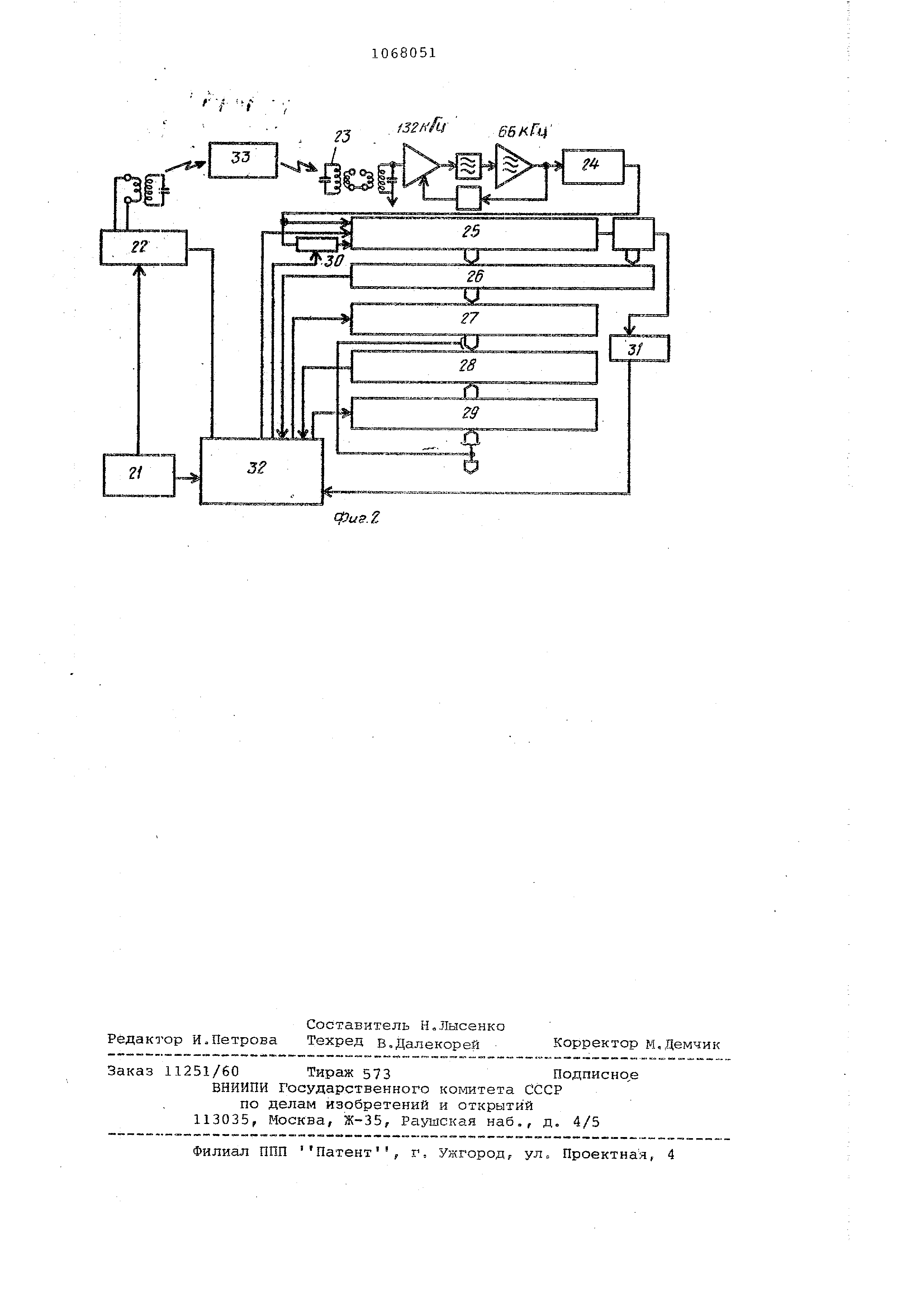

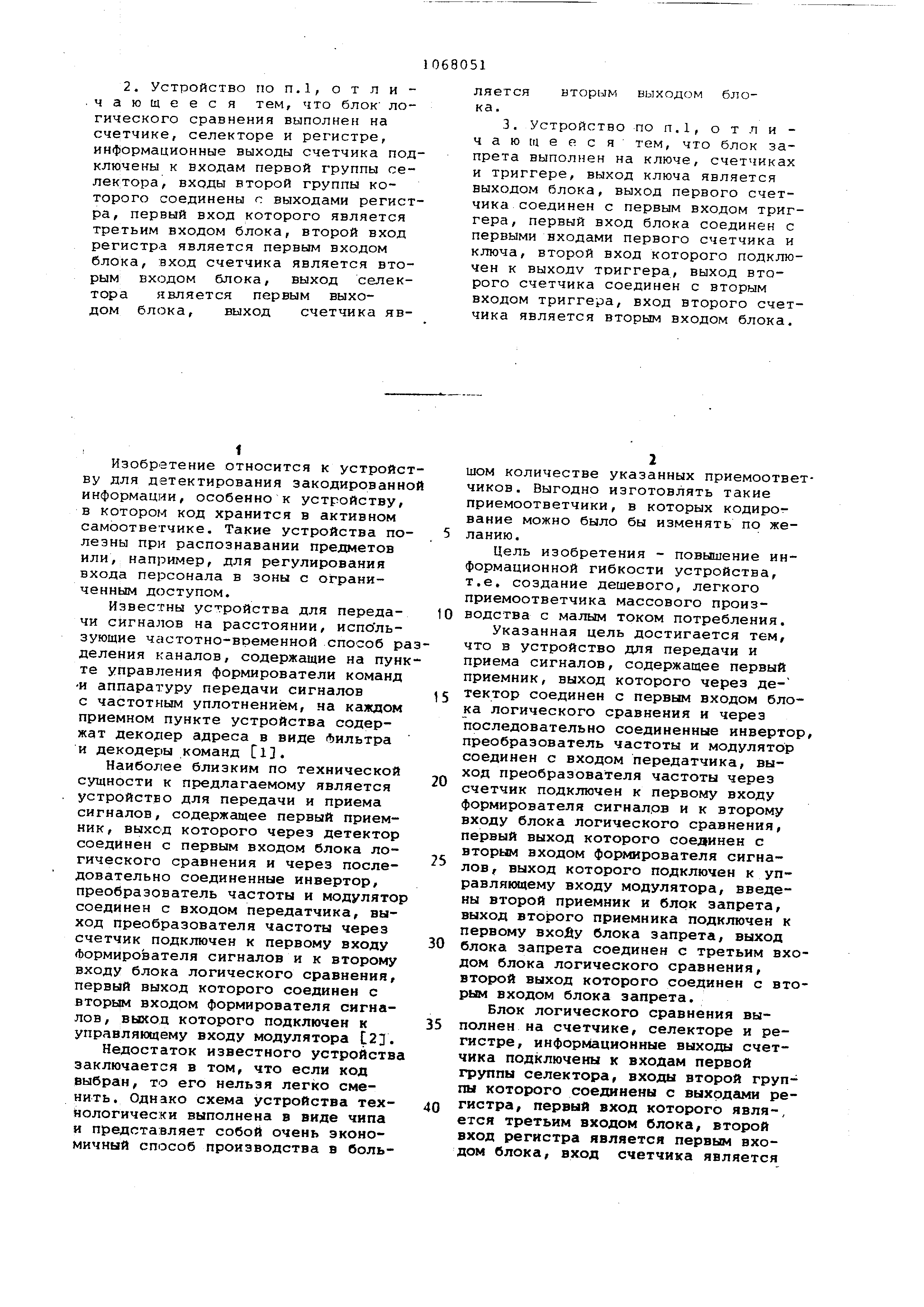

На фиг.1 приведена функциональная

схема устройства для передачи и приема сигналов программируемого

закодированного тега; на фиг.2 функциональная схема, иллюстрирующая процесс запроса кода и его проверки

, осуществляемые запросчиком.

Устройство содержит первый приемник

1, выполненный на инверторах 2 и 3, детектор 4, инвертор 5, преобразователь 6 частоты, модулятор 7

передатчик 8, счетчик 9, формирователь 10 сигналов, блок 11 логического

сравнения, выполненный на счетчике 12, селекторе 13 и регистре 14

Блок 15 запрета содержит ключ 16 триггер 17 и счетчики 18 и 19, Блок

15 запрета соединен со вторым приемником 20.

Запросчик сбдержит генератор 21,

передатчик 22, приемник 23, декодер 24, регистр 25 сдвига, детектор 26,

первый блок 27 триггеров,, компаратор 28,.второй блок 29 триггеров,

ключ 30, детектор 31 нуля и времязадакндий блок 32, в зоне действия запросчика установлено устройство 33

для передачи и приема сигналов, схему 34 сброса счетчика.

Устройство {фиг.1) представляет собой полупроводниковую интеграль- ную схему ДМОП типа, предназначенную

для работы в диапазоне частот индуктивной связи, т.е. до 150 кГц. Устройство излучает ответ

с когерентной на субгармонике передачи запроса.

Приемник 1 содержит самосмещающий входной каскад, используемлй в качестве усилителя высокой частоты для

сигнала запроса, который передается на частоте 132 кГц, и два инвертора 2 и 3 . Детектированный сигнал

запроса подается через дополнительный инвертор 5 на преобразователь б

частоты, который делит частоту сигнала на два, получая несущую повторной передачи с частотой 66 кГц.

Выход приемника 1 также подсоединен к .детектору 4, а выход инвертора

5 также подсоединен к схеме 34 сброса счетчика. Сигнал несущей с

частотой 66 кГц от преобразователя б частоты подается на модулятор 7, содержащий элемент И, где несущая

модулируется словом данных кодл. Сигнал несущей с частотой 66 кГц также подается на счетчик 9 деления

на 384.

Модулированный сигнал затем подается на передатчик 8, который

вк.гаочает буферный усилитель, питающий антенну для повторной передачи

0

сигналом увеличенной мощности.

Блок 11 логического сравнения

содержит регистр 14 для памяти кодовых данньлх, в котором хранятся програ имируемые кодовые данные.

5 Схема адресации памяти содержит N битовый селектор 13, цифровой выход

данных памяти которого определяется индектирующим счетчиком 12. Счетчик 12 получает тактовые импульсы

0 от счетчика 9. Схема задания Формата выходных данных состоит из

полубитового формирователя 10 сигналов , который является элементом ИСКЛЮЧАЮЩЕЕ ИЛИ. Выбранные

5 данных объединяются с выходом счетчика 9, образуя полубитовый формат

передачи данных. Таким образом.

в теченуль передается при

ние половины периода времени, за

0

которым следует i « в течение оставшейся половины с дополнительными передачами для единицы данных.

Второй -усилитель высокой частоты предусмотрен для использования

5 при программировании устройства и является вторым приемником 20, выход

которого через ключ 16 подсоединен к тактовому входу регистра 14. Ключ 16 представляет собой часть

блока 15 запрета, служащего для

0 защиты памяти от случайного тактирования

регистра памяти кода.

Как показано на фиг.2, с закодированным

устройством 33 используется запросчик. Главный генера5 тор 21 на 132 -кГц питает и передатчик 22 и центральный времязадающий

блок 32. Сигнал с частотой 66 кГц, излученный устройством 33, обнаруживается приемником 23. Выход де0

кодера 24 тока приемника подается на каскадный регистр 25 сдвига под

управлением центрального времязадающего блока 32. Детектор 26 полубитового

формата проверяет полубитовый

5 формат, и N-битовый блок 27 триггеров

служит для временного хранения данных. В последствии данные переносятся на второй N-битовый блок 29

триггеров, содержимое-которого срав0 нивается с содержимым блока 27 компа ратором

28. Также предусмотрен шумовой ключ 30 для подавления нежелательных сигналов шума. Детектор

31 нуля подсоединен к регистру

5 25 сдвига.

Устройство работает следуюгдим образом.

Предположим вначале, что устройство 33 удалено из чувствительной зоны и что на его входе нет

сигнала с частотой 132 кГц, тогда выход инвертора 2 имеет высокий уровень (логическая 1), а выход

инвертора 3 принимает- низкий уровень (логический Q). В результате также имеет малую величину вход

кодовых данных, подаваемый детектором 4 на регистр 14. Выход инвертора 5 принимает большое значение,

вызывая прикладывание сигнала сброса ко всем счетчикам и другим последовательным логическим функциям

, устанавливающим известное начальное состояние.

Когда устройство вводится в чувствительную зону, оно принимает непрерывный сигнал с частотой 132 кГц

и сигнал сброса снимается, тем самым включая все счётчики. Затем преобразователь или делитель 6 частоты

подает сигнал подачи несущей с частотой 66 кГц на модулятор 7 и на счетчик 9 для получения тактового

импульса для, индексирующего счетчика 12 и полубитового формирователя 10 сигналов. Индексирующий

счетчик, таким образом, за-, пускается с нуля с интервалом повторения импульсов 5,82 мс. Первоначально

необходим выход данных нуля, так чтобы вход данных для модуляторе 7 имел низкую величину

в течение мс и высокую величину в течение следующих 2,91 мс в полубитовом формате. Этот метод

защищает закодированное устройство реагирующее на передачу от системы сигналов 132 кГц в течение

2,0 мс с интервалами 35 мс. Индексирующий счетчик 12 подсчитывает один-очный импульс в конце начальных

5,82 мс, вызывая-выход Ъервой цифра кодовых данных, хранимой в регистре 14 в полубитовом формате.

Эта последовательность повторяется до тех пор, пока не будут адресованы

все цифры кодовых данных и выведены в полубитовом формате,после чего передатчик 22 запроса с

частотой 132. кГц выключается на период времени приблизительно от 20 до 50 мс, чтобы автосброс был

приведен в состояние готовности дл следующего запроса. Таким способом в устройстве передается сигнал с

частотой 66 кГц, модулированный по амплитуде его уникальным кодом. Поэтому полное время между циклами

запроса равно Nх5,8+35±15 мс, например 175415 мс для 24-битового кода.

Ведущая единица или нуль могут быть постоянно запрограммированы п

изготовлении устройства посредством связывания первой ячейки памяти

О

(фиг.1). Это позворегистра

лит устройству реагировать если

необходимо на чувствительную к наличию сигнала систему запроса.

В течение каждого цикла запроса центральный времязадающий блок 32 стробирует нес5лдую 132 кГц в сос

.тояние Включено во время периода времени, равного (N-1)5,82 мс,

где N - число кодовых битов. Последовательный цифровой поток битов, соответствующий закодированному

ответному сигналу, переданному устройством 33., подается на (2N+2) каскадный

регистр 25 сдвига под управлением времязадающего блока 32. « После завершения цикла из (2N+2) тактовых

импульсов форма кода провеРяется на правильный полубитовый формат и если он достоверен, данные

загружаются во временную память, состоящую из первого N-битового блока 27 триггеров-.

Декодирующий прюцесс начинается при удовлетворительном обнаружении

вещущего нуля детектором 31.

Данные, полученные из ответа на

следующий запрос, вводятся в первый

блок 27 триггеров, тогда как первоначальные

данные перенесены во второй блок 29. Результаты двух последовательных запросов сравниваются в

компараторе 28 (если достигается совпадение, данные считаются достоверными

) и затем подаются как выходной сигнал для индикации сигнала тревоги или дальнейшей обработки

.

Можно осуществлять необходимое количество сравнений. Например, могут

быть предусмотрены дополнительные компараторы и триггерные блоки или может быть подсчитано множество

сигналов достоверности данных до включения центрального времязадающего блока для вырабатывания

выходного сигнала.

В то время, как принимаемый сигнал

подается на регистр 25 сдвига, он также проверяется на шумовые переходн ( вблизи момента тактирования

посредством шумового ключа 30. Если обнаруживается переход с Ч на О , во время которого доллсен

быть сигнал , предполагается, что зто вследствие нежелательного

шума и уже полученные данные разрушаются повторной установкой регистра

25 сдвига. Таким образом, вмес- .

то выполнения всего цикла передачи

цикл заканчивается и начинается новый цикл. Это приводит к экономии времени.

Теперь рассмотрим программирующий режим работы устройства, при

котором необходимый код подается на устройство 33.

В этом режиме кодовые данные пердаются на приемник 1 (132 кГц), и н приемник 20 подается высоко;частотны

кодовый сигнал тактирования памяти посредством индуктивной связи. Это исключает необходимость излучать

высокую частоту, на что в некоторых странах необходимо разрешение. Высокий уровень входного сигнала, н

.обходимый для внутреннего генерирования тактового импульса, также повышает помехоустойчивость системы

. Выходные сигналы приемника детектируются и подаются соответственно на входы данных и тактировани

регистра 14. Если блок 15 запрета разрешает прохождение тактовых сиг1|алов

, Пс1мять программируется сигналом закодированного потока данных Затем осуществляется обычный цикл

запроса для определения достоверности кода.

Тактовый вход регистра 14 запирается на период времени, соответствующий , по крайней мере, двум перодам

передачи запроса счетчиком 19. Ключ 16 запирается до повышения напряжения на выходD-триггера 17,

что может произойти только тогда, когда принято правильное целое число

импульсов на. программном тактовом приемнике 20, что определяется счетчиком 18, и одновременно принято

число импульсов с частотой 132 кГц, соответствукадее удвоенному полному подсчету индуксирующего

счетчика 12. Цикл программирования кода, таким образснч, больше обычного цикла запроса.

Преимущество предлагаемого устройства заключается в том, что потребитель

легко может повторно запpoгpaммиJ oвaть кодируемые данны Это особенно выгодно там, где такие

данные необходимы только для небольшого промежутка времени, или данные

включают некоторый элемент, который необходимо периодически корректировать . Примерами такого применения

являются автоматическая транспортировка багажа, идентификация контейнеров на маршруте мешкрв с почтой

.. Данные могут относиться, кроме

того, к размерам, весу, месту назначения

, дате, времени, цене или другой классификации, включая также уникальную идентификацию. Преимуществом

устройства является также то, что повторное программирование может быть осуществлено

без установления какого-нибудь физического и электрического контакта с устройством или без нару0

|Шения его. Кроме того, устройство только необходимо изъять из работы на очень короткий период времени

для удобства потребителя.

Нет ограничения числу циклов

5 повторного программирования, которые могут производиться в течение

срока службы устройства. Число возможных кодов, также очень большое, при этом единственным ограничением

0 является размер используемого чипа. Можно использовать миллиард уникальных

кодов.

Вследствие требования на малые физические размеры устройства и

5 запросчика их роли взаимозаменяемые, т.е. запросчик может быть статическим

и использоваться для обнаружения присутствия приемоответчика в чувствительной зоне или альтернативно

, приемоответчики могут быть ус0 тановлены на больших объектах, а портативный

запросчик использоваться для считывания кодов для идентификации содержимого и т.д.

в предлагаемом устройстве могут

5

быть сделаны различные дополнительные изменения. Например, устройство

может быть установлено непосредственно или может быть интегральной частью любого предмета, который

0 желательно обнаружить.

При альтернативном изменении устройство

может быть заменено свободно двигающимся устройством, которое

5 работает непрерывно без потребности в сигнале запроса. Сигнал, передаваемый

устройством, содержит закодированную информацию, которая может быть изменена время от времени

f. по необходимости.

Устройство может быть вьтолнено

для работы в любом месте в диапазоне частот индуктивной связи. /5fЛД/

Комментарии