Устройство фотоэлектрического преобразования, способ возбуждения устройства фотоэлектрического преобразования, система формирования изображения и подвижный объект - RU2730175C1

Код документа: RU2730175C1

Чертежи

Описание

Уровень техники

Область техники, к которой относится изобретение

[0001] Настоящее изобретение относится к устройству фотоэлектрического преобразования, способу возбуждения устройства фотоэлектрического преобразования, системе формирования изображения и подвижному объекту.

Описание предшествующего уровня техники

[0002] Известно устройство фотоэлектрического преобразования, которое в цифровом виде подсчитывает количество фотонов, поступающих на модуль приема света, и выводит значение подсчета из пикселя в виде цифрового сигнала. Опубликованная патентная заявка Японии № 2017–083298 раскрывает схему считывания, включающую в себя схему подсчета, которая подсчитывает количество фотонов, поступающих в элемент фотоэлектрического преобразования, схему интегрирования, которая интегрирует выходной ток элемента фотоэлектрического преобразования для формирования сигнала напряжения, и блок обработки сигнала, который определяет уровень падающего света на основании результата подсчета и сигнала напряжения. Опубликованная патентная заявка Японии № 2017–083298 раскрывает, что при такой конфигурации схемы считывания можно поддерживать широкий диапазон количества света.

[0003] В опубликованной патентной заявке Японии № 2017–083298, однако, не рассматривается ситуация, когда множество сигналов, выводимых из элементов фотоэлектрического преобразования, создают помехи друг другу и не могут быть разделены как импульс напряжения. Таким образом, в частности, при высокой яркости выходное значение из схемы подсчета может быть намного ниже идеального значения, и ошибка значения подсчета может увеличиваться.

Сущность изобретения

[0004] Настоящее изобретение предназначено для предоставления устройства фотоэлектрического преобразования с подсчетом фотонов, имеющего улучшенную функцию фотоэлектрического преобразования на высокой яркости.

[0005] Согласно одному аспекту настоящего изобретения предоставляется устройство фотоэлектрического преобразования, включающее в себя множество пикселей, каждый из которых включает в себя модуль приема света, который выводит импульс в ответ на попадание фотона, и блок формирования сигнала, который выводит сигнал на основе вывода из модуля приема света, и каждый из множества пикселей дополнительно включает в себя блок обнаружения, который обнаруживает, превышает ли или нет ширина импульса, выводимого из модуля приема света, заданное пороговое значение.

[0006] В соответствии с другим аспектом настоящего изобретения предоставлен способ возбуждения устройства фотоэлектрического преобразования, включающего в себя модуль приема света, который выводит импульс в ответ на попадание фотона, и блок формирования сигнала, который выводит сигнал на основе вывода из модуля приема света, и способ включает в себя обнаружение того, превышает ли или нет ширина импульса, выводимого из модуля приема света, заданное пороговое значение.

[0007] Дополнительные признаки настоящего изобретения станут очевидными из последующего описания примерных вариантов осуществления со ссылкой на приложенные чертежи.

Краткое описание чертежей

[0008] Фиг. 1 – это блок–схема, иллюстрирующая общую конфигурацию устройства фотоэлектрического преобразования согласно первому варианту осуществления настоящего изобретения.

[0009] Фиг. 2 представляет собой схему, иллюстрирующую пример конфигурации пикселя устройства фотоэлектрического преобразования в соответствии с первым вариантом осуществления настоящего изобретения.

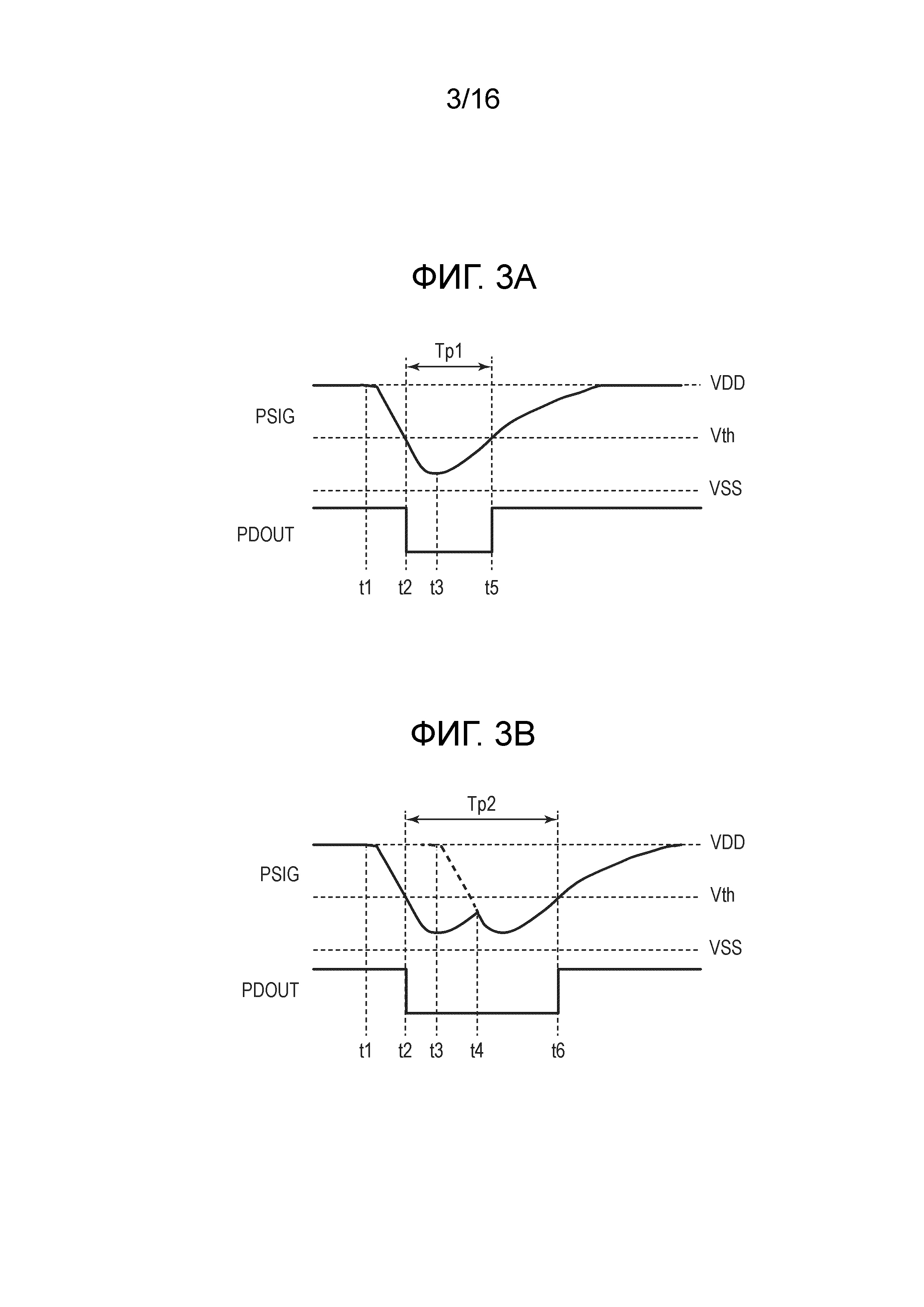

[0010] Фиг. 3А и фиг. 3В представляют собой временные диаграммы, иллюстрирующие работу блока преобразования импульсов устройства фотоэлектрического преобразования в соответствии с первым вариантом осуществления настоящего изобретения.

[0011] Фиг. 4 представляет собой временную диаграмму, иллюстрирующую работу пикселей устройства фотоэлектрического преобразования в соответствии с первым вариантом осуществления настоящего изобретения.

[0012] Фиг. 5 представляет собой схему, иллюстрирующую пример характеристики фотоэлектрического преобразования устройства фотоэлектрического преобразования согласно первому варианту осуществления настоящего изобретения.

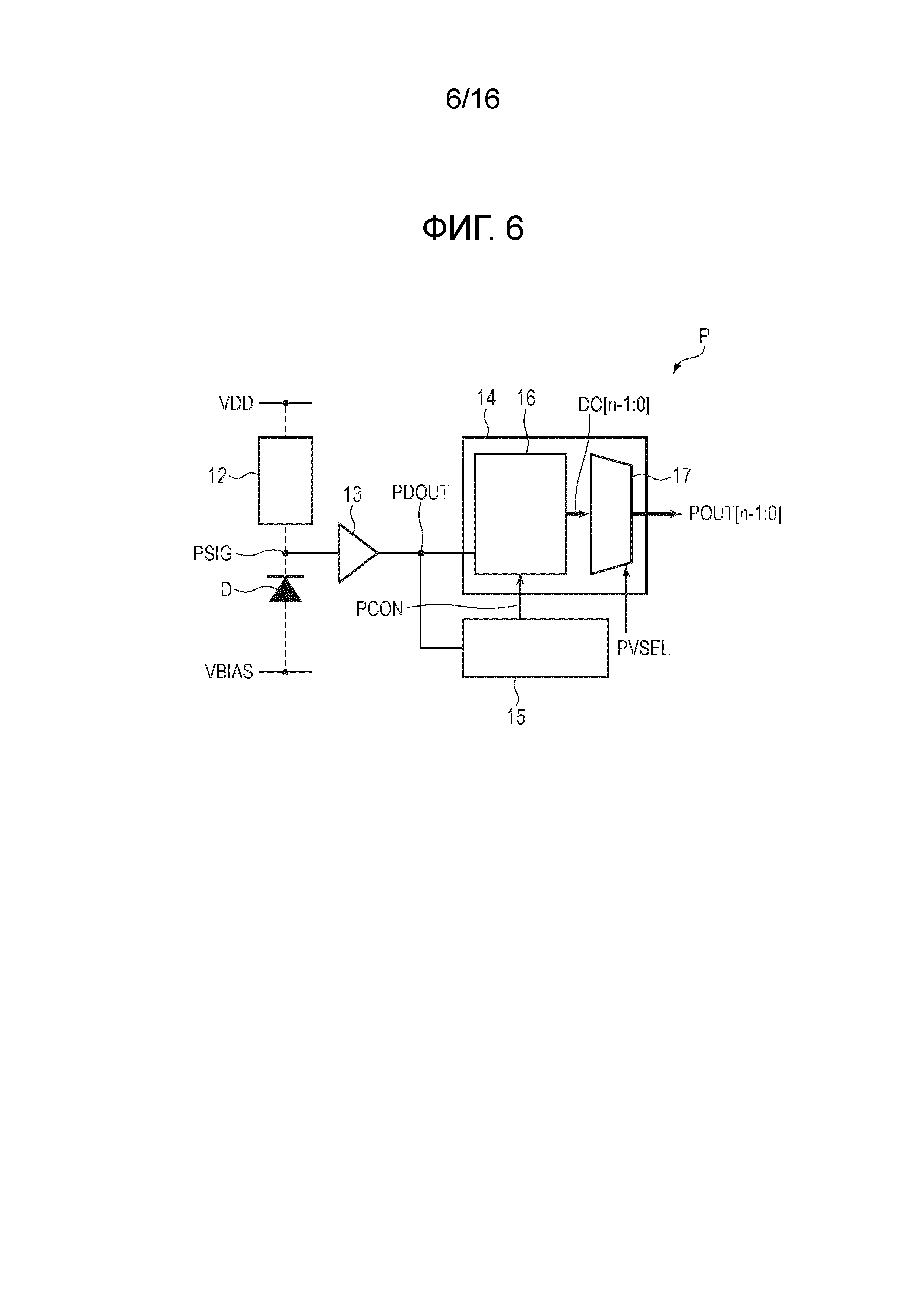

[0013] Фиг. 6 представляет собой схему, иллюстрирующую пример конфигурации пикселя устройства фотоэлектрического преобразования в соответствии со вторым вариантом осуществления настоящего изобретения.

[0014] Фиг. 7 представляет собой временную диаграмму, иллюстрирующую работу пикселя устройства фотоэлектрического преобразования согласно второму варианту осуществления настоящего изобретения.

[0015] Фиг. 8 представляет собой схему, иллюстрирующую пример конфигурации пикселя устройства фотоэлектрического преобразования согласно третьему варианту осуществления настоящего изобретения.

[0016] Фиг. 9 представляет собой временную диаграмму, иллюстрирующую работу пикселя устройства фотоэлектрического преобразования согласно третьему варианту осуществления настоящего изобретения.

[0017] Фиг. 10 представляет собой схему, иллюстрирующую пример конфигурации пикселя устройства фотоэлектрического преобразования согласно четвертому варианту осуществления настоящего изобретения.

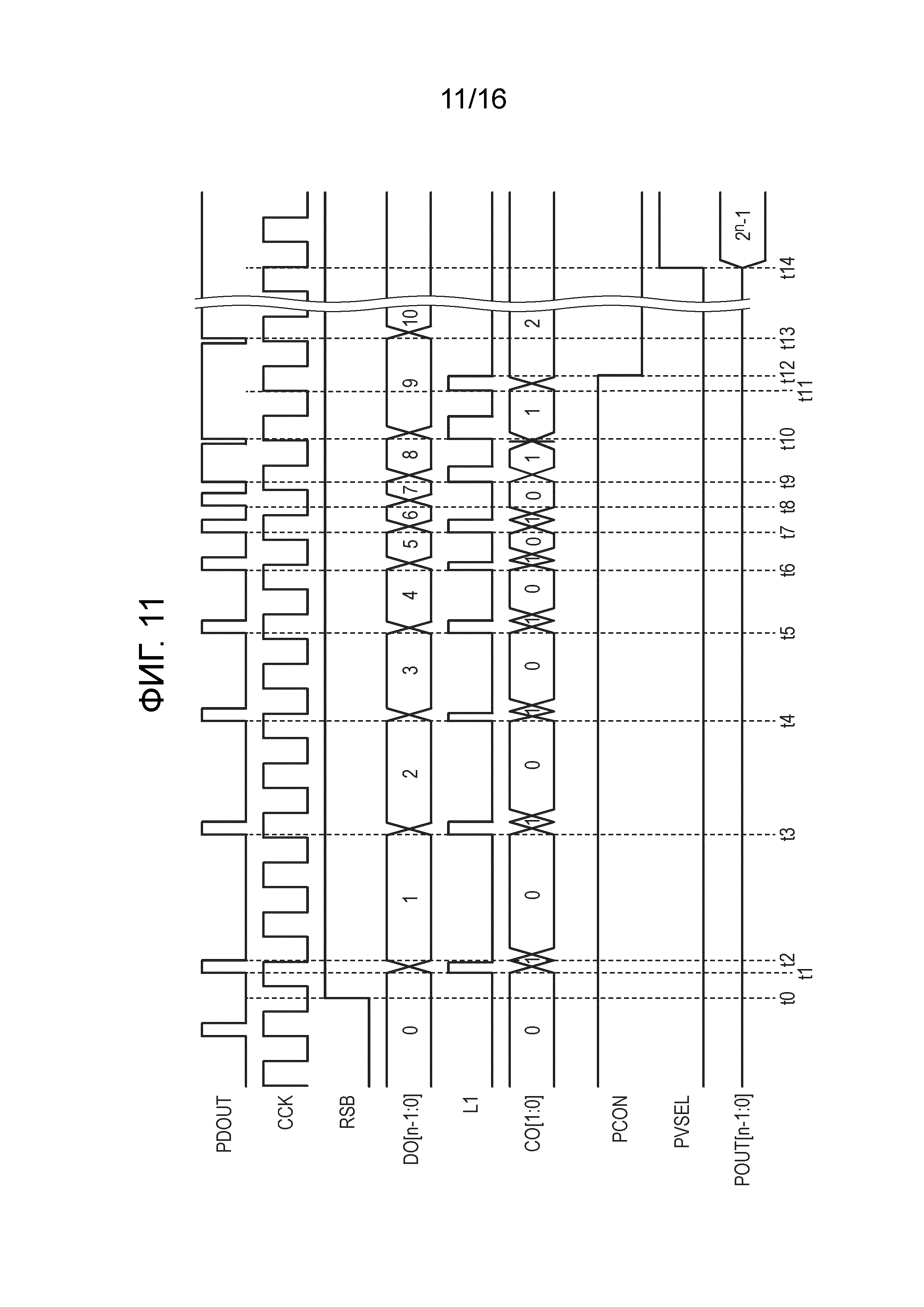

[0018] Фиг. 11 представляет собой временную диаграмму, иллюстрирующую работу пикселя устройства фотоэлектрического преобразования согласно четвертому варианту осуществления настоящего изобретения.

[0019] Фиг. 12 представляет собой схему, иллюстрирующую пример конфигурации пикселя устройства фотоэлектрического преобразования согласно пятому варианту осуществления настоящего изобретения.

[0020] Фиг. 13 представляет собой временную диаграмму, иллюстрирующую работу пикселя устройства фотоэлектрического преобразования согласно пятому варианту осуществления настоящего изобретения.

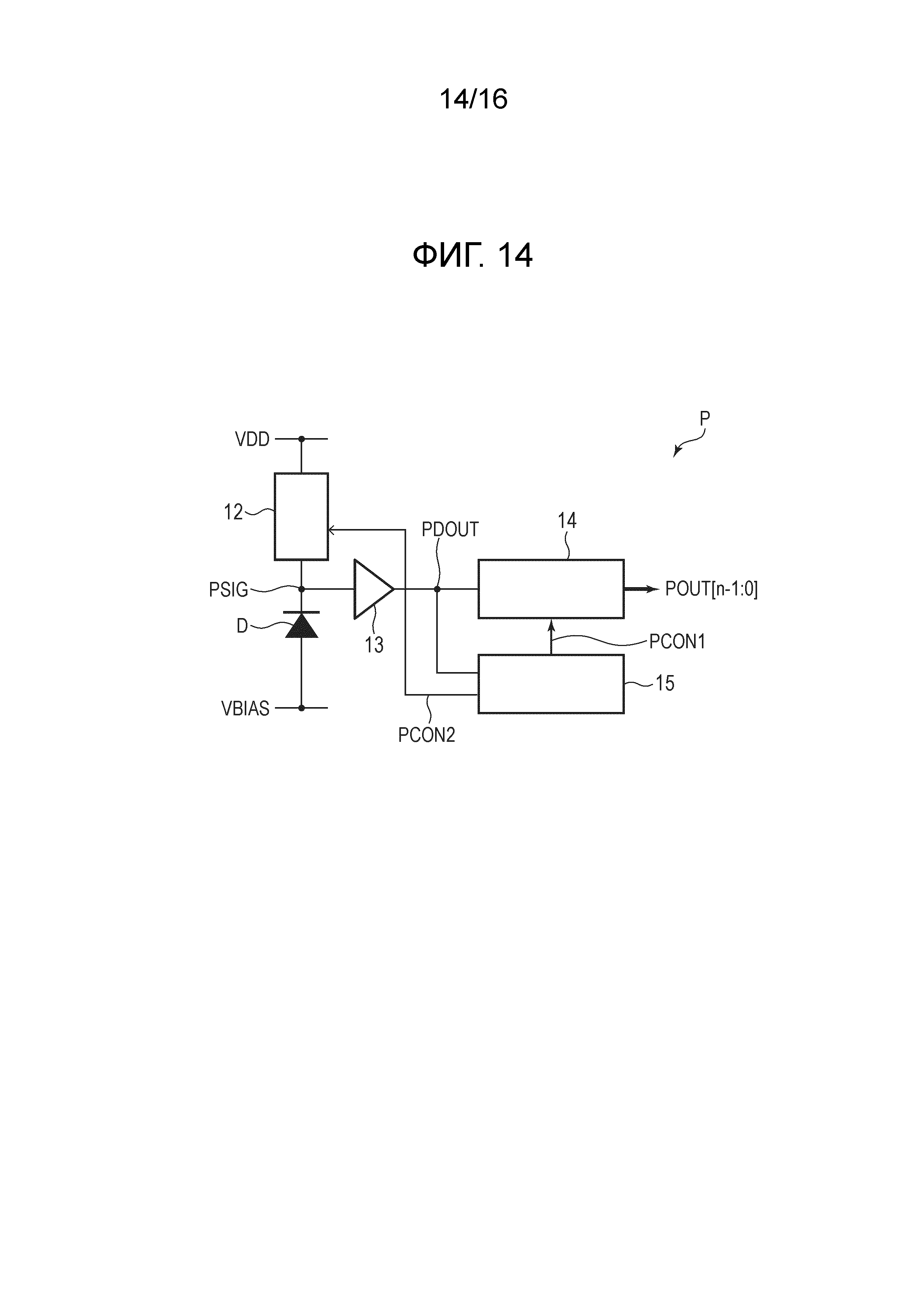

[0021] Фиг. 14 представляет собой схему, иллюстрирующую пример конфигурации пикселя устройства фотоэлектрического преобразования согласно шестому варианту осуществления настоящего изобретения.

[0022] Фиг. 15 представляет собой блок–схему, иллюстрирующую общую конфигурацию системы формирования изображения согласно седьмому варианту осуществления настоящего изобретения.

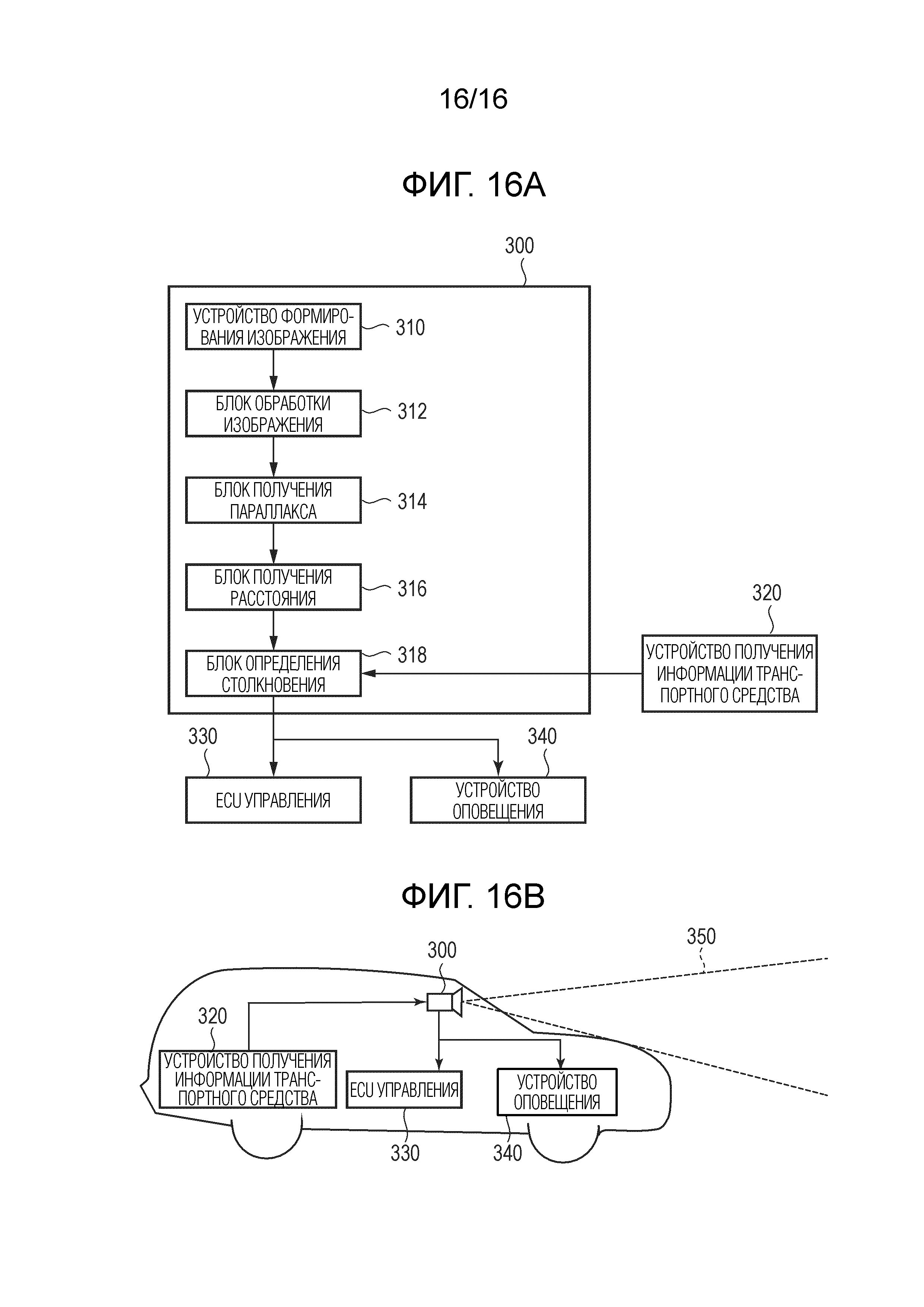

[0023] Фиг. 16A представляет собой схему, иллюстрирующую пример конфигурации системы формирования изображения согласно восьмому варианту осуществления настоящего изобретения.

[0024] Фиг. 16В представляет собой схему, иллюстрирующую пример конфигурации подвижного объекта согласно восьмому варианту осуществления настоящего изобретения.

Описание вариантов осуществления

[0025] Предпочтительные варианты осуществления настоящего изобретения будут теперь описаны подробно в соответствии с сопровождающими чертежами.

[0026] [Первый вариант осуществления]

[0027] Устройство фотоэлектрического преобразования и способ возбуждения устройства в соответствии с первым вариантом осуществления настоящего изобретения будет описан со ссылкой на фиг. 1–5. На фиг. 1 изображена блок–схема, иллюстрирующая общую конфигурацию устройства фотоэлектрического преобразования в соответствии с настоящим вариантом осуществления. На фиг. 2 показана схема, иллюстрирующая пример конфигурации пикселя устройства фотоэлектрического преобразования в соответствии с настоящим вариантом осуществления. Фиг. 3А и фиг. 3В представляют собой временные диаграммы, иллюстрирующие работу блока преобразования импульсов устройства фотоэлектрического преобразования в соответствии с настоящим вариантом осуществления. Фиг. 4 представляет собой временную диаграмму, иллюстрирующую работу пикселей устройства фотоэлектрического преобразования в соответствии с настоящим вариантом осуществления. Фиг. 5 представляют собой схему, иллюстрирующую пример характеристики фотоэлектрического преобразования устройства фотоэлектрического преобразования согласно настоящему варианту осуществления.

[0028] Как показано на фиг. 1, устройство 100 фотоэлектрического преобразования согласно настоящему варианту осуществления включает в себя блок 10 датчика и блок 20 схемы. Блок 20 схемы включает в себя схему 21 вертикального выбора, схемы 22 обработки сигналов, схему 23 горизонтального выбора и схему 24 управления.

[0029] Блок 10 датчика снабжен множеством пикселей P, размещенных в матрице во множестве направлений строк и множестве направлений столбцов. Фиг. 1 иллюстрирует 36 пикселей P, расположенных в 6 строках с 0–йстроки по 5–ю строку и 6 столбцах с 0–го столбца на 5–й столбец вместе со ссылками, каждая из которых указывает номер строки и номер столбца. Например, пиксель P, расположенный в первой строке четвертого столбца, помечен ссылкой "P14". Следует отметить, что количество строк и количество столбцов матрицы пикселей, образующих блок 10 датчика, в частности, не ограничены.

[0030] На каждой строке массива пикселей блока 10 датчика, управляющая линия для подачи управляющего сигнала PVSEL проходит в первом направлении (горизонтальном направлении на фиг. 1). Каждая из управляющих линий соединена с пикселями P, выровненными соответственно, в первом направлении, и образует общую управляющую линию для этих пикселей P. Первое направление, в котором проходит управляющая линия, может называться направлением строки или горизонтальным направлением. Следует отметить, что на фиг. 1, управляющий сигнал PVSEL, подаваемый на каждую из управляющих линий, проиллюстрирован вместе со ссылкой, указывающей номер строки. Например, управляющая линия в первом ряду помечена ссылкой "PVSEL[1]".

[0031] Управляющая линия в каждой строке соединена со схемой 21 вертикального выбора. Схема 21 вертикального выбора является схемным блоком, который предоставляет пикселю P через управляющую линию управляющий сигнал PVSEL, используемый для возбуждения схемы формирования сигнала (соответствующей блоку 14 формирования сигнала, описанному ниже) в пикселе P.

[0032] На каждом столбце матрицы пикселей блока 10 датчика, выходная линия POUT проходит во втором направлении (вертикальном направлении на фиг. 1), пересекающим первое направление. Каждая из выходных линий POUT соединена с пикселями P, выровненными во втором направлении, соответственно, и образует сигнальную линию общую для этих пикселей P. Второе направление, в котором проходит выходная линия POUT, может называться направлением столбца или вертикальным направлением. Следует отметить, что на фиг. 1, каждая из выходных линий POUT иллюстрируется вместе со ссылкой, указывающей номер столбца. Например, выходная линия в четвертом столбце помечена ссылкой "POUT4". Каждая из выходных линий POUT включает в себя n сигнальных линий, используемых для вывода n–битного цифрового сигнала.

[0033] Выходные линии POUT соединены со схемами 22 обработки сигналов. Схемы 22 обработки сигналов предусмотрены в связи с соответствующими столбцами матрицы пикселей блока 10 датчиков и подключены к выходной линии POUT в соответствующем столбце. Каждая схема 22 обработки сигналов имеет функцию удержания сигнала, считанного из пикселей P через выходную линию POUT в соответствующем столбце. Поскольку сигналы, выводимые из пикселей P, соответствуют n–битным сигналам, введенным через n сигнальных линий выходных линий POUT, каждая из схем 22 обработки сигналов включает в себя, по меньшей мере, n блоков удержания для удержания сигналов соответствующих битов.

[0034] Схема 23 горизонтального выбора является схемным блоком, который подает управляющий сигнал, используемый для считывания сигнала из схемы 22 обработки сигналов, в схему 22 обработки сигналов. Схема 23 горизонтального выбора подает управляющий сигнал PHSEL в схему 22 обработки сигналов на каждый столбец через управляющую линию. Схема 22 обработки сигналов, которая приняла управляющий сигнал PHSEL от схемы 23 горизонтального выбора, выводит сигнал, удерживаемый в блоке удержания, в качестве выходного сигнала SOUT устройства 100 фотоэлектрического преобразования через горизонтальную выходную линию HSIG.

Следует отметить, что на фиг. 1, управляющий сигнал PHSEL, подаваемый на каждую управляющую линию, проиллюстрирован вместе со ссылкой, указывающей номер столбца. Например, управляющая линия в четвертом столбце помечена ссылкой "PHSEL[4]”. Горизонтальная выходная линия HSIG включает в себя n сигнальных линий, используемых для вывода выходного сигнала SOUT, сформированного из n–битного цифрового сигнала.

[0035] Схема 24 управления является схемным блоком, используемым для обеспечения управляющих сигналов, которые управляют операциями или синхронизацией операций схемы 21 вертикального выбора, схем 22 обработки сигналов и схемы 23 горизонтального выбора. Отметим, что, по меньшей мере, некоторые из управляющих сигналов, которые управляют операциями или синхронизацией операций схемы 21 вертикального выбора, схем 22 обработки сигналов и схемы 23 горизонтального выбора, могут быть предоставлены снаружи устройства 100 фотоэлектрического преобразования.

[0036] Как показано на фиг. 2, каждый пиксель Р включает в себя лавинный умножительный диод D, блок 12 гашения, блок 13 преобразования импульсов, блок 14 формирования сигнала и блок 15 обнаружения периода.

[0037] Анод диода D подключен к узлу источника питания, который подает напряжение VBIAS. Катод диода D подключен к одной клемме блока 12 гашения и к входной клемме блока 13 преобразования импульсов. В дальнейшем узел соединения катода диода D, одной клеммы блока 12 гашения и входной клеммы блока 13 преобразования импульсов называется узлом PSIG. Другая клемма блока 12 гашения соединена с узлом источника питания, который подает напряжение VDD. Выходная клемма блока 13 преобразования импульсов соединена с входной клеммой блока 14 формирования сигнала и входной клеммой блока 15 обнаружения периода. В дальнейшем узел соединения выходной клеммы блока 13 преобразования импульсов, входной клеммы блока 14 формирования сигнала и входной клеммы блока 15 обнаружения периода называется узлом PDOUT. Блок 15 обнаружения периода выводит управляющий сигнал PCON в блок 14 формирования сигнала. Блок 14 формирования сигнала выводит сигнал POUT[n–1:0] на выходную линию POUT в соответствующем столбце.

[0038] Напряжение обратного смещения, большее или равное напряжению пробоя, подается на диод D от узла источника питания, который подает напряжения VDD и VBIAS через блок 12 гашения. Напряжение VDD и напряжение VBIAS являются напряжениями питания, подаваемыми на диод D, соответственно. Таким образом, диод D находится в состоянии, приспособленном работать в режиме Гейгера. Когда фотоны входят в диод D, посредством лавинного умножения формируется большое количество электронов (и дырок) с использованием электронов, возбуждаемых попадающими фотонами в качестве затравок. Когда ток, формируемый лавинным умножением, протекает в блоке 12 гашения, в блоке 12 гашения происходит падение напряжения, и в результате напряжение, подаваемое на диод D, уменьшается, и рабочая область диода D выходит из режима Гейгера. Когда лавинное умножение диода D прекращается, падение напряжения блока 12 гашения возвращается в исходное состояние, и рабочая область диода D снова переходит в режим Гейгера.

[0039] Блок 13 преобразования импульсов преобразует изменение потенциала катода (узла PSIG) диода D в импульсный сигнал, состояние которого изменяется в соответствии с заданным пороговым значением. При такой конфигурации импульс напряжения, соответствующий падению фотона, выводится из выходной клеммы (узла PDOUT) блока 13 преобразования импульсов. Т.е. диод D, блок 12 гашения и блок 13 преобразования импульсов формируют модуль приема света, который выводит импульс в ответ на попадание фотона.

[0040] Блок 14 формирования сигнала является, например, схемой формирования сигнала, которая подсчитывает импульсы напряжения, выводимые из блока 13 преобразования импульсов, и выводит результат как сигнал POUT[n–1:0]. Сигнал POUT[n–1:0] является n–битным цифровым сигналом. Выходная клемма блока 14 формирования сигнала включает в себя n сигнальных линий, используемых для вывода сигнала POUT[n–1:0] для соответствующих битов.

[0041] Блок 15 обнаружения периода представляет собой, например, схему обнаружения, сконфигурированную, чтобы определять ширину импульса напряжения (длительности периода, в течение которого уровень сигнала поддерживается на высоком уровне или низком уровне), выводимого из блока 13 преобразования импульсов. Блок 15 обнаружения периода обнаруживает, превышает ли или нет ширина импульса напряжения, выводимого из модуля приема света, заданное пороговое значение. Блок 15 обнаружения периода затем выводит управляющий сигнал PCON в соответствии с результатом обнаружения в блок 14 формирования сигнала. Т.е., блок 15 обнаружения периода включает в себя блок управления, который управляет блоком 14 формирования сигнала в соответствии с результатом обнаружения ширины импульса напряжения. Управляющий сигнал PCON является сигналом, состояние которого изменяется, когда ширина импульса напряжения, указывающего падение фотона, превышает заданное пороговое значение.

[0042] Далее, операции блока 13 преобразования импульсов и блока 15 обнаружения период будут описано более подробно с помощью фиг. 3А, фиг. 3В и фиг. 4.

[0043] Когда фотон не входит в диод D, потенциал катода (узла PSIG) диода D находится при напряжении VDD. В это время уровень сигнала выходной клеммы (узла PDOUT) блока 13 преобразования импульсов предполагается равным заданному высокому уровню.

[0044] Фиг. 3А представляет собой временную диаграмму, иллюстрирующую работу блока 13 преобразования импульса, когда один фотон входит в диод D. На фиг. 3А, "PSIG" обозначает потенциал узла PSIG и "PDOUT" обозначает потенциал узла PDOUT.

[0045] Как показано на фиг. 3А, когда фотон входит в диод D в момент времени t1, ток, формируемый посредством лавинного умножения, течет в блоке 12 гашения, и происходит падение напряжения в блоке 12 гашения. Таким образом, потенциал узла PSIG постепенно уменьшается от напряжения VDD.

[0046] В момент времени t2, когда потенциал узла PSIG становится ниже заданного порогового значения Vth, уровень потенциала узла PDOUT переходит от высокого уровня к заданному низкому уровню.

[0047] В момент времени t3, когда рабочая область диода D выходит из режима Гейгера, и лавинное умножение диода D прекращается, падение напряжения блока 12 гашения начинает возвращаться в исходное состояние.

[0048] В момент времени t5, когда потенциал узла PSIG становится выше или равен пороговому значению Vth, уровень потенциала узла PDOUT возвращается к высокому уровню с низкого уровня.

[0049] Таким образом, как только один фотон входит в диод D, импульс напряжения, период низкого уровня которого является периодом Tp1, выводится из блока 13 преобразования импульсов в узел PDOUT. Длительность периода Tp1 зависит от физической постоянной, образующей диод D, и постоянной схемы блока 12 гашения и блока 13 преобразования импульсов и становится по существу постоянной величиной.

[0050] Хотя фиг. 3A иллюстрирует случай, когда один импульс напряжения формируется для одного падения фотона, падение фотона может не соответствовать формированию импульса напряжения по принципу один–к–одному для определенных моментов падения фотонов. Один из примеров этого будет описан с помощью временной диаграммы на фиг. 3В.

[0051] Фиг. 3В представляет собой временную диаграмму, иллюстрирующую работу блока 13 преобразования импульсов, когда два фотона входят в диод D в течение короткого периода времени. На фиг. 3B, "PSIG" обозначает потенциал узла PSIG, и "PDOUT" обозначает потенциал узла PDOUT.

[0052] Как показано на фиг. 3В, когда фотон входит в диод D в момент времени t1, ток, формируемый посредством лавинного умножения, течет в блоке 12 гашения, и происходит падение напряжения в блоке 12 гашения. Таким образом, потенциал узла PSIG постепенно уменьшается от напряжения VDD.

[0053] В момент времени t2, когда потенциал узла PSIG становится ниже заданного порогового значения Vth, уровень потенциала узла PDOUT переходит от высокого уровня к заданному низкому уровню.

[0054] В момент времени t3, когда рабочая область диода D выходит из режима Гейгера, и лавинное умножение диода D прекращается, падение напряжения блока 12 гашения начинает возвращаться в исходное состояние. Однако, когда в момент времени t3 снова появляется падающий фотон, например, потенциал узла PSIG снова уменьшается в момент времени t4, прежде чем превысит пороговое значение Vth. Когда лавинное умножение из–за падения второго фотона прекращается, падение напряжения блока 12 гашения начинает возвращаться.

[0055] В момент времени t6, когда потенциал узла PSIG становится выше или равен пороговому значению Vth, уровень потенциала узла PDOUT возвращается к высокому уровню с низкого уровня.

[0056] В этом случае, хотя импульс напряжения, период низкого уровня которого является периодом Tp2, выводится из блока 13 преобразования импульсов в узел PDOUT, количество импульсов напряжения, выводимых из блока 13 преобразования импульсов, меньше, чем количество фотонов, поступающих в диод D. Такое явление вызвано тем, что частота падающих фотонов превышает частоту формирования импульсов напряжения и становится значительной в окружении высокой яркости.

[0057] Фиг. 4 представляет собой временную диаграмму, иллюстрирующую взаимосвязь потенциала PDOUT узла, сигнала POUT[n–1:0] и управляющего сигнала PCON.

[0058] В период до момента времени t1 значение подсчета, представленное сигналом POUT[n–1:0], выводимым блоком 14 формирования сигнала, равно нулю (0). Кроме того, управляющий сигнал PCON имеет заданный высокий уровень, когда ширина импульса напряжения меньше или равна заданному пороговому значению, и переходит на заданный низкий уровень, когда ширина импульса напряжения превышает заданное пороговое значение. В период до момента времени t1 управляющий сигнал PCON находится на высоком уровне.

[0059] Как показано на фиг. 4 присутствует падающий фотон в каждый момент времени t1, t2, t3, t4, t5, t6, t7, t8, t9 и t10. Таким образом, импульс напряжения в соответствии с моментом падения фотона выводится из блока 13 преобразования импульсов в узел PDOUT.

[0060] Блок 14 формирования сигнала подсчитывает импульсы напряжения, выводимые из блока 13 преобразования импульсов в узел PDOUT, и выводит его результат в виде сигнала POUT[n–1:0]. Фиг. 4 иллюстрирует случай, когда блок 14 формирования сигнала подсчитывает импульсы напряжения, формируемый в ответ на моменты падения фотонов в моменты времени t1, t2, t3,..., и значения подсчета, соответствующих десятичным числам 1, 2, 3,..., последовательно выводятся в качестве сигнала POUT[n–1:0].

[0061] Здесь, в момент времени t10, импульс напряжения, имеющий ширину, превышающую период Tp1, который является шириной импульса в соответствии с падением одного фотона, выводится из блока 13 преобразования импульсов. Это при условии падения света высокой яркости, как описано с помощью фиг. 3B.

[0062] Блок 15 обнаружения периода заставляет управляющий сигнал PCON переходить с высокого уровня на низкий уровень, когда ширина импульса напряжения (длительность периода низкого уровня), выводимого на узел PDOUT, превышает заданный период времени. Например, как показано на фиг. 4 блок 15 обнаружения периода заставляет управляющий сигнал PCON переходить с высокого уровня на низкий уровень в момент времени t11, когда длительность периода, в котором импульс напряжения является низким уровнем, превышает предварительно заданный период времени.

[0063] Блок 14 формирования сигнала, который принял управляющий сигнал низкого уровня PCON от блока 15 обнаружения периода, выводит цифровое значение в соответствии с заданным фиксированным значением Y2, например, в качестве сигнала POUT[n–1:0]. Фиксированное значение Y2 может быть установлено в значение подсчета импульсов, соответствующее количеству света, полученному, например, когда частота падения фотонов превышает частоту формирования импульсов.

[0064] Фиг. 5 представляет собой график, иллюстрирующий пример характеристики фотоэлектрического преобразования пикселя P. На фиг. 5, горизонтальная ось представляет количество падающего света к пикселю Р, и вертикальная ось представляет значение подсчета импульсов напряжения, формируемых падением фотонов. Значение по вертикальной оси соответствует значению сигнала POUT[n–1:0], выводимого блоком 14 формирования сигнала.

[0065] В случае, когда количество падающего света на пиксели Р является относительно небольшим, падение фотона по существу соответствует формированию импульса напряжения по принципу один–к–одному, как описано с помощью фиг. 3A. Таким образом, например, когда количество света меньше или равно X2, значение подсчета импульсов также увеличивается с увеличением количества падающего света.

[0066] Однако, когда количество падающего света на пиксели P увеличивается, частота падения фотонов превышает частоту формирования импульсов напряжения, и это приводит к состоянию, когда один импульс напряжения формируется в ответ на падение множества фотонов, как описано с помощью фиг. 3B. Это становится более значимо, когда количество падающего света на пиксели P больше.

[0067] Поэтому, когда количество падающего света на пиксели Р превышает количество X2 света в конфигурации пикселя без блока 15 определения периода, значение подсчета импульсов будет уменьшаться при увеличении количества света, как показано пунктирной линией на фиг. 5 как "сравнительный пример". Например, при количестве X1 света и количестве X3 света значение подсчета импульсов является одним и тем же и равно Y1, и разница в количестве света не различима.

[0068] С другой стороны, настоящий вариант осуществления сконфигурирован таким образом, что, когда длительность периода, при котором импульс напряжения находится на низком уровне, превышает заданный период времени, цифровое значение в соответствии с заданным фиксированным значением Y2 выводится в качестве сигнала POUT[n–1:0]. Когда это фиксированное значение Y2 устанавливаются на накопленное значение числа импульсов в соответствии с количеством X2 света, значение подсчета импульсов становится фиксированным значением Y2 при количестве X2 света или выше, как показано сплошной линией на фиг. 5 как "пример". Следовательно, можно предотвратить уменьшение значения подсчета импульсов при превышении количества X2 света, и уменьшить ошибку в значении подсчета.

[0069] Таким образом, в устройстве фотоэлектрического преобразования согласно настоящему варианту осуществления блок 15 обнаружения периода обнаруживает период ширины импульса для импульса напряжения, выводимого из блока 13 преобразования импульсов, и выводит в блок 14 формирования сигнала управляющий сигнал PCON, состояние которого меняется в соответствии с предварительно заданным пороговым значением. Таким образом, блок 14 формирования сигнала может определять, превышает ли или нет частота падения фотонов частоту формирования импульсов напряжения, и может уменьшить ошибку в значении подсчета при высокой яркости.

[0070] Таким образом, согласно настоящему варианту осуществления, в устройстве фотоэлектрического преобразования типа подсчета фотонов можно уменьшить ошибку в значении подсчета при высокой яркости. Это может улучшать операцию фотоэлектрического преобразования при высокой яркости.

[0071] [Второй вариант осуществления]

[0072] Устройство фотоэлектрического преобразования и способ возбуждения устройства в соответствии со вторым вариантом осуществления настоящего изобретения будут описаны со ссылкой на фиг. 6 и фиг. 7. Компоненты, аналогичные компонентам устройства фотоэлектрического преобразования в соответствии с первым вариантом осуществления, обозначены теми же ссылками, и их описание будет опущено или упрощено. На фиг. 6 показана схема, иллюстрирующая пример конфигурации пикселя устройства фотоэлектрического преобразования в соответствии с настоящим вариантом осуществления. Фиг. 7 представляет собой временную диаграмму, иллюстрирующую работу пикселя устройства фотоэлектрического преобразования в соответствии с настоящим вариантом осуществления.

[0073] В настоящем варианте осуществления будет описан один пример более конкретной конфигурации и работы блока 14 формирования сигнала. Как показано на фиг. 6 блок 14 формирования сигнала в устройстве фотоэлектрического преобразования согласно настоящему варианту осуществления включает в себя блок 16 счетчика и блок 17 селектора. Блок 16 счетчика подключен к блоку 13 преобразования импульсов и блоку 15 обнаружения периода. Блок 17 селектора подключен к блоку 16 счетчика.

[0074] Блок 16 счетчика подсчитывает количество импульсов напряжения, выводимых из блока 13 преобразования импульса к узлу PDOUT, и выводит сигнал DO[n–1:0], представляющий собой значение подсчета, в блок 17 селектора. На фиг. 6 показан случай, когда блок 16 счетчика включает в себя n–битный счетчик в качестве примера. Кроме того, блок 16 счетчика сконфигурирован, чтобы останавливать операцию подсчета в ответ на управляющий сигнал PCON, подаваемый из блока 15 обнаружения периода.

[0075] Блок 17 селектора выводит сигнал DO[n–1:0], который выводится из блока 16 счетчика, в выходную линию POUT в качестве сигнала POUT [n–1:0] на основании управляющего сигнала PVSEL, подаваемого из схемы 21 вертикального выбора. Каждая из сигнальной линии и выходной линии POUT, на которую выводится сигнал DO[n–1:0] из блока 16 счетчика, включает в себя n сигнальных линий, используемых для вывода n–битного цифрового сигнала.

[0076] Фиг. 7 представляет собой временную диаграмму, иллюстрирующую взаимосвязь потенциала узла PDOUT, управляющего сигнала PCON, сигнала DO[n–1:0], управляющего сигнала PVSEL и сигнала POUT[n–1:0].

[0077] В период до момента времени t1 значение подсчета, указанное сигналом DO[n–1:0], выводимое блоком 16 счетчика, равно нулю (0). Кроме того, управляющий сигнал PCON имеет заданный высокий уровень, когда ширина импульса напряжения меньше или равна заданному пороговому значению, и переходит на заданный низкий уровень, когда ширина импульса напряжения превышает заданное пороговое значение. В период до момента времени t1 управляющий сигнал PCON находится на высоком уровне. В период, предшествующий моменту времени t1, управляющий сигнал PVSEL находится на низком уровне.

[0078] Как показано на фиг. 7, присутствует падающий фотон в каждый момент времени t1, t2, t3, t4, t5, t6, t7, t8, t9, t10 и t12. Таким образом, импульс напряжения в соответствии с моментом падения фотона выводится из блока 13 преобразования импульсов в узел PDOUT.

[0079] Блок 16 счетчика подсчитывает импульсы напряжения, выводимые из блока 13 преобразования импульсов в узел PDOUT, и выводит результат подсчета в виде сигнала DO[n–1:0]. Фиг. 7 иллюстрирует случай, когда блок 16 счетчика подсчитывает импульсы напряжения, возникающие в соответствии с моментами падения фотонов в момент времени t1, t2, t3,..., и последовательно выводит значения подсчета, соответствующие десятичным числам 1, 2, 3,..., как сигнал DO[n–1:0].

[0080] Здесь, в момент времени t10, импульс напряжения, имеющий ширину, превышающую период Tp1, которая является шириной импульса в соответствии с падением одного фотона, выводится из блока 13 преобразования импульсов. Это при условии падения света высокой яркости, как описано с помощью фиг. 3B.

[0081] Блок 15 обнаружения периода заставляет управляющий сигнал PCON переходить с высокого уровня на низкий уровень, когда ширина импульса напряжения (длительность периода низкого уровня), выводимого на узел PDOUT, превышает заданный период времени. Например, как показано на фиг. 7 блок 15 обнаружения периода заставляет управляющий сигнал PCON переходить с высокого уровня на низкий уровень в момент времени t11, когда длительность периода, в котором импульс напряжения является низким уровнем, превышает предварительно заданный период времени.

[0082] Блок 16 счетчика останавливает операцию подсчета в ответ на прием управляющего сигнала PCON низкого уровня и сохраняет значение подсчета, когда операция подсчета останавливается. Даже если импульс напряжения выводится из блока 13 преобразования импульсов в последующее время t12, блок 16 счетчика напрямую сохраняет значение подсчета без изменений.

[0083] В момент времени t13 в ответ на управляющий сигнал PVSEL, подаваемый из схемы 21 вертикального выбора, управляемой высоким уровнем, блок 17 селектора выводит значение подсчета, сохраняемое блоком 16 счетчика, в выходную линию POUT как сигнал POUT[n–1:0].

[0084] Как описано выше, согласно настоящему варианту осуществления, в устройстве фотоэлектрического преобразования типа подсчета фотонов, ошибка значения подсчета при высокой яркости может быть уменьшена. Это может улучшить операцию фотоэлектрического преобразования при высокой яркости.

[0085] [Третий вариант осуществления]

[0086] Устройство фотоэлектрического преобразования и способ возбуждения устройства в соответствии с третьим вариантом осуществления настоящего изобретения будут описаны со ссылкой на фиг. 8 и фиг. 9. Компоненты, аналогичные компонентам устройства фотоэлектрического преобразования в соответствии с первым и вторым вариантами осуществления, обозначены теми же ссылками, и их описание будет опущено или упрощено. На фиг. 8 показана схема, иллюстрирующая пример конфигурации пикселя устройства фотоэлектрического преобразования в соответствии с настоящим вариантом осуществления. Фиг. 9 представляет собой временную диаграмму, иллюстрирующую работу пикселя устройства фотоэлектрического преобразования в соответствии с настоящим вариантом осуществления.

[0087] В настоящем варианте осуществления будет описан другой пример более конкретной конфигурации и работы блока 14 формирования сигнала. Как показано на фиг. 8, блок 14 формирования сигнала в устройстве фотоэлектрического преобразования согласно настоящему варианту осуществления дополнительно включает в себя блок 18 формирования замещающего сигнала в дополнение к блоку 16 счетчика и блоку 17 селектора, описанных во втором варианте осуществления. Блок 16 счетчика соединен с блоком 13 преобразования импульсов и блоком 15 определения периода. Блок 17 селектора соединен с блоком 16 счетчика и блоком 18 формирования замещающего сигнала.

[0088] Блок 16 счетчика подсчитывает количество импульсов напряжения, выводимых из блока 13 преобразования импульса к узлу PDOUT, и выводит сигнал DO1[n–1:0], представляющий собой значение подсчета, в блок 17 селектора. На фиг. 8 показан случай, когда блок 16 счетчик включает в себя n–битный счетчик в качестве одного примера.

[0089] Блок 18 формирования замещающего сигнала формирует и выводит сигнал DO2 [n–1:0], представляющий заданное значение замещающего сигнала, которое может быть значением замещения значения подсчета, выводимого блоком 16 счетчика в блок 17 селектора.

[0090] Блок 17 селектора выбирает один из сигнала DO1[n–1:0], подаваемого из блока 16 счетчика, и сигнала DO2[n–1:0], подаваемого из блока 18 формирования замещающего сигнала, на основе управляющего сигнала PCON, подаваемого из блока 15 определения периода, затем блок 17 селектора выводит выбранный сигнал (сигнал DO1[n–1:0] или сигнал DO2[n–1:0]) в выходную линию POUT на основе управляющего сигнала PVSEL, подаваемого от схемы 21 вертикального выбора. Каждая из сигнальной линии, на которую сигнал DO1[n–1:0] выводится из блока 16 счетчика, сигнальной линии, на которую выводится сигнал DO2[n–1:0] из блока 18 формирования замещающего сигнала, и выходной линии POUT включает в себя n сигнальных линий, используемых для вывода n–битного цифрового сигнала.

[0091] Фиг. 9 представляет собой временную диаграмму, иллюстрирующую взаимосвязь потенциала узла PDOUT, управляющего сигнала PCON, сигнала DO1[n–1:0], управляющего сигнала PVSEL, и сигнала POUT[n–1:0].

[0092] В период до момента времени t1 значение подсчета, указанное сигналом DO1[n–1:0], выводимое блоком 16 счетчика, равно нулю (0). Кроме того, управляющий сигнал PCON имеет заданный высокий уровень, когда ширина импульса напряжения меньше или равна заданному пороговому значению, и переходит на заданный низкий уровень, когда ширина импульса напряжения превышает заданное пороговое значение. В период до момента времени t1 управляющий сигнал PCON находится на высоком уровне. Кроме того, в период, предшествующий моменту времени t1, управляющий сигнал PVSEL находится на низком уровне.

[0093] Как показано на фиг. 9, присутствует падающий фотон в каждый момент времени t1, t2, t3, t4, t5, t6, t7, t8, t9, t10 и t12. Таким образом, импульс напряжения в соответствии с моментом падения фотона выводится из блока 13 преобразования импульсов в узел PDOUT.

[0094] Блок 16 счетчика подсчитывает импульсы напряжения, выводимые из блока 13 преобразования импульсов в узел PDOUT, и выводит результат подсчета в виде сигнала DO1[n–1:0]. Фиг. 9 иллюстрирует случай когда блок 16 счетчика подсчитывает импульсы напряжения, возникающие в соответствии с моментами падения фотонов в момент времени t1, t2, t3,..., и последовательно выводит значения подсчета, соответствующие десятичным числам 1, 2, 3,..., как сигнал DO1[n–1:0].

[0095] Здесь, в момент времени t10, импульс напряжения, имеющий ширину, превышающую период Tp1, которая является шириной импульса в соответствии с падением одного фотона, выводится из блока 13 преобразования импульсов. Это при условии падения света высокой яркости, как описано с помощью фиг. 3B.

[0096] Блок 15 обнаружения периода заставляет управляющий сигнал PCON переходить с высокого уровня на низкий уровень, когда ширина импульса напряжения (длительность периода низкого уровня), выводимого на узел PDOUT, превышает заданный период времени. Например, как показано на фиг. 9, блок 15 обнаружения периода заставляет управляющий сигнал PCON переходить с высокого уровня на низкий уровень в момент времени t11, когда длительность периода, в котором импульс напряжения является низким уровнем, превышает предварительно заданный период времени. Таким образом, блок 17 селектора находится в состоянии выбора сигнала DO2[n–1:0] из сигнала DO1[n–1:0] или сигнала DO2[n–1:0].

[0097] В момент времени t13 в ответ на управляющий сигнал PVSEL, подаваемый из схемы 21 вертикального выбора, управляемой высоким уровнем, блок 17 селектора выводит значение замещающего сигнала, удерживаемое блоком 18 формирования замещающего сигнала, в качестве сигнала POUT[n–1:0]. На фиг. 9 показан случай когда, значение замещающего сигнала, удерживаемое посредством блока 18 формирования замещающего сигнала, равно 2n–1, что является максимальным значением в n–битового счетчика в качестве одного примера.

[0098] Как описано выше, согласно настоящему варианту осуществления, в устройстве фотоэлектрического преобразования типа подсчета фотонов, ошибка значения подсчета при высокой яркости может быть уменьшена. Это может улучшить операцию фотоэлектрического преобразования при высокой яркости.

[0099] [Четвертый вариант осуществления]

[00100] Устройство фотоэлектрического преобразования и способ возбуждения устройства, в соответствии с четвертым вариантом осуществления настоящего изобретения будут описаны со ссылкой на фиг. 10 и фиг. 11. Компоненты, аналогичные компонентам устройства фотоэлектрического преобразования в соответствии с первым–третьим вариантами осуществления, обозначены теми же ссылками, и их описание будет опущено или упрощено. На фиг. 10 показана схема, иллюстрирующая пример конфигурации пикселя устройства фотоэлектрического преобразования в соответствии с настоящим вариантом осуществления. Фиг. 11 представляет собой временную диаграмму, иллюстрирующую работу пикселя устройства фотоэлектрического преобразования в соответствии с настоящим вариантом осуществления.

[00101] В настоящем варианте осуществления будет описан другой пример более конкретной конфигурации и работы пикселя P. Пиксель P устройства фотоэлектрического преобразования согласно настоящему варианту осуществления включает в себя лавинный умножающий диод D, блок 12 гашения, блок 13 преобразования импульсов, блок 15 обнаружения периода, блок 16 счетчика и блок 17 селектора, аналогично второму варианту осуществления, описанному с использованием фиг. 6. Блок 16 счетчика и блок 17 селектора соответствуют блоку 14 формирования сигнала на фиг. 6.

[00102] Блок 12 гашения может быть сформирован из p–канального МОП–транзистора Mq. Сток p–канального МОП–транзистора Mq соединен с катодом диода D и входной клеммой блока 13 преобразования импульсов. Исток p–канального МОП–транзистора Mq подключен к узлу источника питания, к которому подается напряжение VDD. Затвор p–канального МОП–транзистора соединен с источником питания, который подает напряжение VQNC, используемое для получения заданного сопротивления гашения.

[00103] Блок 13 преобразования импульсов может быть сформирован из схемы G1 NOT. Входная клемма схемы G1 NOT соответствует входной клемме блока 13 преобразования импульсов, а выходная клемма схемы G1 NOT соответствует выходной клемме блока 13 преобразования импульсов.

[00104] Блок 16 счетчика включает в себя схему Ga1 NOT и n–битный счетчик, образованный из n схем Fa0–Fa(n–1) триггера.

[00105] Выходная клемма схемы G1 NOT, которая также является выходной клеммой (узел PDOUT) блока 13 преобразования импульсов, подключена к одной входной клемме (CK) схемы Fa0 триггера и входной клемме схемы Ga1 NOT. Выходная клемма схемы Ga1 NOT соединена с другой входной клеммой (/CK) схемы Fa0 триггера. Схемы Fa0–Fa(n–1) триггера соединены каскадно, так что выходная клемма схемы Fam триггера младшего бита (m–й бит) и входная клемма схемы Fa(m+1) триггера старшего бита ((m+1)–й бит) связаны друг с другом. Например, выходная клемма (Q) схемы Fa0 триггера подключена к входной клемме (CK) схемы Fa1 триггера, а выходная клемма (/Q) схемы Fa0 триггера подключена к входной клемме (/CK) схемы Fa1 триггера. Таким образом, блок 16 счетчика формирует n–битный счетчик, который подсчитывает количество импульсов напряжения, выводимых из блока 13 преобразования импульсов в узел PDOUT.

[00106] Значение каждого бита сигнала DO[n–1:0], который является выходом блока 16 счетчика, выводится из выходной клеммы (/Q) каждой из схем Fa0–Fa(n–1) триггера. Например, значение 0–го бита (сигнал DO[0]) выводится из выходной клеммы (/Q) схемы Fa0 триггера. Значение первого бита (сигнал DO[1]) выводится из выходной клеммы (/Q) схемы Fa1 триггера. Значение (N–1)–го бита (сигнал DO[n–1]) выводится из выходной клеммы (/Q) схемы Fa(n–1) триггера. Следует отметить, что здесь показана конфигурация случая активного низкого уровня. Кроме того, каждая клемма сброса (RS) схемы Fa0–Fa(n–1) триггера обычно подключается к сигнальной линии, на которую подается управляющий сигнал RSB. Таким образом, блок 16 счетчика может сбрасывать значение подсчета посредством управляющего сигнала RSB. Т.е., когда управляющий сигнал RSB находится на низком уровне, значение подсчета блока 16 счетчика сбрасывается.

[00107] Блок 15 обнаружения периода включает в себя логическую схему, включающую в себя схему G2 NAND, схемы G3, G4 и G6 NOR, и схему G5 NOT и блок 19 счетчика. Блок 19 счетчика включает в себя схему Gb1 NOT и двухбитный счетчик, сформированный из двух схем Fb0 и Fb1 триггера. Следует отметить, что блок 19 счетчика может быть сформирован из счетчика из трех или более битов.

[00108] Выходная клемма (узел PDOUT) схемы G1 NOT, которая также является выходной клеммой блока 13 преобразования импульсов, дополнительно соединена с одной входной клеммой схемы G2 NAND и одной входной клеммой схемы G4 NOR. Другая входная клемма схемы G2 NAND подключена к сигнальной линии, на которую подается тактовый сигнал CCK. Выходная клемма схемы G2 NAND соединена с одной входной клеммой схемы G3 NOR. Выходная клемма схемы G4 NOR соединена с одной входной клеммой схемы G6 NOR. Входная клемма схемы G5 NOT соединена с сигнальной линией, на которую подается управляющий сигнал RSB. Выходная клемма схемы G5 NOT соединена с другой входной клеммой схемы G6 NOR.

[00109] Выходная клемма схемы G3 NOR соединена с входной клеммой (CK) схемы Fb0 триггера и входной клеммой схемы Gb1 NOT. Выходная клемма схемы Gb1 NOT соединена с входной клеммой (/CK) схемы Fb0 триггера. Выходная клемма схемы G6 NOR соединена с клеммой сброса (RS) схемы Fb0 и Fb1 триггера. Выходная клемма (Q) схемы Fb0 триггера соединена с входной клеммой (CK) схемы Fb1 триггера. Выходная клемма (/Q) схемы Fb0 триггера соединена с входной клеммой (/CK) схемы Fb1 триггера. Таким образом, блок 19 счетчика формирует двухбитный счетчик, который подсчитывает количество импульсов напряжения, выводимых из схемы G3 NOR в узел L1, который является входной клеммой. Значение сигнала CO[0], выводимого из выходной клеммы (Q) схемы Fb0 триггера, соответствует значению 0–го бита значения подсчета блока 19 счетчика. Кроме того, значение сигнала CO[1], выводимое из выходной клеммы (Q) схемы Fb1 триггера, соответствует значению первого бита значения подсчета блока 19 счетчика. Выходная клемма (Q) схемы Fb1 триггера соединена с другой входной клеммой схемы G3 NOR и другой входной клеммой схемы G4 NOR.

[00110] Таким образом, тактовый сигнал CCK, полученный, когда выход Q схемы Fb1 триггера находится на низком уровне, а узел PDOUT находится на высоком уровне, выборочно вводится в узел L1, соответствующий входной клемме блока 19 счетчика. Т.е. блок 19 счетчика сконфигурирован, чтобы подсчитывать количество тактовых сигналов CCK, вводимых, когда выход Q схемы Fb1 триггера находится на низком уровне, и узел PDOUT находится на высоком уровне. Следует отметить, что выход Q схемы Fb1 триггера находится на низком уровне, когда значение подсчета блока 19 счетчика меньше или равно единице (1).

[00111] Кроме того, блок 19 счетчика сконфигурирован так, что значение подсчета блока 19 счетчика сбрасывается, когда управляющий сигнал RSB находится на низком уровне, или по другому, когда выход Q схемы Fb1 триггера находится на низком уровне, и узел PDOUT находится на низком уровне.

[00112] В результате блок 19 счетчика подсчитывает количество тактовых сигналов CCK для каждого периода, в котором значение самого старшего бита равно нулю (0) (выход Q схемы Fb1 триггера находится на низком уровне), и узел PDOUT находится на высоком уровне. Следовательно, значение подсчета, указанное блоком 19 счетчика, служит в качестве индекса, представляющего длительность периода, в течение которого импульс напряжения, выводимый на узел PDOUT, постоянно находится на высоком уровне, т.е. ширину импульса напряжения.

[00113] Блок 17 селектора включает в себя n переключателей SW0–SW(n–1) и n схем Gs0–Gs(n–1) NAND в соответствии с соответствующими битами блока 16 счетчика. Каждый из переключателей SW0–SW(n–1) может быть сформирован из n–канального МОП–транзистора, например.

[00114] Одна входная клемма схем Gs0, GS1,…, Gs(n–1) NAND подключена к выходным клеммам (/Q) схем Fa0, Fa1,…, Fa (n–1) триггера блок 16 счетчика, соответственно. Другие входные клеммы схем Gs0, Gs1,…, Gs(n–1) NAND обычно подключаются к выходной клемме (/Q) схемы Fb1 триггера блока 19 счетчика. Сигнал, выводимый с выходной клеммы (/Q) схемы Fb1 триггера блока 19 счетчика, является управляющим сигналом PCON.

[00115] Выходная клемма схемы Gs0 NAND подключена к истоку n–канального МОП–транзистора, образующего переключатель SW0. Аналогичным образом, выходная клемма схемы Gs1 NAND подключена к истоку n–канального МОП–транзистора, образующего переключатель SW1. Каждый из стоков n–канальных МОП–транзисторов, образующих переключатели SW0, SW1,…, SW(n–1), подключен к сигнальной линии соответствующего бита выходной линии POUT, образованной из n сигнальных линий. Затворы n–канальных МОП–транзисторов, образующих переключатели SW0 и SW1, соединены с управляющей линией, на которую подается управляющий сигнал PVSEL из схемы 21 вертикального выбора.

[00116] Таким образом, блок 17 селектора выводит сигналы DO[0], DO[1],…, DO[n–1] в сигнальные линии соответствующих битов выходной линии POUT, образованной из n сигнальных линий, если управляющий сигнал PCON имеет вид на высоком уровне, когда управляющий сигнал PVSEL находится на высоком уровне. Т.е. сигнал POUT[n–1:0], выводимый на выходную линию POUT, является таким же, как сигнал DO[n–1:0], выводимый блоком 16 счетчика. Кроме того, блок 17 селектора выводит сигнал высокого уровня ко всем сигнальным линиям выходной линии POUT, сформированной из n сигнальных линий, если управляющий сигнал PCON находится на низком уровне, когда управляющий сигнал PVSEL находится на высоком уровне. Т.е. значение подсчета, представленное сигналом POUT[n–1:0], выводимое на выходную линию POUT, составляет 2n–1, что является максимальным значением в n–битном счетчике.

[00117] Фиг. 11 представляет собой временную диаграмму, иллюстрирующую взаимосвязь потенциалов узлов PDOUT и L1, тактового сигнала CCK, управляющих сигналов RSB, PCON и PVSEL и сигналов DO[n–1:0], CO[1:0] и POUT[n–1:0].

[00118] В период до момента времени t0 управляющий сигнал RSB находится на низком уровне. Как описано ранее, когда управляющий сигнал RSB имеет низкий уровень, блок 16 счетчика и блок 19 счетчика находятся в состоянии сброса. Значение подсчета, указанное сигналом DO[n–1:0], выводимым блоком 16 счетчика, и значение подсчета, указанное сигналом CO [1:0], выводимым блоком 19 счетчика, оба равны нулю (0). Управляющий сигнал PCON переходит на высокий уровень в ответ на выход (/Q) схемы Fb1 триггера. Кроме того, в период до момента времени t0 управляющий сигнал PVSEL находится на низком уровне.

[00119] В момент времени t0 управляющий сигнал RSB управляется от низкого уровня до высокого уровня, и состояние сброса блока 16 счетчика сбрасывается. Как только фотон входит в диод D, импульс напряжения в соответствии с моментом падения фотона выводится из блока 13 преобразования импульсов в узел PDOUT. В настоящем варианте осуществления, в котором блок 13 преобразования импульсов сформирован из схемы G1 NOT, узел PDOUT находится на низком уровне, когда нет падения фотона, и узел PDOUT находится на высоком уровне в ответ на падение фотона. Блок 16 счетчика подсчитывает количество импульсов напряжения, выводимых на узел PDOUT, и выводит сигнал DO[n–1:0], указывающий значение подсчета.

[00120] После момента времени t0 в моменты времени t1, t3, t4, t5, t6, t7, t8, t9, t10 и t13 импульсы напряжения возникают в узле PDOUT. Блок 16 счетчика подсчитывает количество этих импульсов напряжения. Значение подсчета блока 16 счетчика становится равным десятичному 10, когда подсчитывается до фронта импульса напряжения в момент времени t13.

[00121] С другой стороны, как только узел PDOUT переходит на высокий уровень, выходной сигнал схемы G2 NAND переходит на низкий уровень синхронно с тактовым сигналом CCK. Таким образом, импульс напряжения, синхронизированный с импульсом напряжения, возникающим в узле PDOUT, и тактовым сигналом CCK, выводится в узел L1, который является выходной клеммой схемы G3 NOR. Кроме того, в ответ на изменение узла PDOUT на высокий уровень, выход схемы G4 NOR переходит на низкий уровень, и состояние сброса блока 19 счетчика освобождается. Таким образом, блок 19 счетчика подсчитывает количество импульсов напряжения, выводимых на узел L1.

[00122] Операция подсчета блоком 19 счетчика непрерывно выполняется только в течение периода, в течение которого узел PDOUT находится на высоком уровне. В ответ на переход узла PDOUT на низкий уровень блок 19 счетчика возвращается в состояние сброса. Например, как только импульс напряжения выводится из блока 13 преобразования импульсов в момент времени t1, узел PDOUT переходит на высокий уровень, а узел L1 переходит на высокий уровень, блок 19 счетчика подсчитывает этот импульс напряжения, и значение подсчета блока 19 счетчика становится равным единице (1). В ответ на изменение узла PDOUT на низкий уровень в момент времени t2 блок 19 счетчика находится в состоянии сброса, и значение подсчета блока 19 счетчика возвращается к нулю (0).

[00123] В момент времени t12 значение самого старшего бита блока 19 счетчика становится равным единице (1). Это соответствует случаю, когда значение подсчета блока 19 счетчика становится равным десятичным двум (2) в примере, проиллюстрированном на фиг. 10. Затем выход (Q) схемы Fb1 триггера, соответствующий самому старшему биту, переходит на высокий уровень, узел L1 фиксируется на низком уровне, и подсчет в блоке 19 счетчика останавливается. Кроме того, управляющий сигнал PCON, который является выходом (/Q) схемы Fb1 триггера, переходит с высокого уровня на низкий уровень.

[00124] Управляющий сигнал PVSEL переходит с низкого уровня на высокий уровень в момент времени t14 после момента t12, и сигнал высокого уровня выводится на все сигнальные линии выходной линии POUT, образованной из n сигнальных линий. Т.е. значение подсчета, представленное сигналом POUT[n–1:0], выводимым на выходную линию POUT, становится 2n–1, что является максимальным значением в n–битном счетчике.

[00125] Следует отметить, что на фиг. 11, когда управляющий сигнал PVSEL переходит с низкого уровня на высокий уровень в момент времени до времени t12, то сигнал POUT[n–1:0], который является таким же как сигнал DO[n–1:0], выводимый блоком 16 счетчика, выводится на выходную линию POUT.

[00126] Как описано выше, блок 15 обнаружения периода обнаруживает ширину импульса напряжения, выводимого на узел PDOUT из блока 13 преобразования импульсов, используя блок 19 счетчика, синхронизированный с тактовым сигналом CCK, и выводит управляющий сигнал PCON, состояние которого переходит в соответствии с заданным пороговым значением, в блок 17 селектора. Таким образом, блок 17 селектора может выбрать либо сигнал подсчета фотонов, либо заданный фиксированный сигнал в качестве выходного сигнала пикселя P. Следовательно, можно определить, является ли или нет частота падения фотонов, попадающих в каждый пиксель P, выше частоты появления импульсов напряжения, и можно уменьшить погрешность значения счетчика при высокой яркости.

[00127] Как обсуждалось выше, согласно настоящему варианту осуществления, в устройстве фотоэлектрического преобразования типа подсчета фотонов, ошибка значения подсчета при высокой яркости может быть уменьшена. Это может улучшить операцию фотоэлектрического преобразования при высокой яркости.

[00128] [Пятый вариант осуществления]

[00129] Устройство фотоэлектрического преобразования и способ возбуждения устройства, в соответствии с пятым вариантом осуществления настоящего изобретения будут описаны со ссылкой на фиг. 12 и фиг. 13. Компоненты, аналогичные компонентам устройства фотоэлектрического преобразования в соответствии с первым–четвертым вариантами осуществления, обозначены теми же ссылками, и их описание будет опущено или упрощено. На фиг. 12 показана схема, иллюстрирующая пример конфигурации пикселя устройства фотоэлектрического преобразования в соответствии с настоящим вариантом осуществления. Фиг. 13 представляет собой временную диаграмму, иллюстрирующую работу пикселя устройства фотоэлектрического преобразования в соответствии с настоящим вариантом осуществления.

[00130] В настоящем варианте осуществления будет описан другой пример более конкретной конфигурации и работы пикселя P. Пиксель Р устройства фотоэлектрического преобразования согласно настоящему варианту осуществления является таким же, как и пиксель P устройства фотоэлектрического преобразования в соответствии с четвертым вариантом осуществления, описанным с помощью фиг. 11 за исключением конфигурации блока 15 обнаружения периода. Как показано на фиг. 12, блок 15 обнаружения периода пикселя P в настоящем варианте осуществления включает в себя логическую схему, включающую в себя схему G7 AND и схему G8 NOT, p–канальные МОП–транзисторы M1, M2 и Mc, n–канальный МОП–транзистор M3, и схему DL1 защелки.

[00131] Выходная клемма (узел PDOUT) схемы G1 NOT, которая также является выходной клеммой блока 13 преобразования импульсов, подключена к одной из трех входных клемм схемы G7 AND. Две другие из трех входных клемм схемы G7 AND подключены к сигнальной линии, на которую подается управляющий сигнал RSB, и к выходной клемме (/Q) схемы DL1 защелки. Выходная клемма схемы G7 AND подключена к входной клемме схемы G8 NOT и тактовой клемме (CK) схемы DL1 защелки.

[00132] Узел L2, который является выходной клеммой схемы G8 NOT, соединен с затвором p–канального МОП–транзистора M1 и затвором n–канального МОП–транзистора M3. Исток p–канального МОП–транзистора М1 подключен к узлу источника питания, на который подается напряжение VDD. Сток р–канального МОП–транзистора М1 соединен с истоком р–канального МОП–транзистора М2. Затвор p–канального МОП–транзистора M2 и исток n–канального МОП–транзистора M3 соединены с узлом источника питания, на который подается напряжение VSS.

[00133] Сток p–канального МОП–транзистора M2 и сток n–канального МОП–транзистора M3 соединены с затвором p–канального МОП–транзистора Mc и входной клеммой (D) схемы DL1 защелки. Соединительная часть стока p–канального МОП–транзистора M2, сток n–канального МОП–транзистора M3, затвор p–канального МОП–транзистора Mc и входная клемма (D) схемы DL1 защелки являются узлом L3. Исток и сток p–канального МОП–транзистора Mc подключены к узлу источника питания, на который подается напряжение VDD. Клемма сброса (RS) схемы DL1 защелки соединена с сигнальной линией, на которую подается управляющий сигнал RSB. Выходная клемма (/Q) схемы DL1 защелки подключена к другим входным клеммам схем Gs0, Gs1,…, Gs(n–1) NAND блока 17 селектора, соответственно. Сигнал, выводимый из выходной клеммы (/Q) схемы DL1 NAND, является управляющим сигналом PCON.

[00134] Исток и сток p–канального МОП–транзистора Mc обычно соединены с узлом источника питания, на который подается напряжение VDD, и образуют МОП–конденсатор, используемый для формирования интегральной схемы. Инвертированный сигнал узла PDOUT распространяется к узлу L2, когда управляющий сигнал RSB и управляющий сигнал PCON находятся на высоком уровне. P–канальный МОП–транзистор M1 и n–канальный МОП–транзистор M3 образуют схему NOT, в которой узел L2 является входной клеммой, а узел L3 является выходной клеммой. P–канальные МОП–транзисторы M1, M2 и Mc и n–канальный МОП–транзистор M3 сконфигурированы так, что ответ узла L3, соответствующего узлу L2, поднимается медленно и быстро падает.

[00135] Фиг. 13 представляет собой временную диаграмму, иллюстрирующую взаимосвязь потенциалов узлов PDOUT, L2 и L3, управляющих сигналов RSB, PCON и PVSEL, и сигналов DO[n–1:0] и POUT[n–1:0].

[00136] В период до момента времени t0 управляющий сигнал RSB находится на низком уровне. Когда управляющий сигнал RSB находится на низком уровне, блок 16 счетчика и схема DL1 защелки находятся в состоянии сброса. Т.е. значение подсчета, указанное сигналом DO[n–1:0], выводимым блоком 16 счетчика, равно нулю (0). Кроме того, управляющий сигнал PCON переходит на высокий уровень в ответ на выход (/Q) схемы DL1 защелки. Кроме того, в период до момента времени t0 управляющий сигнал PVSEL находится на низком уровне.

[00137] В момент времени t0 управляющий сигнал RSB управляется от низкого уровня до высокого уровня, и состояние сброса блока 16 счетчика сбрасывается. Как только фотон входит в диод D, импульс напряжения в соответствии с моментом падения фотона выводится из блока 13 преобразования импульсов в узел PDOUT. Блок 16 счетчика подсчитывает количество импульсов напряжения, выводимых на узел PDOUT, и выводит сигнал DO[n–1:0], указывающий значение подсчета.

[00138] После момента времени t0 в моменты времени t1, t3, t4, t5, t6, t7, t8, t9, t10 и t12 импульсы напряжения возникают в узле PDOUT. Блок 16 счетчика подсчитывает количество этих импульсов напряжения. Значение подсчета блока 16 счетчика становится равным десятичному 10, когда подсчитывается до подъема импульса напряжения в момент времени t12.

[00139] В момент времени t1, когда узел L2 переходит на низкий уровень в ответ на изменение потенциала узла PDOUT, потенциал узла L3 начинает расти. В момент времени t2, когда узел L2 возвращается на высокий уровень, потенциал узла L3 немедленно падает и достигает низкого уровня. Потенциал узла L3 выше, когда период узла L2, являющийся низким уровнем, длиннее, т.е. когда количество падающего света больше. Когда количество падающего света мало, и падение фотона соответствует появлению импульса напряжения по принципу один в один, потенциал узла L3 не превышает пороговое значение Vtld схемы LD1 защелки, и управляющий сигнал PCON остается на высоком уровне. Затем аналогичным образом операция подсчета блоком 16 счетчика выполняется с момента времени t3 до момента времени t10.

[00140] В момент времени t11 потенциал узла L3 превышает пороговое значение Vtld схемы LD1 защелки. В ответ выполняется операция защелкивания с помощью схемы LD1 защелки, и управляющий сигнал PCON, который является выходом (/Q) схемы LD1 защелки, переходит с высокого уровня на низкий уровень. Таким образом, узел L2 переходит на высокий уровень, и потенциал узла L3 немедленно падает и достигает низкого уровня.

[00141] В последующее время t12, в ответ на возникновение импульса напряжения в узле PDOUT, в то время как выполняется операция подсчета блока 16 счетчика, управляющий сигнал PCON находится на низком уровне, и, таким образом, узел L2 остается на высоком уровне. В результате управляющий сигнал PCON поддерживается на низком уровне.

[00142] Когда управляющий сигнал PVSEL переходит от низкого уровня к высокому уровню в момент времени t13 после момента t11, блок 17 селектора выводит сигнал высокого уровня на все сигнальные линии выходной линии POUT, сформированные из n сигнальных линий в ответ на низкий уровень управляющего сигнала PCON. Т.е. значение подсчета, представленное сигналом POUT[n–1:0], выводимым на выходную линию POUT, становится 2n–1, что является максимальным значением в n–битном счетчике.

[00143] Следует отметить, что на фиг. 13, когда управляющий сигнал PVSEL переходит с низкого уровня на высокий уровень в момент времени до времени t11, то сигнал POUT[n–1:0], который является таким же как сигнал DO[n–1:0], выводимый блоком 16 счетчика, выводится на выходную линию POUT.

[00144] Как описано выше, блок 15 обнаружения периода определяет ширину импульса напряжения, выводимого на узел PDOUT из блока 13 преобразования импульсов, используя скорость отклика сигнала, синхронизированного с импульсом напряжения, и выводит управляющий сигнал PCON, состояние которого переходит в соответствии с заданным пороговым значением, в блок 17 селектора. Таким образом, блок 17 селектора может выбрать либо сигнал подсчета фотонов, либо заданный фиксированный сигнал в качестве выходного сигнала пикселя P. Следовательно, можно определить, действительно ли или нет частота падения фотонов, входящих в каждый пиксель P, выше частоты появления импульсов напряжения, и это позволяет уменьшить погрешность значения подсчета при высокой яркости.

[00145] Устройство фотоэлектрического преобразования согласно настоящему варианту осуществления имеет меньше элементов, чем устройство фотоэлектрического преобразования согласно четвертому варианту осуществления, и, кроме того, не требует линии тактового сигнала и, таким образом, обеспечивает высокую интеграцию.

[00146] Как обсуждалось выше, согласно настоящему варианту осуществления, в устройстве фотоэлектрического преобразования типа подсчета фотонов, ошибка значения подсчета при высокой яркости может быть уменьшена. Это может улучшить операцию фотоэлектрического преобразования при высокой яркости.

[00147] [Шестой вариант осуществления]

[00148] Устройство фотоэлектрического преобразования согласно шестому варианту осуществления настоящего изобретения будет описано со ссылкой на фиг. 14. В настоящем варианте осуществления напряжение обратного смещения, приложенное к диоду D, управляется так, что диод D выходит из режима Гейгера, когда ширина импульса напряжения, выводимого на узел PDOUT (длительность периода низкого уровня), превышает заданный период времени. Блок 15 определения периода выполняет управление напряжением обратного смещения, приложенного к диоду D.

[00149] Фиг. 14 иллюстрирует пример конфигурации пикселя P в устройстве фотоэлектрического преобразования в соответствии с настоящим вариантом осуществления. В настоящем варианте осуществления блок 15 обнаружения периода выводит управляющий сигнал PCON2 в блок 12 гашения. Отметим, что управляющий сигнал PCON1 на фиг. 14 является управляющим сигналом PCON первого варианта осуществления.

[00150] Управляющий сигнал PCON2 также является сигналом, состояние которого изменяется, когда ширина импульса напряжения, указывающего падение фотона, превышает заданное пороговое значение таким же образом, как и управляющий сигнал PCON1.

[00151] Как описано также в первом варианте осуществления, напряжение обратного смещения, большее или равное напряжению пробоя, подается на диод D через блок 12 гашения от узла источника питания, который подает напряжение VDD или VBIAS в режиме Гейгера. Когда управляющий сигнал PCON2 находится на высоком уровне, блок 12 гашения выполняет ту же операцию, что и в первом варианте осуществления. Т.е. существует состояние, в котором лавинное умножение включено как режим Гейгера, и возникновение лавинного умножения приводит к выходу из режима Гейгера. Затем режим снова переходит в режим Гейгера. С другой стороны, как только управляющий сигнал PCON2 изменяется с высокого уровня на низкий уровень, блок 12 гашения работает так, чтобы не выполнять обратный переход в режим Гейгера. Например, напряжение VQNC управляется до напряжения, которое отключает канал МОП–транзистора Mq, и электрическая цепь между напряжением VDD и диодом D отключается. Таким образом, после выхода из режима Гейгера посредством лавинного умножения диод D не возвращается в режим Гейгера и поддерживается вне режима Гейгера в течение заданного периода. Этот заданный период может быть периодом, например, от времени выхода из режима Гейгера до времени начала периода экспозиции, соответствующего следующему кадру.

[00152] Таким образом, поскольку возможно предотвратить лавинное умножение в диоде D, потребляемая мощность диода D может быть уменьшена.

[00153] Следует отметить, что, хотя управляющий сигнал PCON1 выводится в блок 14 формирования сигнала в качестве управляющего сигнала PCON первого варианта осуществления в настоящем варианте осуществления, потребляемая мощность диода D может быть уменьшена посредством отсутствия вывода управляющего сигнала PCON1, и, таким образом, установлен настоящий вариант осуществления.

[00154] Кроме того, хотя блок 12 гашения управляется управляющим сигналом PCON2 в настоящем варианте осуществления, диод D может поддерживаться вне режима Гейгера в течение заданного периода посредством управления одним или обоими напряжением VDD и напряжением VBIAS. Альтернативно, между диодом D и узлом напряжения VBIAS может быть предусмотрен переключатель, и переключателем можно управлять так, чтобы он был непроводящим, когда управляющий сигнал PCON2 находится на низком уровне.

[00155] Согласно настоящему варианту осуществления потребляемая мощность диода D при высокой яркости может быть уменьшена. Таким образом, тепловыделение устройства фотоэлектрического преобразования из–за увеличения потребляемой мощности может быть уменьшено, и неисправность других пикселей P устройства фотоэлектрического преобразования (флуктуация рабочей точки лавинного умножения, нестабильная работа пикселей P или подобное) также может быть предотвращена.

[00156] Следует отметить, что настоящий вариант осуществления был описан на основе конфигурации первого варианта осуществления, но может быть применен к другим вариантам осуществления.

[00157] [Седьмой вариант осуществления]

[00158] Система формирования изображения в соответствии с седьмым вариантом осуществления настоящего изобретения будет описана с использованием фиг. 15. Фиг. 15 представляет собой блок–схему, иллюстрирующую пример конфигурации системы формирования изображения в соответствии с настоящим вариантом осуществления.

[00159] Как показано на фиг. 15, система 200 формирования изображения в соответствии с настоящим вариантом осуществления включает в себя барьер 201, объектив 202, апертуру 203, устройство 204 фотоэлектрического преобразования и датчик 205 AF. Объектив 202 представляет собой оптическую систему, используемую для захвата оптического изображения объекта. Барьер 201 защищает объектив 202. Апертура 203 предназначена для регулировки количества света, проходящего через объектив 202. Устройство 204 фотоэлектрического преобразования сформировано с использованием устройства 100 фотоэлектрического преобразования, описанного в вариантах осуществления с первого по шестой, которое предназначено для получения оптического изображения объекта, захваченного объективом 202, в качестве сигнала изображения. Датчик 205 AF предназначен для получения сигнала, необходимого для обнаружения фокуса.

[00160] Кроме того, система 200 формирования изображения дополнительно включает в себя блок 208 обработки сигналов. Блок 208 обработки сигналов предназначен для выполнения процесса вывода сигнала из устройства 204 фотоэлектрического преобразования или датчика 205 AF или для выполнения различной коррекции на полученных данных изображения или процесса для упаковки данных.

[00161] Кроме того, система 200 формирования изображения дополнительно включает в себя блок 209 памяти, схему 210 внешнего интерфейса, блок 211 формирования синхронизации, блок 212 общего управления/работы и блок 213 интерфейса управления носителем хранения данных. Блок 209 памяти предназначен для временного хранения данных изображения. Схема 210 внешнего интерфейса предназначена для связи с внешним устройством, таким как внешний компьютер 215. Блок 211 формирования синхронизации предназначен для вывода различных сигналов синхронизации в блок 208 обработки сигналов или т.п. Блок 212 общего управления/работы предназначен для управления различными вычислениями и всей камерой. Блок 213 интерфейса управления носителем хранения данных предназначен для обмена данными со съемным носителем 214 хранения данных, таким как полупроводниковая память, используемая для хранения полученных данных изображения или считывания данных изображения.

[00162] Когда барьер 201 открывается, оптическое изображение от объекта поступает в датчик 205 AF через объектив 202 и апертуру 203. Блок 212 общего управления/работы рассчитывает расстояние до объекта с использованием схемы обнаружения разности фаз, описанной выше, на основе выходного сигнала от датчика 205 AF. Затем блок 212 общего управления/работы приводит в действие объектив 202 на основе результата вычисления, снова определяет, получена ли или нет фокусировка на поверхности захвата, и при определении, что фокусировка не получена, выполняет управление автофокусировкой, чтобы снова приводить в действие объектив 202.

[00163] Затем, после подтверждения фокусировки, начинается операция накопления заряда устройством 204 фотоэлектрического преобразования. По завершении операции накопления заряда устройства 204 фотоэлектрического преобразования сигнал изображения, выводимый из устройства 204 фотоэлектрического преобразования, записывается в блок 209 памяти блоком 212 общего управления/работы через блок 208 обработки сигналов.

[00164] Данные, накопленные в блоке 209 памяти, затем сохраняются на носителе 214 хранения данных через блок 213 интерфейса управления носителем хранения данных посредством управления блоком 212 общего управления/работы. Альтернативно, данные, накопленные в блоке 209 памяти, могут быть непосредственно введены во внешний компьютер 215 или т.п. через схему 210 внешнего интерфейса.

[00165] Как описано в вариантах осуществления с первого по шестой, использование устройства 100 фотоэлектрического преобразования, проиллюстрированного в вышеупомянутых вариантах осуществления, может уменьшить ошибку значения счетчика при высокой яркости. Следовательно, в соответствии с системой формирования изображения настоящего варианта осуществления, использующей устройство 204 фотоэлектрического преобразования, может быть получено изображение более высокого качества.

[00166] [Восьмой вариант осуществления]

[00167] Система формирования изображения и подвижный объект в соответствии с восьмым вариантом осуществления настоящего изобретения будут описаны с помощью фиг. 16А и 16B. На фиг. 16A показана схема, иллюстрирующая конфигурацию системы формирования изображения в соответствии с настоящим вариантом осуществления. Фиг. 16B показана схема, иллюстрирующая конфигурацию подвижного объекта в соответствии с настоящим вариантом осуществления.

[00168] Фиг. 16A иллюстрирует пример системы формирования изображения, связанного с камерой на транспортном средстве. Система 300 формирования изображения включает в себя устройство 310 формирования изображения. Устройство 310 формирования изображения является устройством 100 фотоэлектрического преобразования, описанным в любом из вышеупомянутых первом–шестом вариантах осуществления. Система 300 формирования изображения включает в себя блок 312 обработки изображения, который выполняет обработку изображения для множества данных изображения, полученных устройством 310 формирования изображения, и блок 314 получения параллакса, который вычисляет параллакс (разность фаз параллаксных изображений) из множества данных изображения, полученных системой 300 формирования изображения. Кроме того, система 300 формирования изображения включает в себя блок 316 получения расстояния, который вычисляет расстояние до объекта на основе вычисленного параллакса, и блок 318 определения столкновения, который определяет, существует ли или нет возможность столкновения на основе вычисленного расстояния. Здесь блок 314 получения параллакса и блок 316 получения расстояния являются примером устройства получения информации расстояния, которое получает информацию расстоянии о расстоянии до объекта. Т.е. информация расстояния представляет собой информацию о параллаксе, величине расфокусировки, расстоянии до объекта и т.п. Блок 318 определения столкновения может использовать любую из приведенной выше информаций расстояния для определения возможности столкновения. Устройство получения информации расстояния может быть реализовано специально разработанным аппаратным обеспечением или может быть реализовано программным модулем. Кроме того, устройство получения информации расстоянии может быть реализовано программируемой пользователем вентильной матрицей (FPGA), специализированной интегральной схемой (ASIC) или т.п., или может быть реализовано их комбинацией.

[00169] Система 300 формирования изображения подключена к устройству 320 получения информации транспортного средства и может получать информацию транспортного средства, такую как скорость транспортного средства, скорость относительно вертикальной оси, угол поворота рулевого колеса и т.п. Кроме того, система 300 формирования изображения подключена к ECU 330 управления, который представляет собой устройство управления, которое выводит управляющий сигнал для инструктирования транспортному средству формировать тормозную силу на основании результата определения, выполняемого блоком 318 определения столкновения. Кроме того, система 300 формирования изображения также подключена к устройству 340 оповещения, которое выдает предупреждение водителю на основании результата определения блоком 318 определения столкновения. Например, когда вероятность столкновения является высокой, как результат определения блока 318 определения столкновения, ECU 330 выполняет управление транспортным средством, чтобы избежать столкновения или уменьшить повреждение, применяя тормоз, толкая назад акселератор, подавляя мощность двигателя или т.п. Устройство 340 оповещения предупреждает пользователя путем подачи звукового оповещения, такого как звук, отображения информации оповещения на дисплее автомобильной навигационной системы или т.п., обеспечения вибрации ремня безопасности или рулевого колеса и т.п.

[00170] В настоящем варианте осуществления область вокруг транспортного средства, например передняя область или задняя область, захватывается с использованием системы 300 формирования изображения. Фиг. 16B иллюстрирует систему формирования изображения, когда захватывается передняя область транспортного средства (область 350 захвата). Устройство 320 сбора информации транспортного средства передает инструкцию в систему 300 формирования изображения или в устройство 310 формирования изображения. Такая конфигурация может дополнительно улучшить точность определения дальности.

[00171] Хотя пример управления для предотвращения столкновения с другим транспортным средством был описан выше, вариант осуществления применим к автоматическому управлению вождением для следования за другим транспортным средством, автоматическому управлению вождением для сохранения полосы движения и т.п. Кроме того, система формирования изображения не ограничивается транспортным средством, таким как рассматриваемое транспортное средство, и может применяться, например, к подвижному объекту (движущемуся устройству), такому как корабль, самолет или промышленный робот. Кроме того, система формирования изображения может широко применяться к устройству, которое использует распознавание объектов, такое как интеллектуальная транспортная система (ITS), без ограничения подвижными объектами.

[00172] [Модифицированные варианты осуществления]

[00173] Настоящее изобретение не ограничено вариантами осуществления, описанными выше, и возможны различные модификации.

[00174] Например, пример, в котором часть конфигурации любого из вариантов осуществления добавляется в другой вариант осуществления, или пример, в котором часть конфигурации любого из вариантов осуществления заменяется частью конфигурации другого варианта осуществления, является одним вариантов осуществления настоящего изобретения.

[00175] Кроме того, схема пикселя, формирующая пиксель P в устройстве фотоэлектрического преобразования описанного выше варианта осуществления с первого по шестой, не ограничивается проиллюстрированными.

[00176] Кроме того, схема счетчика, формирующая блок 19 счетчика блока 15 обнаружения периода, сформирована из двухбитного счетчика в четвертом варианте осуществления, описанном выше, но может быть сформирована из трех или более битных счетчиков. Схема счетчика, формирующая блок 19 счетчика, может быть изменена соответствующим образом в соответствии с шириной импульса напряжения, который является ссылкой.

[00177] Кроме того, системы формирования изображения, проиллюстрированные в вышеупомянутых седьмом и восьмом вариантах осуществления, представляют собой пример системы формирования изображения, к которому может быть применено устройство фотоэлектрического преобразования настоящего изобретения, и система формирования изображения, к которой может быть применено устройство фотоэлектрического преобразования настоящего изобретения, не ограничено конфигурацией, изображенной на фиг. 15 и фиг. 16А.

[00178] В то время как настоящее изобретение было описано со ссылкой на примерные варианты осуществления, должно быть понятно, что изобретение не ограничено раскрытыми примерными вариантами осуществления. Рамки следующей формулы должны соответствовать самой широкой интерпретации, так, чтобы охватывать все такие модификации и эквивалентные структуры и функции.

Реферат